# A Touch of Evil: High-Assurance Cryptographic Hardware from Untrusted Components

Vasilios Mavroudis University College London v.mavroudis@cs.ucl.ac.uk

Dan Cvrcek EnigmaBridge dan@enigmabridge.com Andrea Cerulli University College London andrea.cerulli.13@ucl.ac.uk

Dusan Klinec EnigmaBridge dusan@enigmabridge.com Petr Svenda Masaryk University svenda@fi.muni.cz

George Danezis University College London g.danezis@ucl.ac.uk

### **ABSTRACT**

The semiconductor industry is fully globalized and integrated circuits (ICs) are commonly defined, designed and fabricated in different premises across the world. This reduces production costs, but also exposes ICs to supply chain attacks, where insiders introduce malicious circuitry into the final products. Additionally, despite extensive post-fabrication testing, it is not uncommon for ICs with subtle fabrication errors to make it into production systems. While many systems may be able to tolerate a few byzantine components, this is not the case for cryptographic hardware, storing and computing on confidential data. For this reason, many error and backdoor detection techniques have been proposed over the years. So far all attempts have been either quickly circumvented, or come with unrealistically high manufacturing costs and complexity.

This paper proposes Myst, a practical high-assurance architecture, that uses commercial off-the-shelf (COTS) hardware, and provides strong security guarantees, even in the presence of multiple malicious or faulty components. The key idea is to combine protective-redundancy with modern threshold cryptographic techniques to build a system tolerant to hardware trojans and errors. To evaluate our design, we build a Hardware Security Module that provides the highest level of assurance possible with COTS components. Specifically, we employ more than a hundred COTS secure cryptocoprocessors, verified to FIPS140-2 Level 4 tamper-resistance standards, and use them to realize high-confidentiality random number generation, key derivation, public key decryption and signing. Our experiments show a reasonable computational overhead (less than 1% for both Decryption and Signing) and an exponential increase in backdoor-tolerance as more ICs are added.

# **KEYWORDS**

cryptographic hardware; hardware trojans; backdoor-tolerance; secure architecture

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

CCS '17, October 30-November 3, 2017, Dallas, TX, USA

© 2017 Copyright held by the owner/author(s). Publication rights licensed to Association for Computing Machinery.

ACM ISBN 978-1-4503-4946-8/17/10...\$15.00 https://doi.org/10.1145/3133956.3133961

### 1 INTRODUCTION

Many critical systems with high security needs rely on secure cryptoprocessors to carry out sensitive security tasks (e.g., key generation and storage, legally binding digital signature, code signing) and provide a protection layer against cyber-attacks and security breaches. These systems are typically servers handling sensitive data, banking infrastructure, military equipment and space stations. In most cases, secure cryptoprocessors come embedded into Hardware Security Modules, Trusted Platform Modules and Cryptographic Accelerators, which are assumed to be both secure and reliable. This entails that errors in any of the Integrated Circuits (ICs) would be devastating for the security of the final system. For this reason, the design and fabrication of the underlying ICs must abide f to high-quality specifications and standards. These ensure that there are no intentional or unintentional errors in the circuits, but more importantly ensure the integrity of the hardware supply chain. [50].

Unfortunately, vendors are not always able to oversee all parts of the supply chain [36, 58]. The constant reduction in transistor size makes IC fabrication an expensive process, and IC designers often outsource the fabrication task to overseas foundries to reduce their costs [33, 44, 97]. This limits vendors to run only post-fabrication tests to uncover potential defects. Those tests are very efficient against common defects, but subtle errors are hard to uncover. For instance, cryptoprocessors with defective RNG modules and hardware cipher implementations have made it into production in the past [30, 37].

Additionally, parts of the IC's supply chain are left vulnerable to attacks from malicious insiders [11, 61, 65, 82] and have a higher probability of introducing unintentional errors in the final product. In several documented real-world cases, contained errors, backdoors or trojan horses. For instance, recently an exploitable vulnerability was discovered on Intel processors that utilize Intel Active Management Technology (AMT) [47], while vulnerable ICs have been reported in military [57, 76] applications, networking equipment [38, 48], and various other application [2, 54, 74, 75]. Furthermore, the academic community has designed various types of hardware trojans (HT), and backdoors that demonstrate the extent of the problem and its mitigation difficulty [10, 17, 22, 52, 63, 89–91].

Due to the severity of these threats, there is a large body of work on the mitigation of malicious circuitry. Existing works have pursued two different directions: detection and prevention. Detection techniques aim to determine whether any HTs exist in a given circuit [3, 77, 93, 95], while prevention techniques either

impede the introduction of HTs, or enhance the efficiency of HT detection [27, 67, 86, 87, 92]. Unfortunately, both detection and prevention techniques are brittle, as new threats are able to circumvent them quickly [92]. For instance, analog malicious hardware [96] was able to evade known defenses, including split manufacturing, which is considered one of the most promising and effective prevention approaches. Furthermore, most prevention techniques come with a high manufacturing cost for higher levels of security [18, 27, 92], which contradicts the motives of fabrication outsourcing. To make matters worse, vendors that use commercial off-the-shelf (COTS) components are constrained to use only post-fabrication detection techniques, which further limits their mitigation toolchest. All in all, backdoors being triggered by covert means and mitigation countermeasures are in an arms race that seems favorable to the attackers [92, 94].

In this paper, we propose Myst a new approach to the problem of building trustworthy cryptographic hardware. Instead of attempting to detect or prevent hardware trojans and errors, we proposed and provide evidence to support the hypothesis:

"We can build high-assurance cryptographic hardware from a set of untrusted components, as long as at least one of them is not compromised, even if benign and malicious components are indistinguishable."

Our key insight is that by combining established privacy enhancing technologies (PETs), with mature fault-tolerant system architectures, we can distribute trust between multiple components originating from non-crossing supply chains, thus reducing the likelihood of compromises. To achieve this, we deploy distributed cryptographic schemes on top of an N-variant system architecture, and build a trusted platform that supports a wide-range of commonly used cryptographic operations (e.g., random number and key generation, decryption, signing). This design draws from protective-redundancy and component diversification [26] and is built on the assumption that multiple processing units and communication controllers may be compromised by the same adversary. However, unlike N-variant systems, instead of replicating the computations on all processing units, Myst uses multi-party cryptographic schemes to distribute the secrets so that the components hold only shares of the secrets (and not the secrets themselves), at all times. As long as one of the components remains honest, the secret cannot be reconstructed or leaked. Moreover, we can tolerate two or more non-colluding adversaries who have compromised 100% of the components.

Our proposed architecture is of particular interest for two distinct categories of hardware vendors:

- ❖ Design houses that outsource the fabrication of their ICs.

- COTS vendors that rely on commercial components to build their high-assurance hardware.

Understandably, design houses have much better control over the IC fabrication and the supply chain, and this allows them to take full advantage of our architecture. In particular, they can combine existing detection [7, 25, 66] and prevention techniques [24, 27, 67, 92] with our proposed design, to reduce the likelihood of compromises for individual components. On the other hand, COTS vendors have less control as they have limited visibility in the fabrication process

and the supply chain. However, they can still mitigate risk by using ICs from sources, known to run their own fabrication facilities.

To our knowledge this is the first work to use distributed cryptographic protocols to architect hardware that is tolerant to multiple components carrying trojans or errors. To summarize, this paper makes the following contributions:

- Concept: We introduce backdoor-tolerance, where a system can still preserve its security properties in the presence of multiple compromised components.

- ❖ Design: We demonstrate how cryptographic schemes (§4) can be combined with N-variant system architectures (§3), to build high-assurance systems. Moreover, we introduce a novel distributed signing scheme based on the Schnorr blind signatures (§4.5).

- Implementation: We implement the proposed architecture by building a custom board featuring 120 highly-tamper resistant ICs, and realize secure variants of random number and key generation, public key decryption and signing (§5).

- Optimizations: We implement a number of optimizations to ensure the Myst architecture is competitive in terms of performance compared to single ICs. Some optimizations also concern embedded mathematical libraries which are of independent interest.

- Evaluation: We evaluate the performance of Myst, and use micro-benchmarks to assess the cost of all operations and bottlenecks (§6).

Related works and their relation to Myst are discussed in Section 7.

# 2 PRELIMINARIES

In this section, we introduce *backdoor-tolerance*, and outline our security assumptions for adversaries residing in the IC's supply chain.

#### 2.1 Definition

A *Backdoor-Tolerant* system is able to ensure the confidentiality of the secrets it stores, the integrity of its computations and its availability, against an adversary with defined capabilities. Such a system can prevent data leakages and protect the integrity of the generated keys and random numbers. Note that the definition makes no distinction between honest design or fabrication mistakes and hardware trojans, and accounts only for the impact these errors have on the security properties of the system.

## 2.2 Threat Model

We assume an adversary is able to incorporate errors (e.g., a hardware trojan) in some ICs but not all of them. This is because, ICs are manufactured in many different fabrication facilities and locations by different vendors and the adversary is assumed not to be able to breach all their supply chains. Malicious ICs aim to be as stealthy as possible, and conceal their presence as best as possible, while benign components may have hard to detect errors (e.g., intermittent faults) that cannot be trivially uncovered by post-fabrication tests. Hence, malicious and defective components are indistinguishable from benign/non-faulty ones.

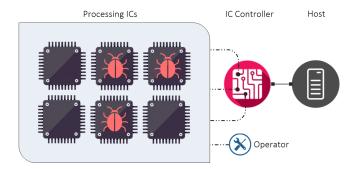

Figure 1: An overview of the Myst's distributed architecture, featuring all the integral components and communication buses. The gray area represents the cryptographic device, featuring several untrusted cryptoprocessors (ICs). As shown, the trusted operator interacts with individual ICs, while the host interacts with the device as a whole.

The adversary can gain access to the secrets stored in the malicious ICs and may also breach the integrity of any cryptographic function run by the IC (e.g., a broken random number generator). Moreover, the adversary has full control over the communication buses used to transfer data to and from the ICs. Hence, they are able to exfiltrate any information on the bus and the channel controller, and inject and drop messages to launch attacks. Additionally, they are able to connect and issue commands to the ICs, and if a system features more that one malicious ICs, the adversary is able to orchestrate attacks using all of them (i.e., colluding ICs). We also assume that the adversary may use any other side-channel that a hardware Trojan has been programmed to emit on – such as RF [5], acoustic [39] or optical [6] channels. Additionally, the adversary can trigger malicious ICs to cease functioning (i.e., availability attacks). We also make standard cryptographic assumptions about the adversary being computationally bound.

Finally, we assume a software developer or device operator builds and signs the applications to be run on the ICs. From our point of view they are trusted to provide high-integrity software without backdoors or other flaws. This integrity concern may be tackled though standard high- integrity software development techniques, such as security audits, public code repository trees, deterministic builds, etc. The operator is also trusted to initialize the device properly and choose ICs and define diverse quorums so that the probability of compromises is minimized.

#### 3 ARCHITECTURE

In this section, we introduce the Myst architecture (build and evalutation in § 5 and 6), which draws from fault-tolerant designs and N-variant systems [26, 80]. The proposed design is based on the thesis that given a diverse set of k ICs sourced from k untrusted suppliers, a trusted system can be build, as long as at least one of them is honest. Alternatively, our architecture can tolerate up to 100% compromised or defective components, if not all of them collude with each other. As illustrated in Figure 1, Myst has three types of components: (1) a remote host, (2) an untrusted IC controller, and (3) the processing ICs.

**Processing ICs.** The ICs form the core of Myst, as they are collectively entrusted to perform high-integrity computations, and provide secure storage space. The ICs are programmable processors or microprocessors. They have enough persistent memory to store keys and they feature a secure random number generator. Protection against physical tampering or side-channels is also desirable in most cases and mandated by the industry standards and best practices for cryptographic hardware. For this reason, our prototype (Section 5), comprises of components that verify to the a very high level of tamper-resistance (i.e., FIPS140-2 Level 4), and feature a reliable random number generator (i.e., FIPS140-2 Level 3). Each implementation must feature two or more ICs, of which at least one must be free of backdoors. We define this coalition of ICs, as a quorum. The exact number of ICs in a quorum is determined by the user depending on the degree of assurance she wants to achieve (see also Subsection 3.2 and the Assessment Subsection 6).

**IC controller.** The controller enables communication between the ICs, and makes Myst accessible to the outside world. It manages the bus used by the processing ICs to communicate with each other and the interface where user requests are delivered to. Specifically, it enables:

- Unicast, IC-to-IC: an IC A sends instructions an IC B, and receives the response.

- Broadcast, IC-to-ICs: an IC A broadcasts instructions to all other ICs, and receive their responses.

- Unicast, Host-to-IC: a remote client send commands to a specific IC, and receives the response.

- Broadcast, Host-to-ICs: a remote client broadcasts commands to all ICs, and receive their responses.

The controller is also an IC and is also untrusted. For instance it may drop, modify packets or forge new ones, in order to launch attacks against the protocols executed. It may also collude with one or more processing ICs.

**Operator.** The operator is responsible for setting up the system and configuring it. In particular, they are responsible for sourcing the ICs and making sure the quorums are as diverse as possible. Moreover, the operator determines the size of the quorums, and sets the security parameters of the cryptosystem (Section 4). They are assumed to make a best effort to prevent compromises and may also be the owner of the secrets stored in the device.

Remote Host. The remote host connects to Myst through the IC controller; it issues high level commands and retrieves the results. The remote host can be any kind of computer either in the local network or in a remote one. In order for the commands to be executed by the ICs, the host must provide proof of its authorization to issue commands, usually by signing them with a public key associated with the user's identity (e.g., certificate by a trusted CA). Each command issued must include: 1) the requested operation, 2) any input data, and 3) the host's signature (see also Section 3.1). We note that a corrupt host may use Myst to perform operations, but cannot extract any secrets, or forge signatures (see also § 3.1).

**Communication Channels.** At the physical level, the ICs, the controller, and the hosts are connected through buses and network interfaces. Hence, all messages containing commands, as well as their eventual responses are routed to and from the ICs through

untrusted buses. We assume that the adversary is able to eavesdrop on these buses and tamper with their traffic (e.g., inject or modify packets). To address this, we use established cryptographic mechanisms to ensure integrity and confidentiality for transmitted data. More specifically, all unicast and broadcast packets are signed using the sender IC's certificate, so that their origin and integrity can be verified by recipients. Moreover, in cases where the confidentiality of the transmitted data needs to be protected, encrypted end-to-end channels are also established. Such encrypted channels should be as lightweight as possible to minimize performance overhead, yet able to guarantee both the confidentiality and the integrity of the transmitted data.

# 3.1 Access Control Layer

Access Control (AC) is critical for all systems operating on confidential data. In Myst, AC determines which hosts can submit service requests to the system, and which quorums they can interact with. Despite the distributed architecture of Myst, we can simply replicate established AC techniques on each IC. More specifically, each IC is provided with the public keys of the hosts that are allowed to have access to its shares and submit requests. Optionally, this list may distinguish between hosts that have full access to the system, and hosts that may only perform a subset of the operations. Once a request is received, the IC verifies the signature of the host against this public key list. The list can be provided either when setting up Myst, or when storing a secret or generating a key.

We note that it is up to the operator to decide the parameters of each quorum (i.e., size k, ICs participating), and provide the AC lists to the ICs. This is a critical procedure, as if one of the hosts turns out to be compromised, the quorum can be misused in order to either decrypt confidential ciphertexts or sign bogus statements. However, the secrets stored in the quorum will remain safe as there is no way for the adversary to extract them, unless they use physical-tampering (which our prototype (§5) is also resilient against). This is also true in the case where one of the authorized hosts gets compromised. For instance, a malware taking over a host can use Myst to sign documents, but it cannot under any circumstances extract any secrets.

## 3.2 Reliability Estimation

In the case of cryptographic hardware, in order for the operator to decide on the threshold k and the quorum composition, an estimation of the likelihood of hardware errors is needed. For this purpose we introduce k-tolerance, which given k foundries and an independent error probability, computes the probability that a quorum is secure.

$$Pr[secure] = 1 - Pr[error]^k$$

(1)

The quantification of the above parameters depends on the particular design and case, and as there is not commonly accepted way of evaluation, it largely depends on the information and testing capabilities each vendor has. For instance, hardware designers that use split manufacturing [27, 67, 92] can estimate the probability of a backdoored component using the *k-security* metric [46]. On the other hand, COTS vendors cannot easily estimate the probability

of a compromised component, as they are not always aware of the manufacturing technical details. Despite that, it is still possible for them to achieve very high levels of error and backdoor-tolerance by increasing the size of the quorums and sourcing ICs from distinct facilities (i.e., minimizing the collusion likelihood). It should be noted that as k grows the cost increases linearly, while the security exponentially towards one.

# 4 SECURE DISTRIBUTED COMPUTATIONS

In this section, we introduce a set of protocols that leverage the diversity of ICs in Myst to realize standard cryptographic operations manipulating sensitive keying material. More specifically, our cryptosystem comprises of a key generation operation (§4.1), the ElGamal encryption operation (§4.2), distributed ElGamal decryption (§4.3), and distributed signing based on Schnorr signatures (§4.5) [34, 35]. These operations are realized using interactive cryptographic protocols that rely on standard cryptographic assumptions. For operational purposes, we also introduce a key propagation protocol that enables secret sharing between non-overlapping quorums (§4.6).

Prior to the execution of any protocols, the ICs must be initialized with the domain parameters T = (p, a, b, G, n, h) of the elliptic curve to be used, where p is a prime specifying the finite field  $\mathbb{F}_p$ , a and b are the curve coefficients, G is the base point of the curve, with order n, and h is the curve's cofactor. More details on the technical aspects of the initialization procedure are provided in the provisioning Section 6.4.

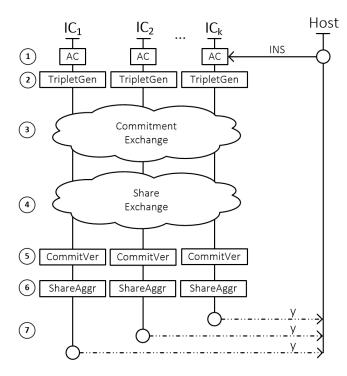

**Distributed Key Pair Generation.** The Distributed Key Pair Generation (DKPG) is a key building block for most other protocols. In a nutshell, DKPG enables a *quorum Q* of k ICs to collectively generate a random secret x, which is an element of a finite field and a public value  $Y_{agg} = x \cdot G$  for a given public elliptic curve point G. At the end of the DKPG protocol, each player holds a share of the secret x, denoted as  $x_i$  and the public value  $Y_{agg}$ . All steps of the protocol are illustrated in Figure 2, and explained in turn below.

The execution of the protocol is triggered when an authorized host sends the corresponding instruction ( $\mathbf{0}$ ). At the first step of the protocol, each member of Q runs Algorithm 4.1 and generates a triplet consisting of: 1) a share  $x_i$ , which is a randomly sampled element from  $\mathbb{Z}_n$ , 2) an elliptic curve point  $Y_i$ , and 3) a commitment to  $Y_i$  denoted  $h_i$ . ( $\mathbf{0}$ )

**Algorithm 4.1:** TripletGen: Generation of a pair and its commitment.

```

Input: The domain parameters \lambda

Output: A key triplet (x_i, Y_i, h_i)

1 x_i \leftarrow \text{Rand}(\lambda)

2 Y_i \leftarrow x_i \cdot G

3 h_i \leftarrow \text{Hash}(Y_i)

4 return (x_i, Y_i, h_i)

```

Upon the generation of the triplet, the members perform a pairwise exchange of their commitments ( $\odot$ ), by the end of which, they all hold a set  $H = \{h_1, h_2, ..., h_t\}$ . The commitment exchange terminates when  $|H_q| = t \ \forall q \in Q$ . Another round of exchanges then

Figure 2: The interaction between the different participants during the execution of the Distributed Key Pair Generation (DKPG) protocol.

starts, this time for the shares of  $Y_{agg}$  (①)  $Y = \{Y_1, Y_2, ..., Y_t\}$ . The commitment exchange round is of uttermost importance as it forces the participants to commit to a share of  $Y_{agg}$ , before receiving the shares of others. This prevents attacks where an adversary first collects the shares of others, and then crafts its share so as to bias the final pair, towards a secret key they know.

```

Algorithm 4.2: CommitVerify: Checks Y_i, against their respective commitments.

```

```

Input :(Y, H)

Output:Bool

1 for i \in \{1, |Y|\} do

2 | if Hash(Y_i) \neq h_i then

3 | return False

4 | return True

```

Once each member of the quorum receives k shares (i.e., |Y| = k), it executes Algorithm 4.2 to verify the validity of Y's elements against their commitments in H. (**6**) If one or more commitments fail the verification then the member infers that an error (either intentional or unintentional) occurred and the protocol is terminated. Otherwise, if all commitments are successfully verified, then the member executes Algorithm 4.3 (**6**) and returns the result to the remote host (**7**). Note that it is important to return  $Y_{agg}$ , as well as the individual shares  $Y_i$ , as this protects against integrity attacks, where malicious ICs return a different share than the one they committed to during the protocol [40, 62]. Moreover, since  $Y_i$

are shares of the public key, they are also assumed to be public, and available to any untrusted party.

```

Algorithm 4.3: ShareAggr: Aggregates elements in a set of shares (e.g., ECPoints, field elements).

```

```

Input : Set of shares Q

Output: The aggregate of the shares q

1 q \leftarrow 0

2 for q_i \in Q do

3 | q \leftarrow q + q_i

4 return q

```

In the following sections, we rely on DKPG as a building block of more complex operations.

# 4.1 Distributed Public Key Generation

The distributed key generation operation enables multiple ICs to collectively generate a shared public and private key pair with shares distributed between all participating ICs. This is important in the presence of hardware trojans, as a single IC never gains access to the full private key at any point, while the integrity and secrecy of the pair is protected against maliciously crafted shares.

We opt for a scheme that offers the maximum level of confidentiality (t-of-t, k = t), and whose execution is identical to DKPG seen in Figure 2. However, there are numerous protocols that allow for different thresholds, such as Pedersen's VSS scheme [40, 62, 79]. The importance of the security threshold is discussed in more detail in Section 6.3.

Once a key pair has been generated, the remote host can encrypt a plaintext using the public key Y, request the decryption of a ciphertext, or ask for a plaintext to be signed. In the following sections we will outline the protocols that realize these operations.

## 4.2 Encryption

For encryption, we use the Elliptic Curve ElGamal scheme [23, 34] (Algorithm 4.4). This operation does not use the secret key, and can be performed directly on the host, or remotely by any party holding the public key, hence there is no need to perform it in a distributed manner.

**Algorithm 4.4:** Encrypts a plaintext using the agreed common public key.

```

Input : The domain parameters T, the plaintext m encoded as an element of the group \mathbb{G}, and the calculated public key Y_{agg}

Output: The Elgamal ciphertext tuple, (C_1, C_2)

1 r \leftarrow Rand(T)

2 C_1 \leftarrow r \cdot G

3 C_2 \leftarrow m + r \cdot Y_{agg}

4 return (C_1, C_2)

```

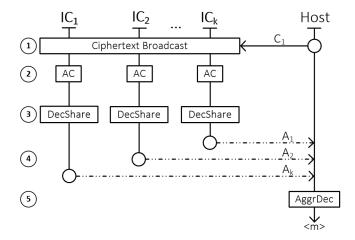

Figure 3: The interaction between the different ICs during the execution of the distributed decryption protocol.

# 4.3 Decryption

One of the fundamental cryptographic operations involving a private key is ciphertext decryption. In settings, where the key is held by a single authority, the decryption process is straightforward, but assumes that the hardware used to perform the decryption does not leak the secret decryption key. Myst addresses this problem by distributing the decryption process between *k* distinct processing ICs that hold shares of the key (Figure 3).

The protocol runs as follows: Initially, the host broadcasts the decryption instruction along with the part of the ciphertext  $C_1$  to the processing ICs ( $\P$ ). Upon reception, the ICs first verify that the request is signed by an authorized user ( $\P$ ), and then execute Algorithm 4.5 to generate their decryption shares  $A_i$  ( $\P$ ). Once the shares are generated they are sent back to the host, signed by the ICs and encrypted under the host's public key ( $\P$ ). Once the host receives k decryption shares, executes Algorithm 4.6 to combine them and retrieve the plaintext ( $\P$ ).

**Algorithm 4.5:** DecShare: Returns the decryption share for a given ciphertext.

**Input** :A part of the Elgamal ciphertext  $(C_1)$  and the IC's private key of  $x_i$ .

**Output:** The decryption share  $A_i$ , where i is the IC's uid

- $1 A_i \leftarrow -x_i \cdot C_1$

- 2 return  $A_i$

It should be noted that during the decryption process, the plaintext is not revealed to any other party except the host, and neither the secret key nor its shares ever leave the honest ICs. An extension to the above protocol can also prevent malicious ICs from returning arbitrary decryption shares, by incorporating a non-interactive zero knowledge proof [20] in the operation output. **Algorithm 4.6:** AggrDec:Combines the decryption shares and returns the plaintext for a given ciphertext.

**Input**: The Elgamal ciphertext  $C_2$  and the set of decryption shares A.

**Output:** The plaintext *m*

- 1  $D \leftarrow 0$

- 2 for  $A_i \in A$  do

- $3 \mid D \leftarrow D + A_i$

- 4  $m \leftarrow (C_2 + D)$

- 5 return m

### 4.4 Random Number Generation

Another important application of secure hardware is the generation of a random fixed-length bit-strings in the presence of active adversaries. The key property of such systems is that errors (e.g., a hardware backdoor), should not allow an adversary to bias the generated bitstring.

The implementation of such an operation is straightforward. The remote host submits a request for randomness to all actors participating in the quorum. Subsequently, each actor independently generates a random share  $b_i$ , encrypts it with the public key of the host, and signs the ciphertext with its private key. Once the host receives all the shares, he combines them to retrieve the b and then uses an one way function (e.g., SHA3-512 [16]) to convert it to a fixed length string.

# 4.5 Signing

Apart from key generation, encryption and decryption, Myst also supports distributed signing – an operation that potentially manipulates a long term signature key. Here we introduce a novel multi-signature scheme, based on Schnorr signature [71].

A multi-signature scheme allows a group of signers to distributively compute a signature on a common message. There has been a very long line of works on multi-signature schemes [13, 21, 53, 55, 56, 60] featuring several security properties (e.g. accountability, subgroup-signing) and achieving various efficiency trade-offs. A significant portion of work has been dedicated in reducing the trust in the key generation process. However, this often involves the use of expensive primitives or increases the interaction between parties [21, 53, 55]. In our construction, we rely on Myst's DKPG for the key generation process.

Our multi-signature scheme is based on Schnorr signatures [71] and has similarities with Bellare and Neven [13] construction. One crucial difference between existing multi-signature schemes and ours, is that we utilize a host intermediating between signers (i.e., ICs). This intermediating host allows us to eliminate any interaction between the ICs and thus improve the efficiency of the construction. To further minimise the interaction between the host and ICs we adapt existing techniques used in proactive two-party signatures [59] into the multi-signature context.

We let  $PRF_s(j)$  be a pseudorandom function with key s, that takes j as input and instantiates it as Hash(s||j).

Initially, all k ICs cooperate to generate a public key y using the distributed key generation operation (Section 4.1), and store securely their own key share  $x_i$ . Moreover, each IC generates a

**Algorithm 4.7:** SigShare: Returns the signature share of the IC for a given plaintext and index *j*.

**Input** : The digest of the plaintext to be signed H(m), the IC's private key of  $x_i$  and secret s, an index j, and the aggregated random EC point  $R_j$ .

**Output:** The signature share tuple  $(\sigma_{ij}, \epsilon_i)$

- $1 \epsilon_j \leftarrow Hash(R_j||Hash(m)||j)$

- $r_{ij} \leftarrow PRF_s(j)$

- $3 \sigma_{ij} \leftarrow r_{ij} x_i \cdot \epsilon_j \mod n$

- 4 return  $(\sigma_{ij}, \epsilon_j)$

secret *s* for the PRF, and stores it securely. After these steps, the signing protocol can be executed. The protocol comprises of two phases: *caching* and *signing*.

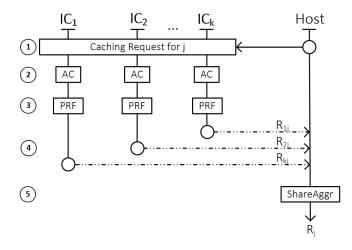

In the caching phase (Figure 4), the host queries the ICs for random group elements  $R_{ij}$ , where i is the id of the IC and j an increasing request counter (1). Once such a request is received, the IC verifies that the host is authorized to submit such a request and then applies the keyed pseudorandom function on the index jto compute  $r_{i,j} = PRF_s(j)$  (2). The IC then uses  $r_{i,j}$  to generate a group element (EC Point)  $R_{ij} = r_{i,j} \cdot G$  (3), which is then returned to the host. Subsequently, the host uses Algorithm 4.3 to compute the aggregate  $(R_i)$  of the group elements (Algorithm 4.3) received from the ICs for a particular j, and stores it for future use ( $\Phi$ ). It should be noted that the storage cost for  $R_i$  is negligible: for each round the host stores only 65 Bytes or 129 Bytes depending on the elliptic curve used (for  $R_i$ ) and the corresponding round index i. This allows the host to run the caching phase multiple times in parallel, and generate a list of random elements that can be later used, thus speeding up the signing process.

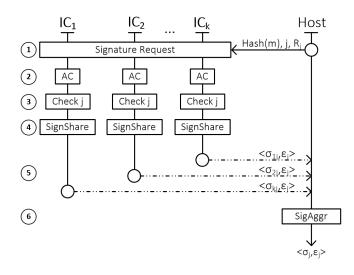

The signing phase (Figure 5) starts with the host sending a Sign request to all ICs (**①**). Such a request includes the hash of the plaintext Hash(m), the index of the round j, and the random group element  $R_j$  corresponding to the round. Each IC then first verifies that the host has the authorization to submit queries (**②**) and that the specific j has not been already used (**③**). The latter check on j is to prevent attacks that aim to either leak the private key or to allow the adversary to craft new signatures from existing ones. If these checks are successful, the IC executes Algorithm 4.7 and generates its signature share (**④**). The signature share ( $\sigma_{i,j}$ ,  $\varepsilon_{j}$ ) is then sent to the host (**⑤**). Once the host has collected all the shares for the same j, can use Algorithm 4.3 on all the  $\sigma_{i,j}$  to recover  $\sigma_{j}$ , obtaining the aggregate signature ( $\sigma_{j}$ ,  $\varepsilon_{j}$ ) (**⑥**).

The recipient of  $\langle (m, j), \sigma, \epsilon \rangle$  can verify the validity of the signature by checking if  $\epsilon = Hash(R||Hash(m)||j)$ , where  $R = \sigma \cdot G + \epsilon \cdot Y$ .

**Security Analysis.** The security of a multi-signature scheme requires that if at least one of the signers behaves honestly, then it is impossible to forge a multi-signature. In our context, the presence of a single honest IC guarantees the signature cannot be forged even in presence of a malicious host controlling all the remaining ICs. The key generation process is a crucial step for the security of multi-signature schemes due to the so called *rogue-key attacks* [13]. The latter enables an attacker to maliciously generate shares of the public key in such a way that is possible for her to forge multi-signatures. In Myst's DKPG process, malicious ICs cannot subvert

Figure 4: The interaction between the different players during the caching phase of the distributed signing protocol.

Figure 5: The figure illustrates the interaction between the different players when signing.

the key generation process as long as at least one IC is not colluding with the others, thus preventing rogue-key attacks. The security of our multi-signature scheme is proved in Theorem 4.1 assuming the hardness of on the one-more discrete logarithm problem [12]. We refer to Appendix A for the security definitions of multi-signatures and the proof of the following Theorem.

Theorem 4.1. If there exists a  $(q_S, q_H, \epsilon)$ -forger  $\mathcal{F}$  for the multisignature scheme described in Figures 4 and 5 interacting in  $q_S = O(1)$  signature queries, making at most  $q_H$  Hash queries and succeeding with probability  $\epsilon$ , then there exists an algorithm  $\mathcal{A}$  that solves the  $(q_S + 1)$ -DL problem with probability at least

$$\delta \ge \frac{\epsilon^2}{q_H^{q_S+1}} - negl(\lambda)$$

# 4.6 Key Propagation

In cases where more than one quorum is available it is useful to enable them all to handle requests for the same public key. This is of particular importance for both the system's scalability and its availability, as we further discuss in Sections 6.2 and 6.4 respectively.

Once a quorum  $Q_1$  has generated its public key y, (Section 4.1) the operator can specify another quorum  $Q_2$  that is to be loaded with y. Each member  $q_i$  of  $Q_1$  then splits its secret  $x_i$  in  $|Q_2|$  shares and distributes them to the individual members of  $Q_2$ . To do that  $q_i$  follows the secret sharing method shown in Algorithm 4.8. However, any t-of-t secret sharing schemes proposed in the literature [19, 62, 73] would do.

**Algorithm 4.8:** SecretShare: Returns a vector of shares from a secret.

**Input**: The domain parameters T, a secret s which is to be shared, and the number of shares k.

**Output:** A vector of shares  $\vec{v}_s$

- **1 for** (i = 0 to k 2) **do**

- $\vec{v}_s[i] \leftarrow Rand(T)$

- $\mathbf{3} \ \vec{v}_s[k-1] \leftarrow (s-\vec{v}_s[1]-\vec{v}_s[2]-\ldots-\vec{v}_s[k-2])$

- 4 return  $\vec{v}_{s}$

Once each member of  $Q_2$  receives  $|Q_1|$  shares, which they then combine to retrieve their share of the secret corresponding to y. Each member of  $Q_2$  can retrieve its share by summing the incoming shares, modulo p (the prime provided in the domain parameters T). An additional benefit of such a scheme is that  $Q_1$  and  $Q_2$  may have different sizes.

It should be also noted that a naive approach of having each member of  $q_1$  send their share of x to a member of  $q_2$  is insecure, as malicious members from  $q_1$  and  $q_2$  can then collude to reconstruct the public key.

# 5 IMPLEMENTATION

In this section, we provide the implementation details of our Myst prototype. We first focus on the custom hardware we built, and outline its different components and capabilities. Thereafter, we discuss the development of the software for the untrusted ICs and the details of the remote host.

Figure 6: Overview of Myst's components.

# 5.1 Hardware Design & Implementation

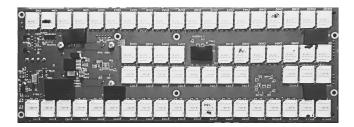

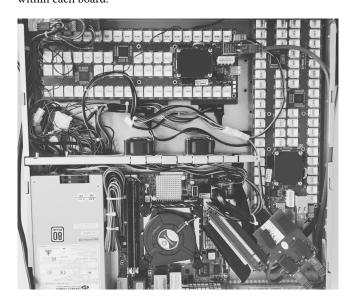

For our Myst prototype, we designed our own custom circuit board, which features 120 processing ICs (set to use 40 quorums of 3 smart-cards from different manufacturers) interconnected with dedicated buses with 1.2Mbps bandwidth.

Figure 7: Myst's smartcard board supports 120 ICs (60 on each side). Our configuration splits them in 40 quorums of 3 diverse ICs each.

The processing ICs are JavaCards (version 3.0.1), loaded with a custom applet implementing the protocols outlined in Section 4. JavaCards are an suitable platform as they provide good interoperability (i.e., applets are manufacturer-independent), which contributes to IC-diversification and prevents lock-in to particular vendors. Moreover, they also fulfill all the requirements listed in Section 2: (1) they are tamper-resistant (FIPS140-2 Level 4, CC EAL4) and can withstand attacks from adversaries with physical access to them [68], (2) they feature secure (FIPS140-2 compliant) on-card random number generators, (3) they offer cryptographic capabilities (e.g., Elliptic curve addition, multiplication) through a dedicated co-processor and (4) there are numerous independent fabrication facilities (Section 6). In addition to these, they have secure and persistent on-card storage space, ideal for storing key shares and protocol parameters.

The host is implemented using a computer that runs a python client application, which submits the user requests (e.g., Ciphertext Decryption) to Myst using a RESTful API exposed by the device. The incoming requests are handled by a Spring server, which parses them, converts them to a sequence of low-level instructions, and then forwards these to the IC controller, through an 1Gbps TCP/UDP interface. The ICs controller is a programmable Artix-7 FPGA that listens for incoming instructions and then routes them to the processing IC, through separate physical connections. We took special care that these buses offer a high bandwidth (over 400kbps), to prevent bottlenecks between controller and ICs even under extreme load. Once the ICs return the results, the controller communicates them back to the server, that subsequently forwards them to the host.

# 5.2 Software

We implement the protocols of Section 4 and provide the necessary methods for inter-component communication and system parameterization

We develop and load the processing ICs with JavaCard applets implementing methods for 1) Card Management, 2) Key Generation, 3) Decryption, and 4) Signing. Although JavaCard APIs since version 2.2.2 specifies a BigNumber class, this class is either unsupported by real cards or provides only too small internal type length (typically at most 8 bytes). The only third-party BigInteger library available (i.e., BigNat¹) is unmaintained and lacked essential operations. Moreover, low-level elliptic curve operations are only

$<sup>^{1}</sup>https://ovchip.cs.ru.nl/OV-chip\_2.0$

poorly supported by standard JavaCard API. The IC vendors often offer own proprietary APIs which provides the required operations (e.g., EC point addition) – but for the price of reduced portability. This made the implementation of our cryptographic schemes more complicated.

We extend BigNat to provide methods catering to our specific needs. Additionally, we develop own EC operations library based solely on public JavaCard API to support ICs where proprietary API is not available or cannot be used. Our EC library provides methods for EC point initialization, negation, addition, subtraction and scalar multiplication, and has been released as an independent project <sup>2</sup>.

Note, that although vendor's proprietary API limits the portability, it usually provides better performance and better protection against various side-channel attacks in comparison to custom software-only implementations. For this reason, we structured the IC applet code for easy incorporation of proprietary API with minimal code changes. Our EC library is thus used only when no other option is available for target IC.

Our current implementation is based on the NIST P-256 [1, 84] curve that provides at least 128 bits of security. However, it can also be trivially adapted for any other curve.

**Optimizations.** We optimize our JavaCard applet for speed and to limit side-channel attacks. Although JavaCard applets are compiled with standard Java compiler, common Java implementation patterns (e.g., frequent array reallocation due to resizing) are prohibitively expensive on JavaCards. Therefore, we use the following optimization techniques based on good practices and performance measurements from real, non-simulated, smart cards [81]:

- We use hardware accelerated cryptographic methods from JavaCard API instead of custom implementations interpreted by JavaCard virtual machine where possible.

- We store the session data in the faster RAM-allocated arrays instead of persistent, but slower EEPROM/Flash

- We use copy-free methods which minimize the move of data in memory, and also utilize native methods provided by JCSystem class for array manipulation like memory set, copy and erase.

- We made sure to pre-allocate all cryptographic engines and key objects during the applet installation. No further allocation during the rest of the applet lifetime is performed.

- Surplus cryptographic engines and key objects are used to minimize the number of key scheduling and initialization of engine with a particular key as these operations impose non-trivial overhead [81].

- We refrain from using single long-running commands which would cause other cards to wait for completion, thus increasing the latency of the final operation.

Finally, we optimized two fundamental operations commonly used in cryptographic protocols: 1) integer multiplication, and 2) the modulo operation optimized for 32 byte-long EC coordinates. This was necessary, as the straightforward implementation of these two algorithms in JavaCard bytecode is both slow and potentially vulnerable to side-channel timing attacks. Instead, we implemented

both operations so as to use the native RSA engine and thus have constant-time run-time.

The integer multiplication of a and b can be rewritten as  $a \cdot b = ((a+b)^2 - a^2 - b^2)/2$ . The squaring operation (e.g.,  $a^2$ ) can be quickly computed using a pre-prepared raw RSA engine with a public exponent equal to 2 and a modulus n, that is larger than the sum of the lengths of both operands. On the other hand, the integer modulo of two operands a (64 bytes long) and b (32 bytes long) is not so straighforward. We exploit the fact that b is always the order of the fixed point G in the P-256 Elliptic Curve [1, 84], and transform  $a \mod b = a - (((a \cdot x) \gg z) \cdot x)$  where x and z values are pre-computed offline [42]. As a result, a modulo operation can be transformed to two RSA operations, one shift (with z being multiple of 8) and one subtraction. Note that we cannot directly use RSA with a public exponent equal to 1 as operands are of different length and also shorter than smallest RSA length available on the card.

## 5.3 System States

Initially, the system is in an non-operational state, where the processing ICs do not respond to user requests. To make it operational, a secure initialization process has to be carried out. During the initialization the processing ICs and the other components described in 3 are loaded with verified application packages, and the domain parameters for the distributed protocols are set. Moreover, the ICs are provided with their certificates that they will later use to sign their packets and establish secure communication channels.

Once the initialization process has been completed, the system switches to an operational state and is available to serve user requests. Depending on the configuration, the system may be brought back to an uninitialized state, in order to load new software or change the protocol parameters. We further discuss the importance of the initialization process in Section 6.4.

## **6 EVALUATION**

In this section, we evaluate Myst by examining both its performance, and its qualitative properties.

**Experimental Setup.** All evaluations were performed using the setup illustrated in Figure 6. The host is a single machine with a CentOS 7 OS (3.10.0 Linux kernel), featuring a 3.00GHz Intel(R) Core i5-4590S CPU, 16GB of RAM, and uses a python client application to submit service requests to Myst, through a 1Gbps Ethernet interface (as described in Section 5). Upon reception, the server uses the Java Spring framework [49] to parse them, and then forward the instructions to the Artix-7 FPGA, which subsequently routes them to the individual smart cards. In all experiments, we collect response-time measurements from both the host and the Spring server. On average the round-trip from the host to the server takes 5ms. For accuracy, we use the host measurements in the rest of the section.

## 6.1 Performance Impact

This subsection evaluates the performance impact of Myst, and compares its throughput and latency with that of a single-IC system. Moreover, it examines the impact of our optimizations on the overall performance of the system.

<sup>&</sup>lt;sup>2</sup>https://OpenCryptoJC.org

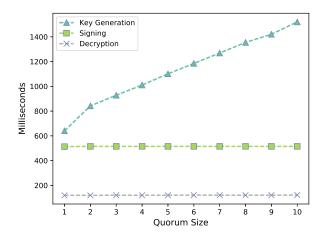

Figure 8: The average response time for each distributed operation of the cryptosystem, in relation to the quorum (i.e., a coalition of multiple ICs) size.

**Methodology.** To better understand the overhead that the use of a distributed architecture entails we run experiments that measure the latency as the size of the protocol quorum grows. We first submit 1,000 requests for each cryptosystem operation (Section 4) in one JavaCard and measure the response time. We then extend the experiment to larger quorums with sizes ranging from 2 to 10, and measure the latency in completing the same 1,000 operations. Simultaneously, to gain a more in-depth understanding of the impact that each low-level instruction type has, we micro-benchmark the response time for all intra-system communications.

Results. Figure 8 plots the average response time for performing Key Generation, Decryption and Signing using IC quorums of different sizes. To begin with, Decryption is the fastest (119ms), since it implements a single round protocol. Moreover, when we compare the runtime between the single-IC run, and the runs with multiple ICs, we observe that the latency is stable and the overhead remains always smaller than 0.8%. Hence, we conclude that the Decryption time does not increase with the size of the quorum, due to the ICs performing the decryption computations simultaneously. This highlights that Decryption is only CPU bound, and the network capacity of our prototype does not pose a bottleneck; and demonstrates that Myst can essentially provide increased assurance, with negligible impact on the decryption runtime. It should be noted that, high-throughput decryption is of extreme importance in applications such as secure key derivation in mix-network infrastructures [32] that heavily rely on decryption. Similarly, the runtime for signing remains the constant (~ 517ms) regardless of the quorum size. This is because our multi-sig signing protocol does not require one-to-one interaction between the ICs. The runtime difference between decryption and signing is mainly because of JavaCard API limitations. Specifically, we were forced to perform some of the mathematical operations for signing in the general purpose processor of the card, and not in the cryptographic coprocessor. The caching phase of the signing protocol (takes on average 169ms/operation) was performed offline for thousands of

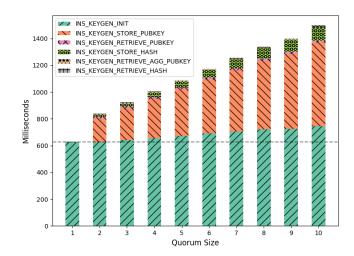

Figure 9: Breakdown of the runtime for low-level instructions that comprise the key generation operation, in relation to the quorum size. The horizontal reference line represent the cost of using a single IC.

indices j and is not considered in the measurements, as it is ran only occasionally.

As with signing and decryption, the runtime for random number generation is also constant, as the protocol is single round and can be executed in parallel.

On the other hand, Key Generation (DKPG) requires two phases (commitment and revelation) and this adds significant latency. In particular, as seen in Figure 8, each additional IC results in an runtime increase of approximately 90ms. Figure 9 examines the timings of low-level operations involved in the key generation protocols. When quorums are small the cost of key generation is dominated by the "INS\_KEYGEN\_INIT" operation that generates a secret share, and derives a public key (624ms). However, as the IC quorums grow the operations related to exchanging public keys ("INS\_KEYGEN\_STORE\_PUBKEY") and commitments ("INS\_KEYGEN\_STORE\_HASH") become significant, and for a quorum of 10 ICs, nearly doubles the cost of key generation. However, for quorums of 3 the impact on runtime is merely 303ms, compared to a single IC. Other low-level operations used in DKPG have negligible cost, regardless of the quorum size.

# 6.2 Scalability & Extensibility

This section examines how the throughput of our prototype grows as the more processing power (i.e., quorums) is added. The absence of bottlenecks in the system is important to be able to provide high-availability in production environments.

**Methodology.** To determine how efficiently our design scales in practice, we run a series of experiments that measure Myst's throughput, for varying numbers of processing quorums. As described in Section 5, our board supports up to 120 processing ICs which can be divided into multiple quorums and serve requests simultaneously. To benchmark the scalability of the system, on each iteration of the experiment we submit 10,000 requests for each

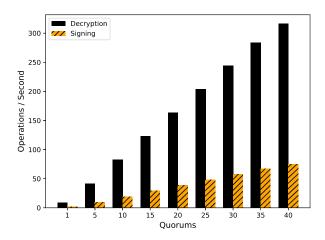

Figure 10: The average system throughput in relation to the number of quorums (k=3) that serve requests simultaneously. The higher is better.

high-level operation supported by our cryptosystem, and measure its throughput. However, this time we fix the quorum size k to 3, and on each iteration we increase the number of quorums serving the submitted requests by one, until we involve 40 quorums, which is the maximum number of 3-IC quorums that our prototype can support. For simplicity, we assign each processing IC to only one quorum. However, it is also technically possible for an IC to participate in more than one quorums, and store more than one secret shares.

Results. Figure 10 illustrates the throughput of the Myst system (in operations per second) as more of the ICs are used for processing transactions. The maximum throughput of Myst was 315ops/sec for Decryption and 77ops/sec for Signing, when using all 40 quorums. We also observe that as the number of quorums increases, the performance increases linearly, at a rate of ~ 9 requests per second per additional quorum for the Decryption operation, and ~ 1.9 requests per second for Signing. This illustrates that the system is CPU bound, and the communication fabric between ICs and the host is not a bottleneck. Consequently, a system with our proposed architecture can be easily tailored for different use cases to provide the throughput needed in each of them. It should be also noted that using a lower threshold k < t does not affect the performance of the system. However, this may result in some ICs being idle longer. For this purpose, it would be beneficial if ICs participated in more than one quorum, thus minimizing their idle time.

## 6.3 Tolerance levels

Myst is tolerant against both fabrication-time and design-time attacks (assuming independent foundries and design houses). Alternatively, if there is only one design house, then Myst protects against fabrication-time attacks only. In this section, we examine the relationship between the system parameters and the tolerance levels provided depending on the attack type (Table 1). The reported tolerance levels are those provided by the schemes outlined in Section 4,

| Parameters                | Leakage   | Denial-of-Service | IC Failures |

|---------------------------|-----------|-------------------|-------------|

| Single IC $k = t$ $k < t$ | 0         | 0                 | 0           |

| k = t                     | t-1 $k-1$ | 0                 | n-1         |

| <i>k</i> < <i>t</i>       | k-1       | t - k             | (t-k)*n     |

Table 1: Number of malicious/faulty ICs that different setups can tolerate in each abnormal scenario. The system is assumed to feature n identical quorums of size t, with a secret-sharing threshold k.

and were also empirically verified using our prototype introduced in Section 5.

In practice, the threshold k and the size of the quorums t express the trade-off between confidentiality and robustness for each particular quorum. The relationship between these two parameters determines how many ICs can cease to function, before the quorum fails: When k equals the number of processing ICs t, then secrets are safe in the presence of t - 1 compromised and colluding ICs. On the other hand, a more "relaxed" threshold (k < t) enables the quorum to remain fully functional unless more than t - k ICs fail (maliciously or through wear). Alternatively, (k = t)-systems can withstand multiple ICs failing (due to wear) using the technique introduced in Section 4.6. This technique enables several quorums to handle requests for the same public key, and thus even if multiple ICs (and consequently the quorums they belong to) fail, the remaining quorums can still handle incoming requests for those public keys. It should be noted that this technique provides robustness only in the presence of faulty & defective ICs, but does not mitigate denial of service attacks. This is because, all *n* quorums are identical (same manufacturer diversity) and thus a malicious IC from a breached supply chain will participate in all quorums. In contrast, defective ICs will fail with a probability less than 1 (post-fabrication tests detect always failing ICs) and thus several quorums will remain functional.

From all the above, the security guarantees offered by Myst are determined by the threshold k, the IC diversity and the number of quorums. In our prototype, we chose to maximize confidentiality, and resist the presence of t-1 actively malicious ICs. Malicious ICs launching denial-of-service attacks are easier to detect and replace, compared to those subtly leaking secrets or weakening keys. In cases where increased robustness and availability are paramount, the security level can be adjusted in favor of redundancy using the appropriate threshold schemes [62].

#### 6.4 Other Considerations

In this section, we consider several qualitative properties commonly used in the industry.

Physical Security & Diversity. SmartCards forms the core of our prototype and have multiple benefits as they were designed to operate in a hostile environment that is assumed to be fully controlled by the adversary [68]. For this reason, they come with very-high tamper-resistance (FIPS140-2, Level 4) and secure storage capabilities, that are constantly evolving. Another benefit is that there are several manufacturers owning foundries including

NXP-semiconductors, ST Microelectronics, Samsung, Infineon and Athena. Moreover, there are numerous independent facilities used by different vendors to fabricate their ICs [29, 72, 78, 83], which also contributes to the necessary diversity for the quorums.

Code & Parameter Provisioning. Crucial component of the security of Myst. If the code on all the ICs, or the cryptographic parameters contain errors, then the security of the system is not guaranteed. We propose two strategies to ensure secure provisioning. First, we may assume that provisioning occurs at the factory. This leverages our assumption that some of the factories are honest, and ensures that an adversary would have to compromise all fabrication facilities to extract any secrets. The second strategy is to assume the existence of a trusted off-line provisioning facility that is not under the control of an adversary. This facility needs only to guarantee high-integrity, as no secrets are involved in the provisioning step (secrets are generated within the ICs as part of protocols executed later).

Formal Security Validations. Any off-premise use of ICs raises a question of trust. To address this problem, independent security validations (e.g., FIPS140-2, or Common Criteria) have been introduced. These validations are performed by a third party, which verifies the claims of hardware vendors. However, these validations are a serious bottleneck when introducing new IC design. Myst does not need to go through this process as it executes provably secure cryptographic schemes on already validated ICs. As a result, even if one of the ICs has passed an independent validation, the whole instance of the Myst carries this assurance.

Real-world Practicality. Myst provides a platform for generating legally binding digital signatures (eIDAS [28]) under the sole control of the user. Moreover, due to the tamper-resistance properties of SmartCards, ICs can be also stored remotely thus making Myst a highly practical system that is able to support some non-typical real-world use-cases. For instance, Myst can perform code-signing of mobile applications for apps stores (e.g., AppStore or Google Play), by sharing the signing keys between developers' laptops, managers' computers, and securely stored ICs providing protection against internal enterprise/company attackers without compromising developers' control over the signing process. Finally, another practical feature of Myst is that each party maintains its own independent audit logs, thus ensuring non-repudiation.

### 7 RELATED WORK

This section examines existing literature on hardware trojans and countermeasures, outlines relevant fault-tolerant designs and architectures, and discusses how Myst compares to prior works.

Hardware Trojans & Countermeasures. To better understand the extend of the Hardware Trojans threat, numerous attacks and exploitation techniques have been proposed in the literature in the last decade. For instance, the authors in [51] design two hardware trojans and implement a proof-of-concept attack against the PRINCE cipher [22]. The novelty of their attacks is that they use dopant polarity changes (first introduced in [10]), to create a hard-to-detect fault-injection attack backdoor. Moreover, [63] also introduces a hardware trojan attacking RSA applications. In this attack, the adversary is able to use power supply fluctuations to trigger the trojan,

which then leaks bits of the key through a signature. Another very hard to detect class of trojans (inserted by fabrication-time attackers) was introduced by K Yang et al. in [96]. Such trojans leverage analog circuits and require only a single logic gate to launch their attack (e.g., switch the CPU's mode). Apart from these, detection evasion and stealthy triggering techniques have been proposed in [17, 52, 89–91].

As discussed in Section 1, malicious components carrying errors have been also observed in commercial and military hardware [2, 38, 48, 54, 57, 74–76], while a subset of those incidents also involved misbehaving cryptographic hardware [41, 43, 69, 70]. In all these cases, the errors were eventually attributed to honest design or fabrication mistakes, but the systems were left vulnerable to attacks regardless. For instance, one popular and well-studied example of attacks against weak cryptographic hardware is [15]. In this work, Bernstein et al. study the random number generators used in smartcards and found various malfunctioning pieces, that allowed them to break 184 public keys using in "Citizen Digital Certificates" by Taiwanese citizens.

To address the aforementioned threats, different approaches have been proposed. The most common ones attempt to either detect malicious circuitry, or prevent insertions. In particular, detection techniques aim to determine whether any HTs exist in a given circuit and feature a wide range of methods such as side-channel analysis [3, 77, 93, 95], logic testing [25], and trust verification [7, 66, 88, 100]. On the other hand, prevention techniques aim to either impede the introduction of HTs, or make HT easier to detect, such approaches are Split manufacturing [27, 67, 92] which tries to minimize the circuit/design exposure to the adversary, logic obfuscation [24] and runtime monitoring [45, 86]

Moreover, there is also a smaller body of work which attempts to tackle the even harder problem of inferring additional information about the HT such as its triggers, payload, and exact location [93, 95]. On top of the above works, there are also verifiable computation architecures (such as [85]), which provide guarantees for the correctness of the computation on untrusted platforms. However, they come with a computation overhead and do not guarantee secure handling of secrets or protection from side-channel attacks.

Myst follows an alternative approach that leverages a diverse set of untrusted ICs to minimize the risk of compromises by distributing trust between them. For this reason, all the above countermeasures remain applicable and would even increase the security of the final system. In other words, our proposed approach is not an alternative to existing techniques, as it provides a way to combine ICs fabricated by different manufacturers, in various locations and featuring a wide-range of protection techniques in one system.

**Fault-Tolerant Systems.** Component-redundancy and component-diversification are both key concepts used in N-variant systems that aim to achieve high fault-tolerance [26]. An example of such a system is the Triple-Triple Redundant 777 Primary Flight Computer [98, 99], that replicates the computations in three processors and then performs a majority voting to determine the final result. The applications of N-variance in security scenarios has been studied in only few works aiming to protect systems against software attacks. In particular, [31] introduces a method to generate randomized system copies, that will have disjoint

exploitation sets, thus achieving memory safety. On the other hand, [4] proposes a N-variant method for IC diversification, aiming again to achieve disjoint exploitation sets. However, this method is not effective against fabrication-time attacks and protects only against (potentially exploitable) unintentional errors. Finally, heterogeneous architectures with COTS components have been also proposed in [8, 9]. However, the practicality of these works is very limited as the computations are simply replicated between the different components, thus not protecting against confidentiality attacks.

# 8 CONCLUSION

High-assurance cryptographic hardware, such as hardware security modules, is used in production under the assumption that its individual components are secure and free from errors. However, even though post-fabrication testing is capable of detecting defective ICs with high-accuracy, there are certain error classes that are hard to uncover (e.g., RNG defects). Unfortunately, these errors are also detrimental to the security of high-assurance hardware such as hardware security modules. Moreover, hardware trojans and malicious circuitry have been extensively studied, and there is an abundance of designs, mitigation techniques and countermeasure evasion methods. This line of work assumes that not all errors can be detected and that due to the arms race, between trojan horses and mitigation techniques, countermeasures will never be 100% effective against all possible threats.

To resolve this, we introduce Myst, which brings the adversary into the unfavorable position of having to compromise 100% of the hardware components to gain any advantage. By employing threshold schemes and a redundancy-based architecture, Myst is able to distribute both secrets and cryptographic computations among multiple, diverse integrated circuits. Consequently, an adversary aiming to breach the confidentiality or the integrity of the system, must be able to compromise all the ICs. This is not a trivial task when the ICs are manufactured from different vendors, in different premises. To evaluate Myst, we build a custom board featuring 120 Smart Cards controlled by an Artix-7 FPGA. The maximum throughput for distributed decryption is 315ops/sec, while for signing is 77ops/sec. Both come with an overhead of less than < 1% compared to a typical single-point of failure system. All in all, our results show that Myst is highly scalable, and provides strong guarantees for the security of the system thus making it suitable for production.

## 9 ACKNOWLEDGEMENTS

This work was supported by the European Commission through the H2020-DS-2014-653497 PANORAMIX project and the European Research Council via the European Union's Seventh Framework Programme (FP/2007-2013) / ERC Grant Agreement n. 307937, and the Czech Science Foundation under project GA16-08565S.

### **REFERENCES**

- [1] Mehmet Adalier. 2015. Efficient and Secure Elliptic Curve Cryptography Implementation of Curve P-256. (2015).

- [2] Sally Adee. 2008. The hunt for the kill switch. IEEE Spectrum 45, 5 (2008), 34-39.

- [3] Dakshi Agrawal, Selcuk Baktir, Deniz Karakoyunlu, Pankaj Rohatgi, and Berk Sunar. 2007. Trojan detection using IC fingerprinting. In Security and Privacy, 2007. SP'07. IEEE Symposium on. IEEE, 296–310.

- [4] Yousra Alkabani and Farinaz Koushanfar. 2008. N-variant IC design: methodology and applications. In Proceedings of the 45th Design Automation Conference, DAC 2008, Anaheim, CA, USA, June 8-13, 2008. 546-551. https://doi.org/10.1145/1391469. 1391606

- [5] Jacob Appelbaum, Judith Horchert, and Christian Stöcker. 2013. Shopping for spy gear: Catalog advertises NSA toolbox. Der Spiegel 29 (2013).

- [6] Michael Backes, Markus Dürmuth, and Dominique Unruh. 2008. Compromising reflections-or-how to read LCD monitors around the corner. In Security and Privacy, 2008. SP 2008. IEEE Symposium on. IEEE, 158–169.

- [7] Chongxi Bao, Yang Xie, and Ankur Srivastava. 2015. A security-aware design scheme for better hardware Trojan detection sensitivity. In IEEE International Symposium on Hardware Oriented Security and Trust, HOST 2015, Washington, DC, USA, 5-7 May, 2015. 52–55. https://doi.org/10.1109/HST.2015.7140236

- [8] Mark Beaumont, Bradley Hopkins, and Tristan Newby. 2012. Safer path: Security architecture using fragmented execution and replication for protection against trojaned hardware. In Proceedings of the Conference on Design, Automation and Test in Europe. EDA Consortium, 1000–1005.

- [9] Mark Beaumont, Bradley Hopkins, and Tristan Newby. 2013. Hardware trojan resistant computation using heterogeneous COTS processors. In Proceedings of the Thirty-Sixth Australasian Computer Science Conference-Volume 135. Australian Computer Society, Inc., 97–106.

- [10] Georg T Becker, Francesco Regazzoni, Christof Paar, and Wayne P Burleson. 2013. Stealthy dopant-level hardware trojans. In *International Workshop on Cryptographic Hardware and Embedded Systems*. Springer, 197–214.

- [11] Georg T. Becker, Francesco Regazzoni, Christof Paar, and Wayne P. Burleson. 2014. Stealthy dopant-level hardware Trojans: extended version. J. Cryptographic Engineering 4, 1 (2014), 19–31. https://doi.org/10.1007/s13389-013-0068-0

- [12] Mihir Bellare, Chanathip Namprempre, David Pointcheval, and Michael Semanko. 2003. The One-More-RSA-Inversion Problems and the Security of Chaum's Blind Signature Scheme. J. Cryptology 16, 3 (2003), 185–215.

- [13] Mihir Bellare and Gregory Neven. 2006. Multi-signatures in the plain public-Key model and a general forking lemma. 390–399.

- [14] Mihir Bellare and Phillip Rogaway. 1993. Random Oracles are Practical: A Paradigm for Designing Efficient Protocols. In CCS '93, Proceedings of the 1st ACM Conference on Computer and Communications Security, Fairfax, Virginia, USA, November 3-5, 1993, 62–73.

- [15] Daniel J Bernstein, Yun-An Chang, Chen-Mou Cheng, Li-Ping Chou, Nadia Heninger, Tanja Lange, and Nicko Van Someren. 2013. Factoring RSA keys from certified smart cards: Coppersmith in the wild. In International Conference on the Theory and Application of Cryptology and Information Security. Springer, 341–360.

- [16] Guido Bertoni, Joan Daemen, Michaël Peeters, and Gilles Van Assche. 2009. Keccak sponge function family main document. Submission to NIST (Round 2) 3 (2009), 30.

- [17] Swarup Bhunia, Michael S. Hsiao, Mainak Banga, and Seetharam Narasimhan. 2014. Hardware Trojan Attacks: Threat Analysis and Countermeasures. Proc. IEEE 102, 8 (2014), 1229–1247. https://doi.org/10.1109/JPROC.2014.2334493

- [18] Swarup Bhunia, Michael S Hsiao, Mainak Banga, and Seetharam Narasimhan. 2014. Hardware Trojan attacks: threat analysis and countermeasures. Proc. IEEE 102, 8 (2014), 1229–1247.

- [19] George Robert Blakley. 1979. Safeguarding cryptographic keys. Proc. of the National Computer Conference 1979 48 (1979), 313–317.

- [20] Manuel Blum, Paul Feldman, and Silvio Micali. 1988. Non-interactive zero-knowledge and its applications. In Proceedings of the twentieth annual ACM symposium on Theory of computing. ACM, 103–112.

- [21] Alexandra Boldyreva. 2003. Threshold Signatures, Multisignatures and Blind Signatures Based on the Gap-Diffie-Hellman-Group Signature Scheme. In Public Key Cryptography - PKC 2003. 31–46.

- [22] Julia Borghoff, Anne Canteaut, Tim Güneysu, Elif Bilge Kavun, Miroslav Knezevic, Lars R Knudsen, Gregor Leander, Ventzislav Nikov, Christof Paar, Christian Rechberger, et al. 2012. PRINCE-a low-latency block cipher for pervasive computing applications. In International Conference on the Theory and Application of Cryptology and Information Security. Springer, 208–225.

- [23] Felix Brandt. 2005. Efficient Cryptographic Protocol Design Based on Distributed El Gamal Encryption. In Information Security and Cryptology - ICISC 2005, 8th International Conference, Seoul, Korea, December 1-2, 2005, Revised Selected Papers (Lecture Notes in Computer Science), Dongho Won and Seungjoo Kim (Eds.), Vol. 3935. Springer, 32–47. https://doi.org/10.1007/11734727\_5

- [24] Rajat Subhra Chakraborty and Swarup Bhunia. 2009. Security against hardware Trojan through a novel application of design obfuscation. In Proceedings of the 2009 International Conference on Computer-Aided Design. ACM, 113–116.

- [25] Rajat Subhra Chakraborty, Francis G. Wolff, Somnath Paul, Christos A. Papachristou, and Swarup Bhunia. 2009. MERO: A Statistical Approach for Hardware Trojan Detection. In Cryptographic Hardware and Embedded Systems CHES 2009, 11th International Workshop, Lausanne, Switzerland, September 6-9, 2009, Proceedings. 396–410. https://doi.org/10.1007/978-3-642-04138-9\_28

- [26] Liming Chen and Algirdas Avizienis. 1978. N-version programming: A fault-tolerance approach to reliability of software operation. In Digest of Papers FTCS-8:

- Eighth Annual International Conference on Fault Tolerant Computing. 3-9.

- [27] Zhang Chen, Pingqiang Zhou, T. Y. Ho, and Y. Jin. 2016. How secure is split manufacturing in preventing hardware trojan?. In 2016 IEEE Asian Hardware-Oriented Security and Trust (AsianHOST). 1–6. https://doi.org/10.1109/AsianHOST. 2016.7835561

- [28] European Commission. 2016. Questions & Answers on Trust Services under eIDAS. https://ec.europa.eu/digital-single-market/en/news/questions-answers-trust-services-under-eidas. (February 2016).

- [29] Semiconductor Manufacturing International Corporation. 2017. Embedded Non-Volatile Memory for Smart Card & MCU. http://www.smics.com/eng/foundry/technology/tec\_envm.php. (May 2017).

- [30] Nicolas T Courtois. 2009. The dark side of security by obscurity and cloning Mifare Classic rail and building passes, anywhere, anytime. (2009).

- [31] Benjamin Cox and David Evans. 2006. N-Variant Systems: A Secret-less Framework for Security through Diversity. In Proceedings of the 15th USENIX Security Symposium, Vancouver, BC, Canada, July 31 August 4, 2006. https://www.usenix.org/conference/15th-usenix-security-symposium/n-variant-systems-secretless-framework-security-through

- [32] George Danezis, Claudia Diaz, and Paul Syverson. 2009. Systems for anonymous communication. Handbook of Financial Cryptography and Security, Cryptography and Network Security Series (2009), 341–389.

- [33] Don Edenfeld, Andrew B. Kahng, Mike Rodgers, and Yervant Zorian. 2004. 2003 Technology Roadmap for Semiconductors. *IEEE Computer* 37, 1 (2004), 47–56. https://doi.org/10.1109/MC.2004.1260725

- [34] Taher ElGamal. 1985. A public key cryptosystem and a signature scheme based on discrete logarithms. IEEE transactions on information theory 31, 4 (1985), 469–472

- [35] Amos Fiat and Adi Shamir. 1986. How to prove yourself: Practical solutions to identification and signature problems. In Conference on the Theory and Application of Cryptographic Techniques. Springer, 186–194.

- [36] Task Force. 2005. High Performance Microchip Supply. (2005).

- [37] Bastian Fredriksson. 2016. A case study in smartcard security Analysing Mifare Classic Rev. (2016).

- [38] Sean Gallagher. 2014. Photos of an NSA aăIJupgradeaăİ factory show Cisco router getting implant. Ars Technica 14 (2014).

- [39] Daniel Genkin, Adi Shamir, and Eran Tromer. 2014. RSA key extraction via low-bandwidth acoustic cryptanalysis. In *International Cryptology Conference*. Springer, 444–461.

- [40] Rosario Gennaro, Stanislaw Jarecki, Hugo Krawczyk, and Tal Rabin. 2007. Secure Distributed Key Generation for Discrete-Log Based Cryptosystems. J. Cryptology 20, 1 (2007), 51–83. https://doi.org/10.1007/s00145-006-0347-3

- [41] Dan Goodin. 2013. 'We cannot trustâĂİ Intel and ViaâĀŹs chip-based crypto', FreeBSD developers say. http://arstechnica.com/security/2013/12/wecannot-trust-intel-and-vias-chip-based-crypto-freebsd-developers-say/. (December 2013).

- [42] Torbjörn Granlund and Peter L Montgomery. 1994. Division by invariant integers using multiplication. In ACM SIGPLAN Notices, Vol. 29. ACM, 61–72.

- [43] FreeBSD Security Working Group. 2013. FreeBSD Developer Summit: Security Working Group. https://wiki.freebsd.org/201309DevSummit/Security. (December 2013).

- [44] Stefan Heck, Sri Kaza, and Dickon Pinner. 2011. Creating value in the semiconductor industry. McKinsey & Company (2011).