# Computationally Efficient Adaptive Spike Processor With Real-Time Decoding of Neural Signals for Implantable Applications

Majid Zamani

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

Of

University College London

Department of Electrical Engineering University College London

Supervisor: Prof. Andreas Demosthenous

February 2017

# **Declaration**

I herewith certify that all material in this dissertation which is not my own work has been properly acknowledged.

Majid Zamani

# Copyright

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work.

#### **Abstract**

Recent advances in the field of neuroscience have suggested that new generation brain computer interfaces demand a critical step in biomedical signal processing requiring *online/on-chip spike sorting*. Spike sorting is the process of grouping signals from an individual neuron by grouping action potentials (spikes) into a specific cluster based on the similarity of their shapes. The extraction of single-unit activity by sensors at a distance from specific neurons is necessary for a wide range of clinical applications such as disorder treatments, muscular stimulation (e.g., epidural spinal cord stimulation for treatment acceleration), cochlear implant and neural prostheses. A brain machine interface, for example, can potentially substitute the missing motor pathway/sensory information between the motor cortex and an artificial limb.

With the aim of developing an energy-efficient spike sorting chip for hardware implantable systems, this thesis introduces a new feature extraction method based on extrema analysis (positive and negative peaks) of spike shapes and their discrete derivatives. The proposed method runs in real-time and does not require any offline training. Compared to other methods it offers a better tradeoff between accuracy and computational complexity using online sorting. It additionally eliminates multiplications which are computationally expensive, power hungry and require appreciable silicon area.

A minimum power limit for implantable neural front-end interfaces is also derived. It involved: 1) system level optimization - the front-end specifications including the bandwidth, data converter resolution and sampling rate were defined by exploring the effect of the parameters on spike sorting via a standard spike bank; 2) block level optimization - The front-end power was minimized by using an opamp-less cyclic converter; and 3) estimating the power limit equation of the front-end. The new optimization methodology addresses the future demands of neural recording interfaces.

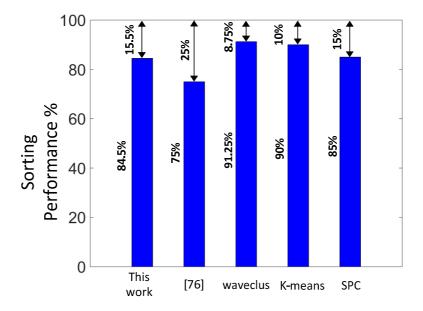

Finally the thesis presents the design, implementation and testing of the first generation of an adaptive spike sorting processor. It enhances the accuracy-power characteristics by employing self-calibration of processing features. The chip prototype was fabricated in a 180-nm CMOS technology. It achieves an overall clustering accuracy of 84.5% using a standard spike data bank and has a power consumption of 148-µW from 1.8-V supply voltage. The fabricated spike

processor has almost 10% higher clustering accuracy than the state-of-the-art. Measurements show good power-performance characteristics compared to the state-of-the-art online and offline clustering methods.

To my parents

### Acknowledgments

I would like to thank Prof. Andreas Demosthenous for his constant guidance, support, patience, and contribution throughout this work. It has been an honor to work with him on my Ph.D. dissertation during which I learned a lot from him both academically and professionally. He encouraged me to develop my own ideas with his positive spirit and great patience to find the direction towards the right path.

A special thanks goes to my second thesis advisor Dr. Miguel Rodriguez for his inspiring discussions which helped me to understand to successfully conduct my thesis. I am especially thankful to Prof. Nick Donaldson from the Implanted Devices Group at University College London for providing the recorded in-vivo neural data.

I would like to thank Dr. Dai Jiang for his support regarding chip tape-out and layout of the spike processor. I am grateful to Peter Langlois who provided a lot of input to my papers and thesis corrections. This project was financially supported by a Ph.D. scholarship from University College London (UCL) Graduate School.

Last, but not least, my deep gratitude goes to my beloved family for their love and encouragement and their continuous faithful support during all phases of my life. Their timeless and countless supports were always motivating during my education. Indeed, they have a big share to this achievement and I would like to express my deep appreciation.

# **Table of Contents**

| 1 Introduction                                            | 29 |

|-----------------------------------------------------------|----|

| 1.1 Motivation                                            | 29 |

| 1.2 Research Objectives                                   | 31 |

| 1.3 Outline of the Thesis                                 | 32 |

| 1.4 List of Publications                                  | 35 |

| 2 Background and State-of-the-Art                         | 36 |

| 2.1 Brain-Machine Interfaces (BMIs)                       | 36 |

| 2.1.1 Levels of Interfacing.                              | 37 |

| 2.1.2 Nature of Neurons and Action Potentials             | 39 |

| 2.2 Recorded Signal                                       | 42 |

| 2.3 Spike Sorting                                         | 43 |

| 2.3.1 Constraints in Hardware for Implantable Devices     | 43 |

| 2.3.2 State-of-the-Art Spike Sorting                      | 45 |

| 2.3.2.1 Off-chip Spike Sorting                            | 45 |

| 2.3.2.2 On-chip Spike Sorting                             | 47 |

| 2.3.2.3 Compression-based Spike Sorting Methods           | 50 |

| 2.4 Spike Sorting Testing Methodology                     | 51 |

| 2.4.1 Test Data                                           | 51 |

| 2.4.2 Accuracy Calculations                               | 53 |

| 2.5 Explanations of the Spike Sorting Operators           | 54 |

| 2.5.1 Spike Detection                                     | 55 |

| 2.5.1.1 Determination of the Threshold Using the Operator | •• |

| 2.5.1.2 Determination of the Threshold Using the Absolute Val                               | lue56 |

|---------------------------------------------------------------------------------------------|-------|

| 2.5.1.3 Stationary Wavelet Transform Product (SWTP)                                         | 57    |

| 2.5.2 Alignment                                                                             | 58    |

| 2.5.3 Feature Extraction                                                                    | 59    |

| 2.5.3.1 Principle Component Analysis (PCA)                                                  | 59    |

| 2.5.3.2 Discrete Wavelet Transform (DWT)                                                    | 59    |

| 2.5.3.3 Feature Set                                                                         | 61    |

| 2.5.3.4 Template Matching (TM)                                                              | 61    |

| 2.5.3.5 Zero Crossing Features (ZCF)                                                        | 62    |

| 2.5.4 Dimensionality Reduction                                                              | 63    |

| 2.5.5 Clustering                                                                            | 67    |

| 2.5.5.1 <i>k</i> -Means Clustering                                                          | 68    |

| 2.5.5.2 Artificial Neural Networks (ANN)                                                    | 69    |

| 2.5.5.3 SPC                                                                                 | 70    |

| 2.5.5.4 Online Sorting (O-Sort) Clustering                                                  | 71    |

| 2.6 Conclusion.                                                                             | 72    |

| New Feature Extraction Using Extrema Sampling of Discrete Derivative ting  3.1 Introduction | 73    |

|                                                                                             |       |

| 3.2 Algorithms.                                                                             |       |

| 3.2.1 Off-Chip Feature Extraction Methods                                                   |       |

| 3.2.2 Proposed Method for On-Chip Feature Extraction                                        |       |

| 3.2.3 Comparison with Other Feature Extraction Methods                                      |       |

| 3.2.4 Sorting (O-Sort Clustering)                                                           | 79    |

| 3.3 Results and Discussions.                                                                | 80    |

| 3.3.1 Determination of the Optimal Threshold                                                                                        | 80  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.3.2 Classification Accuracy                                                                                                       | 81  |

| 3.3.3 Clustering Results with Synthetic Data                                                                                        | 84  |

| 3.3.4 Clustering Results with Recorded In-Vivo Neural Data                                                                          | 87  |

| 3.3.5 Complexity Analysis                                                                                                           | 90  |

| 3.3.6 Proposed Data Reduction Application Example                                                                                   | 92  |

| 3.4 Conclusion.                                                                                                                     | 93  |

| 4 Design Techniques and Power Limit Analysis of Neural Front-end Interfactular Ultralow Power Implantable Devices  4.1 Introduction | 95  |

| 4.2 NFI Power Model                                                                                                                 | 98  |

| 4.2.1 LNA Power Analysis                                                                                                            | 99  |

| 4.2.2 Assigning Noise Multiplying Factor (NMF= $\alpha$ ) through Data Co Analysis                                                  |     |

| 4.2.3 Programmable Gain Amplifier (PGA)                                                                                             | 107 |

| 4.2.4 ADC Power Consumption                                                                                                         | 109 |

| 4.2.4.1 SAR ADC                                                                                                                     | 110 |

| 4.2.4.1.1 Dynamic Latch Comparator (DLC)                                                                                            | 110 |

| 4.2.4.1.2 SAR Register                                                                                                              | 113 |

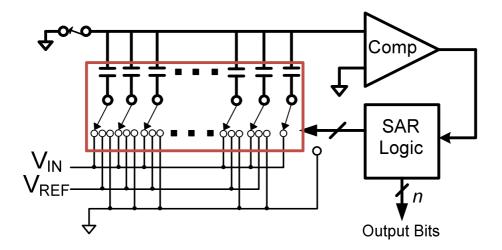

| 4.2.4.1.3 Binary Weighted Charge-Scaling DAC                                                                                        | 114 |

| 4.2.4.2 CBSC Cyclic ADC                                                                                                             | 115 |

| 4.2.4.2.1 Current Sources                                                                                                           | 116 |

| 4.2.4.2.2 Threshold Detection Comparator (TDC)                                                                                      | 118 |

| 4.3 MATLAB-FPGA Interfacing                                                                                                         | 121 |

| 131 Spike Sorting Processor                                                                                                         | 121 |

|      | 4.4 Validation Tests and Results                                                        | 124 |

|------|-----------------------------------------------------------------------------------------|-----|

|      | 4.4.1 Test Setup                                                                        | 124 |

|      | 4.4.2 Design Optimization.                                                              | 125 |

|      | 4.4.2.1 Defining Band-pass Response With Respect to Spike S<br>Performance              | _   |

|      | 4.4.2.2 Resolution and Sampling Rate Versus Spike Proc<br>Performance                   | _   |

|      | 4.4.3 NFI Power Bound                                                                   | 129 |

|      | 4.4.4 Towards the Parametric NFI Design                                                 | 131 |

|      | 4.5 Conclusion.                                                                         | 135 |

|      |                                                                                         |     |

| 5 Bi | iomedical Signal Processing Using Adaptive Techniques                                   | 136 |

|      | 5.1 Introduction                                                                        | 136 |

|      | 5.2 System-Level Illustration of Adaptive Spike Sorting                                 | 137 |

|      | 5.2.1 Development of Adaptive Frames for the Spike Sorting Application                  | 137 |

|      | 5.2.2 Transforming the Defined Adaptive Frames into Processing Units                    | 139 |

|      | 5.2.3 Overall System Discription                                                        | 139 |

|      | 5.3 Adaptive Spike Sorting Processor for Accuracy Self-tuning and Inherent Suppression. |     |

|      | 5.3.1 Detection and Alignment                                                           | 142 |

|      | 5.3.2 Adaptive Feature Extraction                                                       | 145 |

|      | 5.3.3 Feature Vector Monitoring                                                         | 149 |

|      | 5.3.4 Online Sorting (O-Sort)                                                           | 150 |

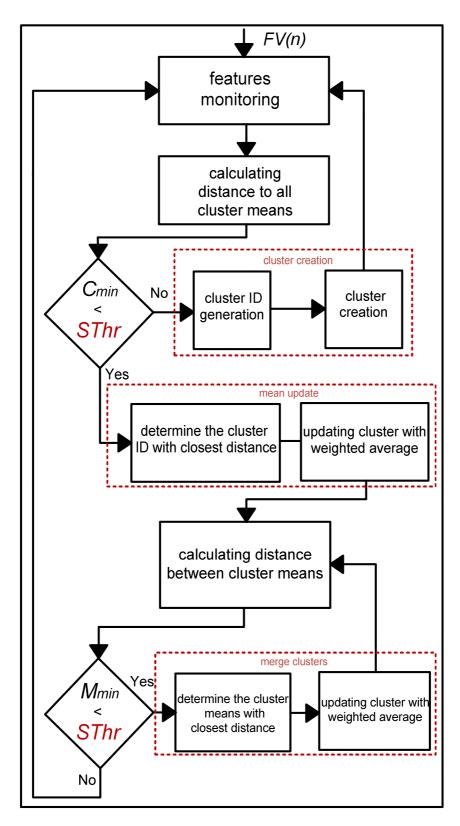

|      | 5.3.4.1 Unsupervised Clustering                                                         | 150 |

|      | 5.3.4.2 Clustering Operation Methodology                                                | 153 |

|      | 5.3.5 Training Unit Structure                                                           | 154 |

|     | 5.3.5.1 Training Memory Structure                        | 155 |

|-----|----------------------------------------------------------|-----|

|     | 5.3.5.2 Status Engine                                    | 157 |

|     | 5.3.5.3 Cluster Generation (ID Generator)                | 158 |

|     | 5.3.5.4 <i>l1</i> -norm Unit Structure                   | 159 |

|     | 5.3.5.5 Merging Unit Structure                           | 161 |

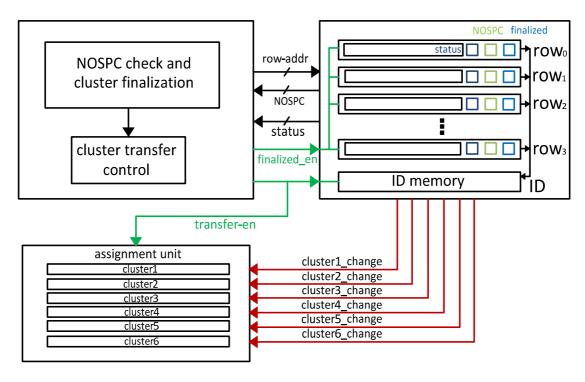

|     | 5.3.5.6 Finalized Cluster Means Transfer Unit            | 163 |

|     | 5.3.6 Assignment Unit                                    | 164 |

|     | 5.3.7 Performace Check Unit                              | 165 |

|     | 5.4 ASIC Implementation                                  | 167 |

|     | 5.4.1 FPGA-based ASIC Verification                       | 167 |

|     | 5.4.2 Chip Measurement Results                           | 169 |

|     | 5.4.3 Dynamic Test Methodology                           | 175 |

|     | 5.4.4 Comparison with Prior Works                        | 177 |

|     | 5.4.5 Interleaved Architecture                           | 179 |

|     | 5.4.6 Power Management Techniques                        | 180 |

|     | 5.4.7 Towards the Next Generation of Adaptive Processing | 181 |

|     | 5.4.7.1 Feature Extraction Development phases            | 181 |

|     | 5.4.7.2 Clustering Algorithm                             | 181 |

|     | 5.5 Conclusion                                           | 182 |

| 6 C | onclusion                                                | 185 |

|     | 6.1 Original Contributions                               | 185 |

|     | 6.2 Future Work                                          | 187 |

|     | 6.2.1 Multi-channel Processing                           | 187 |

|     | 6.2.2 Brain Activity Analysis                            | 187 |

# **List of Figures**

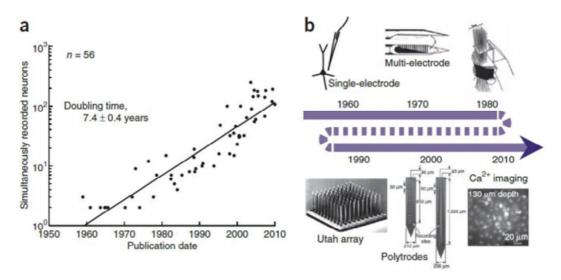

| 1.1: Examining 56 studies of neural recording systems published over the last five decades. (a)      |

|------------------------------------------------------------------------------------------------------|

| Number of simultaneously recorded neurons, (b) Timeline of recording technologies. Adopted           |

| from31                                                                                               |

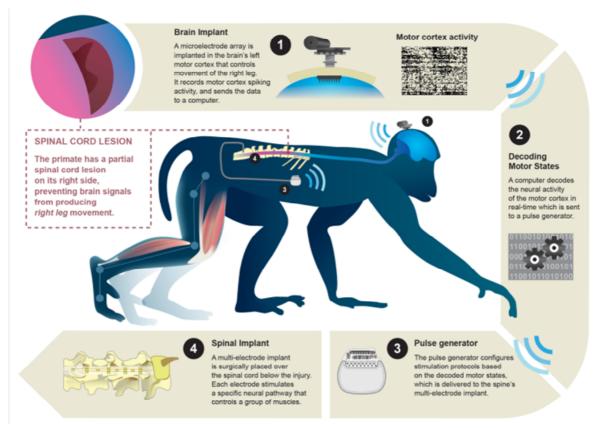

| 2.1: BMI demonstration for rehabilitation of a paralyzed monkey. The stimulus parameters are         |

| sent to the implanted site for adjusting the stimulation parameters using a wireless data            |

| transmission system37                                                                                |

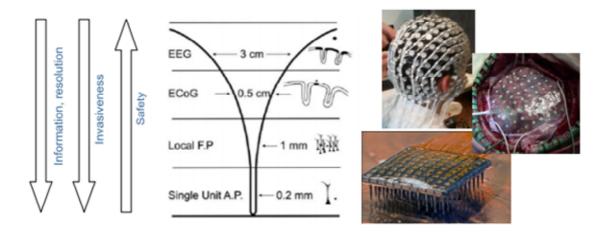

| 2.2: Various neural interface modalities with different levels of spatio-temporal resolution and     |

| invasiveness38                                                                                       |

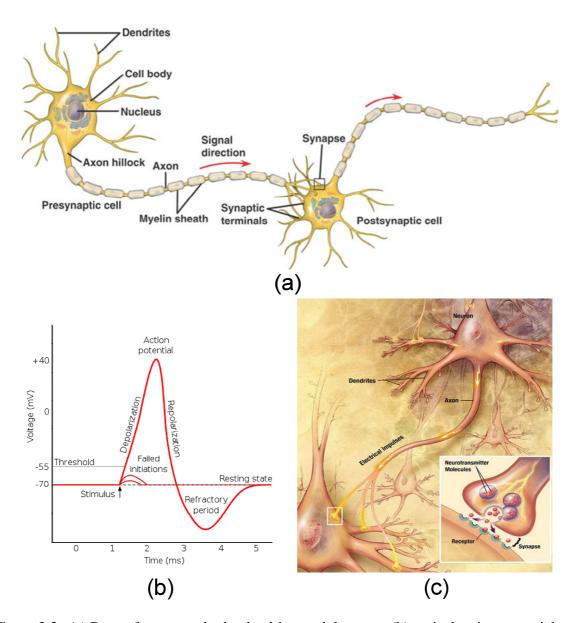

| 2.3: (a) Parts of a neuron: body, dendrites and the axon; (b) typical action potential; and (c)      |

| communication between neurons40                                                                      |

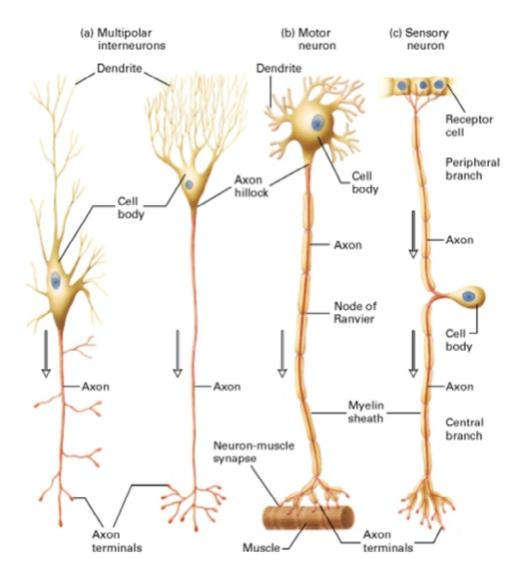

| 2.4: Structure for different types of neuron                                                         |

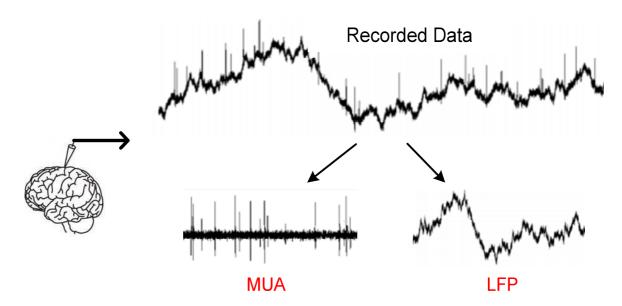

| 2.5: Contribution of LFP and multi-unit activity (MUA) which is the sum of the                       |

| EAPs42                                                                                               |

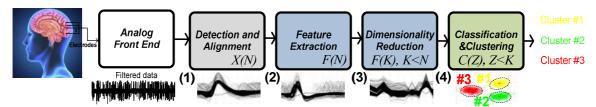

| 2.6: Spike sorting chain for determining single unit activity. Data dimensionality is reduced over   |

| processing units $(Z < K < N)$                                                                       |

| 2.7: Variation in the observed extracellular action potential profile from a pyramidal cell with     |

| spatial position. Variations depend on some cell proprieties such as the cell type and the cell      |

| geometry, as well as the distance of the electrode from cell and position of the recording electrode |

| relative to the cell                                                                                 |

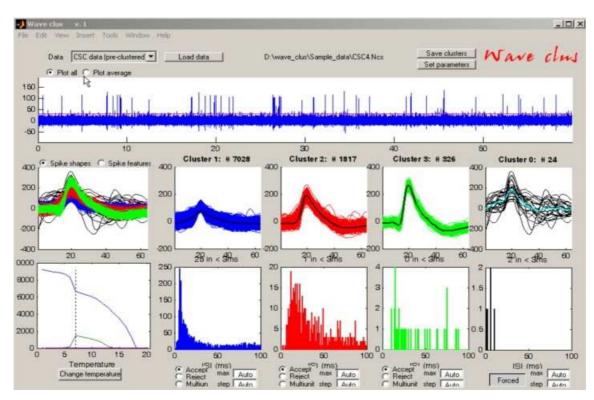

| 2.8: Waveclus graphical user interface                                                               |

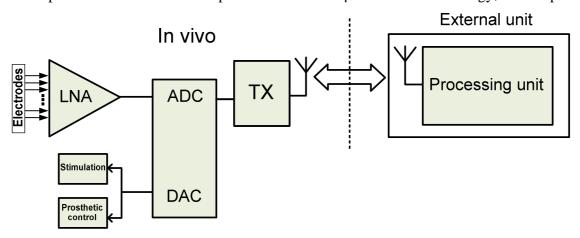

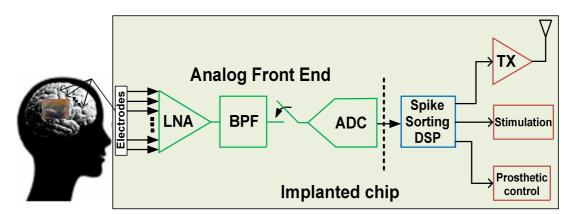

| 2.9: Block diagram of the conventional neural processing interface                                   |

| 2.10: General architecture of an implantable chip from recording (front-end neural interface) to     |

| processing and transmission/stimulation/decoding (back-end)49                                        |

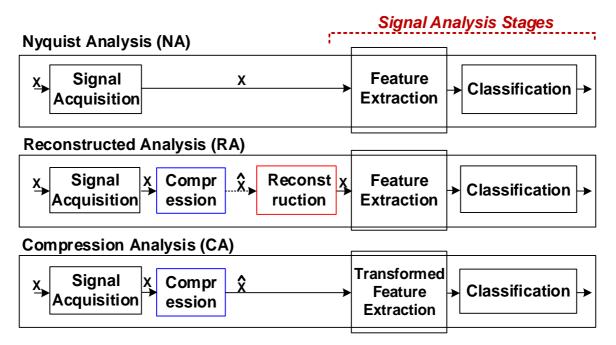

| 2.11: Demonstration of processing stages used in each of the three approaches. (a) Nyquist                   |

|--------------------------------------------------------------------------------------------------------------|

| Analysis (NA), (b) Reconstructed Analysis (RA) and Compressed Analysis (CA). Reconstruction                  |

| is bypassed in CA to provide significant savings in computational energy50                                   |

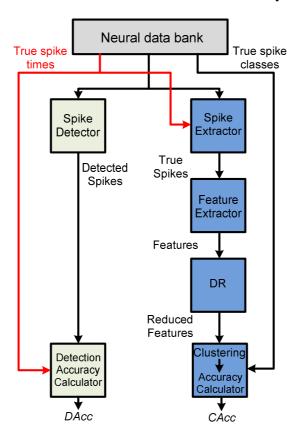

| 2.12: Signal processing chain used to evaluate detection and clustering accuracies                           |

| 2.13: Spike bank mean waveforms (peak-aligned) used for testing with corresponding Bray–Curtis               |

| similarity index (shown at the bottom). (a) C_Easy1_noise, (b) C_Easy2_noise, (c)                            |

| C_Difficult1_noise and (d) C_Difficult2_noise53                                                              |

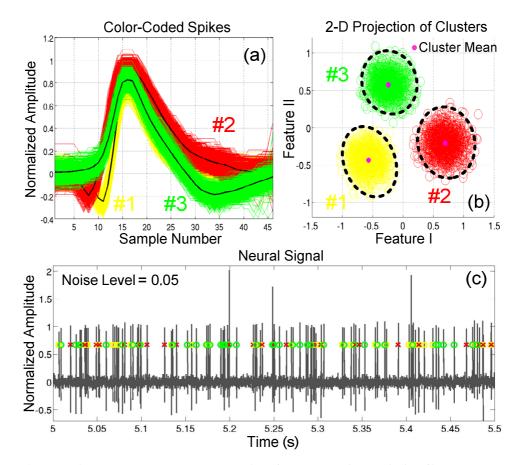

| 2.14: Test dataset 2 (C_Easy2_0.05) showing: (a) Color-coded spikes corresponding to different               |

| neurons (#1 yellow, #2 red, #3 green). (b) 2-D projection of spike clusters. (c) Segment of                  |

| simulated dataset 254                                                                                        |

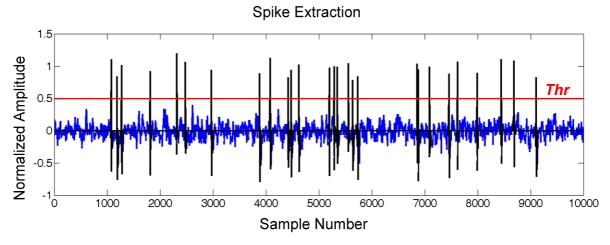

| 2.15: A short segment of a real neural signal including the extracted spikes. The extracted spikes           |

| (black color) are superimposed to the original waveform (blue color)56                                       |

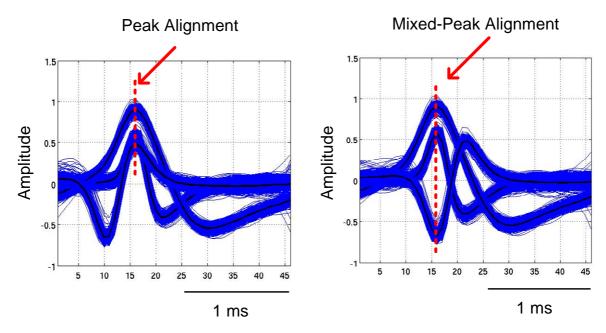

| 2.16: Examples of two different alignment methods. Left: peak-alignment method, Right: mixed-                |

| peak alignment method58                                                                                      |

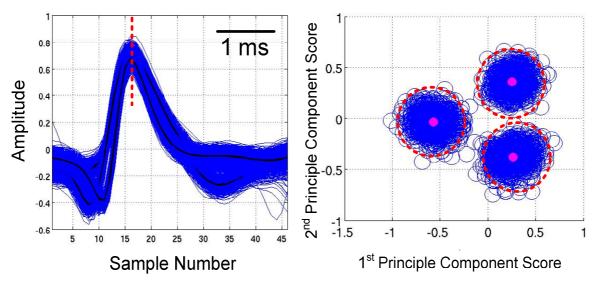

| 2.17: Example of feature extraction using PCA. Left: alignment to maximum amplitude, Right:                  |

| PC coefficients in feature space. The neural data simulator explained in section 2.4.1 is used for           |

| PCA analysis60                                                                                               |

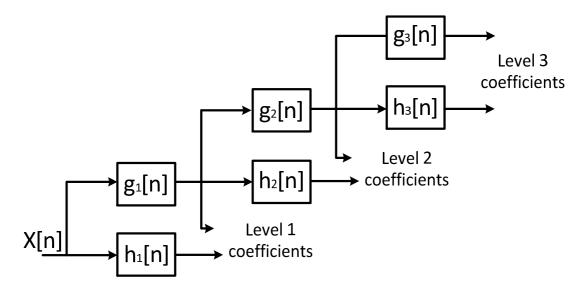

| 2.18: Wavelet decomposition by filter bank61                                                                 |

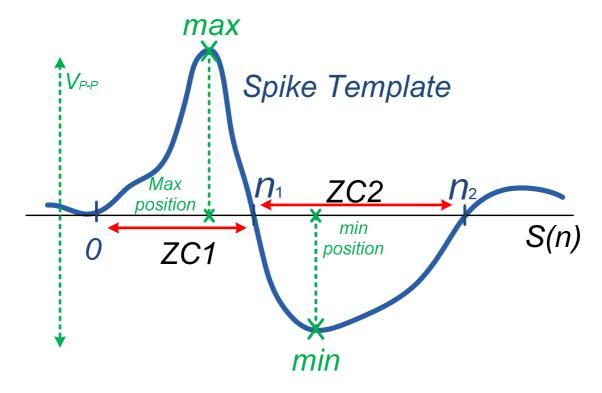

| 2.19: Spike template, $s(n)$ , for TM clustering. Illustration of zero crossing features ( $ZC1$ , $ZC2$ )64 |

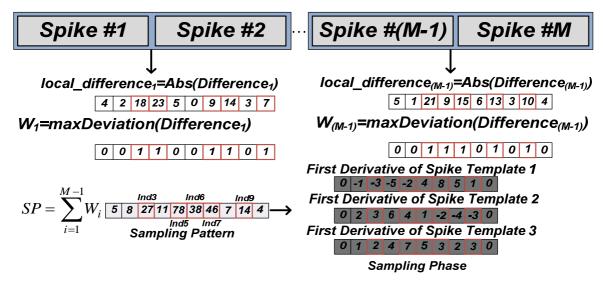

| 2.20: Asynchronous sampling of first derivative features. <i>M</i> spikes are considered for training        |

| period. Differences between two subsequent spikes are taken and weight $W=1$ allocated to                    |

| coefficients with maximum deviation from normality. Sampling pattern vector (SP) is the                      |

| summation of differences to find uncorrelated limits. Finally, sampling phase is done based on the           |

| sampling pattern from feature waveforms ( <i>K</i> =5)65                                                     |

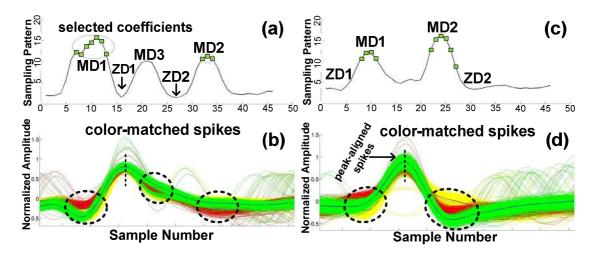

| 2.21: Sorting results with absolute value of sampling pattern for different datasets from original           |

| spike shapes. (a) and (b), C Easy2 01. (c) and (d), C Difficult2 01. Maximum difference (MD)                 |

| and zero difference (ZD) areas are annotated on the sampling profiles. The $K$ (=10 here) largest points are depicted with green squares                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

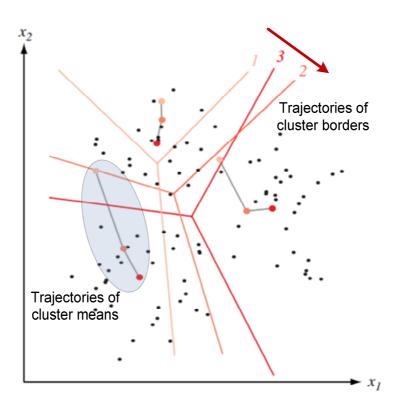

| 2.22: Trajectories for the means of the <i>k</i> -means clustering procedure applied to two-dimensional data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

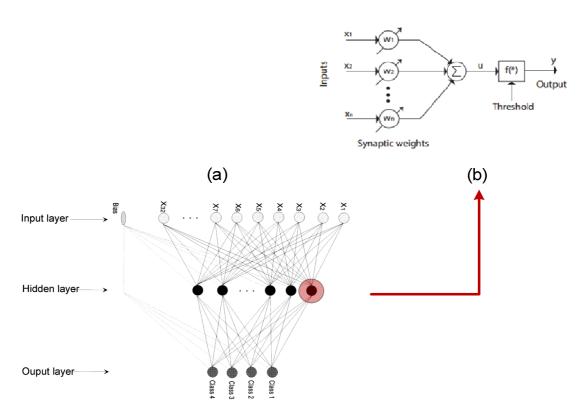

| 2.23: (a) Structure of a neural network used in the classification. (b) Basic artificial neuron model, where f (*) is the activation function. The synaptic weights are updated in the training phase by supervised or unsupervised algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

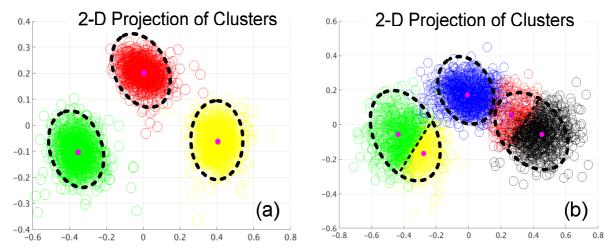

| 2.24: Clustering results using two different clustering methods, including (a) <i>K</i> -means and (b) O-Sort. The overclusterig issue is illustrated using different colors and borders are depicted with dashed line. The used data in this demonstration discussed previously in section 2.4.171                                                                                                                                                                                                                                                                                                                                                                                                                                           |

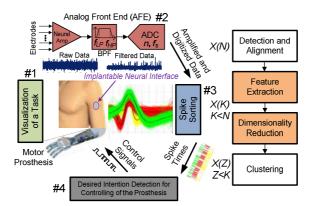

| 3.1: Schematic description for a BMI that relies on real-time recording and processing of neural activity to control a robotic prosthetic arm. The implanted electrodes in the recording site are used to monitor the activity of large populations of single neurons simultaneously. Spike sorting is used to classify the recorded spikes (active neurons) to their source of origin. The combined activity of classified spikes is transformed by a decoding (mathematical) algorithm into arm control signals (arm trajectory signals) that can be used to control the movements of the robotic prosthetic arm. The closed-loop control system is stablished by providing the subject with both visual and tactile feedback signals [110] |

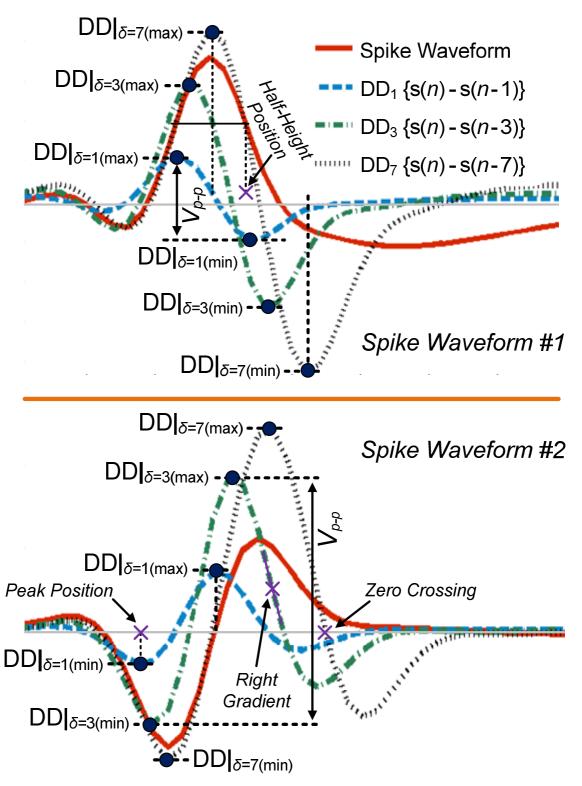

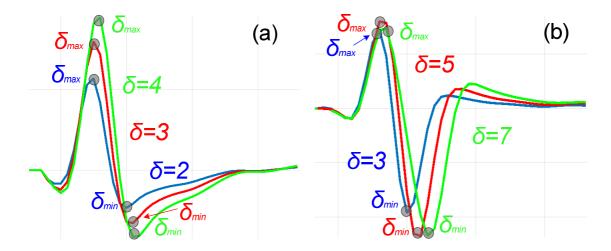

| 3.2: Two spike waveforms (spike shapes) and their discrete derivatives. The positive peaks, negative peaks and peak-to-peak amplitudes are annotated. Other features such as spike gradients and peak position are also depicted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

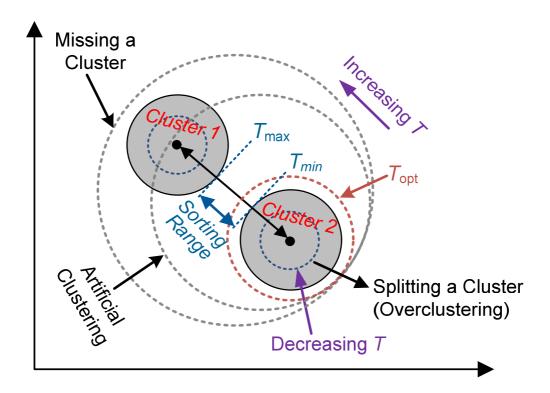

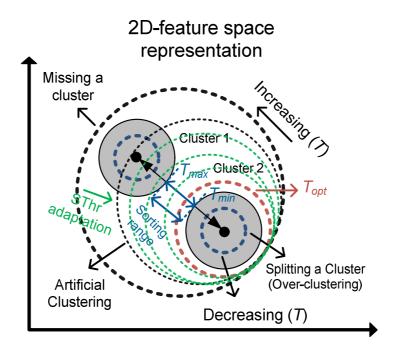

| 3.3: 2-D representation of feature space for two clusters from dataset 4 with the highest similarity. The effect of increasing (or decreasing) the threshold $T$ is depicted. Different threshold levels ( $T_{\rm opt}$ , $T_{\rm max}$ and $T_{\rm min}$ ) and sorting range are indicated. For $T > T_{\rm max}$ the risk of missing a cluster and artificial clustering is high. For $T < T_{\rm min}$ the main cluster would artificially be split into two or more sub-clusters.                                                                                                                                                                                                                                                        |

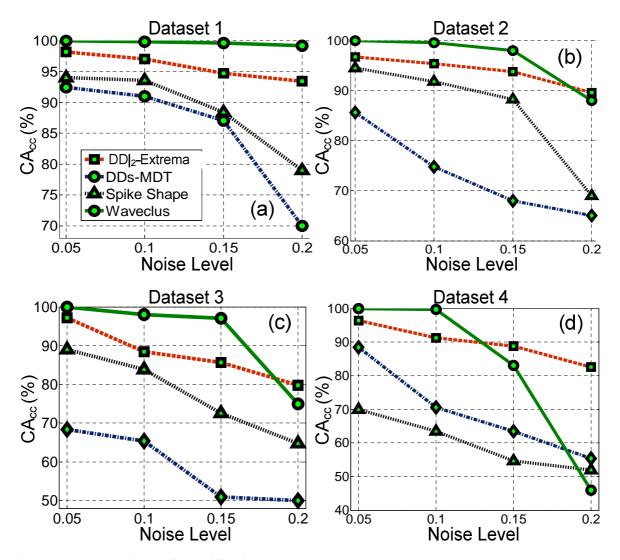

| 3.4: Comparison of classification accuracy between the DD <sub>2</sub> -Extrema method and other methods as a function of noise level for the four datasets. The result of Waveclus is used for comparison.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The optimum threshold (T <sub>opt</sub> ) is calculated for each feature extraction method                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

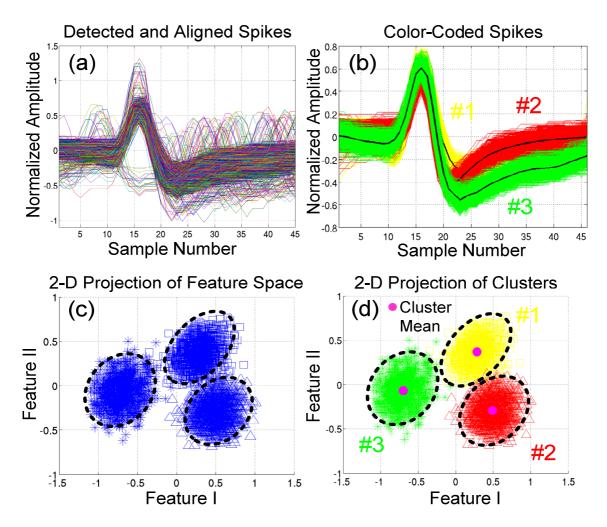

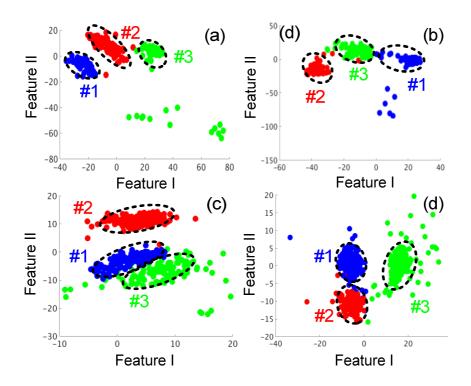

| 3.5: Test dataset 3 ( <i>C_Difficult1_0.05</i> ) showing: (a) Detected and peak-aligned spikes. (b) Color-                                                                                     |

| coded spikes corresponding to different neurons(#1 yellow,#2 red,#3 green). (c) 2-D projection of                                                                                              |

| feature space as seen by the spike classifier. (d) 2-D projection of spike clusters. The markers " $\Box$ ",                                                                                   |

| " $\Delta$ ", and "*" refer to the features for the members of the first, second, and third spike templates,                                                                                   |

| respectively84                                                                                                                                                                                 |

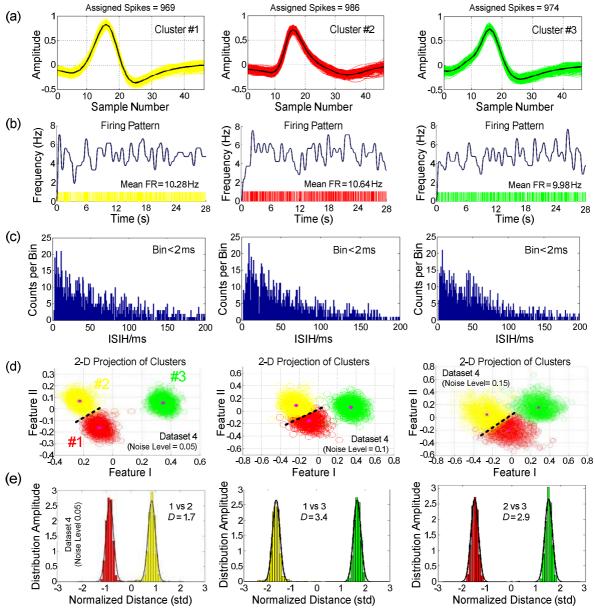

| 3.6: Sorting results of <i>C_Difficult2_005</i> . (a) Color-coded clusters with number of assigned spikes                                                                                      |

| in each cluster (#1 yellow, #2 red, #3 green. Note: The colors are not matched with Fig. 4). The                                                                                               |

| amplitude is of arbitrary units. (b) Corresponding firing pattern which depicts firing rate of each                                                                                            |

| neuron (0-28 s). Approximated firing rate determined by the Gaussian window function. The mean                                                                                                 |

| firing rate (FR) is annotated in each plot. (c) Inter-spike interval histogram (ISIH) of each cluster.                                                                                         |

| (d) 2-D projection of clusters for C_Difficult2_0.05, C_Difficult2_0.01 and C_Difficult2_0.15.                                                                                                 |

| (Spikes have been colored according to the ground truth). (e) Illustrates projection test using                                                                                                |

| probability density functions for the three combinations of cluster (C_Difficult2_0.05). For each                                                                                              |

| combination of neurons the distance between the two distributions is described by how many                                                                                                     |

| standard deviations they are apart (D value in each                                                                                                                                            |

| plot)85                                                                                                                                                                                        |

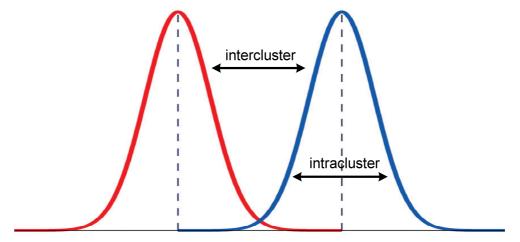

| 3.7: Representation of intracluster and intracluster for DisDeg calculation                                                                                                                    |

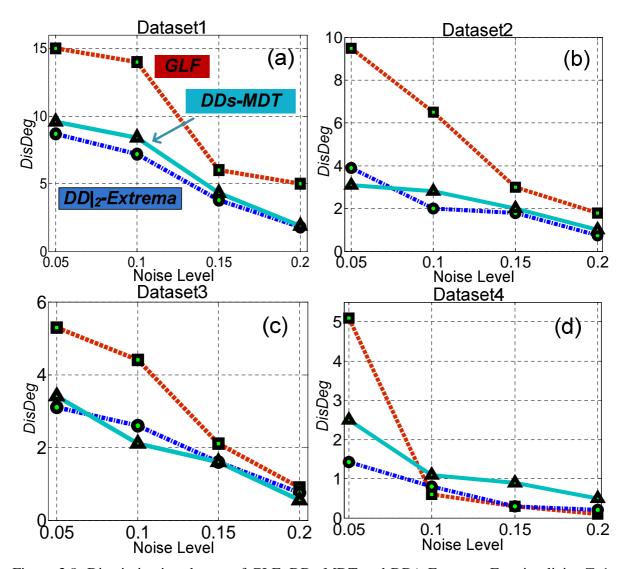

| 3.8: Discrimination degree of GLF, DDs-MDT and DD/2-Extrema. For simplicity $T=1$ . DisDeg of                                                                                                  |

| GLF was calculated using the quality metric                                                                                                                                                    |

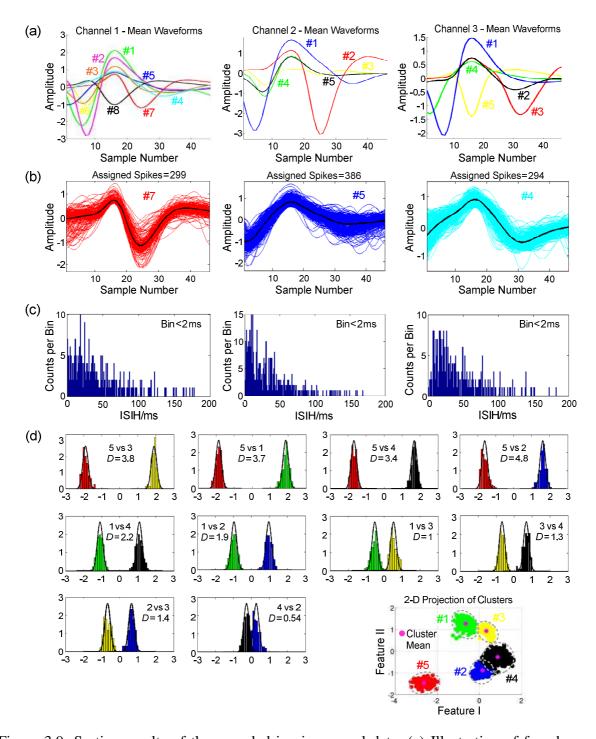

| 3.9: Sorting results of the recorded in-vivo neural data. (a) Illustration of found mean waveforms                                                                                             |

| in channels 1-3. The amplitude is of arbitrary units.(b) Color-coded clusters with number of                                                                                                   |

| assigned spikes in each cluster form channel 1 (#7 red, #5 blue, #4 cyan). (c) ISIH of the neurons                                                                                             |

| form channel 1. (d) Results of projection test using estimated probability density functions for all                                                                                           |

| possible combinations of channel 2. 2-D projection of clusters is included for visual clarity. The                                                                                             |

| vertical axis shows the distribution amplitude and the horizontal axis is the distance between the                                                                                             |

| two distributions                                                                                                                                                                              |

|                                                                                                                                                                                                |

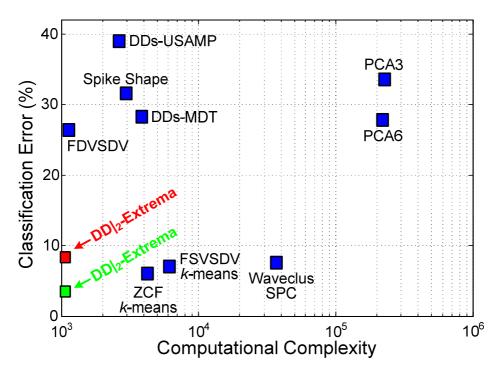

| 3.10: Classification error versus computational complexity for the different feature extraction and sorting methods considered herein. The red square (DDb-Extrema) shows the average accuracy |

| sorume incurous considered herein. The red square (DD)2-Exhemal shows the average accuracy                                                                                                     |

| amongst all datasets and all noise levels. The green square ( $DD _2$ -Extrema) shows the average                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| accuracy amongst all datasets using noise with a standard deviation of                                                                     |

| 0.0592                                                                                                                                     |

| 3.11: Classification error versus dimensionality factor for the different feature extraction                                               |

| methods93                                                                                                                                  |

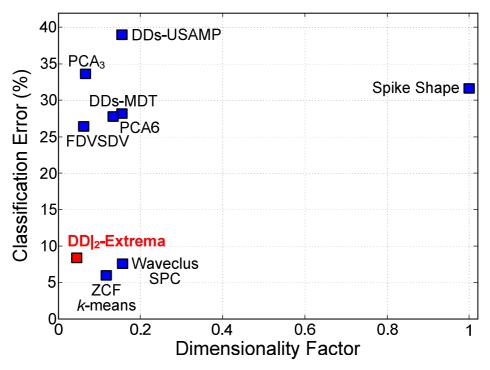

| 3.12: The spike-sorting process, annotated with an example of typical data rates. The data rate at                                         |

| the end of spike sorting is lower than that of the raw data. (Assumptions are annotated on the figure                                      |

| in red italics)94                                                                                                                          |

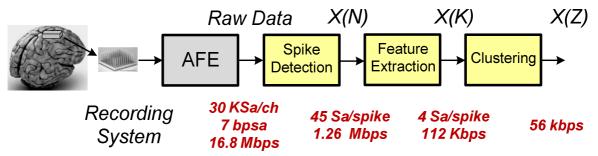

| 4.1: Multi-channel signal monitoring with (a) conventional recording and (b) the spike sorting                                             |

| chain is included in the neural interface. The power reduction due to the proposed power                                                   |

| optimization framework allows the integration of spike sorting into the implant. For the same                                              |

| power consumption as in the traditional model. The amount of saved power budget for spike                                                  |

| processor integration is 30% (c) which is discussed in section 4.3.396                                                                     |

|                                                                                                                                            |

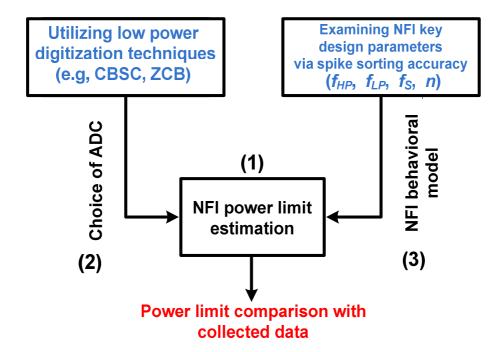

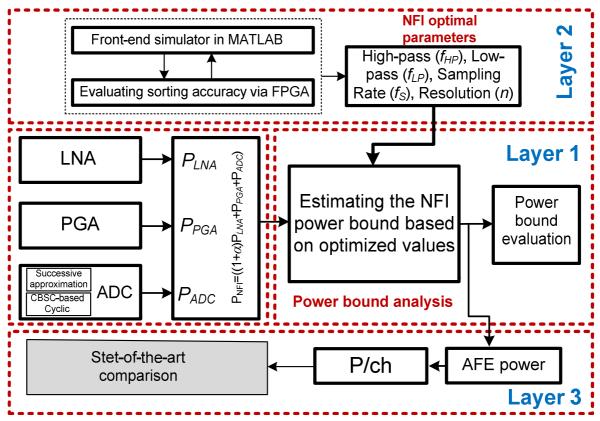

| 4.2: The optimization framework98                                                                                                          |

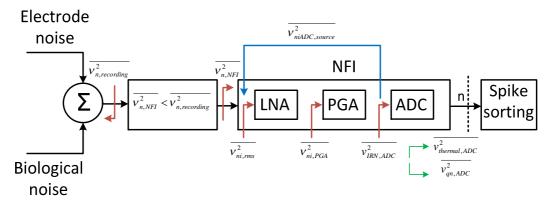

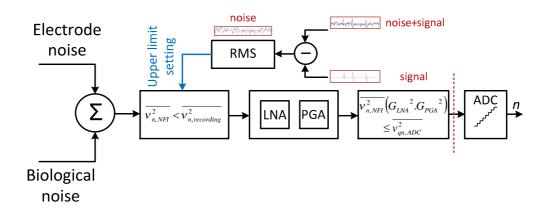

| 4.3: Illustration of noise sources in NFI. The definition of each noise source is:                                                         |

| $\overline{v_{n,recording}^2}$ : neural recorded signal noise power, $\overline{v_{n,NFI}^2}$ : Overall input referred NFI noise power,    |

| $\overline{v_{ni,rms}^2}$ : LNA Input referred noise power, $(\overline{v_{ni,PGA}^2} \approx 0)$ : PGA Input referred noise power, and    |

| $\overline{v_{IRN,ADC}^2}$ : ADC Input referred noise power which is composed of thermal noise power ( $\overline{v_{thermal,ADC}^2}$      |

| ) and quantization noise power ( $\overline{v_{qn,ADC}^2}$ ). $\overline{v_{niADC,source}^2}$ : the LNA input referred thermal noise power |

| of the ADC99                                                                                                                               |

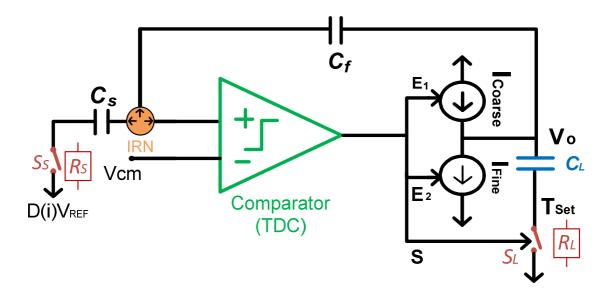

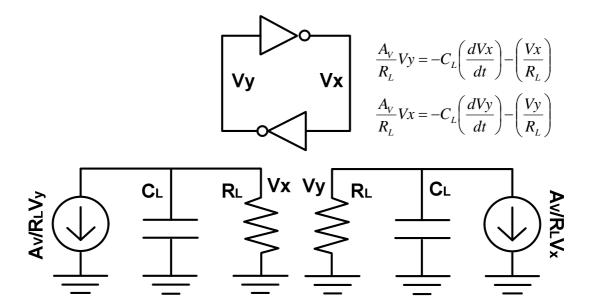

| 4.4: CBSC gain stage noise analysis. The effect of noise contribution from different elements are                                          |

| depicted via green (TDC noise), blue (load sampling capacitance $C_L$ ) and red (switches $R_S$ and $R_L$ ).                               |

| The overall input referred noise of gain stage is represented via (IRN). $D(i)V_{REF}$ is the output of                                    |

| analog multiplexer in 1.5-bit/stage. Vcm is the common mode voltage102                                                                     |

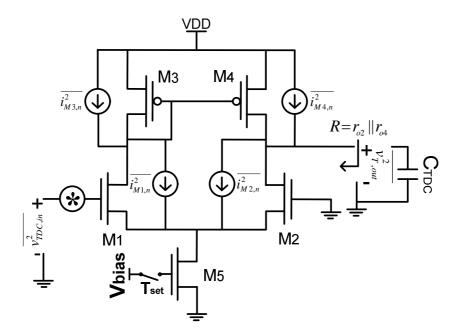

|                                                                                                                                            |

| 4.5: Comparator with noise sources. TDC is active when T <sub>Set</sub> is on                                                              |

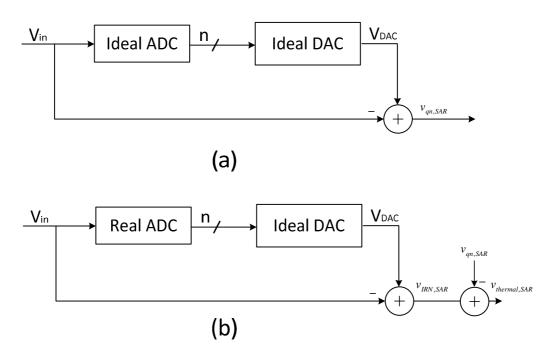

| 4.6: Model for ideal quantization noise and (b) Proposed model for thermal noise voltage in an                                             |

| SAR ADC                                                                                                                                    |

| 4.7: Model for ideal quantization noise and (b) Proposed model for thermal noise voltage in an SAR ADC                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

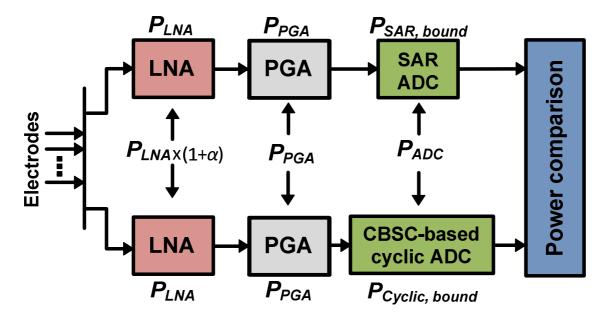

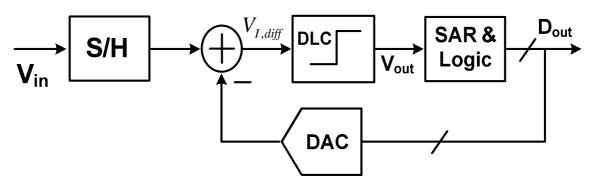

| 4.8: Block diagram for NFI power evaluation using different converters. The overall power consumption is expressed as $P_{NFI}=(P_{LNA}).(1+\alpha)+(P_{PGA})+(P_{ADC}).$                                                                                                                                                                                                                                                                                             |

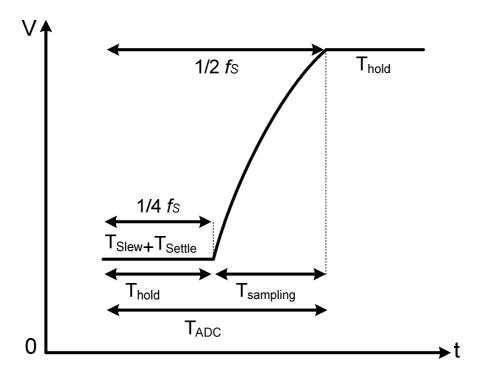

| 4.9: Illustration of PGA operation timing. PGA drives the S/H of data converter                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.10: Charge-redistribution SAR ADC                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.11: Simple model for dynamic latch comparator                                                                                                                                                                                                                                                                                                                                                                                                                       |

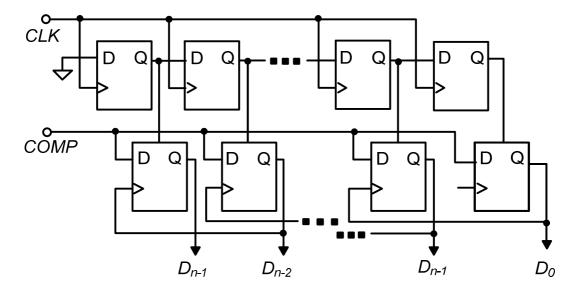

| 4.12: SAR digital logic                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.13: SAR ADC switching                                                                                                                                                                                                                                                                                                                                                                                                                                               |

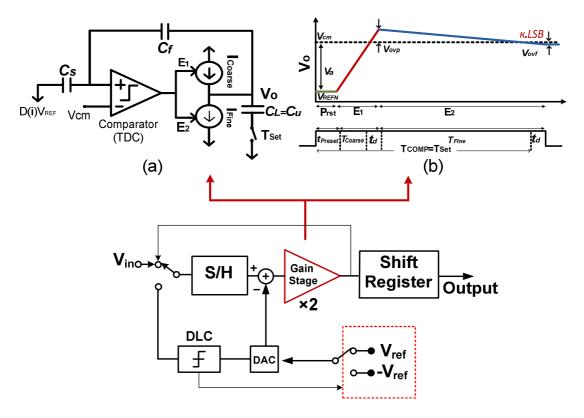

| 4.14: Block diagram of a cyclic ADC. (a) CBSC gain stage core and (b) timeline for output voltage (V <sub>O</sub> )                                                                                                                                                                                                                                                                                                                                                   |

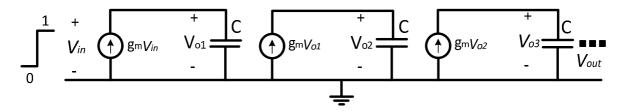

| 4.15: Illustration of a cascaded comparator. $A_{TDC}=V_{out}/V_{in}$                                                                                                                                                                                                                                                                                                                                                                                                 |

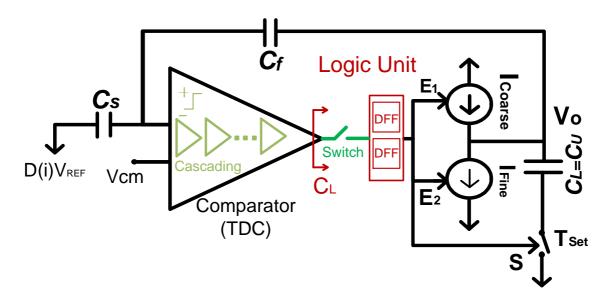

| 4.16: Driving logic by TDC (N=1)                                                                                                                                                                                                                                                                                                                                                                                                                                      |

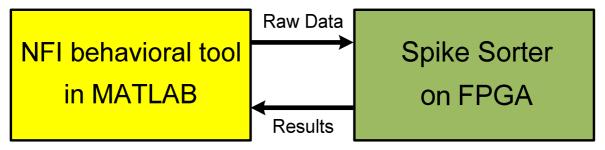

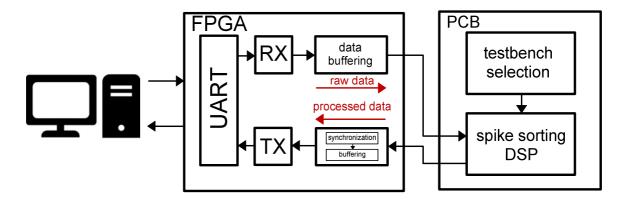

| 4.17: MATLAB-FPGA Interfacing used for NFI key parameters optimization                                                                                                                                                                                                                                                                                                                                                                                                |

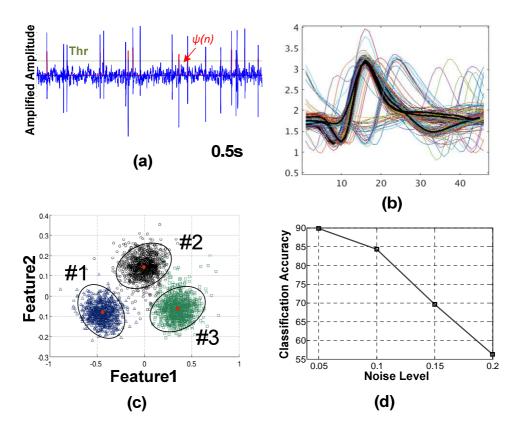

| 4.18: Block diagram of the spike sorting processor                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.19: Block diagram of the features buffering memory                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.20: Block diagram of the processing elements on the FPGA                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.21: The spike sorting processor clustering test using template matching (TM) FPGA platform. The sample output from one of the channels is shown in this figure. (a) Segment of neural signal. (b) Distinguished cluster means from 250 spikes in training phase. The spike processor for TM is developed for this test. (c) A 2-D projection of the clustered spikes color-coded, each represents a cluster. (d) The relation of clustering accuracy to noise level |

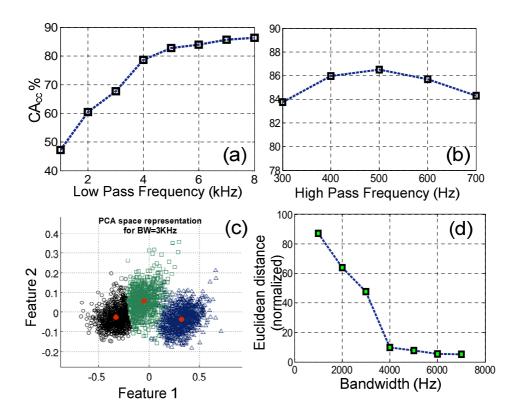

| 4.22: Effect of low pass (a) and high pass (b) filtering on spike sorting accuracy (mean over all spike datasets). The local field potential was extracted from <i>in-vivo</i> recording and superimposed                                                                                                                                                                                                                                                             |

| on the dataset under examination. (c) PCA feature space for the feature vectors of three neurons.                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (d) Euclidean distance analysis of feature vectors                                                                                                             |

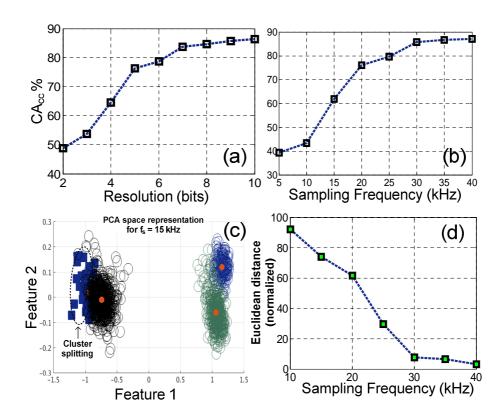

| 4.23: Effect of data conversion (a) resolution, and (b) sampling rate on spike sorting accuracy                                                                |

| (mean over all datasets). (c) PCA features when the sampling rate is reduced to 15 kHz for three                                                               |

| neurons. The effect of cluster splitting is highlighted in the figure. (d) Euclidean distance analysis                                                         |

| of feature vectors128                                                                                                                                          |

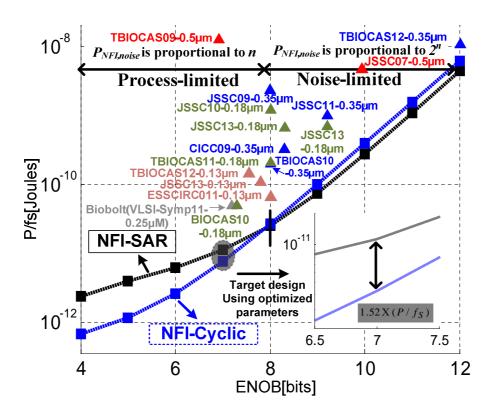

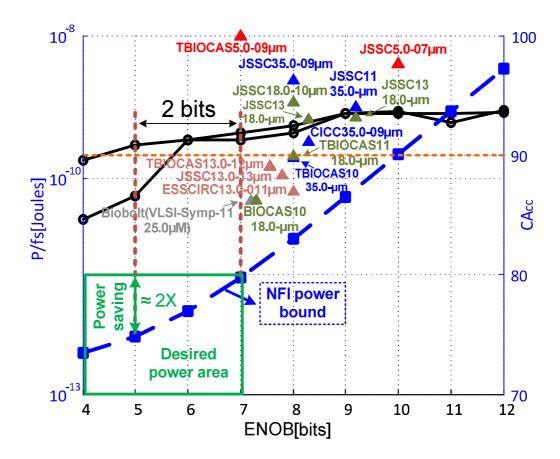

| 4.24: Estimated minimum power limit of NFIs based on SAR converter (dashed black line), CBSC                                                                   |

| cyclic ADC (dashed blue line) versus converter resolution. The following typical process                                                                       |

| parameters were used (180-nm CMOS): $V_{FS} = 1 \text{ V}$ , $T = 300 \text{ K}$ , $V_{\text{eff}} = 180 \text{ mV}$ and $C_{\text{min}} = 5 \text{ fF}$ . The |

| NFI parameters were $G_{LNA} = 100 \text{ V/V}$ , $G_{PGA} = 10 \text{ V/V}$ , NEF = 2 [7], $BW_{LNA} = f_{LP} - f_{HP} = 6.5 \text{ kHz}$                     |

| and $f_s = 30$ kS/s. Data for published neural recording interfaces are also shown ( $\triangle$ ) for comparison.                                             |

| $\alpha$ =0.5 is defined based on the reported $v_{ni,rms}$ =2.2 $\mu$ V/Hz (0.5 Hz to 50 KHz in                                                               |

| [7]130                                                                                                                                                         |

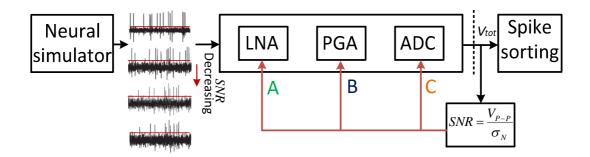

| 4.25: parametric NFI design. The system calibration is performed by recording channel SNR. A,                                                                  |

| B and $\mathbb{C}$ are the tuning parameters                                                                                                                   |

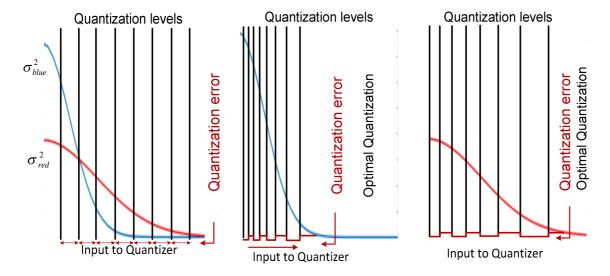

| 4.26: Examples of uniform and optimal quantization levels for narrow ( $\sigma_{blue}^2$ ) and wide ( $\sigma_{red}^2$ )                                       |

| Gaussian pdfs. This curve reveals that the decision levels are densely located in high-probability                                                             |

| region of the x-axis and coarsely in the low-probability region                                                                                                |

| 4.27: Power (blue)-CA <sub>CC</sub> (black) analysis when $OQ$ is used. Using $OQ$ saves 2-3 bits in                                                           |

| digitization. Desired power-area is illustrated with green square                                                                                              |

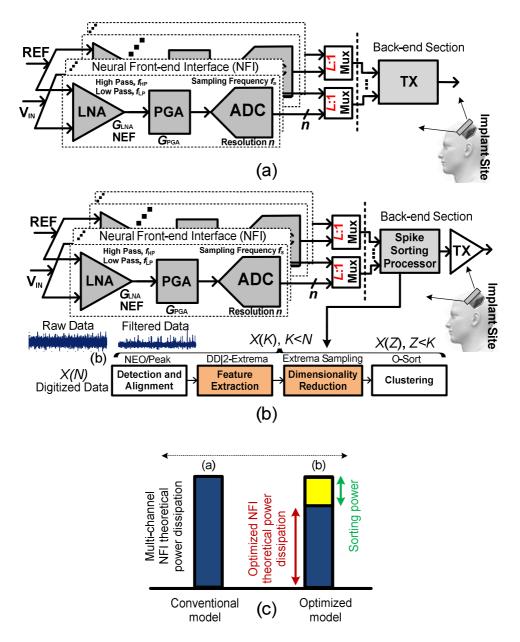

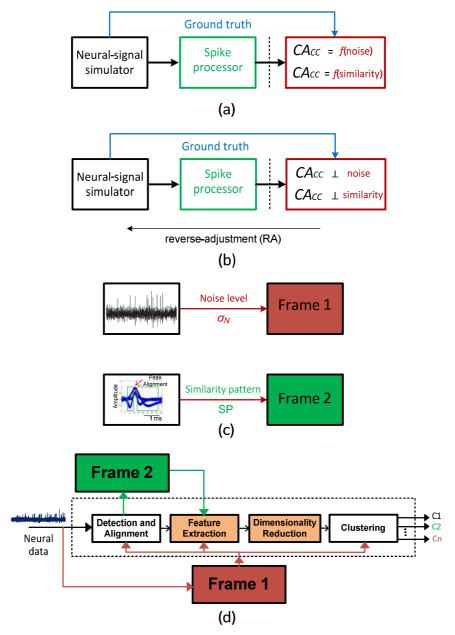

| 5.1: (a) Traditional spike sorting which in the performance is the function of noise (f(noise)) and                                                            |

| similarity ( $f$ (similarity)). (b) Illustration of spike processor independent ( $\bot$ ) of recorded data noise                                              |

| and similarity of spike waveforms. In this class of processing it is expected that the CAcc is                                                                 |

| matched with ground truth and at any condition set in neural signal simulator (c) Abstract view of                                                             |

| mapping the proposed reverse-adjusted spike processor characteristics into the frames (Frame1                                                                  |

| and Frame2) for implementing adaptive concept. Frame 1 increases the processor noise robustness                                                                |

| while Frame 2 is adapts the similarity level between the extracted spike waveforms. (d)                                                                        |

| Transformation of developed spike processor in Chapter3 based on developed frames (Frame 1                                                                     |

| and Frame 2). The created frames are embedded to the main processing line                                                                                      |

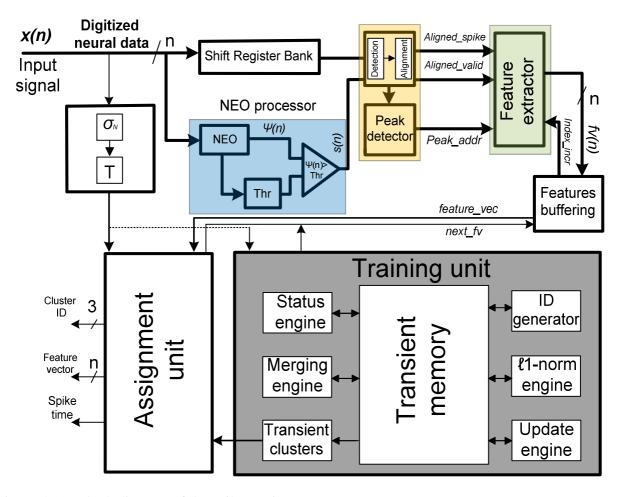

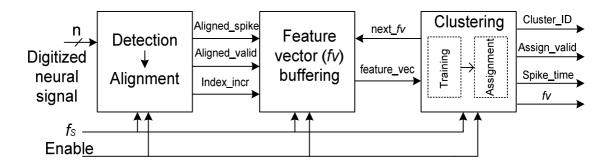

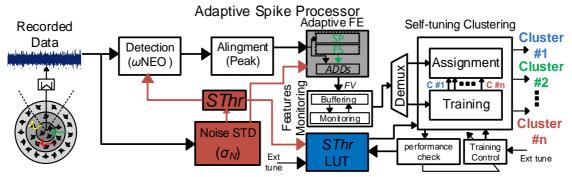

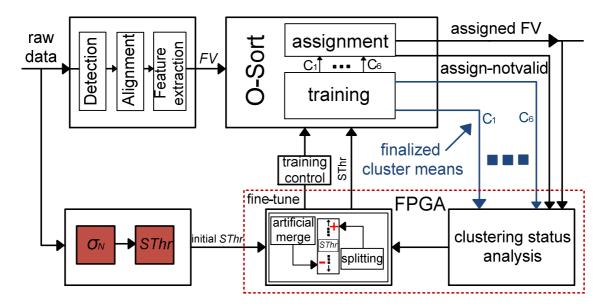

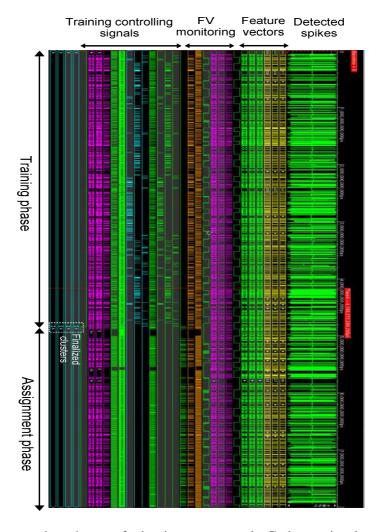

| 5.2: Adaptive spike sorting block diagram. The created frames in Figure 5.1(Frame 1 and Frame           |

|---------------------------------------------------------------------------------------------------------|

| 2) are embedded in the spike processor as (Frame $1 = \sigma_N$ ) and (Frame $2 = SP$ ). The introduced |

| adaptive processor scheme obeys the built-in principals for on-chip tuning of sorting parameters.       |

| n=1,,6 represents the number of existing clusters in the recorded data140                               |

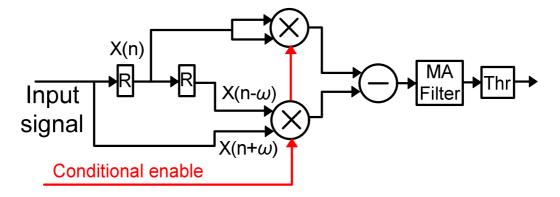

| 5.3: $\omega$ NEO conditional control. Conditional enable is initiated by ( <i>SThr</i> )               |

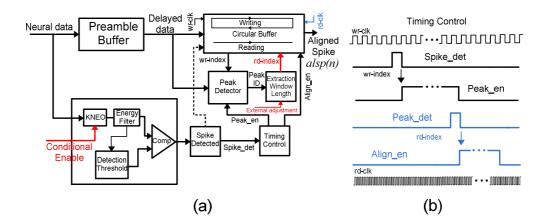

| 5.4: (a) Detection and alignment block diagram. (b) Operation timing diagram144                         |

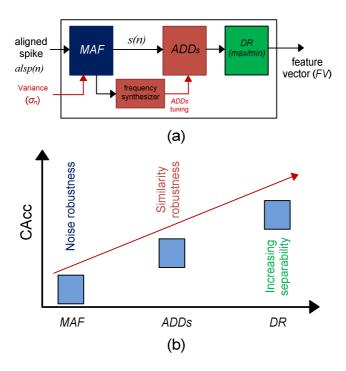

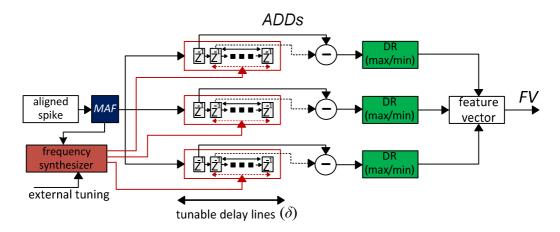

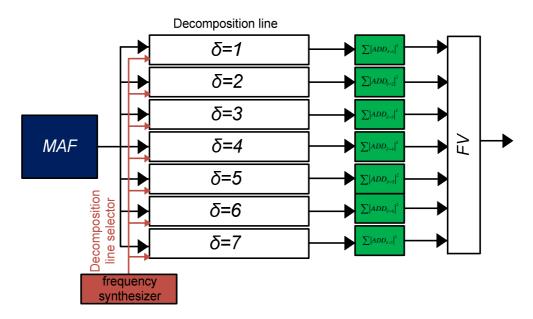

| 5.5: Adaptive Feature extraction unit. The MAF suppresses the effect of random and high                 |

| frequency noise. The $ADDs$ and frequency synthesizer blocks provide the adaptive decomposition         |

| The $DR$ block reduces dimensionality by retaining the most informative features of decomposed          |

| spike waveforms. Extrema (max/min) sampling is used in DR unit. It should be noted that other           |

| DR methods also can be employed for distinguishing the most appropriate features in the selected        |

| sub-bands (e.g. integral of a selected sub-band or spectral analysis of a decomposed signal)142         |

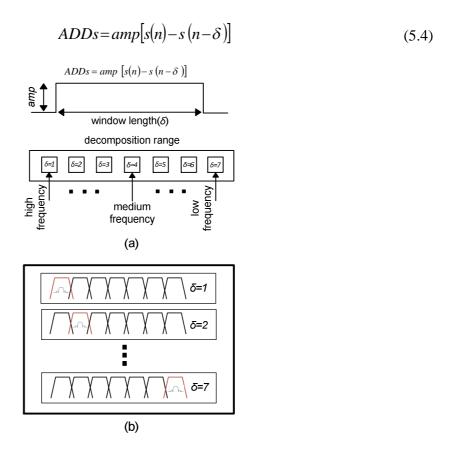

| 5.6: Demonstration of feature extraction processor employing spectral analysis a) parameterized         |

| ADDs (amp=1) and b) illustration of ADDs as an adaptive filtering                                       |

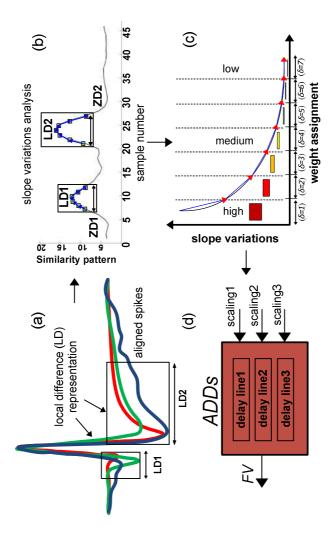

| 5.7: Frequency synthesizer and scaling factor tuning. (a) Peak aligned mean waveforms in                |

| C_Difficult1. Local differences are demonstrated with LD1 and LD2. (b) Generated sampling               |

| pattern from accumulated local differences. ZD1,2 identify the zero differences. (c) Weight             |

| assignment to the variations in the generated sampling pattern and extracting the scaling factors       |

| corresponding to the largest weights. The decomposition intensity is depicted by different colours      |

| from high (red) to low (black) (d) Tuning delay lines based on the selected scaling factors. FV is      |

| extracted based on the extrema of the delay lines (delay line1-3) outputs                               |

| 5.8: <i>ADDs</i> hardware implementation block diagram. Selecting the number of decomposition lines     |

| will be investigated further in future work. In this analysis three decomposition lines are used and    |

| six feature ( $K$ =6) are selected for clustering                                                       |

| 5.9: Feature vector monitoring unit                                                                     |

| 5.10: Flowchart for unsupervised clustering algorithm (O-Sort)                                          |

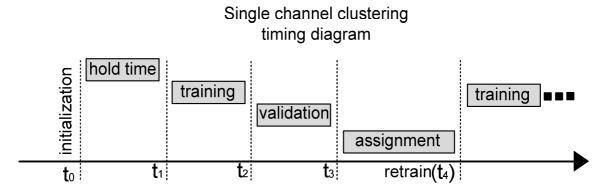

| 5.11: Multiphase clustering timing diagram                                                              |

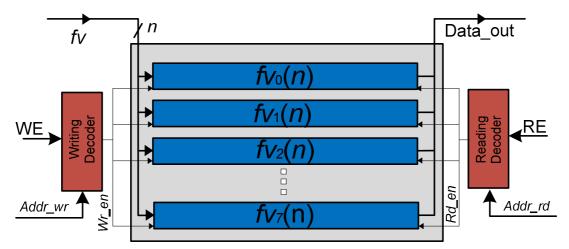

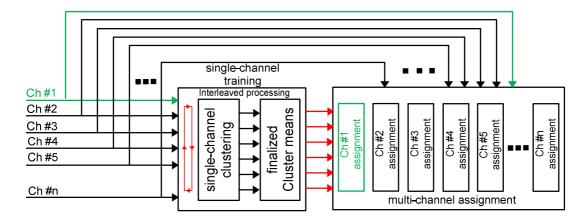

| 5.12: Example of multi-channel processing of recorded data                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------|

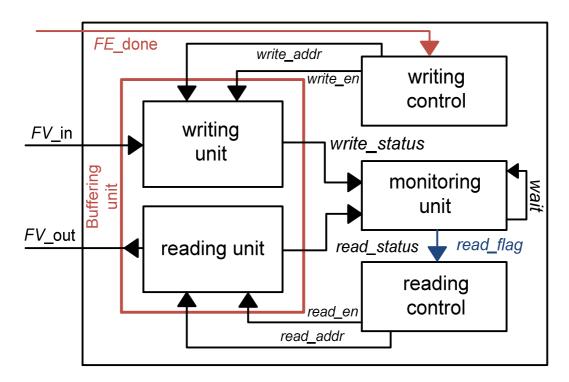

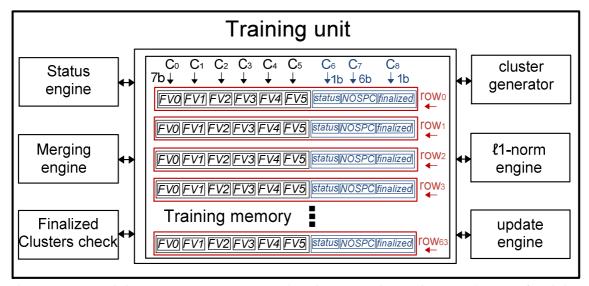

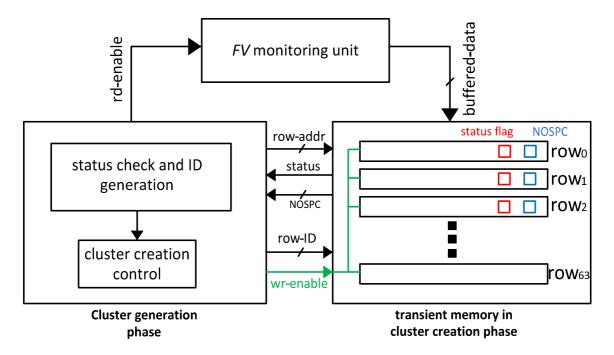

| 5.13: Training memory structure and main processing units. Each row of training memory consists                               |

| of six locations for accommodating extracted features (FV <sub>0</sub> -FV <sub>5</sub> ), 1bit status flag; 6bits represents |

| number of spikes per cluster (NOSPC) and 1bit for finalized flag155                                                           |

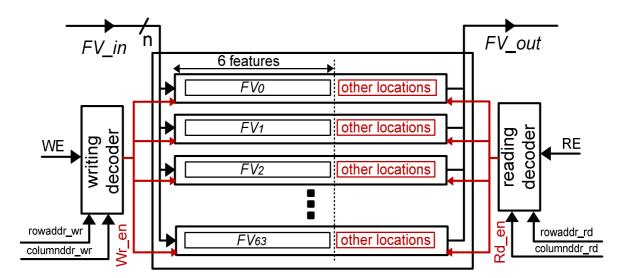

| 5.14: Block diagram of the register bank memory. Writing and reading of FVs are shown in this                                 |

| figure. Other memory locations include status, NOSPC and finalized flags                                                      |

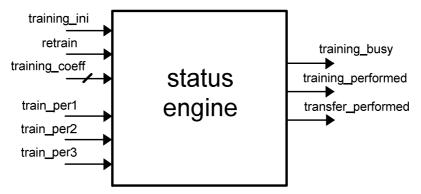

| 5.15: Status engine block diagram with inputs/outputs                                                                         |

| 5.16: Cluster ID generation flow                                                                                              |

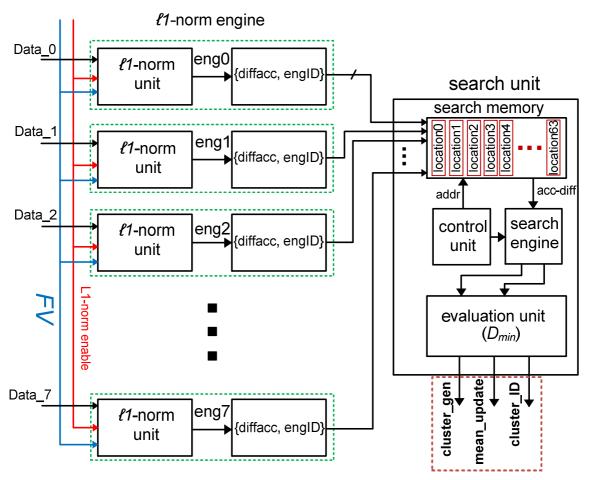

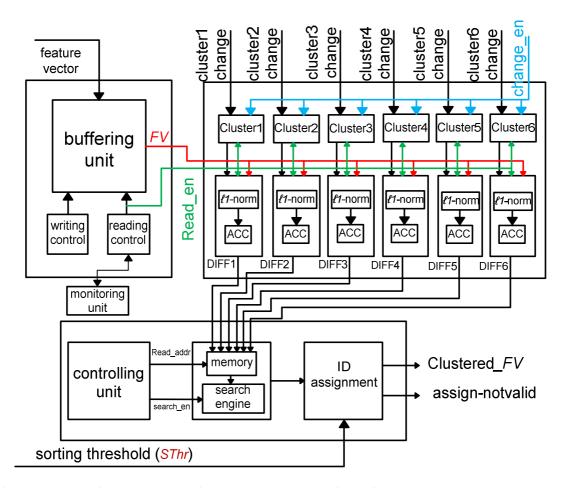

| 5.17: Block diagram of the $\ell I$ -norm engine. $\ell I$ -norm consists of eight parallel engines and it is                 |

| reused eight times to calculate the $\ell I$ -norm difference accumulation for all the 64 rows (row <sub>0</sub> -            |

| row <sub>63</sub> ) as shown in Figure 5.13159                                                                                |

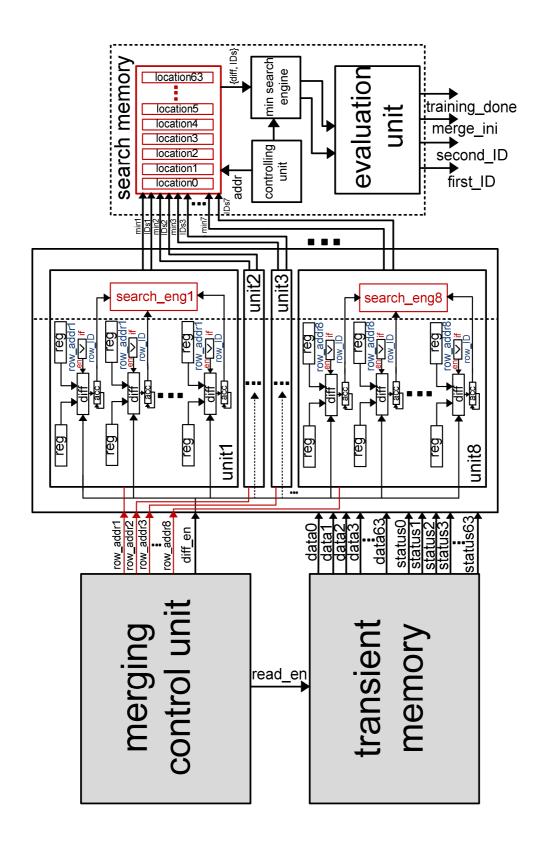

| 5.18: Demonstration of a moving merging matrix which is interleaved between all the transient                                 |

| memory rows (row <sub>0</sub> -row <sub>63</sub> )                                                                            |

| 5.19: Hardware implementation of the merging unit. The first section depicts the interleaving                                 |

| processing in the merging phase. The second section shows the block diagram of the search engine                              |

| and evaluation unit162                                                                                                        |

| 5.20: Converged cluster means check                                                                                           |

| 5.21: Assignment block diagram. Accumulator is depicted by ACC                                                                |

| 5.22: 2-D representation of feature space for two clusters. The effect of increasing (decreasing) the                         |

| threshold is depicted. Different threshold levels ( $T_{opt}$ , $T_{Max}$ and $T_{Min}$ ) and sorting range are shown.        |

| With increasing the threshold $(T>T_{Max})$ , the probability of missing a cluster and artificial clustering                  |

| is high. In addition, with declining the threshold ( $T < T_{Min}$ ), the main cluster would artificially be                  |

| split into two or more sub-clusters                                                                                           |

| 5.23: Sorting threshold ( <i>SThr</i> ) self-tuning methodology                                                               |

| 5.24: Data-streaming interface. RX is the symbol of receiver and TX is the symbol of transmitter.                             |

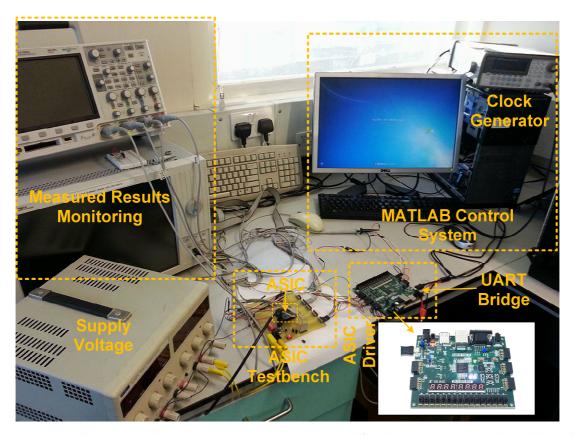

| 5.25: Fabricated processor and MATLAB-based ASIC verification setup. FPGA is used for driving                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASIC                                                                                                                                                                                                       |

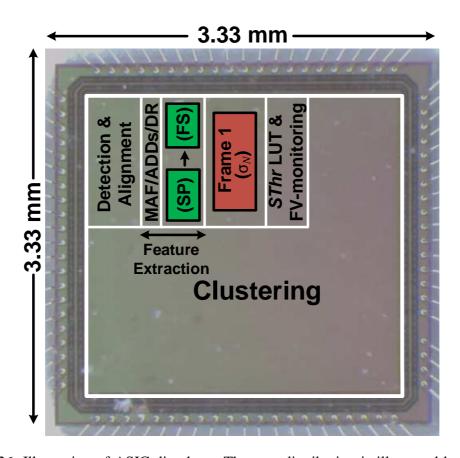

| 5.26: Illustration of ASIC layout in Cadence. The area distribution is illustrated based on the                                                                                                            |

| Cadence synthesize results                                                                                                                                                                                 |

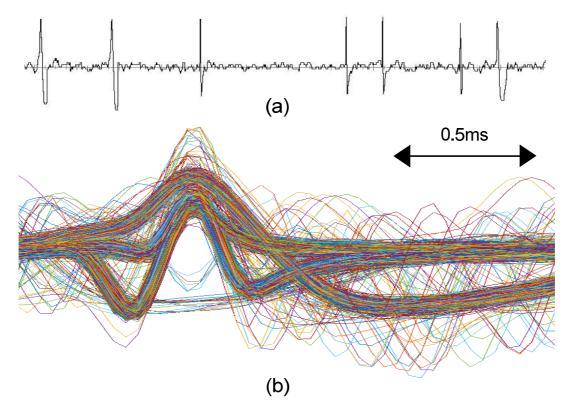

| 5.27: (a) A segment of neural signal depicted on logic analyzer and (b) the recorded spike                                                                                                                 |

| waveforms in MATLAB using the interfacing system                                                                                                                                                           |

| 5.28: (a) An illustration of extrema features using different sets of scaling factors. The scaling                                                                                                         |

| factors are selected based on $\underline{ADDs}$ methodology for (a) C_Easy2_0.05 (b) C_Difficult1_0.05. The                                                                                               |

| identified scaling factors for each dataset can be compared with the manual decomposition                                                                                                                  |

| approach discussed in chapter3                                                                                                                                                                             |

| 5.29: (a) 2-D projection of clusters for (a) <i>C_Easy1_0.05</i> , (b) <i>C_Easy2_0.05</i> , (c) <i>C_Difficult1_0.05</i>                                                                                  |

| and (d) <i>C_Difficult2_0.05</i> . (Spikes have been colored according to the ground truth)173                                                                                                             |

| 5.30: (a) Performance comparison of implemented processor and the state-of-the-art spike                                                                                                                   |

| processors. The mean accuracy of K-means and SPC is considered based on the template matching                                                                                                              |

| FE173                                                                                                                                                                                                      |

| 5.31: The operation phases of adaptive processor in Cadence simulator                                                                                                                                      |

| 5.32: The data generation based on random data selection. Data is generated based on the tuning                                                                                                            |

| parameters (data selector, NTP and $t_{gen}$ )                                                                                                                                                             |

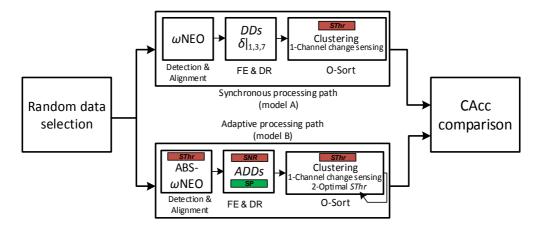

| 5.33: Dedicated set-up for comparing the performance between the non-adaptive and adaptive                                                                                                                 |

| processors                                                                                                                                                                                                 |

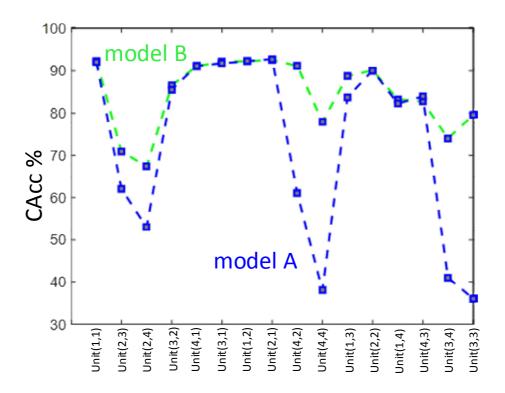

| 5.34: Comparison of clustering accuracy between the non-adaptive (model A) and adaptive (model B) processing chains. The data at input of the processor is generated based on the dynamic test methodology |

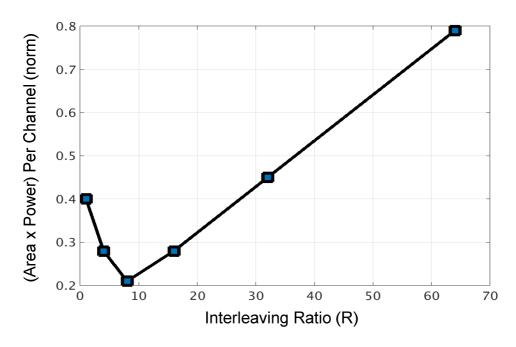

| 5.35: The normalized area and power trade-off versus interleaving ratio (R)                                                                                                                                |

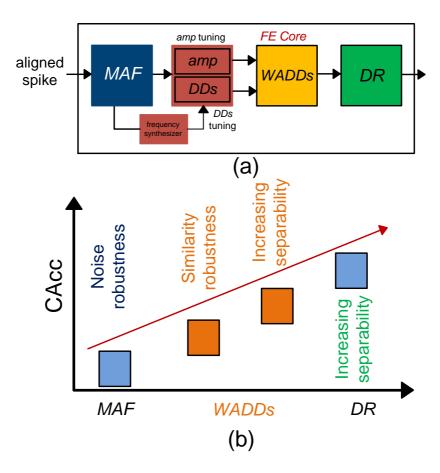

| 5.36: (a) Future implementation of FE (b) Separability level versus utilized units. WADDs is the                                                                                                           |

| acronym of weighted adaptive discrete derivatives                                                                                                                                                          |

| 5.37: (a) Demonstration of power spectral density calculation for the decomposed | ranges | from |

|----------------------------------------------------------------------------------|--------|------|

| high $(\delta=1)$ to low $(\delta=7)$ in DR unit                                 |        | 183  |

| 6.1: Proposed flow chart for NFI power optimization methodology                  |        | 186  |

# **List of Tables**

| 2.1 Various neural interface modalities with different levels of spatio-temporal resolution and |

|-------------------------------------------------------------------------------------------------|

| invasiveness. Adapted from [33-39]                                                              |

| 2.2 Overview of neuronal signal features62                                                      |

| 2.3 Distance and similarity measures used in template matching                                  |

| 2.4 Dimensionality reduction procedure                                                          |

| 3.1 Classification accuracy comparison of the examined feature set combinations82               |

| 3.2 Computational complexity comparison of various feature extraction and dimensionality        |

| reduction methods90                                                                             |

| 5.1 Adaptive spike processor summary                                                            |

| 5.1 Comparison to the state-of-the–art processors178                                            |

### **List of Abbreviations**

ABS: Absolute Value

ADC: Analog to Digital Converter

ADDs: Adaptive Discrete Derivatives

ANN: Artificial Neural Networks

AS: Asynchronous Sampling

ASIC: Application-Specific Integrated Circuit

BMI: Brain Machine Interface

BW: Bandwidth

CBSC: Comparator-Base Switched-Capacitor

CMOS: Complementary Metal-Oxide-Semiconductor

**CS:** Compressed Sensing

DAC: Digital to Analog Converter

**DBS**: Deep Brain Stimulation

DDs: Discrete Derivatives

DDS-MDT: Discrete Derivatives and Maximum Difference Test

DDS-USAMP: Discrete Derivatives and Uniform Sampling

DFFs: D-type Flip-Flops

DLC: Dynamic Latch Comparator

DR: Dimensionality Reduction

DSP: Digital Signal Processing

**DWT**: Discrete Wavelet Transform

EAPs: Extracellular Action Potentials

ECG: Electrocardiography

ECoG: Electrocorticography

EEG: Electroencephalography

EM: Expectation Maximization

**ENOB: Effective Number of Bits**

FDV: First Derivative

FDVSDV: First and Second Derivatives

FE: Feature Extraction

FoM: Figure of Merit

FPGA: Field-Programmable Gate Array

FR: Firing Rate

FV: Feature Vector

GLF: Graph Laplacian Feature

HAL: Hybrid Assistive Limb

KS: Kolmogorov-Smirnov

ICA: Independent Component Analysis

IRN: Input Referred Noise

ISIH: Inter-Spike Interval Histogram

IT: Integral Transform

LFPs: Local Field Potentials

LNA: Low Noise Amplifier

LUT: Look-Up-Table

MAF: Moving Average Filtering

MDT: Maximum Difference Test

MEAs: Multi-Electrode Arrays

MUA: Multi-Unit Activity

NEF: Noise Efficiency Figure

NEO: Non-linear Energy Operator

NFI: Neural Front-end Interface

NMF: Noise Multiplying Factor

NOSPC: Number of Spikes per Cluster

NSR: Noise-to-Signal Ratio

OQ: Optimal Quantization

O-Sort: Online Sorting

PCA: Principal Components Analysis

PGA: Programmable Gain Amplifier

RA: Reverse-Adjustment

RF: Radio Frequency

SAR: Successive Approximation Registry

SD: Standard Deviation

SDV: Second Derivative

SNQR: Signal -to- Noise and Quantization Ratio

SNR: Signal-to-Noise Ratio

SPC: Superparamagnetic Clustering

SPSs: Synchronous Processing Systems

SThr: Sorting Threshold

SUA: Single-Unit Activity

SWTP: Stationary Wavelet Transform Product

TDC: Threshold Detection Comparator

TEO: Teager Energy Operator

TM: Template Matching

UART: Universal Asynchronous Receiver / Transmitter

**USAMP:** Uniform Sampling

ZCB: Zero Crossing Based

ZCF: Zero - Crossing Features

#### **CHAPTER 1**

#### Introduction

#### 1.1 Motivation

Millions of people suffer from different neurodegenerative diseases around the world [1]. The consequence of such diseases is the devastating loss-of-function and resulting emotional problems such as depression for the patients and their families. In addition, treatment of such diseases requires significant financial support. For example, there were approximately 45 million cases of brain disorders in the UK, with a cost of £110 billion per annum [2]. The five most costly disorders were dementia, psychotic disorders, mood disorders, addiction and anxiety disorders. In addition, figures show that there are currently 127,000 people diagnosed with Parkinson's disease in the UK and this is predicted to rise to 162,000 by 2020, an increase of 28% [3].

One way of curing and managing diseases is the prescription of appropriate medication. It should be noted that this treatment method is not very effective for types of disease such as Alzheimer's. For example, medicines (e.g., acetylcholine) can ease the Alzheimer's symptoms and slow down the progress of the disease, but the effect lasts for a limited time with possible side effects such as diarrhea, vomiting, insomnia and fatigue. On the other hand, the application of therapeutic devices in the category of alternative treatment have offered more efficient and reliable treatment (e.g., in the case of Parkinson's disease) with promising results and fewer side effects [4].

Detailed understanding of neuron-related activities such as the generation of thoughts/ perceptions/actions remains an important challenge for improved alternative treatments using neuroprosthetic devices. The first step in any alternative treatment is the ability of interfacing and decoding the interactions between neurons. This ability has already significantly changed the development path of neuroprosthetic devices. Typically neuroprosthetic devices are categorized into: 1) decoding sensory information (stimulation patterns) which is used for rehabilitation (e.g., spinal cord injury) or to lessen symptoms (e.g., Parkinson's); and 2) devices for extraction of motor pathways for controlling assistive technologies such as a prosthetic hand. There are nearly 2 million people living with limb-loss in the United States; the main cause is diabetes [5].

Approximately 185,000 amputations occur in the United States each year and in 2009 [6], hospital costs associated with amputation totaled more than \$8.3 billion [7]. An increased projection of 2 million cases is estimated from 2005 to 2050 for those who require amputation surgery [5].

Studies in the field of neuroscience have suggested that the realization of neuroprosthetic devices for motor/sensory applications are significant within the concept of brain machine interfaces (BMIs). The BMI concept is an interpreter for analysis of the characteristics of active neurons in the acquired data such as the number of neurons, their firing rates and the degree of correlation between the identified neurons. These features help to build application-specific experimental models (e.g., for neurodegenerative disease treatments). Nowadays reliable acquisition of high channel count recording is possible thanks to astonishing advancements in microtechnology such as interfacing probes and CMOS integrated circuits [8-10]. The quality of neural data monitoring depends on the level of invasiveness including: (1) electroencephalography (EEG); (2) electrocortiography (ECoG); and (3) multi-electrode arrays (MEAs) with sub-micron resolution features which all will be extensively discussed in Chapter 2.

The science of integration in the field of recording technology in conjunction with nanostructure fabrication techniques (e.g., Michigan arrays) have significantly increased the number of recording sites. The monitoring of the brain functionality down to individual neuron level [referred to as extracellular action potentials (EAPs) or spikes] allows the study of the underlying network dynamics. Implantable neural recording systems follow a modified Moore's law as shown in Figure 1.1, where the number of recording channels since the 1960s has exponentially grown. The number of neurons recorded doubles every 7 years [11].

On the other hand, the vast amount of data recorded from the distributed recording sites introduce fundamental limitations in either processing data using highly complex processing methods or transmission of raw data to an external processing unit. In implantable devices there is a limited power budget which limits the type of processing that can be included. Hence high channel count processing of data using complex methods is extremely difficult. In addition, transmitting large quantities of data to external units results in a transmitter bandwidth bottleneck. To alleviate the issues related to high channel count monitoring schemes, reduction of the data prior to transmission is necessary. This can be achieved by *on-chip spike sorting*. Spike sorting is the process of identifying individual neurons from the multiple signals sensed by an electrode tip. This process

Figure 1.1: Examining 56 studies of neural recording systems published over the last five decades. (a) Number of simultaneously recorded neurons; (b) Timeline of recording technologies. Adopted from [11].

aims to extract some distinguishable features of each neuron and to subsequently classify each neuron to its source of origin. The research in this thesis is primarily devoted to providing advanced processing using low power techniques suitable for implantable on-chip spike sorting. In addition to overcoming these issues, retaining the useful information regarding active neurons can be utilized for application-specific BMIs. The spike sorting concept has its inherent signal processing complexities; hence employing traditional power hungry algorithms such as principle component analysis (PCA) are not suitable.

## 1.2 Research Objectives

Within this context, there is still a gap to fill in the realization of real-time, on-chip and highly accurate spike sorting. Processing specifications are crucial in order to fulfill closed-loop and open-loop application requirements. For example, in a closed-loop application (e.g., spinal cord paralysis rehabilitation), it is important to develop a highly efficient on-chip sorting method for generating stimulation commands with minimum delay.

The research in this thesis aims to introduce an on-chip spike sorting framework from theory to hardware design and implementation which is scalable with the number of recording sites and has

high efficiency in terms of resource utilization to fulfill implantable applications in the future generation of BMIs. The research has the following objectives:

- To develop a feature extraction method which outperforms the available established state-of-the-art. In addition to power efficiency, another concern relies on the fact that the simplicity in spike waveform transformation should not result in information fidelity loss which would directly affects the clustering performance. Other questions considered are about scalability and reconfigurability (adaptivity) of feature extraction. An online method with low complexity is of particular interest when a large number of channels are monitored. This thesis develops a feature extraction methodology which provides better power-area-accuracy compared to the state-of-the-art.

- To identify the neural front-end interface (NFI) theoretical minimum power limit taking account of all the analog processing chain key stages (amplification, filtering and digitization) together with the spike sorting process. The NFI specifications have direct effect on the performance of the spike sorting unit. This study has three important potentials including: 1) proper resource utilization in NFI design parameters without compromising the spike sorting performance; 2) pushing the power envelope towards the predicted NFI power limit using novel digitization methods; and 3) introducing a desired power region for future NFI design.

- To propose a new processing approach in the context of adaptivity for on-chip sorting utilization. Spike sorting is a computationally demanding signal processing technique due to its inherent challenges, thus developing a novel hardware implantable processing scheme with performance self-tuning and inherent power suppression capabilities is required. To this extent, investigation of design methods and signal processor structures with reference to "adaptivity" or "reconfigurability" to complement the conventional synchronous digital signal processors (DSPs) is important. An adaptive processor is capable of shaping its parameters (behaviors) according to the property of the input neural data stream. Embedding the adaptive framework in the classical synchronous processing systems makes the processor operation "signal-dependent" which offers various benefits from accuracy tuning to asynchronous power management.

#### 1.3 Outline of the Thesis

The thesis proposes an advanced and effective algorithm for improving spike sorting performance in its major stages, namely, feature extraction and clustering. The aim is to have the least amount of supervision and complexity whilst obtaining high clustering performance. The feature extraction and clustering of neural waveforms and the proposed approach to improve the results at each stage are discussed. The thesis has the following chapters: