# A Planar CMOS Field-Emission Vacuum Magnetic Sensor

Paul J. French, Anthony J. Kenyon, Member, IEEE, and David M. Garner

Abstract—We have fabricated a CMOS vacuum magnetic sensor that exploits the deflection of an electron beam produced by field emission by a perpendicular magnetic field. The device is planar and fabricated by conventional lithography and etching processes. An extremely high magnetic field sensitivity of  $4 \times 10^3 \%/T$  is reported.

Index Terms—CMOS, field emission, magnetic sensing.

# I. INTRODUCTION

THE FIELD OF magnetic sensing is dominated by Halleffect sensors, which have the advantages of ease of fabrication and compatibility with silicon-based microelectronics. For field strengths between 0.1 mT and 1 T, they are convenient and cheap. However, they are highly sensitive to temperature and suffer from offset voltages that are indistinguishable from applied magnetic fields. This limits their sensitivity to low-frequency or static magnetic fields, as does their susceptibility to 1/f noise. Notwithstanding recent works on Hall-effect sensors with integrated on-chip control circuitry and current spinning technology to reduce noise and offset [1], [2], their long-term stability of sensitivity and offset remain problematic, and mechanical stress affects the zero-field offset through the piezoresistive effect. Competing technologies such as anisotropic magnetoresistance, colossal magnetoresistance, and superconducting quantum interference devices (SQUIDs) offer extremes of sensitivity, but suffer from expense and complexity of manufacturing and operation, and are therefore used in applications in which high sensitivity is paramount. Fluxgate magnetometers, which offer resolutions down to fractions of a picotesla, suffer from high power consumption and cost, along with large size. Despite recent impressive progress on miniaturization of such sensors [3], a gap in the market exists for a magnetic sensor which has high sensitivity and broad measurement range and is small, cheap to manufacture, and compatible with silicon VLSI. The vacuum magnetic sensor (VMS) is a promising solution.

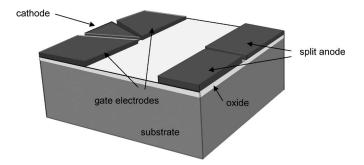

In the VMS, a sharp conducting tip is placed close to a gate electrode that produces an electron beam by field emission. This beam propagates through a vacuum and is detected using a split

Fig. 1. Schematic layout of the planar VMS device.

anode. Any difference in the current received by each half of the anode indicates a lateral deflection of the electron beam and can be used to measure an external magnetic field. The technique is inherently temperature independent and low noise. Of the few examples of such sensors found in the literature [4]–[6], the most successful reports are from the group led by Uemura and Itoh [5], [7]. They rely on microfabrication techniques only to produce a single sharp tip, an extraction gate, and a focusing electrode. The split anode is separately mounted 5 mm away from the cathode. Despite this, their device produced extremely high sensitivities at 10 000%/T.

Using conventional lithography techniques, the device can be made planar, highly sensitive (resolutions of 10-100 nT and changes in differential anode current in the range of 1000–10000%/T are predicted by modeling [4]), and high bandwidth (electron transit time from field-emission tip to anode is around 1 ps). Other benefits include the following: ease of integration with CMOS processing, the ability to manufacture thin sensors, and fabrication of long anode-cathode distances while still retaining a thin device. For magnetic fields within about 50% of the measurable field range, the response is predicted to be linear to within a few percent [4]. There have been few examples of planar devices, although Sugiyama [8] made a lateral device on a quartz substrate which had a sensitivity of around 1000%/T, but this device had extremely low anode currents that were some two orders of magnitude smaller than the gate current. A more recent device produced by electron beam lithography using metallic cathode, gate, and anode structures on silicon has been reported to have a maximum sensitivity around 98%/T [9].

We have previously presented the design and outlined the processing steps required to produce a planar CMOScompatible field-emission VMS device [10]. In this brief, we report the realization of a working device with a magnetic field sensitivity of  $4 \times 10^3 \%/T$ .

Manuscript received June 11, 2008; revised January 9, 2009. First published February 27, 2009; current version published March 25, 2009. This work was supported by LEM-HEME Ltd. In particular, the work of P. J. French was supported by the Engineering and Physical Sciences Research Council through a project grant and a studentship. The review of this brief was arranged by Editor C. Nguyen.

The authors are with the Department of Electronic and Electrical Engineering, University College London, WC1E 7JE London, U.K.

Digital Object Identifier 10.1109/TED.2009.2014430

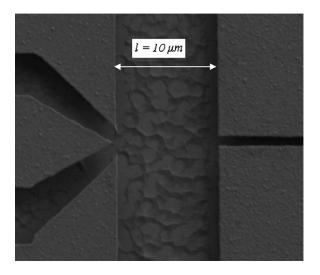

Fig. 2. SEM image of a fabricated device, showing the (LHS) cathode/gate structure and the (RHS) split anodes.

# **II. DEVICE DESIGN AND FABRICATION**

A schematic diagram of the device is shown in Fig. 1. Cathode, gates, and anodes are all formed in silicon, separated physically and electrically from the silicon substrate by a  $3-\mu m$  thermal oxide. The cathode has a very sharp tip, which acts as the field-emission tip, and two gate electrodes are placed close to this, the aperture size, tip position, and gate–cathode distance defining both the field required for electron emission and the angular divergence of the emitted electron beam. The split anodes are some distance from the cathode–gate assembly, with a gap of 500 nm between the two electrodes. The cathode–anode spacing was varied in our devices between 10 and 500  $\mu m$ .

Devices were fabricated by INNOS Ltd. at Philips' fabrication facility in Eindhoven. Wafer-bonded SOI wafers were used as substrates in order to ensure high-quality oxide layers. The top silicon layer was phosphorous doped to become heavily n-type (to a carrier concentration of  $10^{20}$  cm<sup>-3</sup>). A thin pad oxide was grown on the top silicon layer, followed by the deposition of silicon nitride, which was patterned using i-line photolithography with the outlines of the cathode tip, the gate, and the anode. LOCal Oxidation of Silicon (LOCOS) was then used to oxidize this top silicon away in the areas where there is no nitride; the LOCOS process results in a very sharp tip at the end of the silicon cathode. Finally, the nitride was stripped in hot phosphoric acid, and then, an etch in buffered hydrofluoric acid removed the oxide surrounding the cathode tip, the split anode, and the gate to leave the completed sensor. Gold contact pads were evaporated, and individual devices were sawn from the wafer, mounted in chip carriers, and wire bonded.

Samples were mounted in a vacuum chamber, which was evacuated to  $10^{-6}$  mbar and placed within a Helmholtz coil arrangement that permitted the application of a controlled field of up to 2.5 mT in any direction.

Measurements of the device magnetic sensitivity were performed using Keithley Instruments source-measure units (models 236 and 6430). The cathode was grounded, the gates were held at a potential of +100 V to initiate filed emission, and the split anodes were held at +175 V to ensure maximum

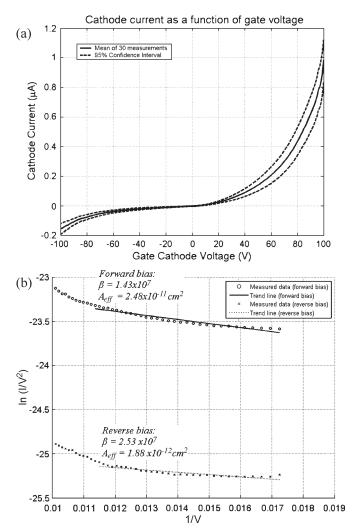

Fig. 3. (a) Gate/cathode current/voltage characteristics for a typical device. (b) Corresponding Fowler–Nordheim plots for forward- and reverse-bias cases.

current at the anodes and a low gate current (in practice,  $I_g$  was approximately 10% of the total anode current).

#### **III. EXPERIMENTAL RESULTS**

Fig. 2 shows an scanning electron microscope (SEM) image of a single device. The example shown has a cathode–anode separation of 10  $\mu$ m, and the cathode tip is slightly behind the level of the gate electrodes.

Fig. 3(a) shows a current–voltage plot for the gate–cathode structure of a typical device, demonstrating field emission. Note that there is emission in both forward and reverse cathode–gate bias. In the former case, emission is from the cathode, and in the latter, it is from the gate electrodes. This is a result of the gate electrodes having sharp tips (see Fig. 2), which act as field-emission sources under reverse bias. This is not a problem for normal device operation, as VMS devices will always be operated under forward bias (positive gate voltages), and it is the anode currents that will be measured. Fig. 3(b) shows a Fowler–Nordheim plot of the data from Fig. 2a, from which both the effective cathode tip area  $A_{\rm eff}$  and the field-emission factor  $\beta$  are obtained.  $A_{\rm eff}$  values of 2.48 × 10<sup>-11</sup>

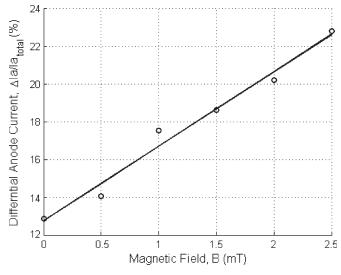

Fig. 4. Differential anode current [defined by (1)] as a function of applied magnetic field. The slope of the line gives the device sensitivity as 4000%/T.

and  $1.88 \times 10^{-12}$  cm<sup>2</sup> were found for forward- and reverse-bias cases, respectively. These values compare favorably with other devices reported in the literature [9] and imply field-emission tip radii of approximately 28 and 8 nm, respectively. The beta values of  $1.43 \times 10^7$  and  $2.53 \times 10^7$  (forward- and reverse-bias cases, respectively) are a little high but, within fitting error, are consistent with the device geometry. Although there is some deviation from linear behavior at both high and low fields, this may be ascribed to Joule heating effects (high field) and threshold effects (low field). Note that only the central (linear) portion of the data was used for fitting.

Fig. 4 shows a plot of differential anode current as a function of magnetic field applied perpendicular to the plane of the device. Each point is the mean of five readings of each of the currents received by the split anodes. We define the differential anode current, where  $I_{a1}$  and  $I_{a2}$  are the currents received by the two anodes, as

$$I_d(\%) = \left| \frac{I_{a1} - I_{a2}}{I_{a1} + I_{a2}} \right| \times 100.$$

(1)

The slope of a plot of  $I_d$  versus B therefore yields the sensitivity of the device in units of percent per tesla. From Fig. 4, we calculate the sensitivity of our device to be  $4 \times 10^3 \%/T$ . We note that this figure is significantly higher than that reported for similar devices in [9]. We attribute the higher sensitivity of the reported structure to a combination of improved device geometry (i.e., a longer cathode–anode distance), higher quality oxide material (SOI instead of wet oxidation), and good control of processing to ensure high-quality tips, uniform conductivity of the poly-Si layer, and low surface roughness after etching. We note that the major contributors to noise and measurement uncertainty in the present generation of devices are likely to be Joule heating of the tip at high cathode currents and tip degradation due to ion bombardment and contamination if the operating pressure is too high. Although these devices were tested at pressures around  $10^{-6}$  mbar, they operate successfully up to pressures of  $10^{-4}$  mbar at the expense of an increased rate

of tip degradation. Further work may concentrate on optimizing operation at higher pressures in order to relax constraints on vacuum level.

# IV. CONCLUSION

We have demonstrated a field-emission vacuum magnetic sensor fabricated using standard CMOS processing techniques. The device exhibits the highest magnetic field sensitivity reported to date for a planar field-emission device:  $4 \times 10^3 \%/T$ . This is a very promising result and suggests that this is a viable technology for the production of low-cost magnetic sensors with high sensitivity.

### REFERENCES

- R. S. Popovic, P. M. Drljaca, and P. Kejik, "CMOS magnetic sensors with integrated ferromagnetic parts," *Sens. Actuators A, Phys.*, vol. 129, no. 1/2, pp. 94–99, May 2006.

- [2] D. R. Popovic, S. Dimitrijevic, M. Blagojevic, P. Kejik, E. Schurig, and R. S. Popovic, "Three-axis teslameter with integrated Hall probe," *IEEE Trans. Instrum. Meas.*, vol. 56, no. 4, pp. 1396–1402, Aug. 2007.

- [3] P. M. Drljaca, P. Kejik, F. Vincent, D. Piguet, and R. S. Popovic, "Low-power 2-D fully integrated CMOS fluxgate magnetometer," *IEEE Sensors J.*, vol. 5, no. 5, pp. 909–915, Oct. 2005.

- [4] M. I. Marques, P. A. Serena, D. Nicolaescu, and A. Correia, "Design of field emission based magnetic sensors," J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 18, no. 2, pp. 1068–1072, Mar. 2000.

- [5] K. Uemura, S. Kanemaru, and J. Itoh, "Fabrication of a vacuum-sealed magnetic sensor with a Si field emitter tip," J. Micromech. Microeng., vol. 11, no. 1, pp. 81–83, Jan. 2001.

- [6] D. Nicolaescu, V. Filip, and J. Itoh, "Field emitter magnetic sensor with steered focused electron beam," *Jpn. J. Appl. Phys. 1, Regul. Rap. Short Notes*, vol. 40, no. 4A, pp. 2173–2177, Apr. 2001.

- [7] J. Itoh, K. Uemara, and S. Kanemaru, "Three-dimensional vacuum magnetic sensor with a Si emitter tip," J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 16, no. 3, pp. 1233–1235, May 1998.

- [8] Y. Sugiyama, "Recent progress on magnetic sensors with nanostructures and applications," J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 13, no. 3, pp. 1075–1083, May 1995.

- [9] K. Lee and K. E. Holbert, "Lateral-type field emission-based magnetic sensor fabricated by electron-beam lithography," *J. Electrochem. Soc.*, vol. 151, no. 4, pp. H81–H85, 2004.

- [10] D. M. Garner, P. J. French, G. Hui, and A. Fung, "Design of a complementary-metal-oxide-semiconductor-compatible field-emission magnetic sensor with adjustable sensitivity," *J. Vac. Sci. Technol. B, Microelectron. Process. Phenom.*, vol. 22, no. 3, pp. 1202–1205, May 2004.

**Paul J. French** received the Ph.D. degree in electronic and electrical engineering from University College London, London, U.K., in the area of field-emission magnetometers. He is currently undertaking postdoctoral research in the Space Magnetometer Laboratory, Imperial College London, London, U.K., in the field of space physics.

From this, he has developed a number of wideranging research interests.

Dr. French was a recipient of the WCSIM scholarship twice, i.e., once in 2004 and again in 2006, for

his work on magnetic sensors and devolvement of a new type of pressure sensor.

**Anthony J. Kenyon** (M'08) received the D.Phil. degree in chemical physics from the University of Sussex, Brighton, U.K., in 1992.

Since completing his degree in 1992, he has been with the Department of Electronic and Electrical Engineering, University College London, London, U.K., where he is currently a Senior Lecturer. His research includes the application of nanostructured semiconductor materials to electronics and photonics. He is the author of more than 60 peerreviewed publications and is an Editorial Board

Member of a number of journals, including *Advances in Optoelectronics*, the *Open Condensed Matter Physics Journal*, and the *Open Optics Journal*. He has given invited talks at a number of major international meetings and has co-organized a number of international symposia.

Dr. Kenyon is a member of the Institute of Physics and the Institution of Engineering and Technology and serves on the Board of Delegates of the European Materials Research Society.

**David M. Garner** received the B.A. and Ph.D. degrees from the University of Cambridge, Cambridge, U.K., in 1993 and 1997, respectively.

This was followed by three years of postdoctoral research work with research interests in the fields of power semiconductor devices and vacuum microelectronics, after which he became a Process Development Engineer with Texas Instruments, working on advanced BCD processes. He returned to academia in 2001 as a Lecturer in electronic engineering with University College London, London,

U.K., where he resumed his research interests in vacuum microelectronics and is currently with the Department of Electronic and Electrical Engineering; concurrently, he was a Consultant with Cambridge Semiconductor Ltd., U.K. In 2004, he was with Cambridge Semiconductor Ltd. as a Full-Time Analog Design Engineer, eventually becoming the Head of the IC Design Team. He has about 50 publications in the areas of power semiconductor devices, vacuum microelectronics, and switch-mode power supplies.