#### REFERENCE ONLY

# **UNIVERSITY OF LONDON THESIS**

| Degree                  | Pho                                   | Year 2006                                         | Name of Author ADENIRAN                                                                                                                                |    |

|-------------------------|---------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| unpublis                | a thesis accept<br>shed typescript    |                                                   | of the University of London. It is an by the author. All persons consulting at Declaration below.                                                      | .( |

| that no                 |                                       | it or information derived                         | LARATION scribed thesis rests with the author and d from it may be published without the                                                               |    |

| approve<br>of those     | ed libraries with<br>e libraries. App | in the United Kingdom,                            | University Library may lend a copy to for consultation solely on the premises to: The Theses Section, University of condon WC1E 7HU.                   |    |

| Univers permiss the The | sion from the Ureses Section          | niversity of London Libra<br>of the Library. Regu | reproduced without explicit written ary. Enquiries should be addressed to lations concerning reproduction vary sis and are listed below as guidelines. |    |

| Α.                      |                                       |                                                   | y upon the prior written consent of the vide addresses where possible).                                                                                |    |

| В.                      |                                       | In many cases the aut<br>a Copyright Declaration. | hor has agreed to permit copying upon                                                                                                                  |    |

| C.                      | 1975 - 1988.<br>Declaration.          | Most theses may be o                              | copied upon completion of a Copyright                                                                                                                  |    |

| D.                      | 1989 onwards.                         | . Most theses may be co                           | opied.                                                                                                                                                 |    |

| This th                 | esis comes wi                         | ithin category D.                                 |                                                                                                                                                        |    |

|                         | This copy has                         | been deposited in the L                           | ibrary of UCL                                                                                                                                          |    |

|                         |                                       | s been deposited in the<br>Street, London WC1E 7  | e University of London Library, Senate<br>HU.                                                                                                          |    |

# Low-Power Low-Voltage Analogue-to-Digital Converter Design for Mobile Video and Wireless Applications

By

# ADENIRAN, Olujide Adeyemi

A thesis submitted for the degree of Doctor of Philosophy

August 2006

Department of Electrical and Electronic Engineering

University College London

London, United Kingdom

UMI Number: U591789

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### UMI U591789

Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

## **Abstract**

With the rapid embracing and deployment of Wideband Code Division Multiple Access (WCDMA)-based Third Generation (3G) mobile networks [1] in Europe and East Asia and with the ratification of the Digital Video Broadcast – Handheld (DVB-H) - terrestrial television for battery-powered mobile devices standard in Europe [2], minimization of hand-set power consumption is becoming a key requirement. Higher baseband bandwidth is necessary for these enhanced wireless and mobile broadcast services, which translates to an increase in battery power utilization over existing second generation (2.xG) technology-enabled devices.

The Analogue-to-Digital Converter (ADC) that does the transformation of received analogue baseband signals to the digital domain for digital demodulation and data extraction consumes some portion of the receiver front-end power budget and its minimization will contribute significantly to overall elongation of mobile device battery life. This research focuses on the design of power-efficient Nyquist and Over-sampled ADCs for DVB-H and GSM/WCDMA applications with the specific contributions to knowledge being the determination of optimal partitioning of pipeline ADCs for low power consumption, novel sampling switch linearization circuit for use in the design of high dynamic range Delta-Sigma ( $\Delta\Sigma$ ) ADCs and novel power and area efficient background calibration schemes for low-voltage high-speed 12-bit and higher resolution pipeline ADCs. A number of silicon devices were designed and fabricated (or in the process of fabrication) in the course of the research viz.

- A 10-bit 20.48 MS/s 1.5 V optimally partitioned pipeline ADC silicon in 0.35 μm CMOS technology for mobile DVB-H with measured results showing only 19 mW power consumption, 100 MHz Effective Resolution Bandwidth (ERBW), 56 dB Signal-to-Noise Ratio (SNR), 60 dB Spurious Free Dynamic Range (SFDR) and an ultra-low 0.19 pJ/conversion energy consumption, one of the lowest reported for a measured device in the literature.

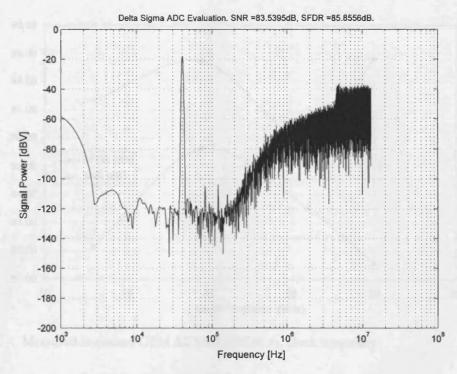

- A 13-bit 26 MS/s 135 kHz bandwidth, 2.7 V switched-capacitor ΔΣ ADC silicon in 0.35 μm BiCMOS technology for GSM frequencies with linearised sampling switch, achieving measured performance of 85.8 dB SFDR, 83.5 dB SNR and consuming 7 mW.

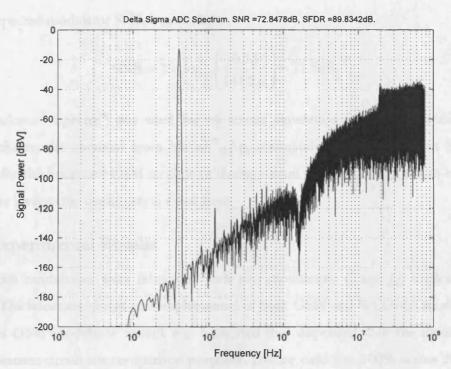

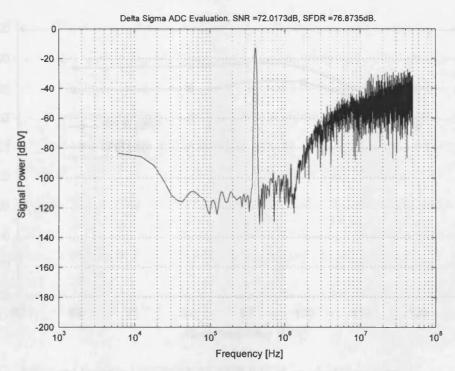

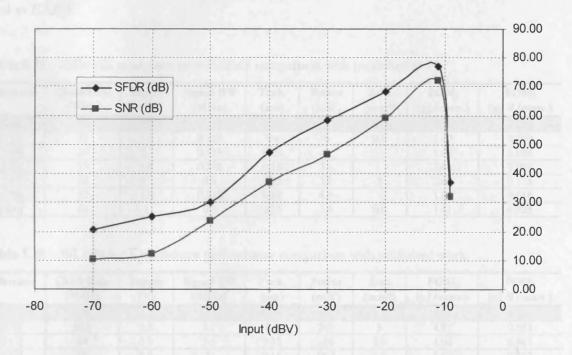

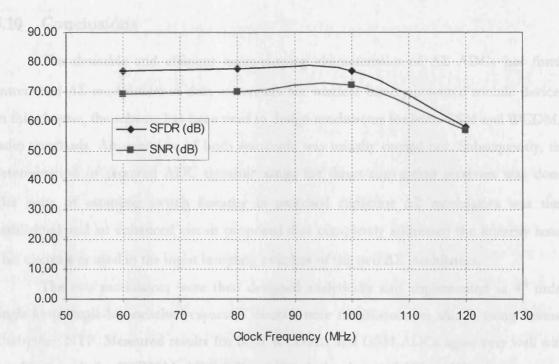

- An 11-bit 153.6 MS/s 1.92 MHz bandwidth, 2.7 V switched-capacitor ΔΣ ADC silicon in 0.35 μm BiCMOS technology for WCDMA frequencies with linearised

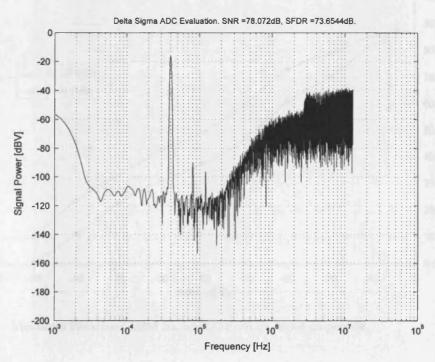

- sampling switch, achieving measured performance of 76.9 dB SFDR, 72 dB SNR and consuming 14 mW.

- A 12-bit 120 MS/s 1.2 V pipeline ADC with novel digital background calibration in 0.12 µm CMOS technology with over 85.5 dB simulated SFDR, 72.1 dB simulated SNR and consuming an estimated 100 mW.

# Acknowledgements

I still can remember that day in the latter part of 2001 when I accosted Dr. Robin Miller, my then Manager and asked about the possibility of working part-time on my PhD and my employer, Sony UK partly sponsoring me. It was however a pyrrhic victory when the PhD approval eventually came but the group I was working for had ceased to exist and Dr. Miller no longer in Sony to hear the news. Many thanks however, to him for all his effort to make it all happen and to Trisha Western, our then Human Resources Manager for authoring all the required paperwork and contracts. I could then begin the search for a suitable university and finally ended up in November 2002 with a young dynamic analogue integrated circuit design research group in University College London (UCL) headed by Dr. Andreas Demosthenous after a series of interviews.

I am also very grateful to Dr. Chris Clifton, our then Director of Wireless Technologies who actually took time off his busy schedule to visit UCL with me in order to chart out my progress path and agree a research focus. His advice on my focusing on ADC research was visionary as little would we have known then how the dependency of telecommunication and broadcast sub-systems on data converters will increase with the incessant shrink in device geometry.

Appreciation also goes to Murakami-san, Managing Director of the Sony UK Semiconductor Design Centre, Tanabe-san, my present Manager and General Manager of Wireless IC products, Dr. Sam Atungsiri, Consultant DSP Engineer and one of my industrial supervisors, Dr. Randeep Soin (my other industrial supervisor and a former Sony employee), Kawasaki-san (my former Manager) and Anthony Eaton (my former Manager and a former Sony employee) for all their support during the research period. In addition, Sony SDC is much appreciated for partly funding the research and for creating a stimulating environment for research work.

I also thank Lee Heagney, Scott Landers and Dr. Tom Crummey of the UCL Electronic and Electrical Engineering Department IT Support group for all their help in enabling me remotely access the high-performance departmental servers and integrated circuit design software from the comfort of my home computer sixty miles away thus saving me tons on transportation costs. The complete recovery of my design database after a freak deletion was also really appreciated. The help rendered by Mike Brent in regularly updating the CAD tools and debugging new process technology kits is much appreciated.

My late parents (both transitioned during the research period) are also remembered with affection and appreciated for honoring my insistence to do Electrical & Electronic

Engineering instead of Medicine for my Bachelors degree and for all their support during my various post-graduate studies.

Appreciation goes to my supervisor par excellence, Dr. Andreas Demosthenous for all his support, tutelage, motivation, empathy and help and to Angela, his wife and his children for their understanding (I once kept Andreas until midnight at UCL whilst trying to prepare a chip for tape-out...). It has been a fulfilling experience working with him and he remains a very good friend. To Iasonas, Mladen and Billy and all other co-researchers in Andreas's group, the periods of discourse over circuit and layout techniques were always very stimulating.

To my dear lovely wife, Funmi who had to bear with my idiosyncratic and monosyllabic responses when engrossed in research-related work after hours and the incessant wakefulness as the bedroom door slowly squeaks (I should have oiled it) in the early hours of the morning heralding my departure from my computer and my arrival at the bedstead. And for the periods when all motivation goes out of the window and I get completely disorientated and lost downstairs flipping the television channels ... she knows just how to banish me back to the Spartan study ... you are much appreciated and a wife indeed.

And to our adorable son, Mikun who was born amid the throes of putting the thesis framework together as the research neared completion. Watching him rock gently and babble in his swing as I type at nights or seeing him smile delightfully back at me as I make silly faces and sing even sillier songs to him literally sky-rocket motivational levels ... Suddenly, it all seems worth it all ...

I also wish to thank both the internal and external examiners of the thesis, Dr. David Haigh and Prof. Izzet Kale respectively, for an excellent and thorough review of the thesis and the very stimulating technical discussions enjoyed during the PhD Viva.

Finally, great appreciation to my awesome Lord and Savior Jesus Christ and to God my Father who knew I would need a Savior two thousand years later when He sent His son to save my soul and "in Him I live, and move and have my being" Acts 17:28 KJV paraphrased.

# **Contents**

| Acknowl   | ledgements                                           | 4  |

|-----------|------------------------------------------------------|----|

|           | ······································               |    |

|           | ables                                                |    |

| List of F | igures                                               | 10 |

|           | of Terms                                             |    |

| 1.0 In    | ntroduction                                          | 18 |

| 1.1       | Historical Overview of Digital Communication Systems | 18 |

| 1.2       | Motivation for the Research Work                     | 21 |

| 1.3       | Thesis Organization                                  | 23 |

| 1.4       | Research Contributions                               | 24 |

| 1.5       | Publications                                         |    |

| 2.0 A     | nalogue to Digital Converter Fundamentals            | 26 |

| 2.1       | Analogue and Discrete-time Signals                   | 26 |

| 2.2       | ADC Transfer Function and Quantization Noise         | 28 |

| 2.3       | ADC Specification Terminologies                      | 33 |

| 2.3.1     |                                                      |    |

| 2.3.2     | Signal to Noise and Distortion Ratio (SNDR)          | 34 |

| 2.3.3     | Spurious Free Dynamic Range (SFDR)                   | 34 |

| 2.3.4     | Total Harmonic Distortion (THD)                      | 34 |

| 2.3.5     | 5 Resolution                                         | 34 |

| 2.3.6     | Effective Number of Bits (ENOB)                      | 35 |

| 2.3.7     | · · · · · · · · · · · · · · · · · · ·                |    |

| 2.3.8     | B Effective Resolution Bandwidth (ERBW)              | 35 |

| 2.3.9     | Sub-sampling                                         | 35 |

| 2.3.1     | • •                                                  |    |

| 2.3.1     | 11 Integral Nonlinearity (INL)                       | 36 |

| 2.3.1     | 12 Differential Nonlinearity (DNL)                   | 37 |

| 2.3.1     |                                                      |    |

| 2.3.1     | 14 Offset Error                                      | 38 |

| 2.3.1     | 15 Gain Error                                        | 38 |

| 2.4       | ADC Testing                                          | 39 |

| 2.5       | ADC Performance Figures of Merit                     | 40 |

| 2.6       | Conclusions                                          | 41 |

| 3.0 A     | nalogue to Digital Converter Architectures           |    |

| 3.1       | The Flash ADC Architecture                           | 42 |

| 3.1.1     | Comparator Input Offset                              | 43 |

| 3.1.2     | 2 Comparator Input capacitance                       | 43 |

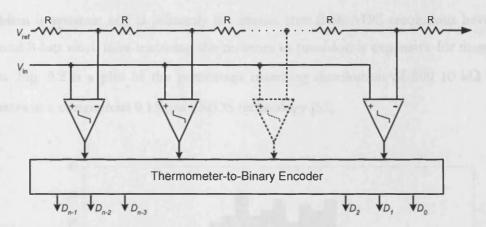

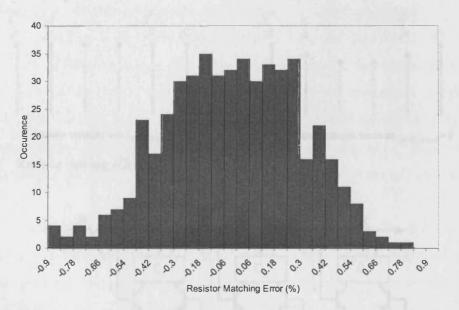

| 3.1.3     | Resistor Network Mismatch                            | 43 |

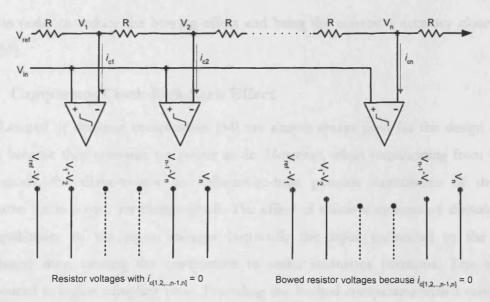

| 3.1.4     | Resistor Voltage Bowing Effect                       | 44 |

| 3.1.5     | Comparator Clock Kick-back Effect                    | 46 |

| 3.1.6     | 6 Bubble Errors                                      | 46 |

| 3.1.7     | Encoder Propagation Delay                            | 47 |

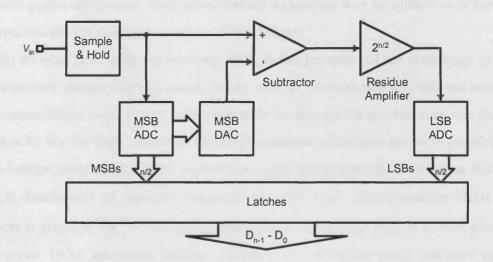

| 3.2       | Two-Step Flash ADC Architecture                      |    |

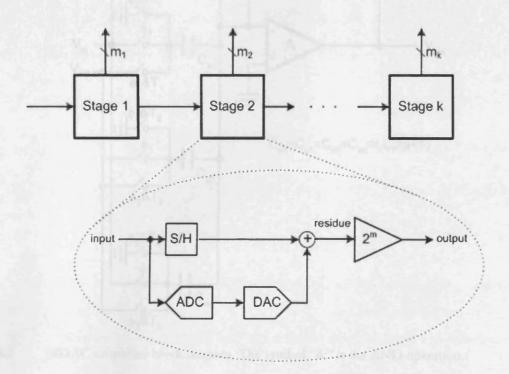

| 3.3       | Pipeline ADC Architecture                            |    |

| 3.3.1     | Digital Error Correction in Pipeline ADCs            | 52 |

| 3.4       | Time-Interleaved ADC Architecture                    |    |

| 3.5       | Folding and Interpolating ADC Architecture           | 54 |

| 3.6       | Integrating ADC Architecture                         | 56 |

| 3.7                      | Successive Approximation ADC Architecture                         | 57                              |

|--------------------------|-------------------------------------------------------------------|---------------------------------|

| 3.8                      | Cyclic/Algorithmic ADC Architecture                               | 58                              |

| 3.9                      | $\Delta\Sigma$ ADC Architecture                                   |                                 |

| 3.10                     | Conclusions                                                       |                                 |

|                          | Pipeline ADC Design for Mobile DVB-H Receivers                    |                                 |

| 4.1                      | DVB-H Overview                                                    |                                 |

| 4.1                      |                                                                   |                                 |

| 4.1                      | .2 DVB Classification and COFDM Demodulator Architecture          | 65                              |

| 4.1                      | .3 COFDM Fundamentals                                             | 67                              |

| 4.1                      |                                                                   | 69                              |

| 4.2                      | System Consideration for DVB-H Receiver                           | 70                              |

| 4.3                      | •                                                                 | 72                              |

| 4.3                      | ·                                                                 |                                 |

| 4.3                      | - 11 / D                                                          | 75                              |

| 4.3                      | 3.3 Amplifier Power Consumption                                   | 77                              |

|                          | 4.3.3.1 Single-Stage OTA                                          | 79                              |

|                          | 4.3.3.2 Two-Stage Miller OTA                                      | 80                              |

| 4.3                      | 6.4 Comparator Power Consumption                                  | 82                              |

| 4.3                      | - I I                                                             |                                 |

| 4.3                      | 1                                                                 |                                 |

| 4.4                      | ADC Design using Optimized Topology                               | 85                              |

| 4.4                      |                                                                   |                                 |

| 4.4                      |                                                                   |                                 |

| 4.4                      |                                                                   |                                 |

| 4.4                      | 1                                                                 |                                 |

| 4.5                      | 1                                                                 |                                 |

| 4.6                      | Conclusions                                                       |                                 |

|                          | Delta-Sigma ADC Design for Mobile GSM & WCDMA Receivers           |                                 |

| 5.1                      | GSM System Overview                                               |                                 |

|                          | .1 GSM Radio Link Considerations                                  |                                 |

|                          | 5.1.1.1 Multiple Access and Channel Structure                     | 99                              |

|                          | 5.1.1.2 Channel Coding and Modulation                             |                                 |

|                          | .2 GSM Enhancements                                               |                                 |

|                          | 5.1.2.1 GPRS                                                      |                                 |

|                          | 5.1.2.2 EDGE                                                      |                                 |

| 5.2                      | WCDMA System Overview                                             |                                 |

| 5.2                      | 1 ,                                                               |                                 |

| 5.2                      |                                                                   |                                 |

|                          | 5.2.2.1 Coding                                                    |                                 |

|                          | 5.2.2.2 Spreading                                                 |                                 |

| 5.2                      | 1                                                                 |                                 |

| 5.2                      |                                                                   |                                 |

|                          | 5.2.4.1 HSDPA                                                     |                                 |

|                          | 5/4/ HSUPA                                                        | 105                             |

| E 7                      |                                                                   |                                 |

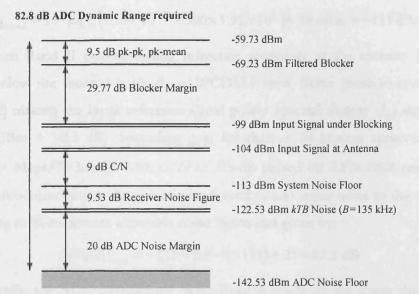

| 5.3                      | GSM ADC Dynamic Range                                             | 105                             |

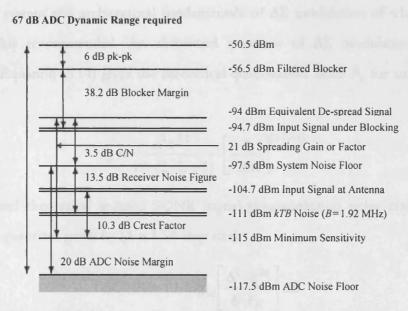

| 5.4                      | GSM ADC Dynamic Range WCDMA ADC Dynamic Range                     | 105<br>108                      |

| 5.4<br>5.5               | GSM ADC Dynamic Range<br>WCDMA ADC Dynamic Range<br>ΔΣ Modulation | 105<br>108<br>110               |

| 5.4<br>5.5<br>5.6        | GSM ADC Dynamic Range                                             | 105<br>108<br>110               |

| 5.4<br>5.5<br>5.6<br>5.7 | GSM ADC Dynamic Range                                             | 105<br>108<br>110<br>111        |

| 5.4<br>5.5<br>5.6        | GSM ADC Dynamic Range                                             | 105<br>108<br>110<br>111<br>122 |

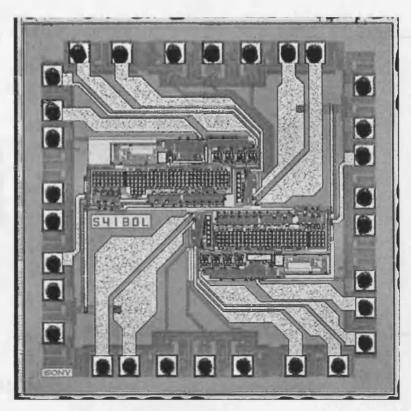

| 5.9.1                 | GSM ΔΣ ADC Silicon                                                | 133 |

|-----------------------|-------------------------------------------------------------------|-----|

| 5.9.2                 | 2 WCDMA ΔΣ ADC Silicon                                            | 136 |

| 5.10                  | Conclusions                                                       |     |

| 6.0 C                 | alibration Techniques for High Resolution Multi-Bit Pipeline ADCs | 141 |

| 6.1                   | Correctible Pipeline ADC Errors                                   | 142 |

| 6.1.1                 | 1                                                                 |     |

| 6.1.2                 |                                                                   |     |

| 6.1.3                 |                                                                   |     |

| 6.2                   | ADC Calibration Schemes                                           |     |

| 6.3                   | Proposed Low-Power Segmented Calibration Scheme I                 |     |

| 6.4                   | Proposed Low-Power Segmented Calibration Scheme II                |     |

| 6.5                   | Calibrated ADC Circuit Design                                     |     |

| 6.6                   | System-Level Simulation Results                                   |     |

| 6.6                   | Conclusions                                                       |     |

|                       | onclusions                                                        |     |

|                       | x A ΔΣ Modulation Overview                                        |     |

| A.1                   | Continuous-time vs. Discrete-time $\Delta\Sigma$ Modulators       |     |

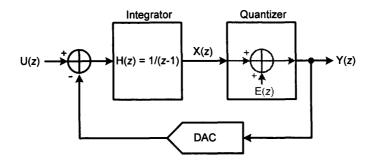

| A.2                   | First-order $\Delta\Sigma$ Modulator                              | 163 |

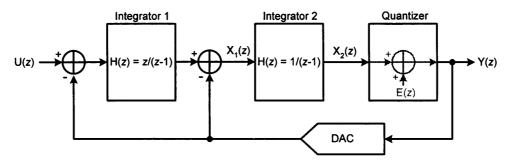

| A.3                   | Second-order $\Delta\Sigma$ Modulator                             | 165 |

| A.4                   | Higher-Order $\Delta\Sigma$ Modulators and Stability Issues       | 167 |

| A.5                   |                                                                   |     |

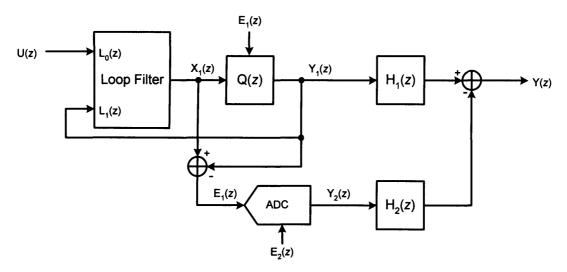

|                       | .5.1 Leslie-Singh Cascade Structure                               |     |

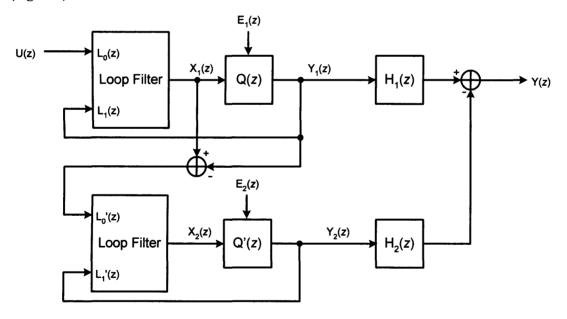

| A                     | .5.2 Multi-Stage Noise Shaping (MASH) Cascade Structure           |     |

| A.6                   |                                                                   |     |

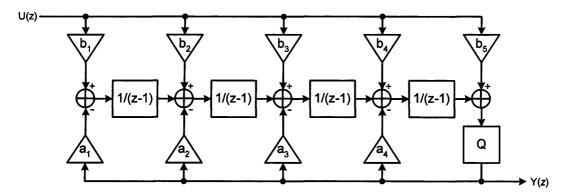

|                       | .6.1 Loop Filter with Distributed Feed-forward and Feedback Paths |     |

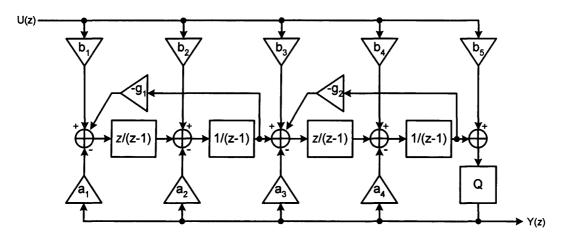

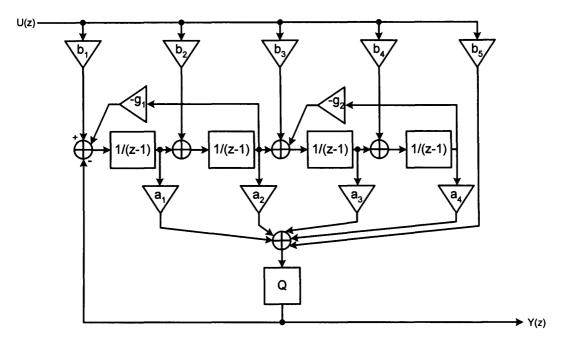

|                       | .6.2 Loop Filter with Feed-forward, Feedback and Resonator Paths  |     |

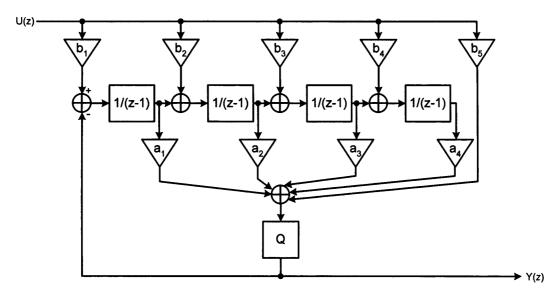

|                       | .6.3 Loop Filter with Weighted Feed-forward Summation             |     |

| A.7                   | ΔΣ Modulator Noise Transfer Functions                             |     |

| A.8                   | ΔΣ Modulators with Multi-Bit Quantizers                           |     |

| A.9                   | Correction of $\Delta\Sigma$ Modulator Feedback DAC Imperfections |     |

|                       | .9.1 Dynamic Element Matching                                     |     |

|                       | .9.2 Mismatch Error Shaping                                       |     |

|                       | .9.3 Rotated Data Weighted Averaging                              |     |

|                       | .9.4 Individual Level Averaging                                   |     |

|                       | .9.5 Vector-Based Mismatch Shaping                                |     |

|                       | .9.6 Tree Structure Element Selection                             |     |

| Appendi               |                                                                   |     |

| <b>гъррена</b><br>В.1 | Matlab script for GSM $\Delta\Sigma$ Modulator simulation         |     |

|                       | •                                                                 |     |

| B.2                   | Matlab script for WCDMA ΔΣ Modulator simulation                   |     |

| B.3                   | Matlab script for Calibration ΔΣ Modulator simulation             |     |

|                       | x C Matlab Processing Scripts                                     |     |

| C.1                   | Matlab script for ΔΣ Modulator FFT Analysis                       |     |

| C.2                   | Matlab script for Nyquist ADC FFT Analysis                        |     |

| Bibliogra             | aphy                                                              | 191 |

# List of Tables

| Table 1.1         | Power Consumption Break-down for DVB-T Demodulator Subsystem                          | 22    |

|-------------------|---------------------------------------------------------------------------------------|-------|

| Table 2.1         | Quantization noise energy for disparate ADC input signals                             |       |

| Table 3.1         | ADC architectural classification                                                      |       |

| Table 4.1         | Post-Layout OTA simulated performance summary.                                        | 90    |

| Table 4.2         | 10-bit ADC performance summary.                                                       | 95    |

| Table 4.3         | 10-bit ADC Performance comparison with published work                                 | 95    |

| Table 5.1         | GSM uplink and downlink frequency spectrum allocation                                 | 99    |

| Table 5.2         | WCDMA uplink and downlink frequency spectrum allocation                               | 103   |

| Table 5.3         | Representative 2 <sup>nd</sup> order Butterworth filtering of GSM blockers            | 107   |

| Table 5.4         | Representative 2 <sup>nd</sup> order Chebyshev filtering of WCDMA Blockers            | 109   |

| Table 5.5         | Theoretical and simulated GSM $\Delta\Sigma$ modulator SQNR (OSR = 96)                | 122   |

| Table 5.6         | Modulator loop filter coefficients for Butterworth NTF                                | 124   |

| Table 5.7         | Quantized modulator loop filter coefficients for Butterworth NTF                      | 124   |

| Table 5.8         | GSM $\Delta\Sigma$ modulator OTA performance summary                                  | 129   |

| Table 5.9         | Theoretical and simulated WCDMA $\Delta\Sigma$ modulator SQNR (OSR = 40)              | 131   |

| <b>Table 5.10</b> | WCDMA ΔΣ modulator OTA performance summary                                            | 132   |

| <b>Table 5.11</b> | GSM $\Delta\Sigma$ modulator performance comparison with published work               | 139   |

| <b>Table 5.12</b> | WCDMA $\Delta\Sigma$ modulator performance comparison with published work             | 139   |

| <b>Table 5.13</b> | GSM and WCDMA ΔΣ ADC performance summary                                              | 140   |

| Table 6.1         | Calibrated 12-bit pipeline ADC specifications                                         | 154   |

| Table 6.2         | Simulated MDAC amplifier performance summary                                          | 155   |

| Table 6.3         | Modulator loop filter coefficients for 2 <sup>nd</sup> order Butterworth NTF          | 156   |

| Table 6.4         | Quantized modulator loop filter coefficients for 2 <sup>nd</sup> order Butterworth NT | F.157 |

| Table 6.5         | Calibrated 12-bit pipeline ADC performance summary                                    | 160   |

| Table A.1         | Continuous-time vs. Discrete-time $\Delta\Sigma$ modulators                           | 163   |

| Table A.2         | Theoretical and simulated $\Delta\Sigma$ modulator SQNR for OSR = 128                 | 168   |

| Table A.3         | Theoretical multi-bit quantizer $\Delta\Sigma$ modulator SQNR at OSR of 128           | 177   |

# List of Figures

| Fig. 1.1  | Simplified block diagram of a direct conversion tuner for DVB-H reception.     |    |

|-----------|--------------------------------------------------------------------------------|----|

| Fig. 1.2  | Discharge profile of a 4.2 V 1.5 Ah lithium-ion battery.                       | 22 |

| Fig. 2.1  | Representative sinusoidal waveform with overlaid 5th and 9th harmonics         | 27 |

| Fig. 2.2  | Descriptive coherent sampling subsystem with anti-aliasing filter included     | 27 |

| Fig. 2.3  | Sampled signal spectra (a) without and (b) with anti-alias filtering used      |    |

| Fig. 2.4  | Ideal n-bit ADC block diagram.                                                 | 28 |

| Fig. 2.5  | Quantization error extraction test-bed.                                        | 29 |

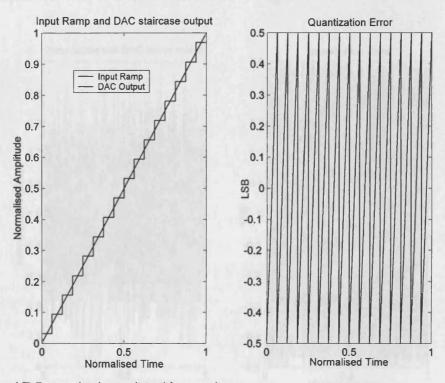

| Fig. 2.6  | ADC quantization noise with ramp input                                         | 29 |

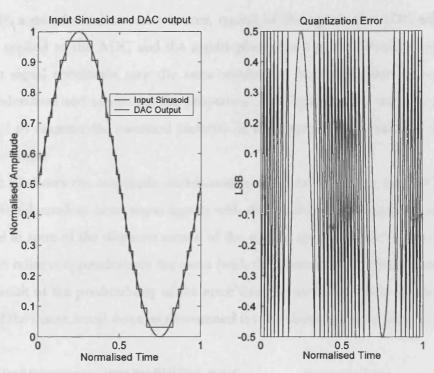

| Fig. 2.7  | ADC quantization noise with sinusoidal input                                   | 30 |

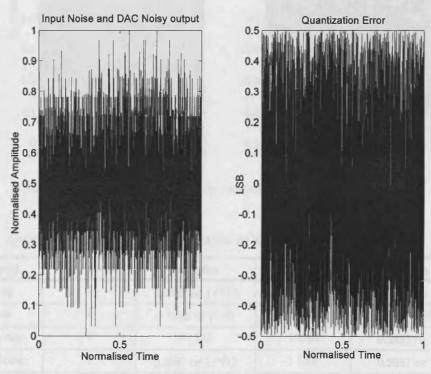

| Fig. 2.8  | ADC quantization noise with Gaussian noise input                               | 30 |

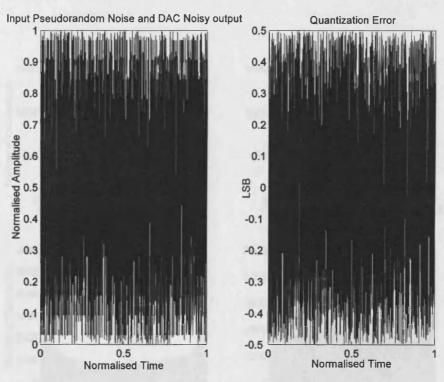

| Fig. 2.9  | ADC quantization noise with pseudo-random noise input                          | 31 |

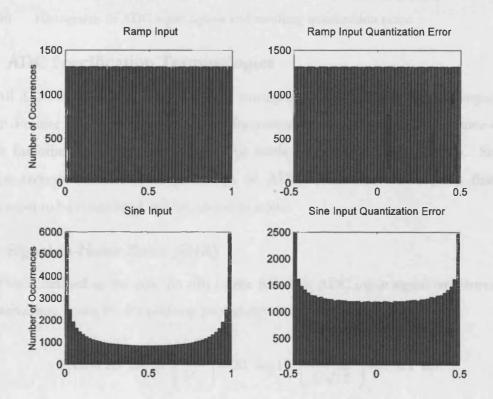

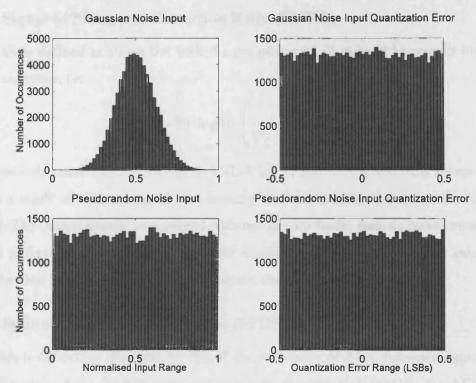

| Fig. 2.10 | Histograms of ADC input signals and resulting quantization noise               | 33 |

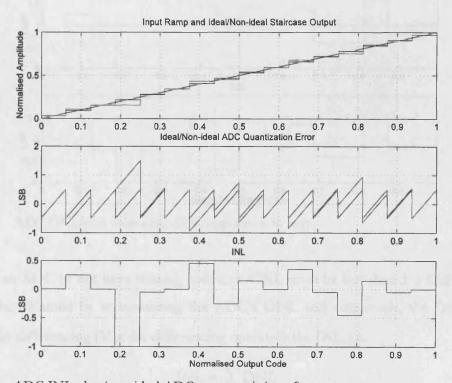

| Fig. 2.11 | ADC INL plot (non-ideal ADC response is in red)                                | 36 |

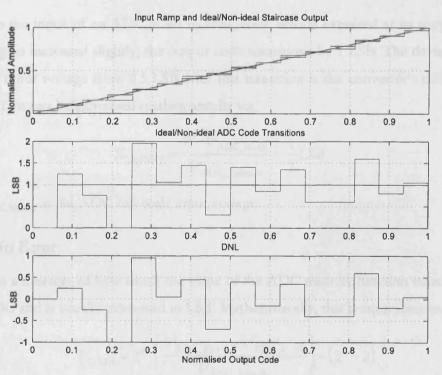

| Fig. 2.12 | ADC DNL plot (non-ideal ADC response is in red)                                | 37 |

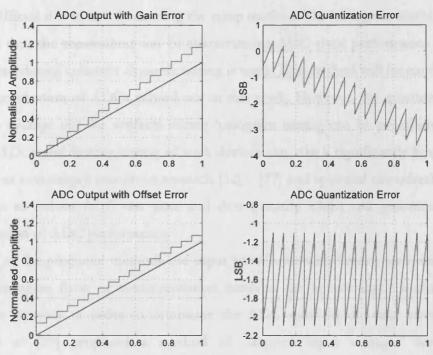

| Fig. 2.13 | Transfer response of ADCs with both offset and gain errors.                    |    |

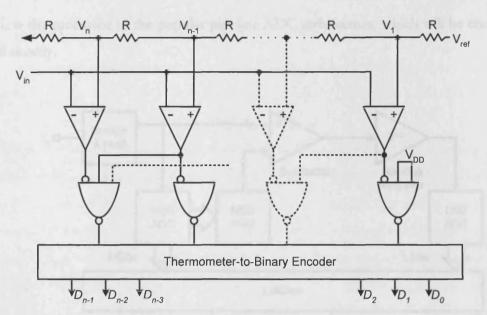

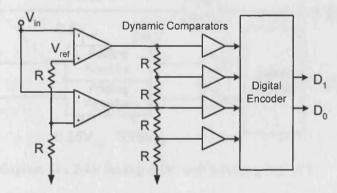

| Fig. 3.1  | Block diagram of an <i>n</i> -bit Flash ADC.                                   |    |

| Fig. 3.2  | Statistical distribution of polysilicon resistor matching for 500 resistors    |    |

| Fig. 3.3  | Resistor bowing effect in an <i>n</i> -bit bipolar flash ADC                   |    |

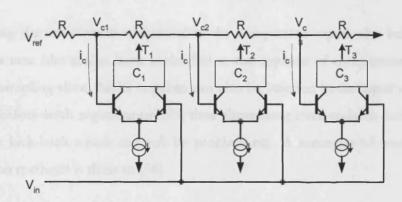

| Fig. 3.4  | Bipolar 2-bit flash ADC.                                                       |    |

| Fig. 3.5  | Single bubble removal method using 3-input NAND gates                          |    |

| Fig. 3.6  | Block diagram of a two-step flash ADC                                          |    |

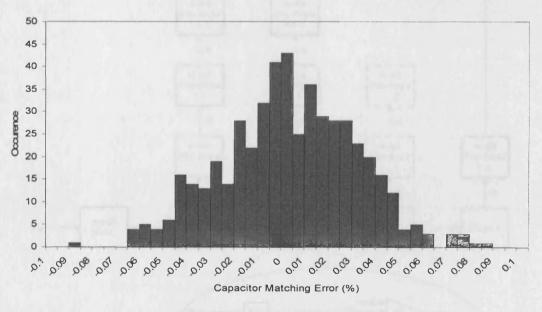

| Fig. 3.7  | Statistical distribution of MiM capacitor matching for 500 capacitors          |    |

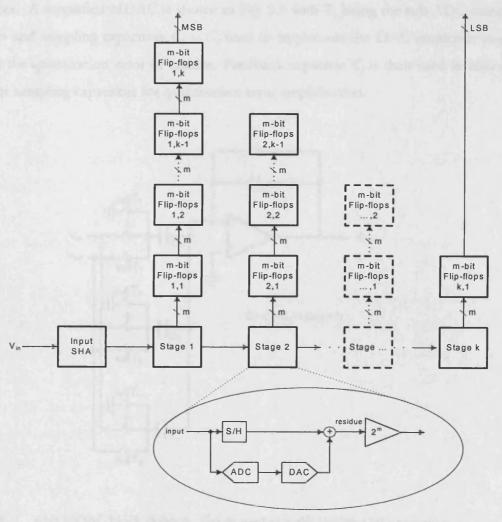

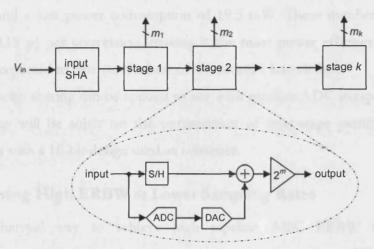

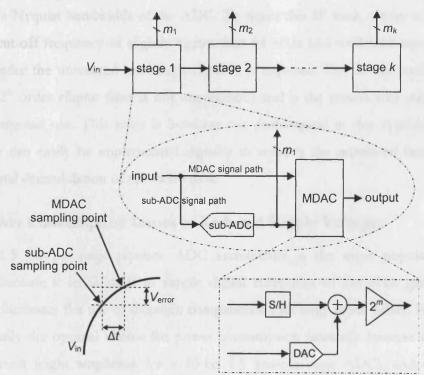

| Fig. 3.8  | Block diagram of an <i>n</i> -bit pipeline ADC where $n = k \cdot m$           |    |

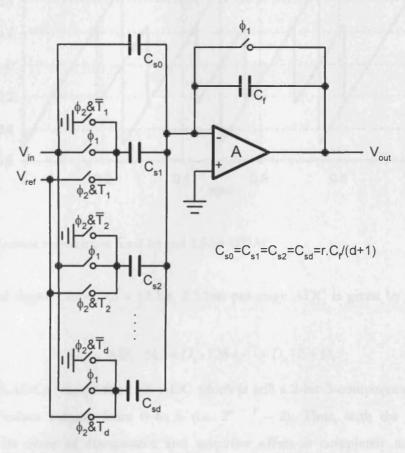

| Fig. 3.9  | n-bit MDAC block diagram. The & symbol is the logical AND operation            |    |

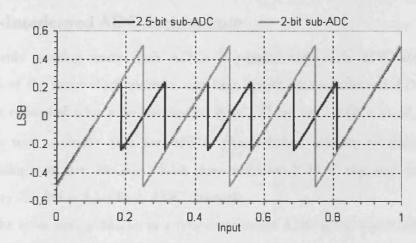

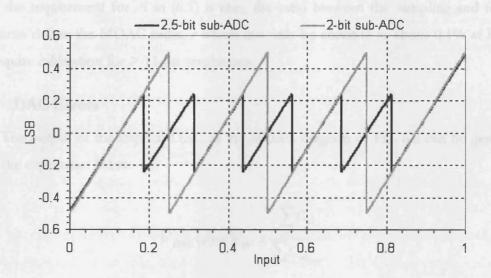

| Fig. 3.10 | Residue vs. input for an m-bit and m.5-bit MDAC.                               | 53 |

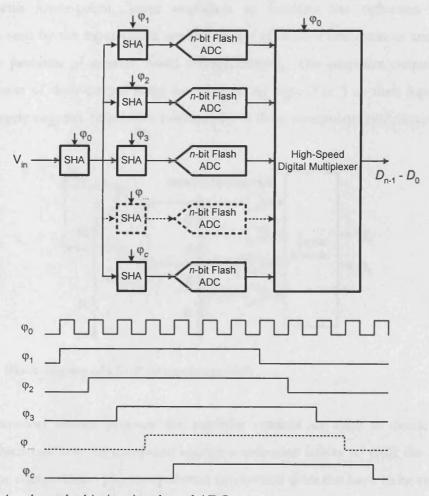

| Fig. 3.11 | A c-channel n-bit time-interleaved ADC                                         |    |

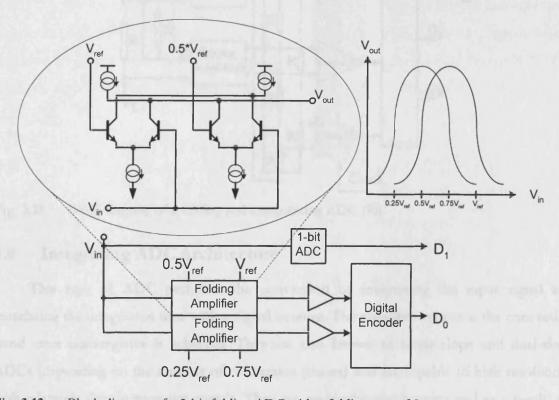

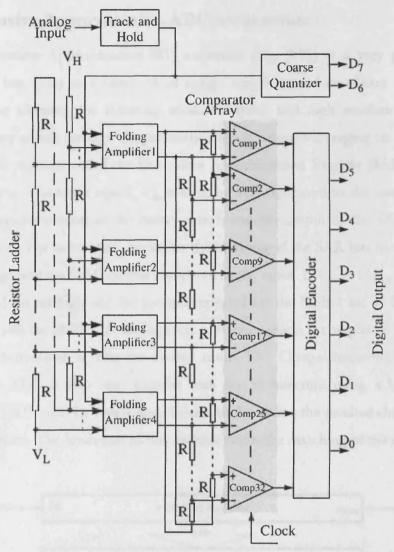

| Fig. 3.12 | Block diagram of a 2-bit interpolating ADC                                     |    |

| Fig. 3.13 | Block diagram of a 2-bit folding ADC with a folding rate of 2                  |    |

| Fig. 3.14 | Block diagram of a folding and interpolating ADC [78]                          |    |

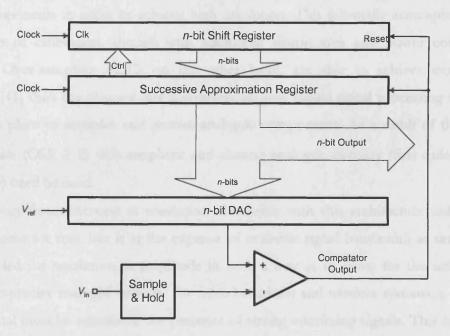

| Fig. 3.15 | The successive approximation ADC                                               |    |

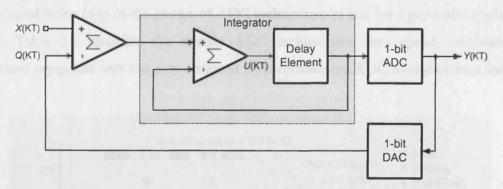

| Fig. 3.16 | First-order $\Delta\Sigma$ modulator                                           |    |

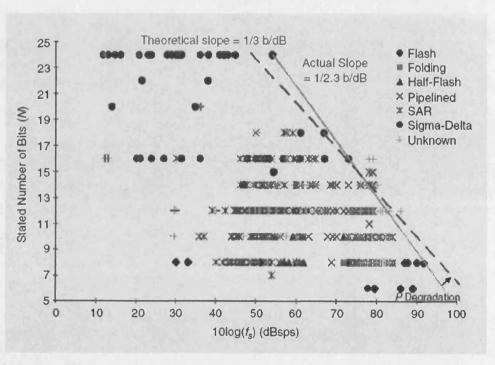

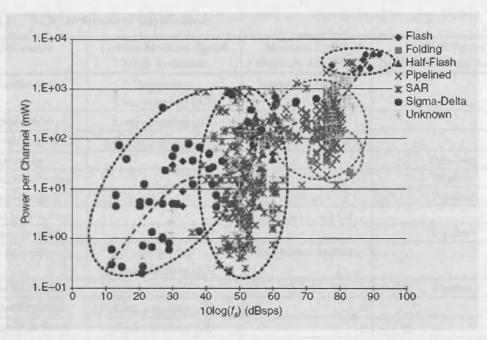

| Fig. 3.17 | Plot of selected ADC resolution vs. logarithm of sample rate [19]              |    |

| Fig. 3.18 | Plot of selected ADC power consumption vs. logarithm of sample rate [19]       |    |

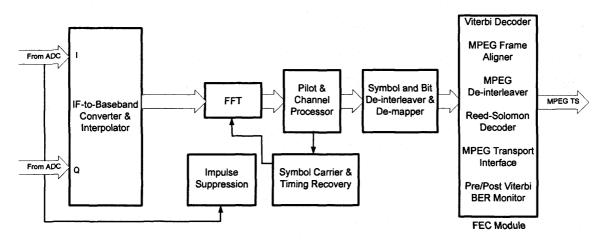

| Fig. 4.1  | Block diagram of a COFDM demodulator.                                          |    |

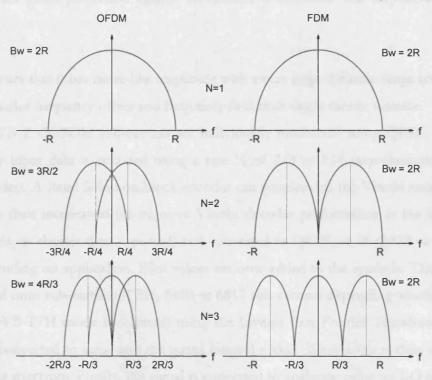

| Fig. 4.2  | OFDM multi-carrier technique vs. FDM multi-carrier technique                   |    |

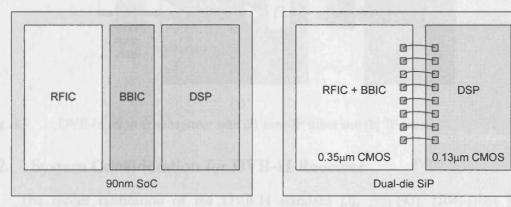

| Fig. 4.3  | SoC and SiP methods for the DVB-H sub-system silicon implementation            |    |

| Fig. 4.4  | DVB-H receiver subsystem with (a) zero-IF tuner and (b) IF tuner               |    |

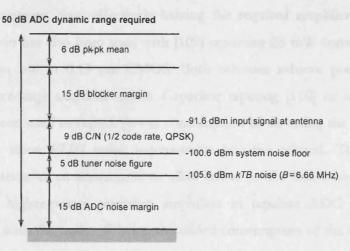

| Fig. 4.5  | ADC dynamic range specification.                                               |    |

| Fig. 4.6  | Generic pipeline ADC block diagram                                             |    |

| Fig. 4.7  | Pipeline ADC block diagram illustrating the aperture error problem             |    |

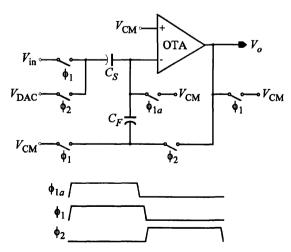

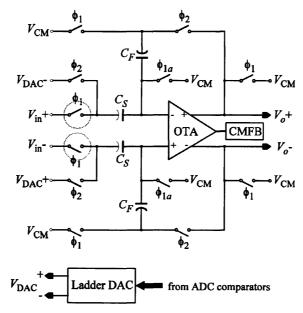

| Fig. 4.8  | Simplified ADC MDAC diagram.                                                   |    |

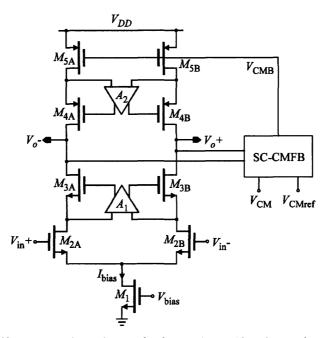

| Fig. 4.9  | Fully-differential gain-enhanced telescopic OTA schematic.                     |    |

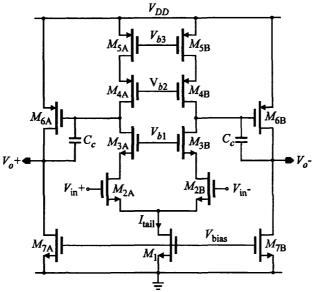

| Fig. 4.10 | Fully-differential Miller OTA schematic                                        |    |

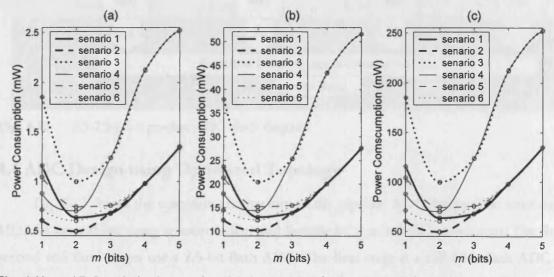

| Fig. 4.11 | ADC optimization results: $f_s = (a)$ 1 MS/s, (b) 20.48 MS/s and (c) 100 MS/s. |    |

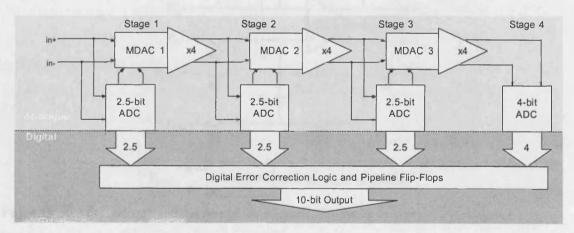

| Fig. 4.12 | 2.5-2.5-4 pipeline ADC block diagram.                                          |    |

| Fig. 4.13 | ADC MDAC architecture block diagram. The linear switches are highlighted       |    |

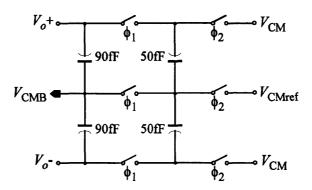

| Fig. 4.14 | Switched-capacitor CMFB circuit.                                               |    |

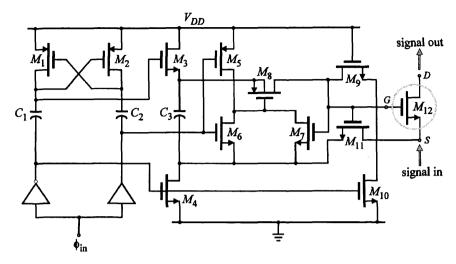

| Fig. 4.15 | Bootsd switch $(M_{12})$ schematic [115]                                       |    |

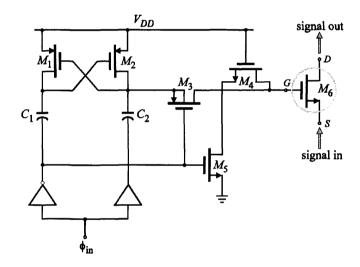

| Fig. 4.16 | Boosted switch (M <sub>6</sub> ) schematic                                     | 88 |

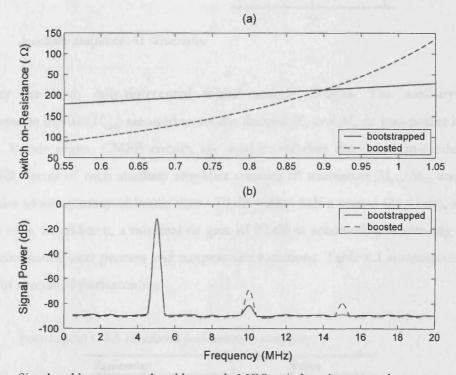

| _    | 4.17        | Simulated bootstrapped and boosted nMOS switch resistance and spectrum.                       |     |

|------|-------------|-----------------------------------------------------------------------------------------------|-----|

| _    | 4.18        | Auxiliary amplifier A1 schematic                                                              | 90  |

| _    | 4.19        | Dynamic comparator schematic.                                                                 |     |

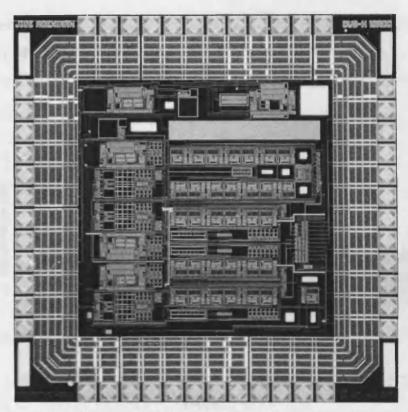

| _    | 4.20        | ADC chip microphotograph.                                                                     |     |

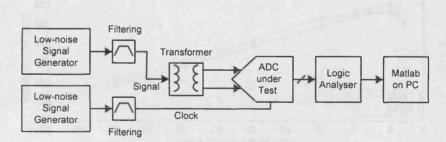

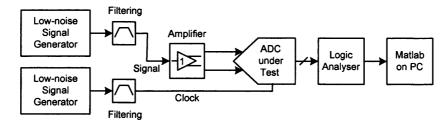

| _    | 4.21        | ADC test-bench setup                                                                          |     |

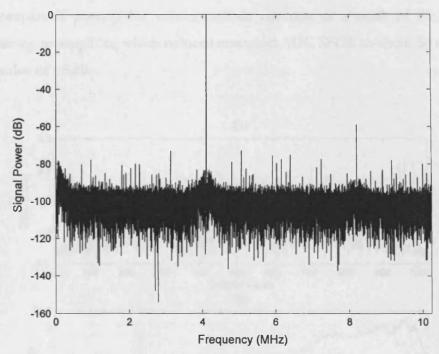

| -    | 4.22        | ADC power spectrum with 4.1 MHz tone                                                          | 93  |

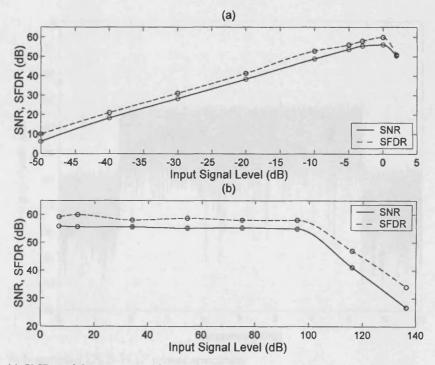

| _    | 4.23        | (a) SNR and SFDR versus input amplitude and (b) versus input frequency                        |     |

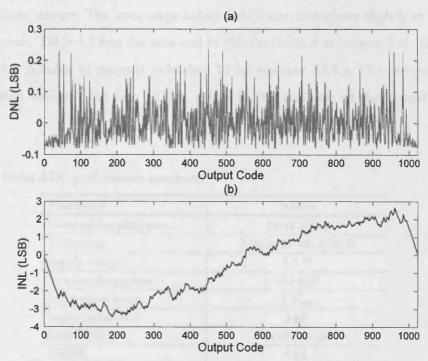

| _    | 4.24        | (a) ADC DNL plot. (b) ADC INL plot                                                            |     |

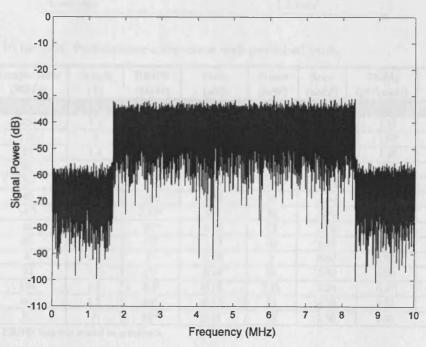

| _    | 4.25        | Sub-sampled DVB-H IF power spectrum.                                                          |     |

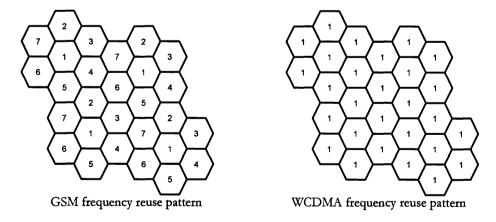

| Fig. |             | GSM and WCDMA frequency reuse pattern.                                                        |     |

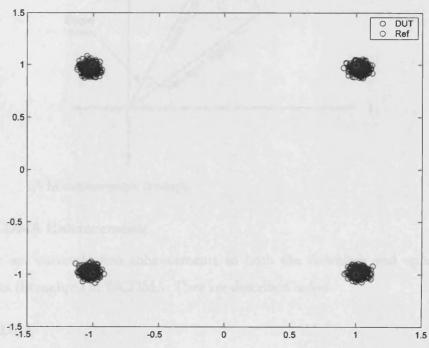

| Fig. |             | QPSK constellation display.                                                                   | 103 |

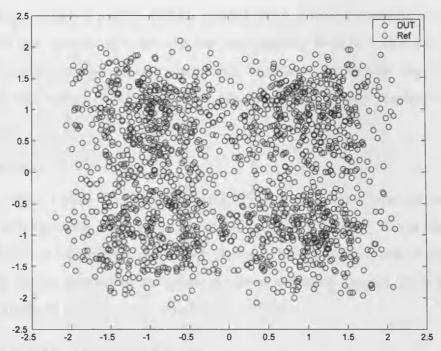

| Fig. |             | QPSK constellation display with severe channel impairment                                     | 104 |

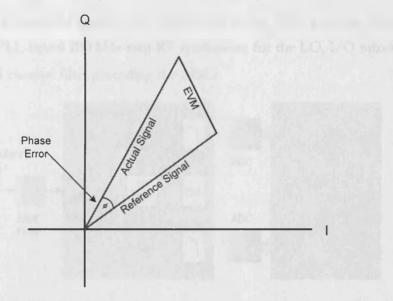

| Fig. |             | EVM measurement concept                                                                       |     |

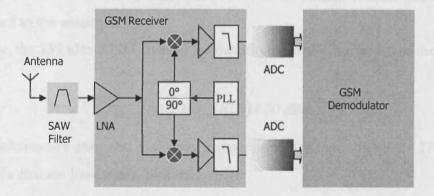

| Fig. |             | Simplified block diagram of a direct conversion GSM receiver subsystem                        |     |

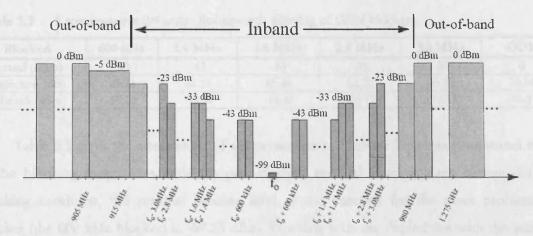

| Fig. |             | E-GSM blocking profile [143].                                                                 | 106 |

| Fig. |             | GSM ADC dynamic range specification.                                                          | 108 |

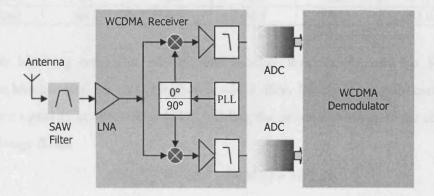

| Fig. |             | Simplified diagram of a direct conversion WCDMA receiver subsystem                            |     |

| Fig. |             | WCDMA ADC dynamic range specification                                                         |     |

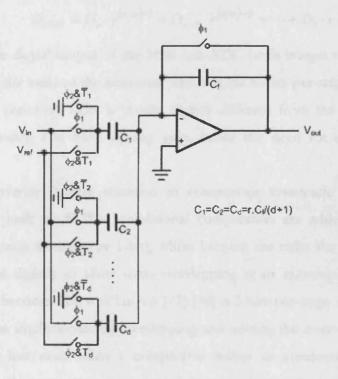

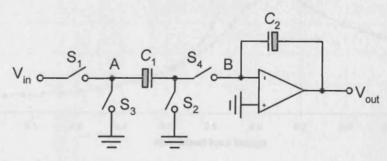

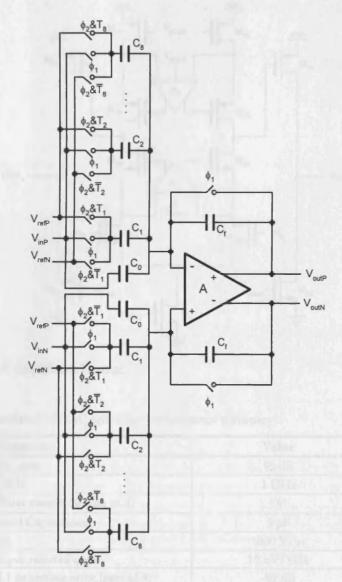

| _    | 5.10        | Parasitic-insensitive integrator topology                                                     |     |

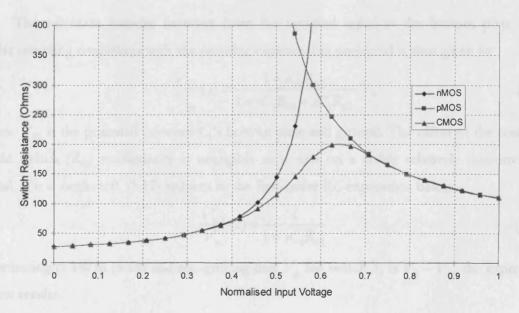

| _    | 5.11        | CMOS, nMOS and pMOS sampling switch resistance versus input                                   |     |

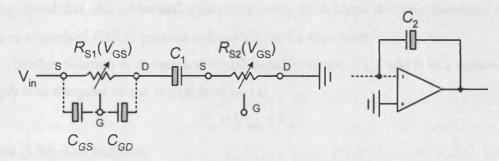

| _    | 5.12        | Non-linear sampling switch representative diagram                                             |     |

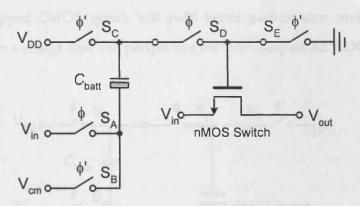

| _    | 5.13        | Bootstrap circuit using nMOS sampling switches                                                | 115 |

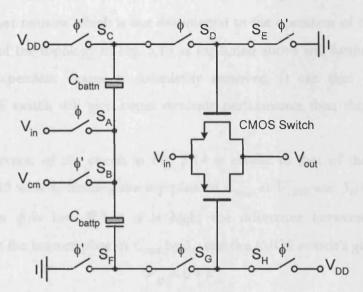

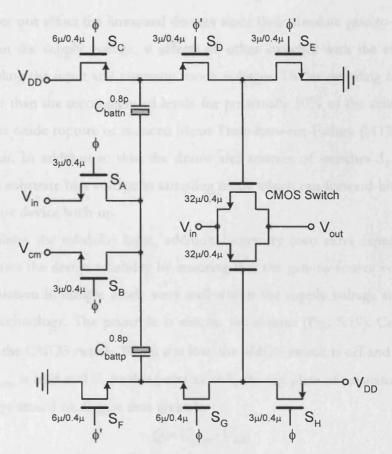

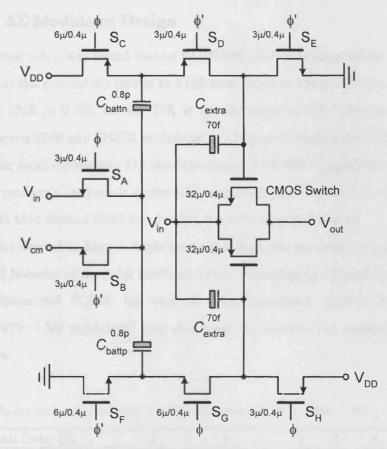

| _    | 5.14        | Simplified CMOS sampling switch lineariser circuit                                            |     |

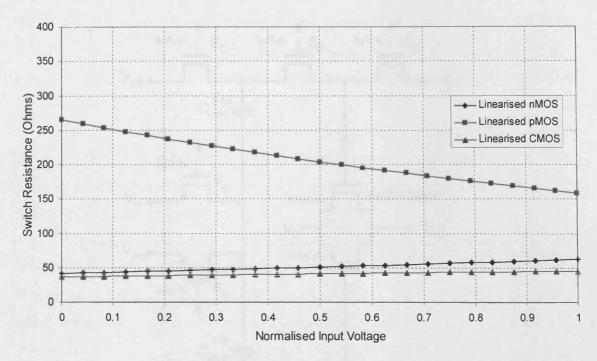

| _    | 5.15        | Linearised CMOS, nMOS and pMOS sampling switch resistance vs. input                           |     |

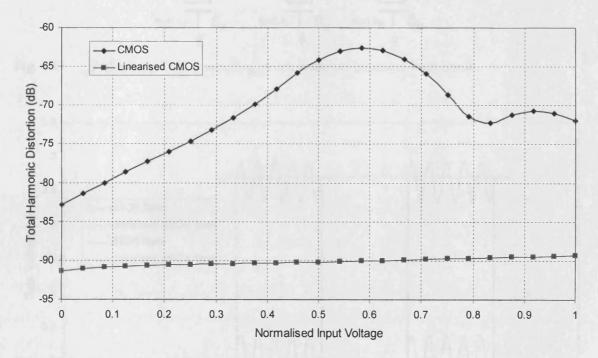

| _    | 5.16        | Linearised CMOS and conventional CMOS THD plot versus input voltage.                          |     |

| _    | 5.17        | Preliminary CMOS sampling switch lineariser transistor-level circuit                          |     |

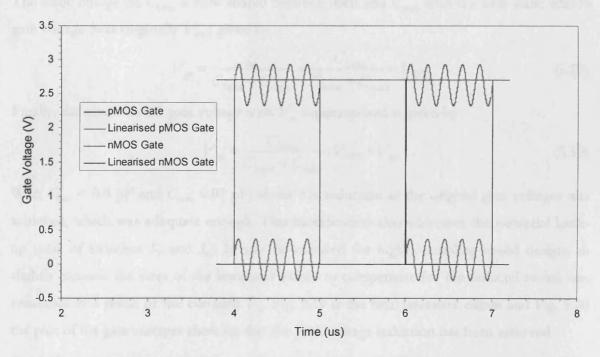

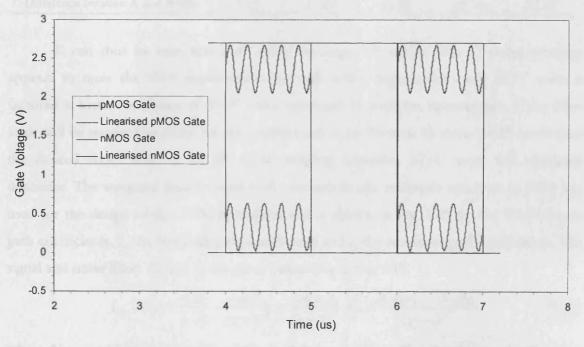

| _    | <b>5.18</b> | Gate voltages of linearised and conventional CMOS switches                                    |     |

| _    | 5.19        | Final CMOS sampling switch lineariser transistor-level circuit                                |     |

| _    | 5.20        | Gate voltages of final linearised and conventional CMOS switches                              |     |

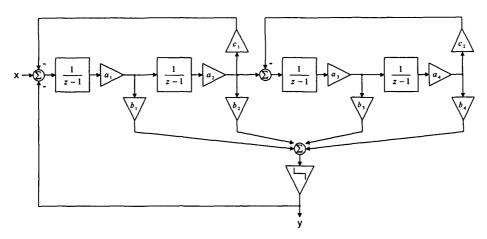

| _    | 5.21        | GSM 4th order modulation architecture.                                                        |     |

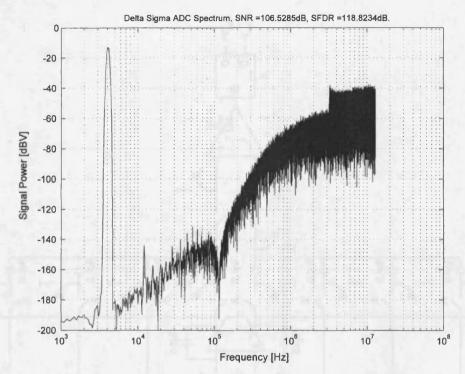

| Fig. | 5.22        | GSM $\Delta\Sigma$ modulator power spectrum plot with the zero at 115.7 kHz                   | 125 |

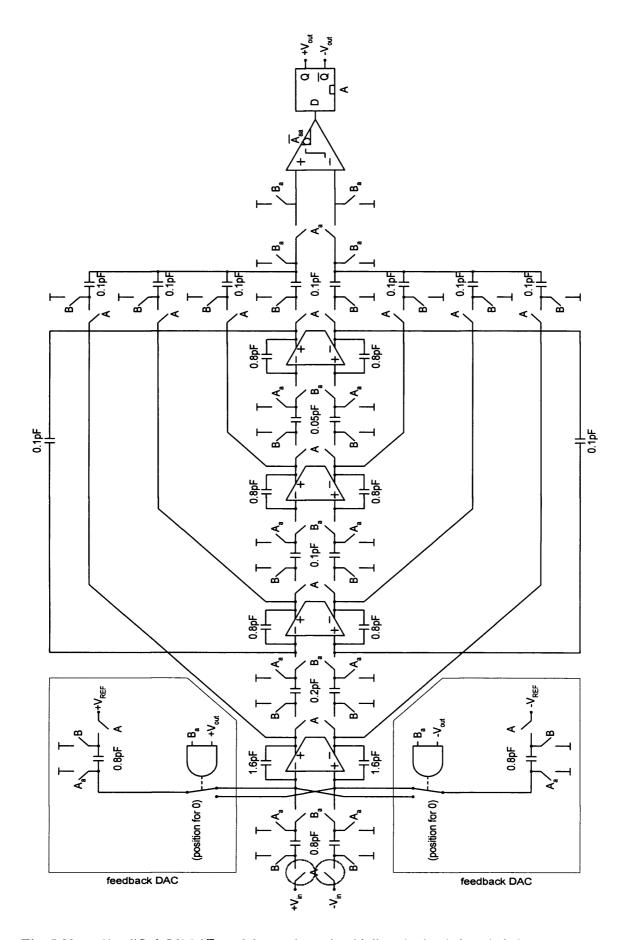

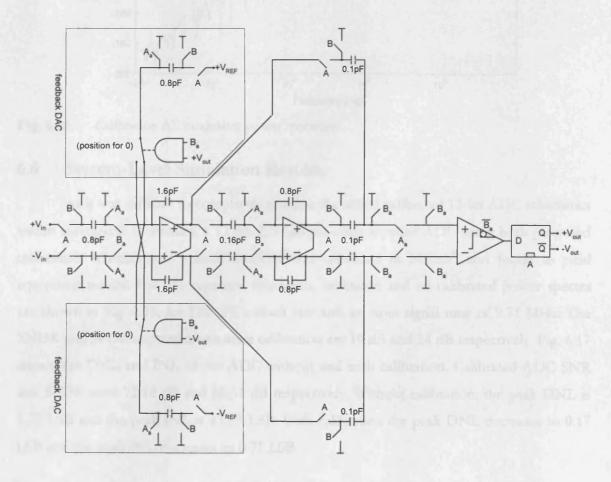

| Fig. | 5.23        | Simplified GSM $\Delta\Sigma$ modulator schematic with linearised switches circled            |     |

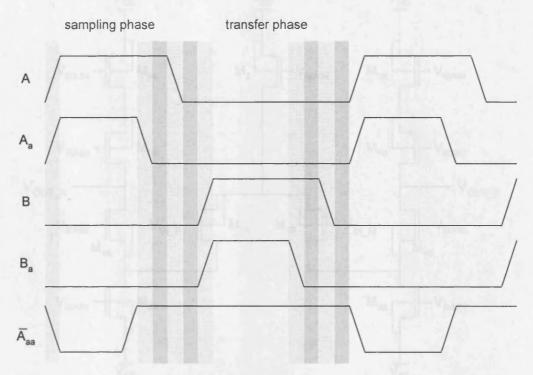

| Fig. | 5.24        | Clock generator timing diagram with 4-phase scheme [84], [190] used                           | 127 |

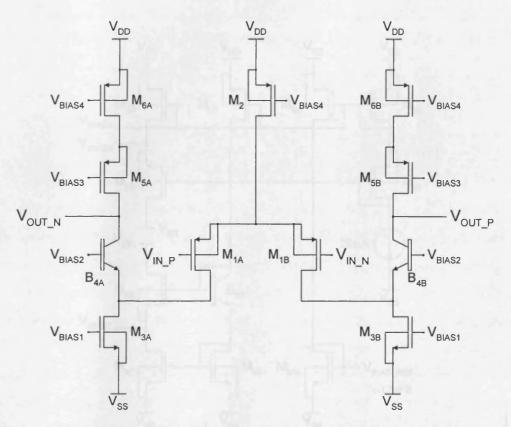

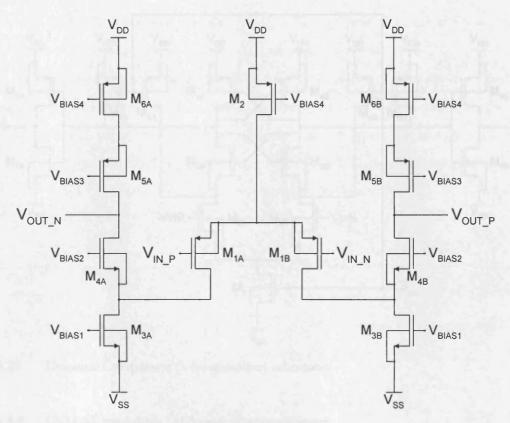

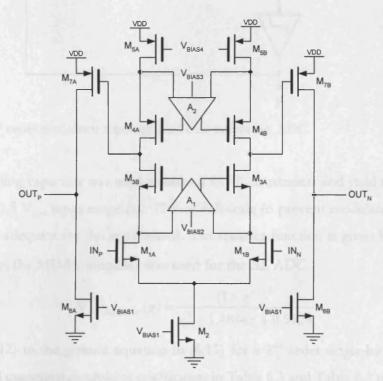

| Fig. | 5.25        | BiCMOS folded cascode OTA for the GSM ΔΣ modulator's 1 <sup>st</sup> integrator               | 127 |

| Fig. | 5.26        | CMOS folded cascode OTA for the GSM $\Delta\Sigma$ modulator's $2^{nd}$ - $4^{th}$ integrator | 128 |

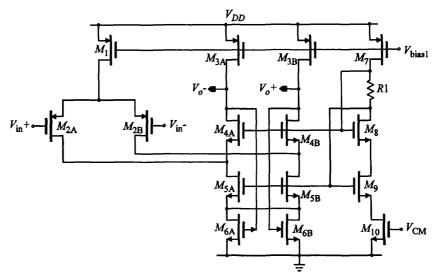

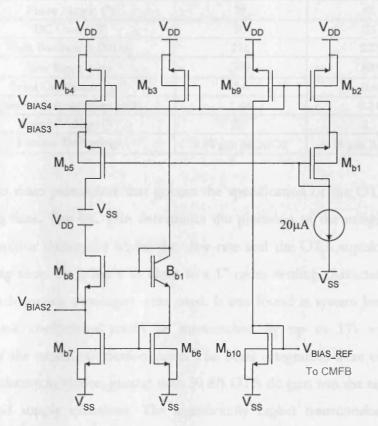

| Fig. | 5.27        | OTA biasing circuit schematic.                                                                | 128 |

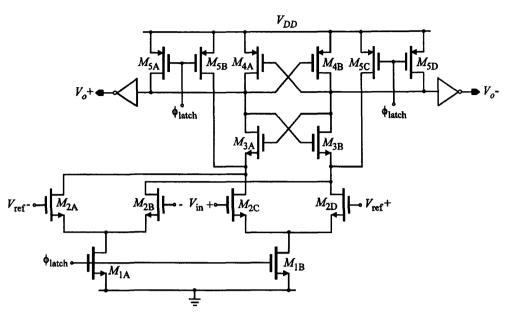

| Fig. | 5.28        | Dynamic Comparator (1-bit quantizer) schematic                                                | 129 |

| Fig. | 5.29        | WCDMA $\Delta\Sigma$ modulator power spectrum plot with the zero at 1.62 MHz                  |     |

| _    | 5.30        | GSM and WCDMA ΔΣ modulator test setup.                                                        |     |

| _    | 5.31        | GSM ΔΣ modulator microphotograph                                                              |     |

| _    | 5.32        | Measured un-linearized GSM ΔΣ modulator power spectrum                                        |     |

| _    | 5.33        | Measured linearized GSM $\Delta\Sigma$ modulator power spectrum                               |     |

| _    | 5.34        | Measured linearized GSM ΔΣ SNR/SFDR vs. input amplitude                                       |     |

| _    | 5.35        | Measured linearized GSM ΔΣ SNR/SFDR vs. clock frequency                                       |     |

| _    | 5.36        | • • • • • • • • • • • • • • • • • • •                                                         |     |

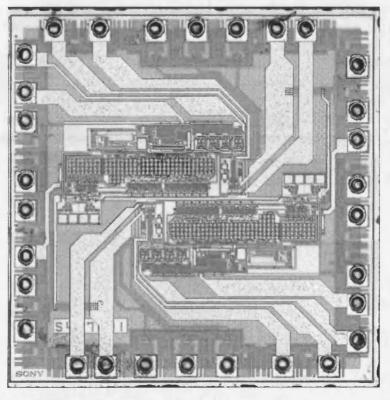

| _    |             | WCDMA ΔΣ modulator microphotograph.                                                           |     |

| _    | 5.37        | Simulated linearized WCDMA ΔΣ modulator circuit power spectrum                                |     |

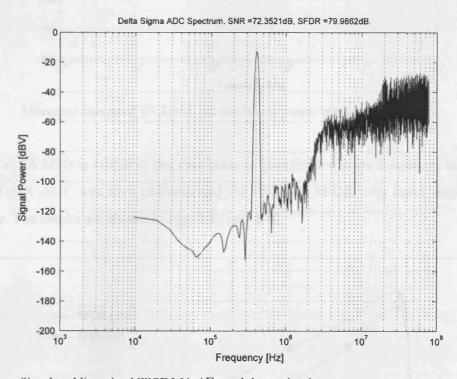

| _    | 5.38        | Measured linearized WCDMA ΔΣ modulator power spectrum                                         |     |

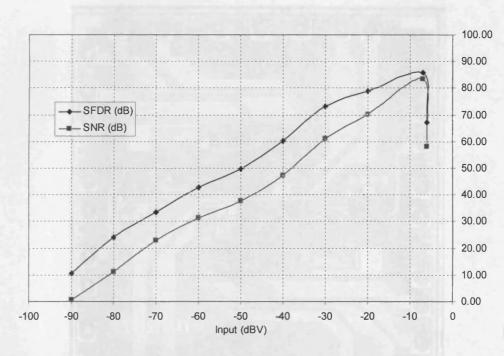

| _    | 5.39        | Measured linearized WCDMA ΔΣ SNR/SFDR vs. input amplitude                                     |     |

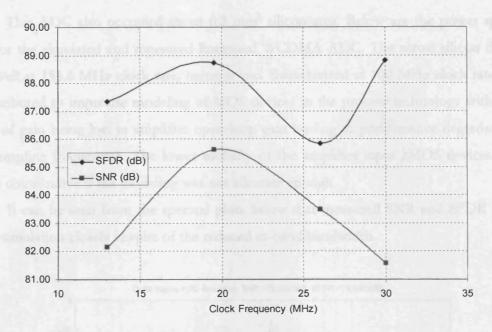

|      | 5.40        | Measured linearized WCDMA ΔΣ SNR/SFDR vs. clock frequency                                     |     |

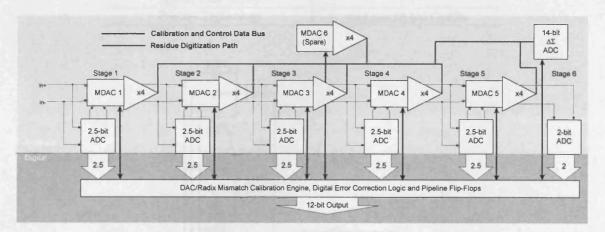

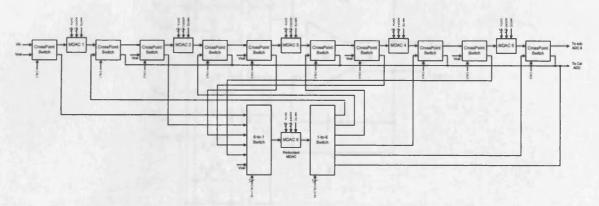

| Fig. | 6.1         | Pipeline ADC block diagram                                                                    | 142 |

| Fig. 6.2  | MDAC simplified block diagram. The symbol "&" is the AND operation        | 143    |

|-----------|---------------------------------------------------------------------------|--------|

| Fig. 6.3  | Residue versus input for 2-bit and 2.5-bit MDAC                           | 144    |

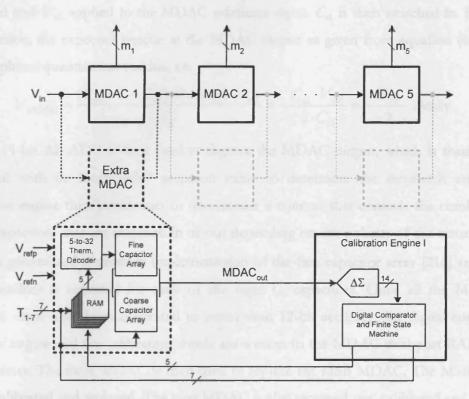

| Fig. 6.4  | Proposed segmented calibration architecture I.                            | 147    |

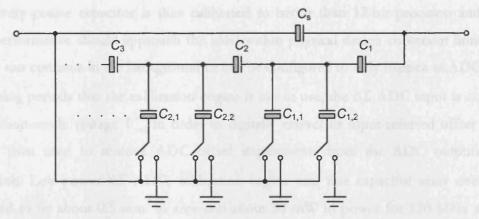

| Fig. 6.5  | A generalized $\pi$ -network implementation of fine capacitor array       |        |

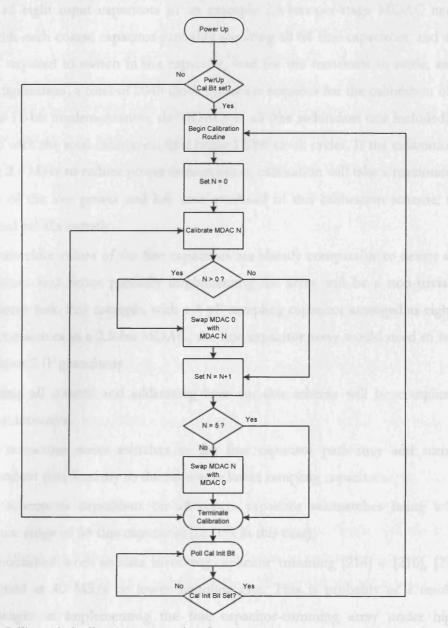

| Fig. 6.6  | Calibrated pipeline ADC operation flowchart                               | 149    |

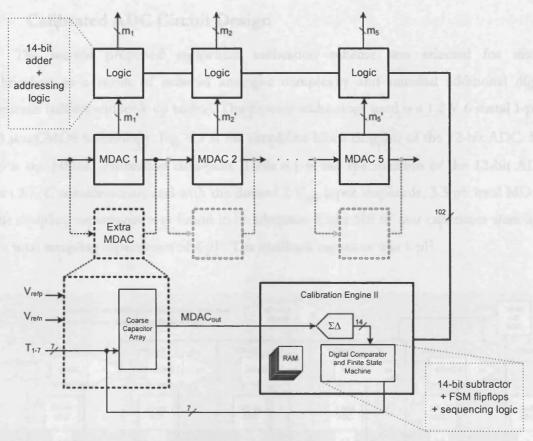

| Fig. 6.7  | Proposed segmented calibration architecture II                            | 152    |

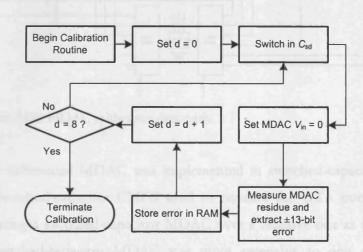

| Fig. 6.8  | MDAC calibration procedure flowchart                                      | 152    |

| Fig. 6.9  | 12-bit 2.5-bit-per-stage ADC block diagram                                |        |

| Fig. 6.10 | 12-bit ADC MDAC calibration data-path                                     | 153    |

| Fig. 6.11 | Calibrated MDAC schematic.                                                | 154    |

| Fig. 6.12 | MDAC amplifier schematic                                                  | 155    |

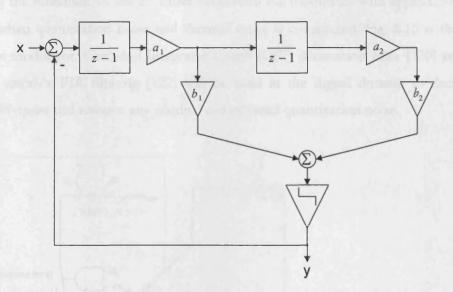

| Fig. 6.13 | 2 <sup>nd</sup> order modulator topology for 14-bit calibration ADC       |        |

| Fig. 6.14 | Calibration ΔΣ modulator schematic                                        |        |

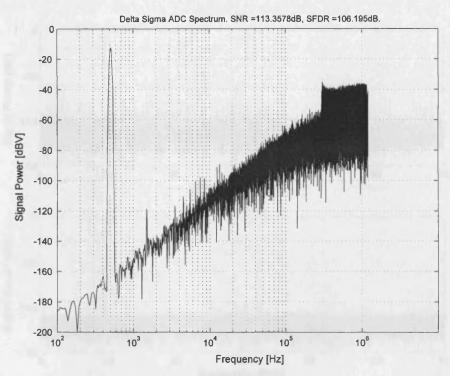

| Fig. 6.15 | Calibration ΔΣ modulator power spectrum.                                  | 158    |

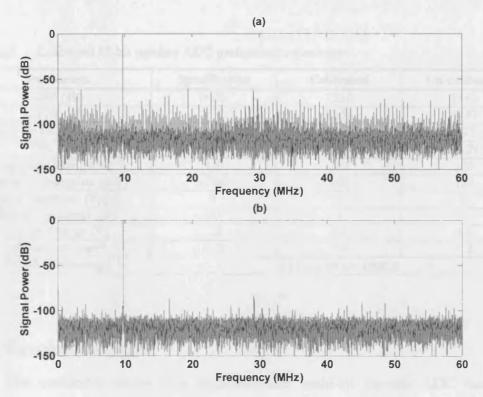

| Fig. 6.16 | ADC output spectra (a) without and (b) with calibration                   | 159    |

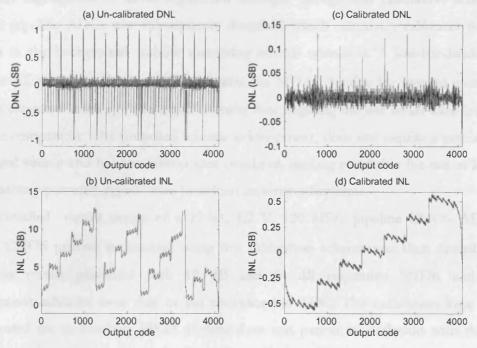

| Fig. 6.17 | (a) DNL, (b) INL without calibration, (c) DNL, (d) INL with calibration   | 159    |

| Fig. A.1  | First-order $\Delta\Sigma$ modulator                                      | 164    |

| Fig. A.2  | Second-order ΔΣ modulator                                                 | 166    |

| Fig. A.3  | Leslie-Singh cascade structure                                            | 169    |

| Fig. A.4  | MASH cascade structure                                                    | 170    |

| Fig. A.5  | 4th-order loop filter with distributed feed-forward and feedback paths    | 171    |

| Fig. A.6  | 4th-order loop filter with feed-forward, feedback and resonator paths     | 172    |

| Fig. A.7  | 4th-order loop filter with weighted feed-forward summation.               | 173    |

| Fig. A.8  | 4th-order loop filter with weighted feed-forward summation and resonators | s. 174 |

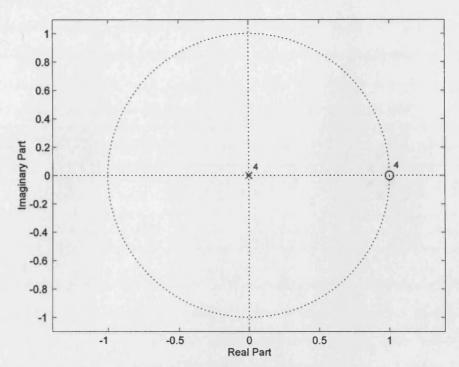

| Fig. A.9  | Pole-zero plot of a 4th order pure differentiation NTF                    | 175    |

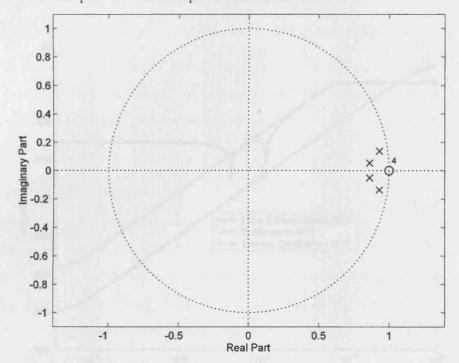

| Fig. A.10 | Pole-zero plot of a 4th order Butterworth NTF.                            |        |

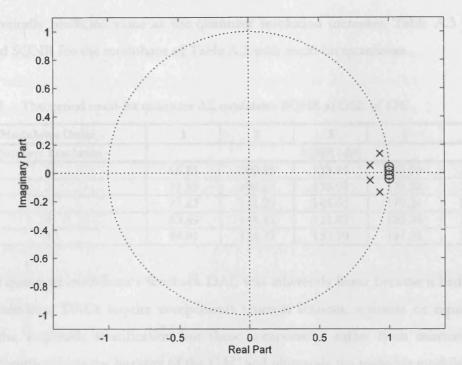

| Fig. A.11 | Pole-zero plot of a 4th order Inverse Chebyshev NTF.                      | 176    |

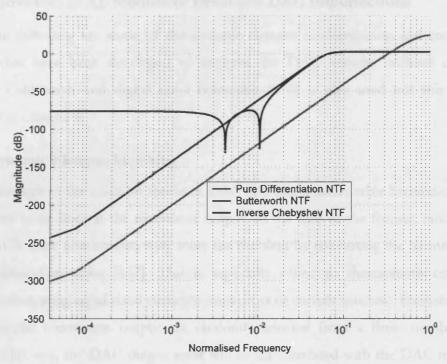

| Fig. A.12 | Frequency response plots of all three NTFs                                |        |

# Glossary of Terms

3-Dimensional

3GPP 3<sup>rd</sup> Generation Partnership Project

8-PSK 8-Phase Shift Keying AC Alternating Current

ACL Closed Loop Gain

ADC Analogue-to-Digital Converter

ADSL Asymmetric Digital Subscriber Line

AFC Automatic Frequency Control

AGC Automatic Gain Control

AMC Adaptive Modulation and Coding

AMPS Advance Mobile Phone Service

AOL Open Loop Gain

BBIC Baseband Integrated Circuit

BER Bit Error Rate

BiCMOS Bipolar Complementary Metal Oxide Semiconductor

BW Bandwidth

CDMA Code Division Multiple Access

CEPT Conference of European Posts and Telegraphs

CIC Cascaded Integrator Comb

CMFB Common Mode Feedback

CMOS Complementary Metal Oxide Semiconductor

C/N Carrier-to-Noise Ratio

COFDM Coded Orthogonal Frequency Division Multiplexing

CS Circuit Switched

CSI Channel State Information

CT Continuous Time

DAC Digital-to-Analogue Converter

D-AMPS Digital Advance Mobile Phone Service

dBFS dB Full-Scale

DC Direct Current

DEM Dynamic Element Matching

DFT Discrete Fourier Transform

DNL Differential Nonlinearity

D-QPSK Differential Quadrature Phase Shift Keying

DR Dynamic Range

$\Delta\Sigma$  Delta-Sigma

DT Discrete Time

DTT Digital Terrestrial Television

DTV Digital Television

DVB Digital Video Broadcast

DVB-C Digital Video Broadcast, Cable

DVB-H Digital Video Broadcast, Handheld

DVB-S Digital Video Broadcast, Satellite

DVB-T Digital Video Broadcast, Terrestrial

DWA Data Weighted Averaging

E-DCH Uplink Enhanced Dedicated Channel

EDGE Enhanced Data rates for Global Evolution

E-GSM Enhanced Global System for Mobile communications

ELG European Launching Group

ENOB Effective Number of Bits

ERBW Effective Resolution Bandwidth

ETSI European Telecommunication Standards Institute

EVM Error Vector Magnitude

FDM Frequency Division Multiplexing

FDMA Frequency Division Multiple Access

FEC Forward Error Correction

FFT Fast Fourier Transform

FIR Finite Impulse Response

FOM Figure of Merit

FPGA Field Progammable Gate Array

GaAs Gallium Arsenide

GBW Gain Bandwidth Product

GMSK Gaussian-filtered Minimum Shift Keying

GPRS General Packet Radio Services

GSM Groupe Spécial Mobile

GSM Global System for Mobile communications

HDTV High Definition Television

HSDPA High Speed Downlink Packet Access

HS-DSCH High-Speed Downlink Shared Channel

HSUPA High Speed Uplink Packet Access

I In-phase

ICI Inter-Channel Interference

IF Intermediate Frequency

ILA Individual Level Averaging

INL Integral Nonlinearity

Î<sub>or</sub> Total WCDMA received power spectral density at antenna

IP Internet Protocol

ISDN Integrated Services Digital Network

ISI Inter-Symbol Interference

LMS Least Mean Square

LNA Low Noise Amplifier

LO Local Oscillator

LSB Least Significant Bit

MDAC Multiplying Digital-to-Analogue Converter

MHP Multimedia Home Platform

MiM Metal-insulator-Metal

MOS Metal Oxide Semiconductor

MoU Memorandum of Understanding

MP3 Motion Picture expert group-1, audio layer 3

MPEG Motion Pictures Expert Group

MSB Most Significant Bit

MTBF Mean-Time-Between-Failure

NF Noise Figure

NICAM Near Instantaneous Companded Audio Multiplex

nMOS n-channel Metal Oxide Semiconductor

NMT Nordic Mobile Telephone

NTF Noise Transfer Function

OFDM Orthogonal Frequency Division Multiplexing

OOB Out of Band

Opamp Operational Amplifier

OSR Over-Sampling Ratio

OTA Operational Transconductance Amplifier

PCB Printed Circuit Board

PDA Personal Digital Assistant

PiP Poly-insulator-Poly

PLL Phase Locked Loop

PM Phase Margin

pMOS p-channel Metal Oxide Semiconductor

PN Pseudo Noise PS Packet Switched

PSK Phase Shift Keying

Q Quadrature

QAM Quadrature Amplitude Modulation

QPSK Quaternary Phase Shift Keying

RAM Random Access Memory

RF Radio Frequency

RFIC Radio Frequency Integrated Circuit

RMS Root Mean Square

RRC Root-Raised-Cosine

RS Reed Solomon

SAR Successive Approximation Register

SAW Surface Acoustic Wave

SC Switched Capacitor

SF Spreading Factor

SFDR Spurious Free Dynamic Range

SFN Single Frequency Network

SHA Sample-and-Hold Amplifier

SiGe Silicon Germanium

SiP System-in-a-Package

SNDR Signal-to-Noise and Distortion Ratio

SNR Signal-to-Noise Ratio

SN<sub>th</sub>R Signal-to-Thermal Noise Ratio

SoC System-on-a-Chip

SQNR Signal-to-Quantization Noise Ratio

SR Slew Rate

STF Signal Transfer Function

TACS Total Access Communication System

TDMA Time Division Multiple Access

THD Total Harmonic Distortion

TS Transport Stream

UHF Ultra High Frequency

UMTS Universal Mobile Telecommunications System

VCO Voltage Controlled Oscillator

VHF Very High Frequency

WCDMA Wideband Code Division Multiple Access

# Introduction

1

"The entrance of thy words giveth light; it giveth understanding unto the simple" Ps. 119:130 KJV

# 1.1 Historical Overview of Digital Communication Systems

Historically, some form of wireless communication has been essential to the very existence of humans and animals alike. The bees for example do a dance (visual communication) to alert other bees to the presence of nectar. Monkeys make a whoopee sound (auditory communication) when they have found food. In the pre-historic times predating what we know now as wireless communication, human beings communicated by means of fire, smoke and drums or by the use of emissaries (a precursor of the structured ubiquitous and archetypal national postal systems). The race between wire-line and wireless communication development was in a sense neck to neck with Samuel Morse, a painter perfecting the Morse code (a variable-length ternary code [3]) and telegraph in 1837, which was then used in 1844 to send the first telegraph message between two American cities. By 1864, James Clerk Maxwell had formulated the electromagnetic theory and inferred the existence of radio waves using the well-known Maxwell equations, which were verified experimentally by Heinrich Hertz in 1887. By 1875, Alexander Graham Bell had invented the wire-line telephone with Almon Brown Strowger's automatic electromechanical switch replacing the erstwhile manual telephone exchange in 1897.

But it was not until Guglielmo Marconi received the first transatlantic wireless transmission in St. Johns, Newfoundland on December 12, 1901 from Poldhu, Cornwall, England, 2100 miles away [4] that communication transcended geographical and continental boundaries. John Ambrose Fleming, then Professor of Electronic Engineering at University College London and a consultant to British Marconi designed the equipment used by Marconi and invented the vacuum tube diode in 1904 paving the way for transcontinental telephony and the dawn of analogue wireless communication in 1913.

Edwin Howard Armstrong invented the super-heterodyne receiver in 1918 (the architecture is still in use today in various guises) paving the way for commercial radio and television broadcast reception. Harry Nyquist's classic and visionary 1928 paper [5] on the correct reception of telegraph signals in dispersive media eventually became the bedrock of digital communication in the future. With better understanding of the nature of wireless signals and the characteristics of the transmission channel, many researchers invented

modulation schemes, optimal reception channel filters, and complex schemes for the representation of baseband signals with the World War II acting as the major catalyst for the then ground-breaking advancements in telecommunications.

By 1948, Jean Claude Shannon established the theoretical foundations of digital communications with his classic paper on the mathematical theory of communication [6], showing that data rate could be increased ad infinitum without affecting the probability of error so long as the data rate was still within the channel capacity, a startling revelation at that time. This was followed by significant research in coding theory and the development of various error correcting codes in order to reach Shannon's theoretical channel capacity limit and thus, allow efficient communication and channel bandwidth utilization.

The solid-state transistor then came into the picture in 1948 when three Bell Laboratory scientists invented it [7] (for which they received the 1956 Nobel Prize in Physics). This stimulated innovation in other quarters with Robert Noyce of National Semiconductors inventing the planar integrated circuit in 1958. Noyce's patent was five months later than Texas Instrument's Jack Kilby's monolithic integrated circuit invention but Noyce's planar technique became commercially dominant. This spawned numerous analogue integrated circuits, logic and memory chips as well as single-chip microprocessors, thus making digital signal processing suddenly fast, power-efficient and affordable - completely transforming the digital communication landscape forever.

The availability of microprocessors naturally led to the development of personal computers, packet switching, computer networks and the Arpanet (1971). This was later renamed the Internet in 1985 and commercialized in 1994 after the invention of hyper-text transport protocol (http), hyper-text markup language (html) and the world wide web (www) caused an astronomical explosion in the Internet's usage and popularity.

From the invention of the television in 1926 by John Logie Baird [8] to the late 1980s, analogue terrestrial broadcast was vogue. This was however plagued by reception problems as a result of multi-path, interference and fading issues, thus motivating research into the possibility of terrestrial digital broadcast. Commercial digital video broadcast was eventually achieved in the late 1990s largely as a result of work done by the Digital Video Broadcast (DVB) working group [1] since September 1993. Cable (DVB-C) and satellite (DVB-S) media were initially used for digital broadcast with the extension to the terrestrial transmission channel (DVB-T) as soon as digital modulation schemes and encoding algorithms were robust enough to address the issues that originally affected analogue

terrestrial broadcast. The first DVB-T commercial service was launched in the United Kingdom in November 1997.

Mobile communications on the other hand had its roots in military communication with point-to-point analogue modulation based radios already in use by World War II. Multipoint 1<sup>st</sup> generation analogue mobile communication was finally commercialized in the mid eighties with the Advance Mobile Phone Service (AMPS) system in use in the United States and Asia, the Total Access Communication System (TACS) in the United Kingdom and the Nordic Mobile Telephone (NMT) system in use in Scandinavia. By 1992, Europe had gone digital with the 2<sup>nd</sup> generation TDMA-based Global System of Mobile Communication (GSM) and America following suit with D-AMPS. Japan also introduced IS-95, a form of CDMA in the mid nineties. By the late nineties, packet switching was in use with the introduction of General Packet Radio Services (GPRS) and Enhanced Data rates for Global Evolution (EDGE), 2.5G enhancements to GSM, which is still in use in over 200 countries and by almost two billion subscribers worldwide [9].

While subscribers were experiencing the multimedia messaging benefits of the 2.5G services, the 3<sup>rd</sup> Generation Partnership Project (3GPP) was already scoping out a Universal Mobile Telecommunication System (UMTS) that would use some form of CDMA and provide high data-rates with efficient use of bandwidth. This has now been deployed in parts of Europe, Asia and America and with Mbps data rates using High Speed Downlink Packet Access (HSDPA) and video streaming capability, is poised to completely eclipse GSM in the near future.

As it became apparent that the evolution of mobile handset design was inevitable, (with high-resolution colour displays and cameras becoming commonplace on lighter, smaller and more power efficient phones), the DVB consortium in the early 21<sup>st</sup> century mulled over the possibility of deploying robust digital terrestrial television for battery-powered mobile devices with guaranteed reception even at high speeds. DVB-Handheld (DVB-H) was then developed and standardized in 2004 and is similar to DVB-T with the broadcast data transmitted as IP packets (to allow for time-slicing at the receiver for power consumption reduction) and a novel Forward Error Correction (FEC) algorithm developed to aid robust reception at high velocities. Trials have actually been done at close to Mach-1 speeds with excellent reception quality [10] and 2006 will be the year that will revolutionize the traditional ways in which multimedia, music, radio and television are enjoyed. The power-efficient WCDMA/DVB-H/MP3/Camera-phone will thus be where all these cutting edge developments in wireless communication will eventually converge.

#### 1.2 Motivation for the Research Work

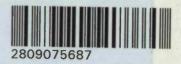

For the subscriber to receive voice, video, broadcast and data, content depictive of the previously outlined advancements in digital wireless communication, a suitable tuner or receiver front-end is required. Fig. 1.1 is a simplified diagram of a direct conversion receiver/tuner used for DVB-H reception. The surface acoustic wave (SAW) filter is used to steeply reject RF signals within the immediate vicinity of the wanted signal band. The low noise amplifier (LNA) amplifies the received signal whilst adding little noise in the process. The phase locked loop (PLL) generates the RF waveforms for use in the in-phase (I) and quadrature (Q) paths of the receiver. The mixer translates the RF input signal directly to baseband. Additional band-limiting is done using an integrated channel filter and an automatic gain control (AGC) loop used to further amplify the wanted signal. Finally, the I/Q analogue-to-digital converters (ADCs) convert the I/Q channel outputs to the digital domain for subsequent digital signal processing and extraction of the transmitted MPEG2 audio and video program.

Fig. 1.1 Simplified block diagram of a direct conversion tuner for DVB-H reception.

In the days of analogue wireless communication, the demodulated analogue baseband output was the desired information. For digital wireless communication, the traditional modulation schemes are only used as bearers of the encoded packetised digital data. The analogue baseband output still needs to be accurately translated to the digital domain with adequate Signal-to-Noise Ratio (SNR) to facilitate digital demodulation, error correction and decoding of the transmitted packets. And this is where the ADC comes into the picture. The ADC's noise floor must be such that its effect on the input baseband signal's Carrier-to-Noise Ratio (C/N) is negligible. In addition, the use of a high dynamic range ADC eases the complexity of the analogue channel filter design and eliminates the need for trimming or

calibration of the baseband filter characteristics whilst translating additional filtering requirement to the digital domain where it can be done more precisely and efficiently.

Table 1.1 is the representative breakdown of power consumption for the individual blocks comprising a typical DVB-T/H tuner and demodulator subsystem [11]-[16].

Table 1.1

Power Consumption Break-down for DVB-T Demodulator Subsystem.

| References                   | Blocks              | Power Consumption (mW) |  |

|------------------------------|---------------------|------------------------|--|

| [11]                         | LNA & RF Filter     |                        |  |

| [12] Mixer, VCO & PLL        |                     | 47                     |  |

| [13] I and Q AGC             |                     | 65.4                   |  |

| [14] I and Q Baseband Filter |                     | 50                     |  |

| [15]                         | I and Q ADCs        | 120                    |  |

| [16]                         | Digital Demodulator | 307                    |  |

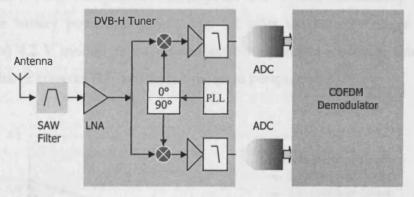

It can thus be seen that the ADC power consumption is a sizeable portion of the overall power budget. Hence, if low-power techniques can be developed and used for the design of the ADCs the DVB-T subsystem's consumption will reduce, immediately translating to mobile device battery power elongation. Fig. 1.2 plots the battery voltage of a 1.5 Ah (Ampere-hour) 4.2 V mobile phone lithium-ion battery versus discharge time for various constant discharge currents [17] to help put things in perspective.

Fig. 1.2 Discharge profile of a 4.2 V 1.5 Ah lithium-ion battery.

This research thus focused on the minimization of power consumption in video-rate pipeline ADCs by the optimization of inter-stage resolution partitioning, the design of a novel switch linearization circuit to address sampling switch linearising issues affecting low-power switched-capacitor  $\Delta\Sigma$  ADCs and the development of low power and low silicon overhead calibration schemes for high-speed and high-resolution pipeline ADCs. The research spawned four silicon devices in total with the designs done using CMOS and BiCMOS 0.35 $\mu$ m and 0.12 $\mu$ m process technologies and easily portable to lower geometry technologies.

## 1.3 Thesis Organization

The thesis is made up of seven chapters. Chapter 2 reviews ADC fundamentals with properties of quantization noise examined, ADC terminologies explained and ADC testing methodologies described.

Chapter 3 goes further, with all available ADC architectures presented and described in detail. The trade-offs between architectures is explained and data presented to illustrate the resolution versus power consumption versus sampling speed segments that the various architectures fall into; a useful means of determining the appropriate architecture to use for a given wireless communication or broadcast receiver subsystem design.

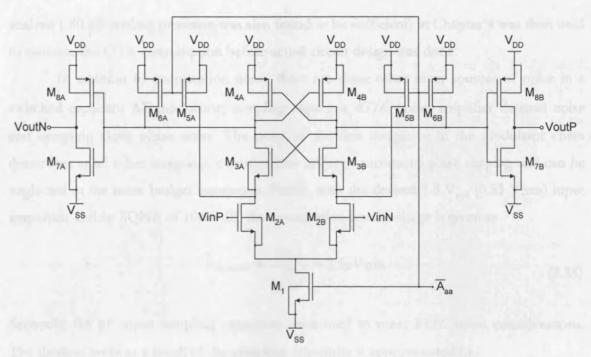

In Chapter 4, the cost benefit of a multiple-die System-in-a-Package (SiP) solution over a monolithic System-on-a-Chip (SoC) for DVB-H receiver sub-system is stated. Systematic analysis is then carried out to determine optimal inter-stage resolution partitioning for lowest power dissipation in video-rate pipeline ADCs. On this vein, the silicon design of a reduced-voltage, ultra-low energy and high input bandwidth pipeline ADC for DVB-H is presented with system design issues of the DVB-H tuner considered. Measured results are then shown.

Chapter 5 presents the design of two low-power  $\Delta\Sigma$  ADCs for both GSM and WCDMA wireless receiver standards with system design issues in both the GSM and WCDMA receiver chains thoroughly considered. The chapter culminates in the system and circuit design of both ADCs with the design of a novel sampling switch linearization scheme enabling the achievement of very high dynamic range for the ADCs. Measured results are subsequently presented.

Chapter 6 show-cases advancements in high-resolution ADC calibration and proposes two equivalent low-power background calibration scheme for high-speed high-resolution pipeline ADCs. Circuit design of a background calibrated 12-bit pipeline ADC using the proposed scheme is then described and system-level simulation results presented.

Conclusions are then suitably drawn in Chapter 7 and potential areas for further research in the quest for high-performance ADC power consumption minimization identified.

#### 1.4 Research Contributions

The main contributions of this research to the body of knowledge can be summarized as follows:

- Determination of optimal inter-stage partitioning for lowest power dissipation in moderate resolution pipeline ADCs. This enabled the design of a video-rate lowpower ADC with the lowest reported energy efficiency to date.

- Novel switch linearization circuit for switched capacitor ADC sampling switch. This

lineariser circuit allowed for over 12 dB ADC dynamic range improvement in

comparison with ADC sampling switch implementation using prior art (transmission

gates) and was successfully verified in silicon for both a GSM and WCDMA ΔΣ

ADC.

- Proposal of novel low-power background calibration schemes for high-speed highresolution pipeline ADCs that was suitable for implementation in battery-powered mobile devices. Circuit and layout design of a 12-bit ADC was then done to demonstrate the scheme with the silicon design planned for fabrication in November 2006.

#### 1.5 Publications

The following papers were accepted for both journal and conference publications within the period of the research:

- A Segmented Analog Calibration Scheme for Low-Power Multi-Bit Pipeline ADCs by

O. A. Adeniran and A. Demosthenous, accepted for publication in the December 2006 IEEE

International Conference on Electronics, Circuits and Systems (ICECS 2006) proceedings.

- An Ultra Energy-Efficient, Wide-Bandwidth Video Pipeline ADC Using Optimized Architectural Partitioning by O. A. Adeniran and A. Demosthenous, submitted to the IEEE Transactions on Circuits and Systems I – Regular Papers, revised May 2006, August 2006 and awaiting publication.

- A 19.5 mW 1.5 V 10-bit Pipeline ADC for DVB-H Systems in 0.35 μm CMOS by O.

A. Adeniran and A. Demosthenous, in Proc. 2006 IEEE International Symposium on Circuits and Systems (ISCAS 2006), Kos island, Greece, pp. 5351-5354, May 2006.

- A 92 dB 560 MHz 1.5 V 0.35 μm CMOS Operational Transconductance Amplifier by O. A. Adeniran and A. Demosthenous, in Proc. the 2005 European Conference on Circuit Theory and Design (ECCTD 2005), Cork, Ireland, pp. 325-328, August 2005.

- Optimization of Bits-per-Stage for Low-Voltage Low-Power CMOS Pipeline ADCs by O. A. Adeniran and A. Demosthenous, in Proc. the 2005 European Conference on Circuit Theory and Design (ECCTD 2005), Cork, Ireland, pp. 55-58, August 2005.

- A CMOS Low-Power ADC For DVB-T And DVB-H Systems by O. A. Adeniran, A.

Demosthenous, C. Clifton, R. Soin and S. Atungsiri in Proc. 2004 IEEE International

Symposium on Circuits and Systems (ISCAS 2004), Vancouver, Canada, pp. 209-212, May

2004.

In addition, a journal paper stemming from the work described in Chapter 5 is currently in preparation.

2

# Analogue to Digital Converter Fundamentals

"The law of the Lord is perfect converting the soul" Ps. 19:7 KJV

Virtually all real-life phenomena produce effects that are continuous in nature from human nerve signals of minuscule electrical magnitude to seismic tremors of significantly higher intensity. To further perceive, transport, analyze or archive these continuous-time analogue signals a means must exist for conversion from physical to electrical form. This is usually achieved via a variety of transducers ranging from strain gauges to the ubiquitous microphone. The analogue electrical outputs of these transducers is then translated to the digital domain where the signal can no longer be corrupted by media ageing and the superior processing power of digital signal processors, dedicated microprocessors and the flexibility of software can be annexed for robust data extraction, demodulation or analysis. The ADC is the bridge between the continuous-time analogue domain and discrete-time digital domain. Since ADCs are sampled sub-systems, some signal pre-conditioning is usually required to preserve signal integrity in the digital domain. This chapter will cover signal characteristics and conditioning issues with the terminologies associated with sampled signals in general and ADCs in particular elucidated. Issues and constraints of ADC testing methodologies will be considered.

#### 2.1 Analogue and Discrete-time Signals

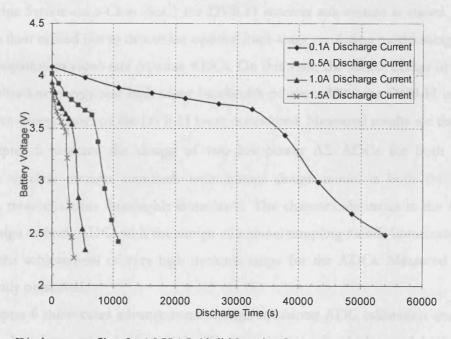

Fig. 2.1 shows an analogue sinusoidal waveform of frequency  $f_{\text{sig}}$  represented by the equation below with overlaid harmonics at  $(2 \cdot n + 1) \cdot f_{\text{sig}}$  for integer n = 2 and 4 and periodically sampled at times  $T = 1/f_{\text{clk}}$  where the sampling frequency,  $f_{\text{clk}} \ge 2 \cdot f_{\text{sig}}$  to obey the Nyquist Criterion [5]:

$$V_{\rm sip}(t) = A \cdot \sin(2\pi f_{\rm sip} t). \tag{2.1}$$

If for example,  $V_{sig}(t)$  is sampled twice within a period at its maxima and minima (magenta circle in Fig. 2.1), all three waveforms of different frequencies are coincident at the sampling points. Coherent sampling thus cannot distinguish between a signal sampled at the Nyquist rate and its harmonics, as the Fourier transform of the discrete-time data will represent the three waveforms with a single tone at  $f_{sig}$ , a problem known as aliasing which may or may not be desirable depending on whether signal sub-sampling is the original intent. This illustration has employed a simple sinusoid but the phenomenon is directly applicable to

both periodic and random signals. In general, if a signal of bandwidth  $f_{\text{bw}}$  is sampled at rate  $f_{\text{clk}}$  where  $f_{\text{clk}} \ge f_{\text{bw}}$ , aliasing will be significantly minimized if the signal is constrained within  $f_{\text{bw}}$  by the use of a suitable anti-alias filter prior to discrete-time sampling.

Fig. 2.1 Representative sinusoidal waveform with overlaid 5th and 9th harmonics.

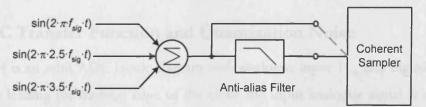

Fig. 2.2 depicts the sampler with a 6th order Butterworth filter used for anti-aliasing.

Fig. 2.2 Descriptive coherent sampling subsystem with anti-aliasing filter included.

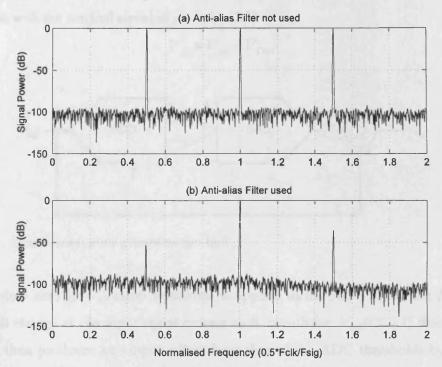

Three noisy sinusoids, one at  $f_{sig}$  and the others at 2.5:  $f_{sig}$  and 3.5:  $f_{sig}$  are generated using Matlab® and applied to the 6<sup>th</sup> order Butterworth anti-alias filter input prior to sampling at exactly  $f_{clk} = 4 \cdot f_{sig}$ . Fig. 2.3 is the normalized (to  $0.5 * f_{clk} / f_{sig}$ ) in-band power spectrum of the pre and post-anti-alias-filtered sampled data with better than 40dB rejection of aliased signals obtained (the  $2.5 \cdot f_{sig}$  alias undergoes less filtering because of its proximity to  $f_{sig}$ ). Ideally, the anti-alias filter stop-band rejection should be high enough to attenuate the aliases to levels comparable to the noise floor. This complicates the analogue filter design considerably, hence the use of pseudo over-sampling in most systems to ease the filter design (i.e. a 20.48MS/s Nyquist ADC used for 4 MHz broadcast video digitization). This issue is further exacerbated in ADCs used for sub-sampling as a result of the closer proximity of in-band and out-of-band Intermediate Frequency (IF) signals (i.e. designing a filter that rejects a

64MHz tone with the wanted tone at 62 MHz is a non-trivial task). To relieve the filter complexity issue for sub-sampling applications, the undesired signal may be allowed to fold down into baseband and is subsequently taken out using digital signal processing.

Fig. 2.3 Sampled signal spectra (a) without and (b) with anti-alias filtering used.

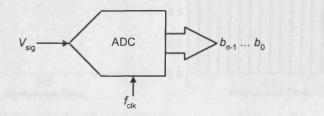

### 2.2 ADC Transfer Function and Quantization Noise

Fig. 2.4 is an *n*-bit ADC block diagram with analogue input  $V_{\text{sig}}$  and digital outputs  $b_{n-1}$  to  $b_0$ . At the leading (or trailing) edge of the clock the input analogue signal is sampled and quantized to a precision determined by the resolution (number of output bits) of the ADC. The analogue input and digital outputs of the ADC can be related by (2.2):

$$V_{\text{ref}} \cdot (b_0 \cdot 2^{-n} + b_1 \cdot 2^{1-n} + \dots + b_{n-2} \cdot 2^{-2} + b_{n-1} \cdot 2^{-1}) = V_{\text{sig}} \pm V_Q \tag{2.2}$$

where  $V_{\text{ref}}$  is the ADC analogue reference voltage (to which cumulative fractions the input signal is compared),  $b_{n-1} \dots b_0$  are the ADC output bits and  $V_Q$  the quantization error or noise which in an ideal ADC is bounded between  $\pm 1/2^{n+1}$  or  $\pm \frac{1}{2}$  LSB (Least Significant Bits).

Fig. 2.4 Ideal *n*-bit ADC block diagram.

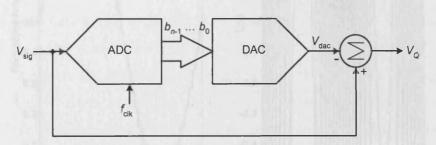

To extract the quantization error from our hypothetical n-bit ADC, the test-bed block diagram in Fig. 2.5 will be required with an ideal n-bit Digital to Analogue Converter (DAC) with output  $V_{\rm DAC}$  used to convert the quantized digital signal back to analogue for comparison with the original signal as given by (2.3).

$$V_Q = V_{\text{sig}} - V_{\text{DAC}} \tag{2.3}$$

Fig. 2.5 Quantization error extraction test-bed.

If a slow zero to  $V_{\rm ref}$  ramp waveform is applied to the ADC input, the ADC digital outputs will change as the input signal crosses each cumulative  $V_{\rm ref}/(2"-1)$  threshold level. The DAC then produces an output offset from that of the ADC thresholds by ½ LSB as illustrated in Fig. 2.6. It can also be observed that the quantization noise,  $V_{\rm Q}$  follows the familiar saw-tooth waveform pattern but is bounded between  $\pm$  ½ LSB limits.

Fig. 2.6 ADC quantization noise with ramp input.

Fig. 2.7 ADC quantization noise with sinusoidal input.

On the other hand, if a sinusoid is applied to the input of the ADC, a different quantization noise profile results (Fig. 2.7) but which is still within the  $\pm \frac{1}{2}$  LSB bounds. If again, a Gaussian noise source with outputs constrained to the ADC input limits is applied to the ADC inputs, the noise-like quantization error in Fig. 2.8 results.

Fig. 2.8 ADC quantization noise with Gaussian noise input.

Finally, a pseudorandom noise source, typical of the signals the ADC will digitize in real life, is applied to the ADC and the results plotted in Fig. 2.9. Would all of the above ADC input signal conditions give the same results for the quantization noise energy? In order to understand and appreciate the properties of the quantization noise or error, it will be beneficial to examine the statistical property of the above input signals and the resultant quantization noise.

Fig. 2.10 shows the amplitude distribution histograms of a ramp, sinusoidal Gaussian noise and pseudorandom noise input signals with their associated quantization errors. It can be seen that in spite of the disparate nature of the signals, the amplitude distribution of their quantization noise is approximately the same (with the sinusoid quantization noise slightly in error as a result of the predictability of the error contribution of its peaks and troughs). The *rms* value of the quantization noise as determined for the above inputs is listed in Table 2.1.

Fig. 2.9 ADC quantization noise with pseudo-random noise input.

Table 2.1 Quantization noise energy for disparate ADC input signals.

| Input Signal   | $V_{ m sig}$ pk-pk | $V_{ m sig}$ rms                 | V <sub>Q</sub> pk-pk | V <sub>Q</sub> rms    |

|----------------|--------------------|----------------------------------|----------------------|-----------------------|

| Slow Ramp      | 1                  | $0.2887 \text{ or } 1/\sqrt{12}$ | 1 LSB                | 0.2887 or 1/√12 LSB   |

| Sine Wave      | 1                  | 0.3536 or 1/√8                   | 1 LSB                | 0.3068 LSB (6% error) |

| Gaussian Noise | 1                  | 0.1192                           | 1 LSB                | 0.2887 or 1/√12 LSB   |

| Random Noise   | 1                  | 0.2887 or 1/√12                  | 1 LSB                | 0.2887 or 1/√12 LSB   |

The above results can also be obtained analytically [18] by assuming a stochastic input signal with the quantization noise uniformly distributed between  $\pm \frac{1}{2}$  LSB. The probability density function  $f_Q(V)$  will be a constant as in Figure 2.10, i.e.

$$\int_{-\infty}^{\infty} f_{\mathcal{Q}}(V) dV = 1 \tag{2.3}$$

The rms value of the quantization noise is then given by:

$$V_{Q(rms)} = \left[\int_{-\infty}^{\infty} V_{Q}^{2} f_{Q}(V) dV\right]^{1/2} = \left[\int_{1/2}^{1/2} V_{Q}^{2} dV\right]^{1/2} = \left[\frac{1}{3} \cdot \left(\frac{1}{2^{3}} - \frac{1}{2^{3}}\right)\right]^{1/2}$$

(2.4)

i.e.