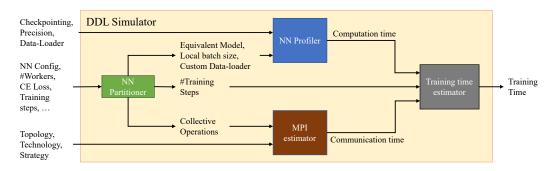

## Graphical Abstract

RAMP: A Flat Nanosecond Optical Network and MPI Operations for Distributed Deep Learning Systems

Alessandro Ottino, Joshua Benjamin, Georgios Zervas

## Highlights

## RAMP: A Flat Nanosecond Optical Network and MPI Operations for Distributed Deep Learning Systems

Alessandro Ottino, Joshua Benjamin, Georgios Zervas

- Research highlight 1

- Research highlight 2

# RAMP: A Flat Nanosecond Optical Network and MPI Operations for Distributed Deep Learning Systems

Alessandro Ottino<sup>a</sup>, Joshua Benjamin<sup>a</sup>, Georgios Zervas<sup>a</sup>

<sup>a</sup> Optical Networks Group, University College London (UCL), Roberts Engineering Building, Torrington Place, London, WC1E 7JE, United Kingdom

#### Abstract

Distributed deep learning (DDL) systems strongly depend on network performance. Current electronic packet switched (EPS) network architectures and technologies suffer from variable diameter topologies, low-bisection bandwidth and over-subscription affecting the completion time of communication and collective operations.

We introduce a near-exascale, full-bisection bandwidth, all-to-all, single-hop, all-optical network architecture with nanosecond reconfiguration called RAMP, which supports large-scale distributed and parallel computing systems (12.8 Tbps per node for up to 65,536 nodes).

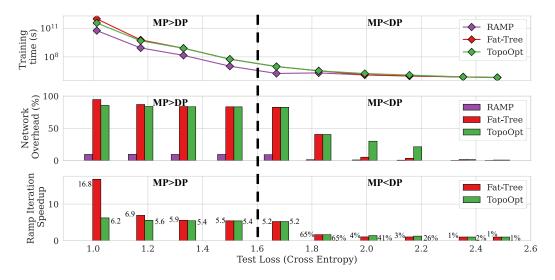

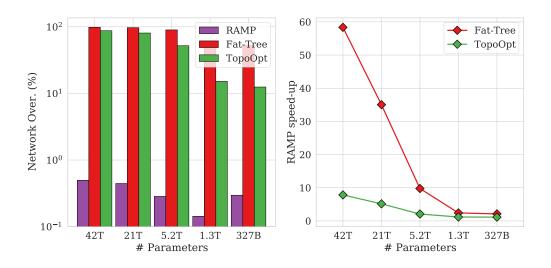

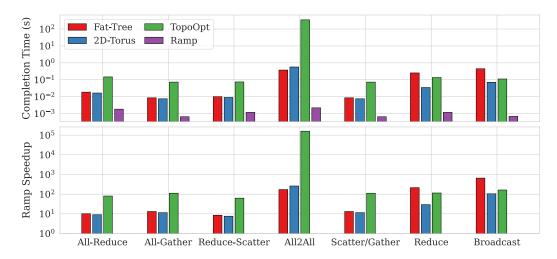

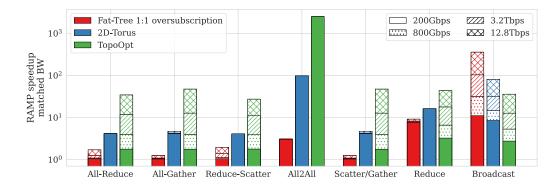

For the first time, a custom RAMP-x MPI strategy and a network transcoder are proposed to run MPI collective operations across the optical circuit switched (OCS) network in a schedule-less and contention-less manner. RAMP achieves  $7.6\text{-}171\times$  speed-up in completion time across all MPI operations compared to realistic EPS and OCS counterparts. It can also deliver a  $1.3\text{-}16\times$  and  $7.8\text{-}58\times$  reduction in Megatron and DLRM training time respectively while offering  $38\text{-}47\times$  and  $6.4\text{-}26.5\times$  improvement in energy consumption and cost respectively.

Keywords:

#### 1. Introduction

In recent years, there has been tremendous growth in distributed deep learning (DDL) Amodei and Hernandez (2018). As the computational complexity of DDL is increasing at a faster rate than hardware improvements, the performance requirement needs to be matched by distributing such jobs to more nodes. As all of these compute resources need to be interconnected, a significant portion of the performance-scaling responsibilities resides in the network. It has been argued Khani et al. (2021) Oyama et al. (2021) that Tbps communication between compute nodes is required to maximise the operational throughput and accommodate future applications. As most of the communications are dominated by MPI (Message Passing Interface) collective operations Clarke et al. (1994) Chunduri et al. (2018) (sec.2.3), the combination of higher node capacity and better collective communication strategies could lead to lower idling time and higher operational throughput, resulting in lower neural network model training times.

Current HPC systems (e.g. NVIDIA Corporation (2021a)) used for DDL training use electronic packet switching (EPS) with Tbps communication (e.g. 2.4Tbps per GPU NVIDIA Corporation. (2020)) at the intra-system (8-16 GPUs) NVIDIA Corporation (2021a) level and are limited to communicate at hundreds of Gbps regime (e.g. 200Gbps per GPU NVIDIA Corporation. (2020)) for the inter-rack/inter-system level, leading to high intra-to-inter system oversubscription (e.g. 12:1 NVIDIA Corporation. (2020)). This is due to network cost and power consumption constraints Khani et al. (2021); Ballani et al. (2020). The network over-subscription forces the use of Ringbased MPI collective operations NVIDIA Corporation: Optimized primitives for inter-GPU communication. (2022) that take full advantage of the available bandwidth but, at large scale, they lead to significant network overheads and slow down the training time of large models. For these reasons, it is critical to co-design novel Tbps all-to-all network architectures together with MPI strategies. This is required to achieve better application performances and meet future High-Performance Computing (HPC) and Data Center Network (DCN) job requirements.

Motivated by these observations, we propose RAMP, a large-scale Deep Neural Network (DNN) training system using a co-optimised nanosecond reconfigurable Optical Circuit Switching (OCS)-based network, MPI strategies and network scheduling. The following are the novel aspects of this paper:

- 1. The co-design of four aspects: optical/opto-electronic network technologies (physical layer), network architecture (network-level), MPI-x communication strategy (kernel-level) and network transcoder (system-level).

- 2. Network level: RAMP OCS network architecture that supports all-to-all, single hop, full-bisection bandwidth (not possible with prior archi-

- tectures) communication with *ramped up* (increased) end-node capacity (12.8 Tbps), scale (65,536 nodes) and system capacity (0.84 Ebps).

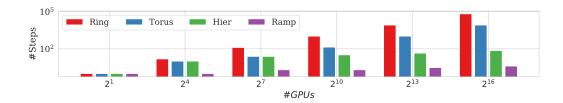

- 3. Kernel level: We introduce custom MPI RAMP-x strategies (x = gather, scatter, reduce, broadcast, etc.) for the proposed OCS-architecture and compare it against Ring-x, Torus-x, Hierarchical-x strategies. The strategies can be applied to any fully-connected network.

- 4. System level: We develop a novel system-level Network Transcoder that maps all MPI collective operations in a schedule-less and contention-less manner to optical network configurations.

- 5. We analyse the scalability, cost, power consumption and computational speed-up of the proposed system/algorithms and compare it with EPS counterparts.

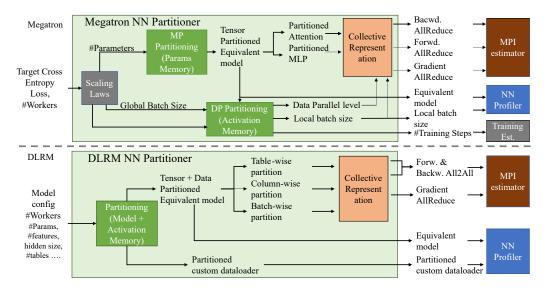

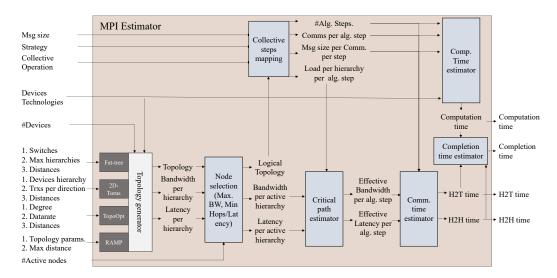

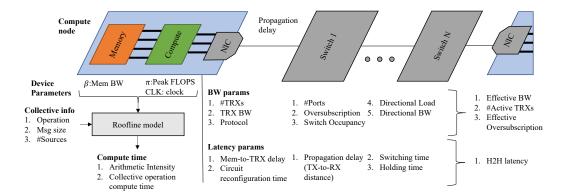

- 6. We assess Megatron Shoeybi et al. (2019) and DLRM training times with the RAMP system for different target losses and model sizes and compare them with EPS and OCS baselines.

We perform extensive simulations to compare RAMP with a plethora of EPS and OCS network topologies and technologies at the network level, MPI collective operations and application level with two representative large-scale distributed neural network models, Megatron and DLRM. We show that the co-design of network technology and architecture of RAMP leads to a 38- $42\times$  reduction in energy consumption and up to  $12.4\times$  reduction in cost per bit with respect to current EPS systems. RAMP's architecture offers both significantly higher node-to-node I/O capacity and full bisection bandwidth with inherent broadcast and nanosecond topology reconfiguration capability. Compared to current electronic switched systems, the RAMP system achieves an improvement from a factor of  $7.6 \times$  (for reduce-scatter) to  $171 \times$  (for all-toall) in completion times across different MPI operations. The values reflect the improvement against the best-performing strategy for the best EPS and OCS topologies at maximum scale using a 1GB message size. We assess the individual contributions of network architectures, network bandwidth and MPI operations on MPI collective completion times (in sec.8). The proposed system is able to achieve a  $1.01-16.7\times$  speed-up and  $7.8-58\times$  faster iteration time in Megatron and DLRM DDL training time, respectively, as well as 23.8-85 percentage points decrease in communication time contribution when compared to the OCS and EPS baselines for maximum scalability systems.

#### 2. Background and motivation

Network and interconnect technologies are limiting factors for the performance of High-Performance Computing (HPC) systems. Recent benchmarks showed that only 5% of peak compute performance of HPC systems can be achieved on practical workloads and network overhead represents one of the main bottlenecks Zhu et al. (2021); Hemsoth (2016). Considering that improvements in hardware and application requirements are growing at a faster pace than interconnect technologies Wiggers (2021); Ballani et al. (2020), the network overhead becomes the significant bottleneck in the system.

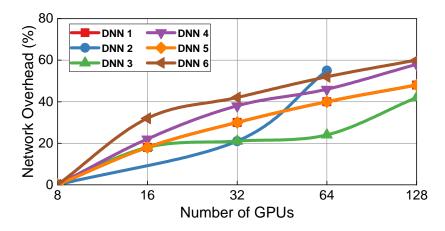

Figure 1: Network overhead of different large-scale Deep Neural Networks with a different number of devices. Figure taken from Wang et al. (2022)

Previous research has shown that training large-scale deep neural network (DNN) models lead to significant network overhead (40-60% even for using as few as 128 nodes) Wang et al. (2022), Fig.1. The demand for bigger and more predictive models is increasing at an exponential rate; the number of neural network parameters is doubling every 3-6 months. This forces the use of more workers and, in turn, leads to higher network overheads on training times. Two key factors that affect the communication/network overhead are the DDL partitioning strategy (sec.2.1) and the DDL scaling method (sec.2.2) used.

At the core of these approaches are the MPI collective operations, which are a set of operations needed to perform data processing across multiple devices sec.2.3. The network overheads are caused by the use of over-subscribed and low-bandwidth EPS networks that also force the use of sub-optimal

strategies across a range of MPI collective operations (e.g all-gather, all-to-all). Therefore, the network bandwidth, network connectivity and MPI strategies of current systems must significantly improve in order to unlock the scalability and performance of DDL systems.

Limitations of current EPS systems and proposed OCS architectures will be explained in sec.2.4 and sec.2.5 respectively.

#### 2.1. DDL partitioning methods

There are three main methods for partitioning a DL job: Data Parallelism (DP), Model Parallelism (MP) and Hybrid Parallelism (HP), which is a combination of DP and MP. **DP** consists of replicating the same model on multiple workers, where each worker processes a different set of data (local batch). In this way, the overall system can process a larger global batch while keeping the iteration time of each worker constant. At the end of each training step, the workers must share their weight updates (gradients). Using larger batch sizes reduces the number of iterations required to converge, reducing the overall training time.

MP consists of partitioning the DNN model between workers who act on the same batch of data. This requires multiple activation/gradient communications between workers within a training iteration. The partitioned DNN model generates multiple different local ML computations for each worker (partitioned local computational graph). When dealing with large models, MP is required as it reduces the memory footprint for a single worker.

#### 2.2. Bandwidth Requirements for DDL applications

There are two main ways to scale DDL jobs: weak and strong scaling. Weak scaling aims at increasing the throughput per training iteration in terms of samples/sec by increasing the number of workers. This is mainly performed using Data Parallelism (DP), which ensures a constant computation and communication time with scaling. These properties make it the most commonly chosen distribution technique, as it does not require an increase in node interconnect bandwidth at scale as the network overhead is approximately constant with the number of workers. This means that, when keeping batch size per worker large, Gbps per second communication might suffice to handle the partitioning, making the weak scaling approach a feasible option for current oversubscribed EPS HPC/DDL systems. However, this approach cannot scale indefinitely as the number of iterations to accuracy does not always decrease with the increase in global batch size Shallue et al.

(2018), leading to inefficient training. In addition, the memory footprint of the model does not decrease with scale, making the technique unfeasible to be used alone for large models, which are the main drive for application growth.

Strong scaling is decreasing the overall time per iteration. It is mostly achieved through Model Parallelism (MP). Achieving strong scaling is fundamental for the development of large models as it is capable of reducing the memory footprint of DNNs Khani et al. (2021); Wang et al. (2022). Achieving strong scaling is challenging because increasing the number of workers working on a specific batch leads to a decrease in computation time, which in turn, leads to more frequent communication steps involving the transmission of constant/increasing messages. This requires a super-linear increase of network bandwidth (multiple Tbps per node) and low latency communication. For this reason, current EPS systems can efficiently support strong scaling only within a single node that hosts 8-16 devices (without incurring significant network overhead).

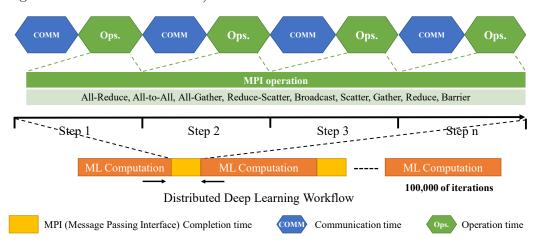

Figure 2: Example of DDL process, involving computation and MPI operations.

#### 2.3. MPI operations for DDL

Both scaling approaches for distributed training rely on MPI collective operations. MPI operations correspond to a series of communication steps between multiple workers followed by local operations with the goal of performing a distributed task. Depending on the strategy selected (e.g. Ringbased strategies), it is possible to (partly) overlap computation and communication to decrease completion time. A DDL workload, as shown in Fig.2,

can be viewed as a sequence of local ML computations (local partitioned computational graph) and MPI operations between the workers to share information. Overlap between MPI communication and computation, when application logic permits, leads to higher operational efficiency, however, for strong scaling scenarios this is unlikely. For example, in most MP cases, there is data dependency between subsequent operations (layers). In weak scaling, the weight update information sharing is represented by an all-reduce operation between workers. In strong scaling, different models require different types of activation sharing depending on their architecture and partitioning strategy, leading to different MPI operations for different models. The most widely used are all-reduce (e.g. Megatron Shoeybi et al. (2019)), all-to-all (e.g DLRM Naumov et al. (2019), Switch Transformer Fedus et al. (2021)) and all-gather (MoE Jacobs et al. (1991)). Different collective operations have different requirements on the network. Operations such as all-reduce and all-gather, allow effective communication on oversubscribed and limited connectivity systems (sec. 8.2). On the other hand, data-intensive operations such as all-to-all benefit from full bandwidth connectivity between all devices (sec. 8.2). For this reason, high and full-capacity connectivity between all device pairs is needed to minimize collective completion times.

#### 2.4. Limitation of EPS systems

One possible solution to achieve strong scaling and meet the network requirements of fast-growing applications consists in increasing the capacity of EPS systems. However, this approach leads to serious challenges. Increasing the capacity of EPS in terms of I/O bandwidth and transistor density is becoming hard to sustain due to physical limitations Ballani et al. (2020). It has been argued that the cost and power of switches are unlikely to stay constant above two generations, resulting in an increase in cost and power and eventually hitting a wall in capacity with standard EPS Khani et al. (2021). Higher capacity switches may still be created by hierarchical/Clos construction of smaller ASICs, at the expense of cost, power and complexity Ballani et al. (2020). Another option is creating parallel networks by replicating copies of EPS systems to increase the overall bandwidth. However, this type of solution leads to unsustainable power and cost as shown in section 4.3. To allow higher capacity systems, limited connectivity networks, such as Toruses and Meshes (e.g. Google TPU Pod Tao Wang (2021)), have been proposed. However, these approaches lead to high-diameter topologies and inefficient node bandwidth and resource utilisation.

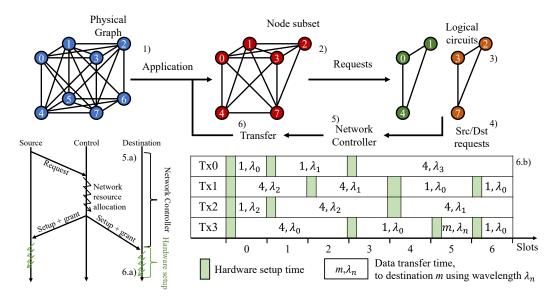

Figure 3: Diagram representing the process to accommodate an OCS request, with transmission example by the different transceivers of node 0 for the described logical circuit.

#### 2.5. OCS for Distributed Deep Learning (DDL) systems

Optical interconnects are capable of achieving high bandwidth low latency communication at scale and are a promising technology to meet the future requirements for DDL and HPC jobs.

Packet switching following one-way reservation (in the form of EPS) is the underlying transportation method used in DCNs and HPCs. This is due to the fact that it allows the creation of highly scalable networks, distributes its forwarding rules to each node, handles diverse flows due to variable packet size structures and has the ability to queue and manage flows along the path Zervas and Benjamin (2019). However, packet-switched networks require complex control methods such as admission and congestion, buffer/queue management and complex addressing Zervas and Benjamin (2019). While these can be handled by electronic chips such as ASICs in EPS systems (with the limitations described in sec.2.4, the equivalent is not possible in optical networks. This is due to the fact that optical technologies are not able to replicate such functionalities due to limited and rigid data processing capabilities (limited optical computing performance Zervas and Benjamin (2019)) and storage (lack of high-capacity and high-bandwidth enough photonic memories Alexoudi et al. (2020)) Zervas and Benjamin (2019). For

these reasons, Optical Packet Switching (OPS) cannot be considered a feasible solution for HPC and DCN applications. Circuit switching, which was widely used in electronic networks before EPS Benes (1965), can deliver guaranteed and deterministic traffic without the need for any of the packet-switching complex methods Zervas and Benjamin (2019); Benjamin et al. (2020), making it compatible with optical technologies.

Optical circuit switching (OCS) has been proposed as a possible replacement for EPS networks for DCN and HPC systems. This type of system decouples the data to the control plane and it could lead to a significant reduction in cost and energy consumption while being capable to scale to high bandwidth and low deterministic latency.

In OCS, the control and scheduling are separate from the data, leading to different operations compared to EPS networks. A flowchart describing the transmission for OCS systems is shown in Fig.3. As for EPS, the 1) application is placed onto a subset of nodes of the physical graph and during its lifetime will generate 2) communication requests between one or multiple workers. However, these requests are handled differently, as they are first converted into 3) logical circuits. The logical circuits contain all the sources and destinations to which the requesting node is involved and represent the overall flow of information in discrete time periods. The logical circuits generate a set of 4) source-destination requests to perform the communication. These set of point-to-point requests are sent to a 5) network controller which allocates the network resources in a synchronous manner. All devices have to transmit synchronously, in a discrete period of time called timeslots. The controller allocates the transceivers, path, wavelength and timeslots to allow communication (5.a). Once the resources are allocated, the setup instructions are sent to the source and destination and their physical system 6.a) is to be reconfigured. The time taken for slots and resource allocation by the network controller (5.a) can be pipelined and does not affect the throughput of the communication, as different data for previously scheduled requests are transmitted in parallel. The time taken for the hardware to configure to allow the transmission is called hardware reconfiguration/setup time or switching time (6.a). During hardware setup no data can be transmitted, effectively limiting the throughput. An example of how the communication looks like for multiple nodes is shown as 6.b) in Fig.3, where the timeslots, path (destinations) and wavelength have been allocated for different transceivers for node 0 for the example logical circuit. The green shaded region represents the hardware reconfiguration time and the white region is the payload transmission time. It needs to be noted that, due to the discrete and synchronous nature of OCS, the overall timeslot might not be fully utilised for transmission. The total number of concurrent transfers per path in an optical network depends on the total amount of wavelengths.

In spite of the multiple advantages that OCS brings, there are significant challenges that prevent the implementation and adoption of these systems for large-scale DCN and HPC.

- 1. One of the main challenges is the control plane, as it is now separate from the data. Fast large-scale scheduling with low latency and high throughput for the traffic is challenging at a large scale, leading to multiple proposals to use schedule-less systems Ballani et al. (2020). However, some promising results have been shown in the development of large-scale scheduling systems Benjamin et al. (2020).

- 2. Fast hardware setup time is required to allow efficient data transmission. In fact, the timeslot duration and minimum message size are directly dependent on it. The timeslot duration needs to be significantly larger (> 10×) than the circuit reconfiguration time to limit the overhead. This affects the utilisation, latency and goodput of the network.

- 3. Synchronisation of transmission for all devices is required to avoid contention. Recently proposed systems have been shown to be capable of synchronising thousands of devices for OCS Inggs et al. (2015).

- 4. Change in paradigm to existing networks is required. Implementing OCS systems would require a significant change in the communication stack of existing systems, by removing all communication protocols and switch-centric network representation.

However, due to the previously discussed limitations of EPS, OCS systems need to be explored and these challenges resolved to meet future HPC and DCN application requirements.

#### 2.6. Previous OCS limitations

Recently, there have been other OCS network architectures proposed for HPCs and DCNs. However, none of the previously proposed systems is capable of meeting all the requirements necessary for HPC and DDL applications. Between these systems, two architectures based on 3D-MEMS/patch panels OCS have been proposed: TopoOpt Wang et al. (2022) and SiP-ML OCS

Khani et al. (2021). These topologies might allow full-bandwidth connectivity between nodes at large scale (1024 and 384 directly connected nodes). However, they are affected by long circuit reconfiguration times, defined by the switching technologies (>10ms and >s for 3D-MEMS and patch panels respectively). These properties make in-application circuit reconfiguration unfeasible as it would lead to significant overhead and they require static circuit pre-allocation Wang et al. (2022). For this reason, for each logical circuit in the application life span, a physical path should be allocated. This limits the effective bandwidth available at any time between device pairs and limits the number of devices that a node can be connected to (communication degree). This might lead to low bandwidth communication and high-diameter logical and physical topologies, which lead to inefficiencies. To mitigate these problems for DDL applications, Khani et al. (2021); Wang et al. (2022) developed custom partitioning methods which consider these physical limitations. In Wang et al. (2022), it has been argued the need for fast circuit reconfiguration networks for DDL applications.

Fast circuit reconfiguration OCS systems have been previously proposed for DCN and HPC applications. For HPC and DDL applications SiP-ML Ring Khani et al. (2021) and TeraRack Khani et al. (2020) have been proposed. These systems use Micro Ring Resonators (MRRs) which lead to  $\sim 25 \mu s$  reconfiguration delay, which could allow in-application dynamic circuit reconfiguration while allowing high-capacity node-to-node connectivity. However, both of these systems are limited by scale and connectivity. In fact, both of these topologies are realised through a wavelength selection add and drop ring connectivity, which limits the number of nodes available in the system to the number of available wavelengths available for the transceiver (namely 256 Khani et al. (2020)). In addition due to the optical ring's physical topology (which allows communication with all nodes in the ring without passing through the neighbouring compute hops), the number of optical hops and network components between node pairs increases linearly with the diameter between node pairs, significantly varying the signal quality between source-destination pairs. The signal quality effectively determines the connectivity of the system, limiting the connectivity of a node to its 16 closest neighbours. Due to this property, all-to-all connectivity is not achievable and complex multi-stage control and routing need to be implemented. In addition, these topologies are largely affected by a single point of failure, where if a single hop is malfunctioning all communication passing through it is lost.

For DCN, multiple architectures which allowed large circuit reconfigura-

tion at high scalability have been proposed. Between these, PULSE Benjamin et al. (2020) and Sirius Ballani et al. (2020) are OCS systems which allow nsspeed switching and large scalability (>10,000 nodes for PULSE, not specified for Sirius). While these systems meet the requirements in terms of scalability and reconfiguration, they are limited by node-pair capacity. In fact in these networks, each node pair is connected by a single transceiver, which limits the node-to-node capacity. In addition, these networks suffer from a single point of failure, where a transceiver or network component malfunctioning leads to one or multiple nodes being unable to communicate to racks and/or clusters. Moreover, the single transceiver connectivity for a rack of devices limits the devices each node can communicate with at the same time. In these types of networks, another main challenge is scheduling. PULSE demonstrated a promising scheduler that could handle thousands of devices while being reliable to skewed and varied traffic Benjamin et al. (2020), but it is not capable to manage deterministic, long-lasting patterns such as the ones for collective operations. Sirius, on the other hand, uses a scheduless round-robin approach for communication Ballani et al. (2020), with limited transmission epoch duration, which makes it unsuitable for skewed and large flow traffic.

In addition, the MPI collective operation strategies considered by these OCS architectures (Wang et al. (2022); Khani et al. (2021)) have been developed for EPS systems without taking into consideration the network architecture characteristics. MPI collective operations for OCS systems should take into consideration the physical properties of the network (e.g. path, wavelength) such that the number of algorithmic steps and completion time is minimised while avoiding contention. This also synchronous scheduling and communication to take advantage of the deterministic latency properties. These characteristics are not present in EPS systems, as each packet can be sent to any destination at any time, without pre-determined circuits and latency (which both depend on the switch buffering and forwarding) Zervas and Benjamin (2019).

#### 3. RAMP Architecture

We introduce the RAMP architecture — the first large-scale, high-capacity, full bandwidth architecture for DCN and HPC/DDL systems. It provides

1. High-capacity communication between node pairs (>12.8Tbps), making it suitable for HPC and DDL application requirements.

- 2. High scalability (>4096 nodes). Capable of handling increasingly complex workloads.

- 3. Nanosecond level circuit reconfiguration through wavelength switching and broadcast-and-select space switching. The system takes advantage of Time-Division Multiplexing (TDM), Wavelength-Division Multiplexing (WDM) and Space-Division Multiplexing (WDM). This allows each node to communicate to any other node with virtually no communication degree constraints; allows using collective operations with logical graphs with significantly lower diameters without sacrificing bandwidth Wang et al. (2022); allows the proposed architecture to handle fast-changing circuits which are required for DCN traffic.

- 4. Port-level all-to-all connectivity and re-arrangeable or strictly non-blocking communication. Any transceiver can transmit/receive information to/from any node. Communication blocking probability depends on the selection of the sub-network only.

- 5. Fully passive interconnect system. Removing complexity from the core of the network and moving it to the edge.

- 6. Unrestricted multi-node communication and reliability, without any single point of failure. Every node can talk to every other node using multiple possible paths, and any failure for transceivers/network components still allows all-to-all communication just at a slightly decreased capacity.

These properties make RAMP the first architecture suitable for both HPC and DCN systems.

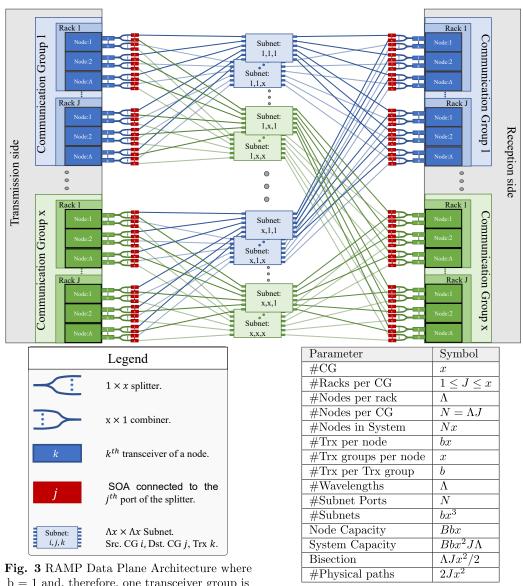

b = 1 and, therefore, one transceiver group is shown as a single transceiver.

Table 2: Parameters of the RAMP architecture

#### 3.1. RAMP Data Plane

The RAMP data plane consists of parallel subnets arranged in communication groups and transceivers. There are x communication groups, where each group contains J racks. The maximum number of racks per communication group is J=x. Each rack contains  $\Lambda$  devices or nodes, where  $\Lambda$  is the total number of available wavelength channels. Hence, the maximum number of nodes in one communication group is  $N = \Lambda x$ . Each node is equipped with x transceiver groups, each containing b transceivers sharing the same tunable light source and the same control instruction but different spatial planes. An increase in the b parameter leads to an increase in node capacity for the same control complexity and reduced energy per bit at the cost of a larger number of components. Further explanation in sec.4.2. Each transmitter is connected to a 1: x splitter, creating x possible paths per transmitter. Each path is selected by activating the Semiconductor Optical Amplifier (SOA) Alkharsan et al. (2022) attached to each port of the 1: x splitter and connected to a different sub-net and therefore, a different communication group. In this way, each transmitter is able to communicate with every communication group. Each receiver is connected to a x:1 combiner so that each receiver can receive information from every communication group. Under the proposed network configuration, the  $i^{th}$  transmitter of any node can send information to the  $i^{th}$  receiver of every node, enabling all-to-all transceiver-wise communication. The topology requires a total of  $bx^3$  sub-nets, i.e. a sub-net for a communication group pair per transceiver. Each node is equipped with a single NIC handling all transceivers.

As shown in Table II in Fig. 3, the RAMP architecture scales up to  $\Lambda x^2$  nodes, providing a total capacity of  $bB\Lambda x^2$ , where B is the effective line rate of each transceiver. The bisection bandwidth is  $\Lambda J x^3/2$ , the total number of fibres is  $2bJx^3$  (same as for the PULSE architecture  $2x^4$  Benjamin et al. (2020)), and the total number of physical links required is  $2Jx^2$  (compared to  $2x^3$  of PULSE Benjamin et al. (2020)), as paths can be grouped/ribboned by racks and source-destination communication groups. Source-destination selection and circuit reconfiguration are performed through path/transceiver, wavelength and time-slot mapping.

There are three possible choices for the subnet: (i) a simple star coupler with N ports (Broadcast and select, B&S), (ii) J parallel  $\Lambda \times \Lambda$  arrayed waveguide gratings (AWGRs) followed by  $\Lambda$  parallel  $J \times J$  star couplers mixing information between same ports of each AWGRs (Route and Broadcast, R&B) or (iii) the same AWGRs followed by SOA based  $J \times J$  crossbars switch (Route and Switch, R&S).

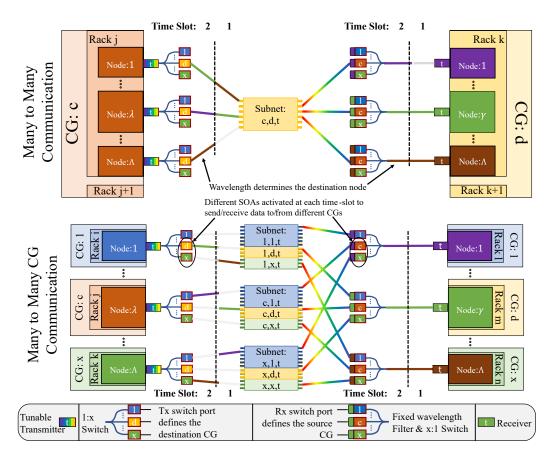

Figure 4: Example of a many-to-many communication pattern across different time slots between nodes of a) same source-destination communication group pairs and b) different source-destination communication group pairs. Showcase the WDM, TDM and SDM (for different communication groups) principles of RAMP). The colour of the line represents the wavelength used to communicate at each time slot (1 & 2). The color of the line used at the transmission side for each timeslot matches the colour of the destination node and receiver line. This way the colour/wavelength maps source and destination for each node-pair (and transceiver) at any timeslot.

Figures Fig.4 and Fig.5 show how the RAMP architecture handles different communication patterns. It needs to be noticed that in both Figures the considered configuration of the RAMP architecture is a fixed receiver Broadcast & Select (B&S).

In Fig.4 the many-to-many communication pattern in multiple time-slots across multiple sources and destinations within a) single source-destination communication groups pair and b) multiple communication groups are shown.

For Fig.4.a) communication between multiple source nodes  $(1, \lambda, \Lambda)$  of rack i and communication group c and destination nodes  $(1, \gamma, \Lambda)$  of rack k and communication group d by using the  $t^{th}$  transceiver. At the transmission side each node has a tunable transmitter followed by a 1: x space switch (implemented by an SOA gated splitter), whereas at the reception side each receiver is preceded by a filtered (single wavelength) x:1 switch (SOA gated coupler), making it fixed receiver. Each node in a rack receives at different wavelengths represented in both Fig.4 and Fig.5 by receiving node, receiver and filter colour. Between the communication group pairs (c-d) for the  $t^{th}$ transceiver exists the single subnet: c, d, t which allows communication between all transmitter t of all source nodes in communication group c and all destination nodes of communication group d. To perform the communication and transmit through the correct subnet the correct port of the switches need to be selected at both the transmission and reception side. At transmission, the switch port corresponds to the destination communication group (port d is used to communicate to the  $d^{th}$  communication group) and at reception the source destination group. For both Fig.4 and Fig.5, the colour of the transmission switch port and subnet matches the one of the destinations communication group, and similarly, the colour of the receiving switch port matches one of the source communication groups which the ports receive from.

At each Time Slot, each node set its destination by selecting its receiving wavelength, as shown at the transmitting side of Fig.4.a) where the transmitting node  $(c, j, \lambda)$  sends info to node  $(d, k, \gamma)$  and (d, k, 1) by choosing wavelength  $\gamma$  and 1 for time slots 1 and 2 respectively. In each subnet, due to the broadcast principle, each active wavelength is available at each output port (represented by the rainbow colour in Fig.4 and Fig.5), the correct for each destination is recovered by the filter before each port of the 1: x switch. For both time slots as the communication group pair of the source and destination, nodes is constant, the ports d and c of the transmission and reception side switches respectively are selected. In a similar fashion, node  $(d, k, \gamma)$  receives from nodes  $(c, j, \lambda)$  and (c, j, 1) in different time slots have been tuned their transmitter at the  $\gamma^{th}$  wavelength.

Fig.4.b) shows a similar many-to-many pattern between different nodes  $(1, \lambda, \Lambda)$  for tx and  $(1, \gamma, \Lambda)$  for rx) in different racks (i, j, k) for tx and (i, m, n) for rx) of different communication groups (1, c, x) for tx and (i, m, n) for rx). Each pair of communication groups is connected by a subnet, accessed through a specific source and destination switch port selection. As in Fig.4.a) the

node selection in a rack is performed through wavelength selection for every time slot whereas different communication groups are accessed by gating different ports of the transmission and reception side switch. In the figure, node  $(c, j, \lambda)$  communicates to nodes  $(d, m, \gamma)$  and (1, l, 1) in different time slots by selecting wavelengths  $1, \gamma$  and gating the ports d, 1 and c, c for transmission and reception side switches respectively in each time slot. Different switch port pairs selection at each time slot lead to different communication group communication allowing effective port-level all-to-all communication with fast reconfiguration.

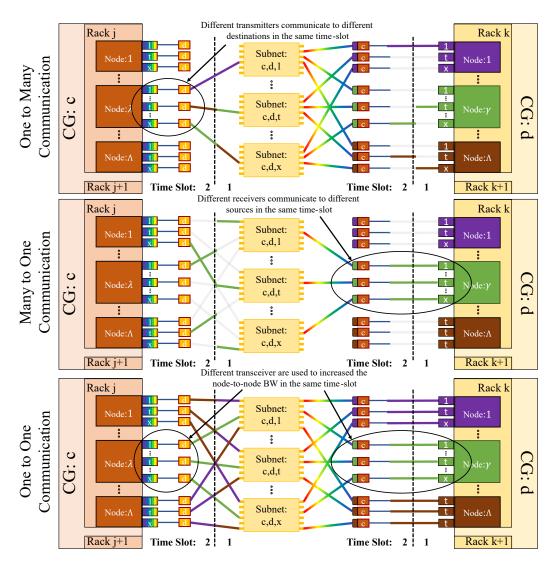

Figure 5: Example a) one-to-many, b) many-to-one and c) one-to-one communication patterns at each time slot between nodes with same source-destination communication group pairs. It shows the WDM, TDM and SDM (across multiple transceivers) principles of RAMP, therefore allowing high bandwidth (up to full capacity) communication between one or multiple node-pairs or sets.

Fig.5 shows different communication patterns per same time-slot: a) one-to-many, b) many-to-one and c) one-to-one. For all the communication patterns Fig.5 depicts the communication between multiple source nodes  $(1, \lambda, \Lambda)$  of rack j and communication group c and destination nodes  $(1, \gamma, \Lambda)$  of

rack k and communication group d by using multiple transceivers.

Fig.5.a) shows the one-to-many communication pattern from the source node  $(c, j, \lambda)$  to all the nodes of communication group d rack k. Each transceiver of the source node transmits in the same time slot to different destinations by selecting different wavelengths. If the destinations would have been in different communication groups different transmission and destination switch ports would have been selected for each time slot, similarly to Fig.5.b).

Fig.5.b) shows the many-to-one communication pattern, where the destination node  $(d, k, \gamma)$  receives at the same time from multiple destinations by using different transceivers.

Fig.5.c) shows multiple one-to-one communication patterns between different source pair destinations. In this figure, all transmitters of each source node are used to communicate to all receivers of the same destination node, such that full-capacity communication between node pairs is used at any time slot. It needs to be noticed that also only a subset o transceivers can be used between node pairs depending on the application requirements.

The described principles can be used at the same time to adapt the network requests and they are extensively used together for collective operations. It needs to be noted that in both Fig.4 and Fig.5 rack selection has not been performed. This is due to the fact that the signal between nodes with the same node number of different racks is coupled together, broadcasting the same information to all racks. This effectively creates contention in each subnet, however, the multiple paths between each source-destination pair allow communication to be re-arrangeably non-blocking, and when correctly scheduled up to full bandwidth.

It needs to be noted that both in Fig. 3, Fig. 4 and Fig.5 we show the architecture with b=1, so the case when a transceiver group is equivalent to one transceiver.

It is possible to create an equivalent Electrical Circuit Switched (ECS) RAMP architecture by replacing each subnetwork with a  $\Lambda J \times \Lambda J$  electrical switches and increasing the total amount of transceivers to  $bx^2J\Lambda(1+x)$ . However, this approach would require the use of high-capacity switches, it would incur electro-optical conversion which would increase energy consumption and increase the cost (number of transceivers and more expensive switches) and inefficiencies as only a portion of the transceivers could be active at all times. These characteristics make an electrical version of RAMP over-provisioned and cost-ineffective. Transforming the ECS to EPS switches

and transceivers would further increase costs and power consumption (explained in sec.2.4).

#### 3.2. Dynamic Traffic

While the focus of this work is on the deterministic traffic of MPI collective operations and the co-design of architecture and collective strategies (described in sec.6), it is important to note that different types of traffic can also be handled. In fact, dynamic traffic is prevalent in DCN and HPC applications and secondary for DDL workloads. The RAMP architecture has been designed such that it is compatible with previously proposed OCS scheduling approaches such that the dynamic nanosecond level circuit scheduler presented in PULSE Benjamin et al. (2022). This scheduler proved to deliver skew-tolerant performances whilst achieving above 90% throughput and tens of millisecond tail latency, making it suitable for DCN and HPC applications. However, to allow this scheduler to work on a RAMP architecture, we need to limit the connectivity such each transceiver is mapped to a specific rack and therefore limiting the effective node-to-node capacity. A novel scheduler which uses the multi-path and full-capacity capabilities of RAMP whilst taking into consideration the sub-network contention is currently under development.

#### 4. Optical Technologies

In this section, we introduce the optical technologies powering the proposed architecture describing the operating principles of the system. These technologies have been experimentally demonstrated in prior art. The components, scalability and operating properties (cost and power consumption) are discussed. Further, a more detailed explanation, with in-depth optical properties analysis and architectural features and characteristics will be discussed in a follow-up optical manuscript.

#### 4.1. Components

Switching in the RAMP networks is achieved by configuring the wavelength/time-slot/path at the end-node transceivers. For wavelength switching, at the transmitter side, we assume the employment of wavelength tunable sources (WTSs). WTSs composed of time-interleaved tunable lasers (spanning a wide range of 122 wavelength channels) with gated SOAs capable of achieving < 1ns wavelength switching Thomas et al. (2021) have been previously

demonstrated. On the destination side, the receiver can be either tunable or fixed depending on the subnetwork choice. If the B&S network is selected, the receiver can operate at a fixed wavelength by the use of passive filters. However, wavelength tunability is required when considering sub-networks with wavelength routing functionalities. The tunability can either be implemented by a wavelength filter gated by SOAs or by the use of an additional tunable laser for coherent detection.

For space switching, broadcast and select filter-based SOA-gated couplers and combiners are used. Using SOA-based gating as a space-switching mechanism allows sub-nanosecond path selection Parsonson et al. (2020). In addition, SOAs are also used for amplification.

Time-division multiplexing is achieved by using pre-defined timeslots. The synchronisation and Clock Data Recovery (CDR) uses the same principle as the one proposed in PULSE Benjamin and Zervas (2020) and Sirius Ballani et al. (2020) and described in Clark and et al. (2018). The duration of the timeslot has been selected such that the maximum reconfiguration overhead is 5%, leading to a minimum data-transfer slot of 20ns.

Transceiver node capacity of (B=) 400 Gbps can be achieved using low-energy silicon-organic hybrid (SOH) modulators Wolf et al. (2018), which is the assumed line-rate for the analysis in this paper. Using this data-rate the minimum message size that can be transmitted in a timeslot per transceiver is 950B. Such small messages are common in DCN traffic and HPC MPI collective operations at large scale. Nanosecond circuit reconfiguration time is fundamental for HPC application as it allows effective transmission of small message sizes and the use of dynamic collective strategies for MPI operations (sec.5). When the circuit reconfiguration time is smaller than the node I/O time (transceiver and computation delay), it will not create any overhead in the transmission time. Since transceiver (I/O) delays can be as low as a few tens of ns Andreades et al. (2019), switching reconfiguration times should follow suit.

Star-couplers are used as broadcast technology at both the edge and core of the network. At the edge, they are used in the form of SOA gated splitters and combiners to create 1:N and N:1 switches. At the core, we propose the use of N:N star-couplers, which have been shown to scale to 1024 ports Funnell et al. (2016) as an individual component and larger when using a cascaded approach. This approach makes the network passive and cost-effective.

The wavelength routing component considered for the network core is AWGR, which has been proven to scale to 100s of ports with low loss Ballani

et al. (2020).

The combination of these technologies allows the RAMP transceiver and network of achieving ns circuit reconfiguration while achieving high node capacity.

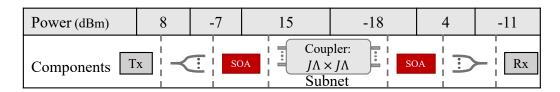

#### 4.2. Scalability

Figure 6: Power budget after each component in the path for most constrained RAMP architecture at maximum scalability.

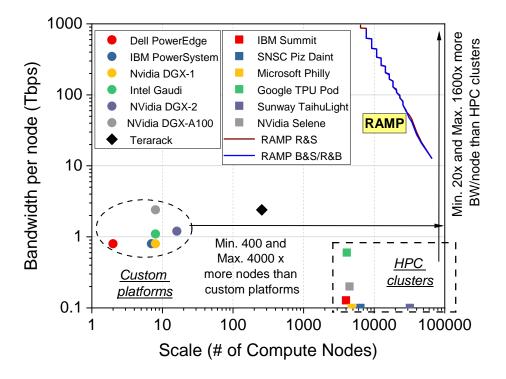

The scalability of the system in terms of end nodes is limited by the optical properties of the network. In fact, the limiting factor is the optical Signal-to-Noise Ratio (SNR) degradation and attenuation that the optical signal incurs at the output of each network component. To allow direct detection the optical power budget at the receiver side photodetector has to be above -15dBm and the minimum optical power across the path have to be above -20dBm to maintain good SNR. Using the architecture proposed and the components described in sec.4.1 under the lossiest configuration (B&S), this leads to a maximum scale of 65,536 nodes each having 12.8 Tbps node capacity. These results are obtained considering the following configuration which is going to be further analysed in sec.8:  $\Lambda = 64, x = J = 32, B = 400Gbps, b = 1$ . The power budget under the described configuration after each network component is shown in Fig.6.

Under the maximum scale conditions, the proposed system is capable of achieving larger scalability than current SoTA HPC clusters ( $> 5.5 \times$ ) while allowing significantly higher effective node-to-node bandwidth ( $> 20 \times$ ) than custom small-scale platforms. These characteristics give the RAMP architecture the upper hand with respect to SoTA HPC and AI system architectures Khani et al. (2020). A comparison between current and proposed HPC systems and RAMP in terms of bandwidth per node and number of compute nodes is displayed in Fig.7 using curves representing the different RAMP configurations. For this analysis, the number of communication groups x and the number of transceivers per transceiver group b have been modified while

the number of racks has been kept equal to the number of communication groups (J=x) and the number of nodes per rack has been kept constant  $(\Lambda=64)$ . By varying x from 32 to 10 and b from 1 to 256, the scalability in terms of nodes reduces to 4096 whereas the node capacity supported increases to 960Tbps. This shows the capability of the RAMP system to scale to future bandwidth requirements. Considering current SoTA technology, a RAMP system could allow full-capacity (288 Tbps), all-to-all communication between 12,544 Tesla DOJO tile Day (2021) accelerators. Currently, such accelerators can only be connected by using limited degree connectivity topologies such as meshes and toruses and limit the effective node-to-node bandwidth.

Figure 7: Comparison in bandwidth per node and system scale between RAMP and current or proposed systems Khani et al. (2020); DELL Technologies (2022); IBM Corporation (2021); NVIDIA (2021); Habana Labs Ltd (2019); NVIDIA Corporation (2019); NVIDIA Corporation. (2020); Summit (2021); Bernauer and Kashinkunti (2021); Jeon et al. (2019); Tao Wang (2021); Fu et al. (2016); Bernauer and Kashinkunti (2021). Figure adapted from Khani et al. (2020).

Similar scalability analysis can be performed while keeping constant other

metrics such as cost and power. Multiple configurations will be explored in future work.

#### 4.3. Cost and Power Consumption

In Tables 4.3, 4.3, the estimated cost and power requirements for the proposed architecture are estimated and compared to EPS systems for HPC and DCN at matched scalability (maximum RAMP scalability of 65,536 nodes) for different intra-to-inter server over-subscriptions (1:1, 10:1, 64:1).

The HPC system considered is a 3-Tier Fat-Tree SuperPod NVIDIA Corporation (2021a) architecture scaled to support 8,192 DGX-A100 NVIDIA Corporation. (2020) servers, each supporting 8 GPUs (65,536 GPUs) and exposing one 200Gbps HDR Infiniband transceiver per GPU NVIDIA (2021). This represents the 64:1 over-subscription ratio case. The switch used is the 40-port 200Gbps-per-port NVidia QM8790 InfiniBand switches Mellanox Technologies (2021); NVIDIA Corporation (2021b), as described in the reference architecture NVIDIA Corporation (2021a). It needs to be noted that intra-server (DGX-A100) connectivity is discarded (this leads to an underestimation of the effective network cost and power consumption).

|                             |               | Component<br>Cost (\$) |       | #items / network           |       |       |              |       |           |           |  |

|-----------------------------|---------------|------------------------|-------|----------------------------|-------|-------|--------------|-------|-----------|-----------|--|

|                             |               |                        |       | HPC SuperPod <sup>17</sup> |       |       | DCN Fat-Tree |       |           | RAMP      |  |

|                             |               | EPS                    | DCN   | 1:1                        | 10:1  | 64:1  | 1:1          | 10:1  | 64:1      |           |  |

| Transceivers for            | <b>EPS</b> 18 | 200                    |       | 25.2M                      | 2M    | 0.3M  | 50.3M        | 4.7M  | 0.8M      | -         |  |

|                             | OCS           | 600-                   | 1200  |                            | 2.1M  |       |              |       |           |           |  |

| Switch EPS 20               |               | 23,7k                  | 44k   | 530k                       | 49.7k | 8.3k  | 655k         | 61.4k | 10.2k     | -         |  |

| Coupler OCS                 | 30            | 000                    | -     |                            |       |       |              | 32.8k |           |           |  |

| Trxs. : Switches cost ratio |               |                        |       |                            | 25:75 |       | 19:81        |       |           | 93:7,96:4 |  |

| Total Network cost (B\$)    |               |                        | 16.8  | 1.57                       | 0.26  | 35.5  | 3.33         | 0.55  | 1.35-2.61 |           |  |

| Normalised cost (\$/Gbps)   |               |                        | 20.02 |                            |       | 42.38 |              |       | 1.62-3.12 |           |  |

Table 3: Cost estimated for RAMP OCS network compared to current state-of-the-art EPS HPC (SuperPodNVIDIA Corporation (2021a)) and DCN (Fat-Tree) networks scaled to 65,536 nodes with matched bandwidth of 12.8Tbps.  $\sigma$  represents the intra-to-inter system oversubscription ratio. To match the EPS system node to the RAMP one at 12.8Tbps ( $\sigma=1:1$ ), 64-128 transceivers (200-100 Gbps) per node and 64-128 copies of separate 3-tier Fat-Tree networks are presented for HPC and DCN, respectively. The OCS system uses x=32 transceivers each operating at 400Gbps.

A 3-Tier Fat-Tree system interconnecting 65,536 nodes (servers) is considered as DCN system. The system is based on Arista 7170-64c Arista (2021a) 64-port 100Gbps-per-port switches. As transceivers, 100Gbps QSFP optical transceivers Arista (2021b) for inter-rack communication and 100Gbps copper twinax cables for intra-rack Fiberworks (2021). This choice has been performed due to the different power drawn by the different transceivers (as shown in Table.4.3)

For both EPS networks, the cost of \$1/Gbps is assumed Taubenblatt (2019). To match the node (GPU) I/O bandwidth to the one of the proposed RAMP system (12.8 Tbps, considered as intra-system bandwidth), additional ports per node are exposed and parallel copies of the network are created. At matched bandwidth (1:1 intra-to-inter server oversubscription), in the HPC system, each GPU exposes 64 200Gbps ports (64 × 8 for DGX-A100) with 64 independent parallel SuperPod networks. For 1:1 over-subscription in Fat-Tree DCN case, each node of the DCN exposes 128 100Gbps ports and all nodes are connected through 128 parallel independent networks. For the 10:1 oversubscription (1.2Tbps inter-node bandwidth), the number of ports and parallel networks for HPC and EPS is 6 and 12, respectively. Equivalently, for the 64:1 these numbers are 1 for HPC (same as in the SuperPod architecture NVIDIA Corporation (2021a)) and 2 for DCN.

We consider for the RAMP architecture the maximum scalability system with 65,536 nodes (x = J = 32, b = 1 and  $\Lambda = 64$ ) with 400Gbps modulators (12.8Tbps total capacity), as described in sec. 4.1, 4.2. For the OCS networks, we propose the use of integrated transceivers (with the laser, modulator, SOAs) and assume cost of 1.5-3× greater than that of EPS transceivers. The cost of the optical coupler for OCS is assumed to be \$3000, estimated from Arévalo et al. (2017). For RAMP, the power consumption of the transceiver and switching elements is estimated by considering the individual power consumption of the relevant components described in sec. 4.1 and reported in Benjamin et al. (2020); Moralis-Pegios et al. (2021); Grobe and Eiselt (2013); Koos et al. (2016); Williamson et al. (2020); Yoshimatsu et al. (2012); Figueiredo et al. (2015). In the power analysis, we consider the power consumption for transceivers with both fixed and tunable wavelength reception.

Table.4.3 shows that the normalised cost (\$/Gbps) of EPS networks is significantly higher than the RAMP counterparts. For the EPS networks, the cost is switch-dominant, having a transceiver:switch cost ratio of 25:75 and 19:81 for HPC and DCN respectively. On the other hand, for the OCS-based

|                     | Units           | HPC<br>SuperPod                |      |      | F                            | DCN  | RAMP |           |

|---------------------|-----------------|--------------------------------|------|------|------------------------------|------|------|-----------|

| Oversub. $\sigma$   | -               | 1:1                            | 10:1 | 64:1 | 1:1                          | 10:1 | 64:1 | -         |

| Switch<br>Comp.     | -               | NVidia<br>QM8790 <sup>43</sup> |      |      | Arista<br>7170 <sup>45</sup> |      |      | SOA<br>46 |

| Power/<br>Comp.     | W/Comp.         | 404                            |      |      |                              | 320  | 0.88 |           |

| Comp./<br>path      | #/path          | 11                             |      |      |                              | 11   | 2    |           |

| Trx.<br>Power       | W               | 4.35 $48$                      |      |      | 0.5-3.5<br>50                |      |      | 3.4-3.8   |

| Energy/<br>bit/path | pJ/<br>bit/path | 383                            |      |      | 400                          |      |      | 8.5-9.5   |

| Power/<br>Gbps      | mW/Gbps         | 365                            |      |      | 400                          |      |      | 85-95     |

| Total<br>Power      | MW              | 306                            | 28.7 | 4.8  | 336                          | 31.5 | 5.2  | 7.1-8     |

Table 4: Power Consumption of RAMP, SuperPodNVIDIA Corporation (2021a) and DCN Fat-tree Medhi and Ramasamy (2018); scaled to 65,536-node networks with 12.8 Tbps/node and all-to-all connectivity. Component: Comp., Transceiver: Transc.  $\sigma$  represents the intra-to-inter system oversubscription ratio.

RAMP architecture, we nearly eliminate the switching cost and significantly reduce the number of transceivers required per connection. Hence, RAMP, the transceiver:switch cost ratio is 93:7 - 98:2, with the overall normalised network cost reduced by a factor  $6.4\text{-}26.5\times$  to 1.62-3.12\$/Gbps. This also applies to the overall network cost at matched bandwidth (1:1) where the budget for EPS networks is  $\geq 16.8B\$$  whereas the RAMP network cost is  $\leq 2.16B\$$ . A similar cost to the proposed RAMP architecture is reported for EPS networks with 10:1 over-subscription (1.57-3.33\$ for HPC and DCN respectively) while offering 10 times lower capacity.

It is important to note that, compared to EPS systems, it might seem that the RAMP architecture is over-provisioned, due to the large number of sub-networks. However, differently to electrical switches, the coupler-based sub-networks are passive, inexpensive devices whose cost will further reduce with mass production, making the proposed interconnect feasible for largescale systems. When compared to PULSE Benjamin and Zervas (2020), the number of subnets required by RAMP to accommodate the same number of nodes is smaller (assuming the maximum scale network, PULSE requires  $32\times$  more subnets than RAMP). It also needs to be noted that, due to the passive properties of the sub-networks, the core of the interconnects does not need to be changed when the computational nodes are upgraded. Accommodating workers with higher data-rate in EPS systems requires substituting all network switches to models capable of handling the new line-rate leading to a short core network life cycle (around 4 years in DCNs). Similarly, in traditional active OCS switching systems such as 3D-MEMS, to take advantage of higher data-rate faster circuit reconfiguration time is needed, requiring the core switching infrastructure to be replaced periodically. On the other hand, RAMP, by using a passive core, does not require any substitution in the network with a higher data-rate, as all switching and line-rate dependent technologies reside at the edge. This means that, when upgrading to higher capacity nodes, the only networking component which requires change is the transceiver. This property significantly decreases recurrent costs.

In Table 4.3, the power consumption of the EPS and proposed OCS architecture is compared. Our study shows that RAMP consumes as low as 8.5-9.5 pJ/bit/path, whereas the HPC and DCN counterparts consume 383 and 400 pJ/bit/path respectively. It is important to note that while the number of paths of the RAMP system is significantly higher than the EPS counterparts, all subnets are passive consuming no power and each communication considers only a single chain of active devices. Therefore, the total amount of active paths at any time step is equal to the number of transceivers in the system  $(bx^2J\Lambda)$ . The overall network energy consumption only depends on the active paths. For this reason, the difference in energy per bit is matched by the overall energy consumption. EPS systems at matched scale (65,536 nodes) and matched bandwidth (12.8Tbps) would consume 306-336 MW, which is  $10 \times$  larger than the upper DCN network power budget of  $\sim 30 \mathrm{MW}$  Ballani et al. (2020). In contrast, RAMP consumes 7.1-8 MW leading to a reduction by a factor of  $38-47\times$ . When compared to the similar cost 10:1 oversubscribed EPS systems, the proposed architecture leads to a reduction in energy consumption  $\geq 3.6 \times$  for  $10 \times$  increase in bandwidth. The proposed system energy consumption is similar (36-66 % increase) to

the EPS networks for 64:1 oversubscription (current SuperPod node-to-node capacity and 2 copies of DCN system) while allowing 64 times higher network communication.

#### 5. RAMP Collective Operations

We propose a set of collective communication algorithms valid for the proposed architecture, arranged in a way such that contention is avoided and collective completion time is minimised. Each RAMP-x (x=MPI operation) collective operation follows a set of schedule-less reconfiguration steps through: a) parallel subgroup mapping (devices performing a subset of collective operations in parallel); b) information/message per node mapping at communication step; c) wavelength selection and subnet selection; d) time-slot mapping.

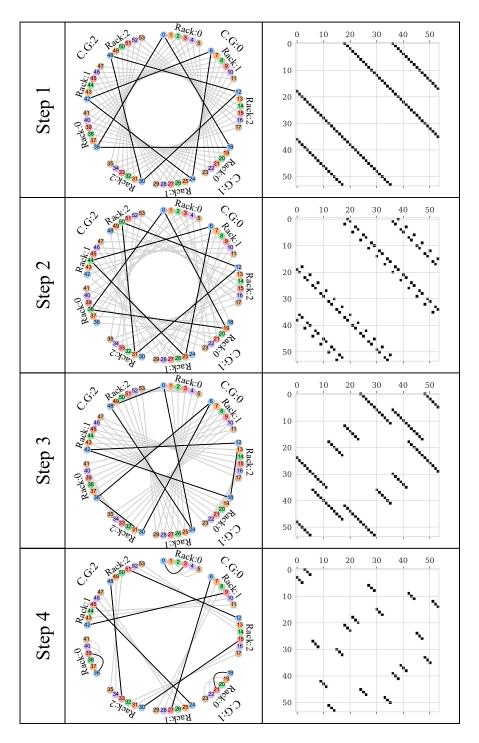

Figure 8: Visualisation of algorithmic steps subgroups for a 54-node  $(x=3,J=3,\Lambda=6)$  network example. Top-to-bottom: Communication steps 1-4.

The proposed strategy could be implemented on any port-level all-toall large-scale network without over-subscription. However, creating such networks using EPS or previous OCS networks would be expensive in terms of cost, power Medhi and Ramasamy (2018); NVIDIA Corporation (2021a), connectivity Benjamin et al. (2020); Ballani et al. (2020) and reconfiguration time Khani et al. (2021). The strategy, topology and scheduling have been co-designed to maximise performance and minimise power and cost to enable high capacity and scalability.

In the following sections,  $0 \le g \le x - 1$ ,  $0 \le j \le J - 1$ , and  $0 \le \lambda \le \Lambda - 1$  correspond to the local communication group, rack and device number (represented by colour in Fig. 8) respectively.

The strategy of MPI operations is performed in RAMP-x using 3-4 sequential algorithmic steps. An example that works as a visual aid for the reconfiguration steps for a strategy (e.g reduce-scatter) is shown in Fig.8, where  $\Lambda = 6$  and J = x = 3.

In this figure, the four rows represent steps 1-4. At each algorithmic step, parallel logical graphs, called subgroups, are created between a unique subset of devices, represented in Fig.8 as a line. The left side of Fig.8 represents the chord diagram of the RAMP network for each step, with nodes grouped in communication groups, racks and device IDs. The right-hand side of the figure represents the connectivity matrix for each node at each step. The number representation of each node for the connectivity matrix is shown as the number inside each vertex of the chord diagram. It needs to be noted that, while the graph is sparse, the network resources are maximised as each node uses x-1 transceivers for the first 3 steps and x for the last. In Fig.8, an example of 3 subgroups is shown with black lines and the others are greyed out in the background. The devices in each subgroup will perform a partial collective operation, depending on the MPI operation. In the first step of the reduce-scatter operation (Step 1), for each node, the overall message is divided in three portions and sent to different destinations in the subgroup. Then the information received is summed (reduced) in each node. The information portion that needs to be sent/received to/by each node is determined by the information map, and the transformation operations (e.g. summation) are dictated by the MPI operation. Each node now contains the sum of a unique 1/3 of the information of the message in each subgroup.

Note that we track the location of the information portion (Table 6.1.2) in every node after each communication step. For the following steps, the subgroups are selected such that they include only nodes with the same

information portion combinations. In the second step (Step 2), the message is further partitioned into 3 parts (1/9 of the original message), transmitted to the correct node in each subgroup and processed. In the same way, the third step (Step 3) is performed, such that each device contains the sum of a unique 1/27 of the original information (global reduce-scatter). In the fourth step (Step 4), the information is exchanged between pairs of nodes to complete information updates across all 54 devices (i.e. nodes). This step might have some variations depending on the formulation chosen for subgroup selection.

A similar process, performed backwards (Steps 4 to 1), is valid for all-gather, where unique portions of information are shared and gathered (concatenated) at each algorithmic step in every subgroup. In this way, starting with having 1/54 of the overall message, each node will contain a full 1/27, 1/9, 1/3 and whole information after Step 4, Step 3, Step 2 and Step 1 respectively. In general, the number of steps required by the algorithm can be described as  $\log_x(N)$  which, for the maximum scalability case of RAMP, is equal to 4. It is important to note that in cases where x=2, the algorithm effectively becomes equivalent to a recursive halving/doubling Thakur et al. (2005). Recursive halving doubling could be used as a collective operation, however, at the maximum data rate, would lead to high network contention. On the other hand, the proposed strategies have been co-designed such that bandwidth is maximised and contention is avoided by selecting different physical paths and time slots and wavelengths for communication.

The following sections provide further explanation on subgroup (sec.6.1.1), wavelength (sec.6.2.1), information map (sec.6.1.2), transformation (sec.6.1.3,sec.6.1.4), transceiver and path (sec.6.2.2) and time-slot (sec.6.2.3) selection.

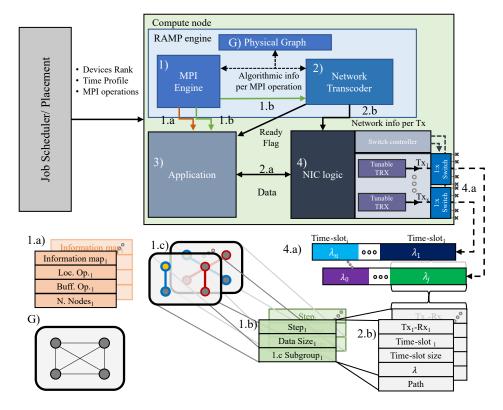

#### 5.1. Overall RAMP-MPI procedure

The core of the proposed research is the combination/co-design of architecture (physical graph sec.3), MPI strategy and scheduling algorithm. An overview of how these components come together to perform an MPI operation is shown in Fig.9. The process can be viewed in subsequent stages.

After a distributed task/job is placed by the job scheduler, the information about the ranks of the devices and the MPI operations are shared to all devices/nodes involved. This information is processed by the RAMP engine. The RAMP engine consists of two main components: 1) the MPI Engine (section sec.6.1) and 2) the network transcoder (section sec.6.2). In the first stage, as shown in Fig. 9, the MPI Engine (1) uses the physical graph (G)

Figure 9: Birdview of the MPI operational process from application to physical implementation.

and the MPI operation information to calculate the number of algorithmic steps required and generates information 1.a) and 1.b). 1.a) contains only the information required by 3) the Application to process and retrieve the data correctly for every step. 1.b) represents the algorithmic information required by the network transcoder and consists for every step, the data-size and the subgroup. 1.c) subgroup information represents the logical graph (a derivative of the physical graph G) of devices performing a partial MPI operation at each step. Note that in 1.c), the current node is represented as the yellow dot and the current subgroup as the blue connection in Fig. 9.

The network transcoder gets the information of 1.b) and G) and translates (trans-codes) it into instructions for the Network Interface Card (NIC). For each algorithmic step, the network transcoder generates instruction 2.b) for each individual transceiver to select time-slot size and number, transmitting/receiving wavelength and path. After processing these instructions, the

network transcoder sends Ready signal (2.a) to the 3) Application signalling that it is ready for transmission. The Application retrieves and transforms the data using 1.a) such that it could be correctly handled and transmitted by the NIC to perform the MPI operation. The Application shares the processed data to the 4) NIC, which using information 2.b), transforms it into 4.a) signal on the physical system. The NIC Logic tunes the transceiver at the instructed wavelength and selects the correct SOA path (to turn on) for the given time-slot size.

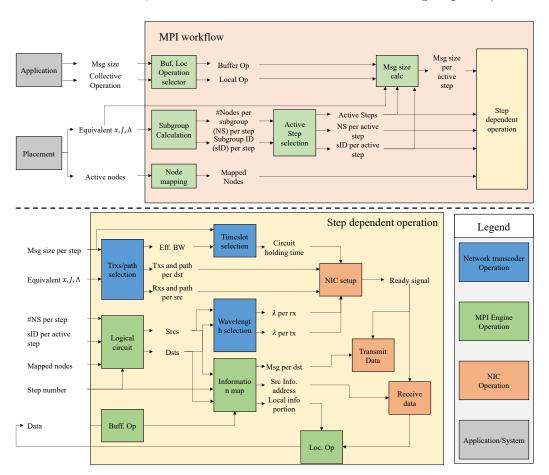

#### 6. RAMP Engine

The RAMP Engine is composed of two main blocks: MPI Engine and Network Transcoder. Together they handle the scheduling and communication while the processing is handled by the application.

#### 6.1. MPI Engine

The MPI Engine uses the physical topology, application, and MPI operation to generate the instructions required by the application and network transcoder to complete the collective operation.

#### 6.1.1. Communication subgroup map

| Step | #SG         | #NS         | Subgroup ID formula                                              |  |

|------|-------------|-------------|------------------------------------------------------------------|--|

| 1    | $\Lambda J$ | x           | $\lambda + \Lambda \cdot j$                                      |  |

| 2    | $\Lambda J$ | x           | $(\lambda - g) \mod x + \Lambda j + \lfloor \lambda/x \rfloor x$ |  |

| 3    | $\Lambda x$ | J           | $(\lambda + \Lambda(j-g)) \mod (\Lambda j)$                      |  |

| 4    | $Jx^2$      | $\Lambda/x$ | 1) $(\lambda - \lfloor \lambda/x \rfloor x) \mod x + x^2 j$      |  |

|      |             |             | $+((g-j\lfloor\lambda/x\rfloor) \mod x) x$                       |  |

|      |             |             | or                                                               |  |

|      |             |             | 2) $x^2j + x[(g - \lfloor \lambda/x \rfloor) \mod x] + d \mod x$ |  |

Table 5: Table showing subgroup ID selection. #SG is the number of subgroups, #NS is the number of nodes per subgroup.

The subgroup describes the set of devices (logical graph) that each node needs to share information (communicate) with at any algorithmic step.

Summary and formulae describing how each device is mapped to any subgroup at any communication step are shown in Table 6.1.1. For this mapping, the nodes in a rack are further divided into groups of x devices

| Step | Communication Group                                          | Rack                                   | Device ID                                                                                                                                                          | Variable                                     |

|------|--------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1    | $(g+\gamma) \mod x$                                          | j                                      | λ                                                                                                                                                                  | $0 \le \gamma \le x - 1$                     |

| 2    | $(g+\gamma) \mod x$                                          | j                                      | $ \begin{array}{c} (\lambda \bmod x + \gamma) \bmod x + \\ x \lfloor \lambda/x \rfloor \end{array} $                                                               | $0 \le \gamma \le x - 1$                     |

| 3    | $ [(g-j) \bmod x \\ +\gamma] \bmod x $                       | $ [(j+\gamma) \bmod J \\ -j] \bmod J $ | λ                                                                                                                                                                  | $0 \le \gamma \le J-1$                       |

| 4.1  |                                                              | j                                      | $\lambda \bmod x + x \times [(\lfloor \lambda/x \rfloor + 1) \bmod \lfloor \Lambda/x \rfloor]$                                                                     | NA                                           |

| 4.2  | $[(g - \lfloor \lambda/x \rfloor) \bmod x + \gamma] \bmod x$ | j                                      | $\lambda \bmod x + x \times [$ $(\gamma + \lfloor \lambda/x \rfloor) \bmod \lfloor \Lambda/x \rfloor$ $-\lfloor \lambda/x \rfloor \bmod \lfloor \Lambda/x \rfloor$ | $0 \le \gamma \le \lfloor \Lambda/x \rfloor$ |

Table 6: Table describing the formulas to calculate the RAMP coordinate (communication group, rack and device ID) the other members of the subgroup of the current node (node:  $g, j, \lambda$ ) at any algorithmic step. The Variable column shows the range of the variable to describe all members of the subgroup.

called device groups, where each node has a unique device group number from 1 to x.

The communication subgroups at each algorithmic step correspond to communication performed between unique sets of devices in different system dimensions. These consist of:

- **Step 1**: Nodes with the same node number, rack and different communication groups;

- **Step 2**: Nodes with sequential node numbers in the same device group, rack and different communication group;

- **Step 3**: Nodes with the same node number, different rack and communication group;

- **Step 4**: Nodes with the same device group number, different device groups, racks and communication groups or nodes in sequential device groups with the same device group number rack and different communication groups.

Depending on the selection of the formulation for the subgroup in Step 4, two different operations will be used. It has to be noted that when the first formulation is selected, the algorithm considered for the last step has to use strategies with one-to-one communication (such as ring, recursive halving/doubling Thakur et al. (2005) and Bruck's Bruck et al. (1997)), which might incur additional steps if the number of devices is greater than 2 (value

| Step | Information portion formula                       |

|------|---------------------------------------------------|

| 1    | $(g - \lambda - j - \lfloor \lambda/x \rfloor j)$ |

| _    | $\mod x$                                          |

| 2    | $(g - j - \lfloor \lambda/x \rfloor j) \mod x$    |

| 3    | j                                                 |

| 4    | $\lfloor \lambda/x \rfloor$                       |

Table 7: Formula describing what portion of the previous message should be received by a node at any algorithmic step.

at maximum scale).

The subgroup selection defines the logical circuit in which each node is part. The number of nodes per subgroup, as shown in Table.6.1.1, selects which of the four steps is active (#NS > 1). From the subgroup information, each node is able to know all sources and destinations active at any algorithmic step as described in Table.6.1.1.

Using the information provided in Tab.6.1.1, the members of each subgroup can be found from each algorithmic step by each node. The formulae to find the coordinate of the other members of the same subgroup for the current step of each node is shown in Table.6.1.1.

### 6.1.2. Information Map

The information map consists of a set of formulae describing the portion of the information that should be sent-received and processed by each node at each algorithmic step. The formulae describing the information map at each algorithmic step for data transfer-related strategies are described in Table 6.1.2. The combination of values generated by the table across each algorithmic step represents the node rank. This also represents either the portion of the original message or the collected information available at the node after the last operation depending on the selected operation. The decimal representation of the information value at all algorithmic steps represents the rank of each node in the collective.

#### 6.1.3. Buffer Operation

The buffer operation (Buff\_op) corresponds to the transformation performed on the message before transmission that is generated by the MPI Engine and defined by the MPI Operation. It takes three arguments: the message that needs to be processed (DATA), the number of nodes in the current subgroup (nodes) and the information map for the current step (info). As shown in Table 6.1.5, there are three types of operations:

- Reshape: the information vector is reshaped such that is divided into nodes addressable contiguous segments of the same size.

- Copy: the buffer size is increased by a factor of *nodes* and reshaped as described above. The original information will be in the segment of the array corresponding to the local rank of the node in the subgroup.

- Identity: no transformation is performed.

info is used to sort the message in such a way that the correct portion of the information is given to the correct transceiver.

### 6.1.4. Local Operation

The local operation ( $Loc_{-}op(DATA)$ ) is the transformation performed on the received data after a communication step. There are four operations:

- Reduce: associative operation, usually sum, between vectors received from different sources.

- Reshape: used only in the all-to-all operation. Transpose the information (considered as a 3D array) in the source, rank dimension and flatten it into a one-dimensional vector. This operation puts the information to be transmitted into a contiguous portion of memory in the correct rank order.

- Logical-AND between Booleans representing the presence of a correct message. Only used for barrier operation.

- Identity: no transformation is performed.

info is used to place in the correct order information coming from the NIC.

|                |            | Message             | size/step (n         | n = origina        | l msg size)          | Local    | Ops.     |

|----------------|------------|---------------------|----------------------|--------------------|----------------------|----------|----------|

|                |            | 1                   | 2                    | 3                  | 4                    | Op.      | Buff_Op  |

|                | RedScatter | m/x                 | $m/x^2$              | $m/(Jx^2)$         | $m/(J\Lambda x)$     | Reduce   | Reshape  |

| suc            | All-Gather | $m \cdot \Lambda/x$ | $m \cdot J\Lambda/x$ | $m \cdot J\Lambda$ | $m \cdot J\Lambda x$ | Identity | Copy     |

| atic           | Barrier    | 0                   | 0                    | 0                  | 0                    | AND      | Identity |

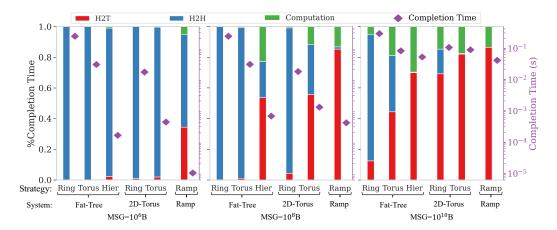

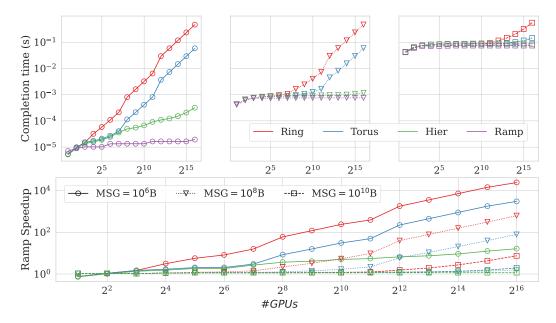

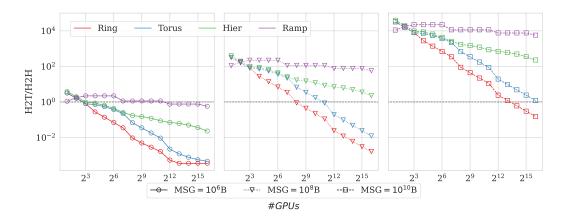

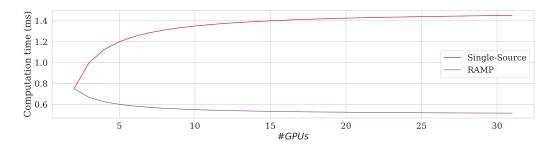

| MPI Operations | All-to-All | m/x                 | m/x                  | m/J                | $m \cdot x/\Lambda$  | Reshape  | Reshape  |