# InP DHBT Single-Stage and Multiplicative Distributed Amplifiers for Ultra-wideband Amplification

Temitope Odedeyi, *Member, IEEE*, Stavros Giannakopoulos, *Student Member, IEEE*, Herbert Zirath, *Fellow, IEEE*, Izzat Darwazeh, *Senior Member, IEEE*

Abstract—This paper highlights the gain-bandwidth merit of the single stage distributed amplifier (SSDA) and its derivative multiplicative amplifier topologies (i.e. the cascaded SSDA (C-SSDA) and the matrix SSDA (M-SSDA)), for ultra-wideband amplification. Two new monolithic microwave integrated circuit (MMIC) amplifiers are presented: an SSDA MMIC with  $7.1\,\mathrm{dB}$  average gain and  $200\,\mathrm{GHz}$  bandwidth; and the world's first M-SSDA, which has a  $12\,\mathrm{dB}$  average gain and  $170\,\mathrm{GHz}$  bandwidth. Both amplifiers are based on an Indium Phosphide DHBT process with  $250\,\mathrm{nm}$  emitter width. To the authors best knowledge, the SSDA has the widest bandwidth for any single stage amplifier reported to date. Furthermore, the three tier M-SSDA has the highest bandwidth and gain-bandwidth product for any matrix amplifier reported to date.

*Index Terms*—Distributed amplification, Single stage distributed amplifier, InP, MMIC, matrix amplifier, ultra-wideband amplifier.

### I. Introduction

Applications such as high resolution imaging, optoelectronic and instrumentation systems continue to drive demand for ultra-wideband integrated circuitry [2]. There are two key elements required to meet this demand: first is the availability of integrated circuit (IC) processes with ultra-wide bandwidth potential at appreciable gain, and the other is the development of circuit design techniques that maximise this potential. On the one hand, advancements in IC fabrication technology continue to deliver processes with increasingly higher gainbandwidth potential, creating the enabling technology to meet ultra-wideband demands. On the other hand, however, there is the need for circuit design topologies and techniques that optimise these new generation devices and enable them to deliver maximum benefits in performance [2], [3]. For instance, an InP HBT process with 130 nm emitter width, developed by Teledyne Scientific Company (TSC), has an extrapolated  $f_T$  of 521 GHz and  $f_{max}$  of 1.15 THz at bias condition of  $V_{CE}=1.6~\mathrm{V}$  and  $I_{C}=6.9~\mathrm{mA}$ . At  $600~\mathrm{GHz}$ , a single  $130~\mathrm{nm}$

This paper is an expanded version of [1], presented at the IEEE Asia Pacific Microwave Conference (APMC), Singapore, December 10-13, 2019.

HBT is expected to have approximately 6 dB gain [2], [3], however, realizable gain is expected to be much lower, as the matching network losses at hundreds of GHz frequencies are quite high, and transistors may only be practically operated at some fraction of their  $f_{max}$  [2], [4].

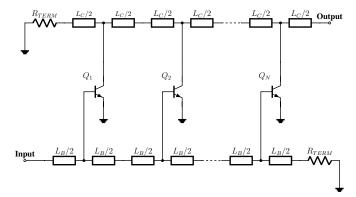

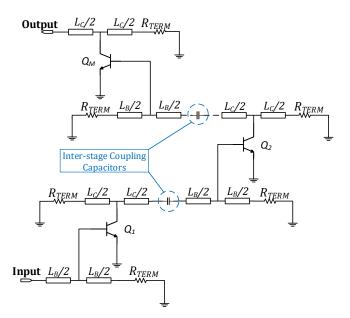

For over eighty years, the concept of distributed amplification, which allows the absorption of the bandwidthlimiting intrinsic capacitances of active devices into artificial transmission lines (ATLs) [5]-[7], has been employed in the design of amplifiers with bandwidth performance approaching the terahertz frequency bands (i.e. 0.3 - 3 THz) [1], [8], [9]. The conventional distributed amplifier (DA), as shown in Fig. 1, comprises of multiple gain cells with an additive gain mechanism. A signal applied at the input travels down the input ATL towards  $R_{TERM}$  where it is absorbed. The travelling voltage wave excites each transistor  $(Q_1 \text{ to } Q_N)$ , and transfers the signal to the output ATL through the transistor transconductance  $g_m$ . In the most commonly used scenarios, where the multistage amplifier is constructed from transistors of equal gains and the phase velocities of both lines are equal, the amplified signal from each of the transistors are all in phase and they add in the forward direction towards the output [6], [7], [10], [11]. It has also been shown that the input and output ATLs may also be purposively kept unequal, to provide specific gain [12] and filtering advantages [13], [14], with application in specialist communication systems.

More recently, in [15], the viability of a single stage distributed amplifier (SSDA) was demonstrated, showing that the distributed effect required to achieve the wideband performance in multistage DAs can also be observed in a SSDA. This was followed up by the introduction of the cascaded SSDA (C-SSDA), which improves the utility of the SSDA topology by providing additional gain at similar bandwidth, through a multiplicative gain mechanism [16]-[18]. The concept of the matrix SSDA (M-SSDA) was introduced in [19], as an alternative to the C-SSDA, with simulated results for an M-SSDA based on full foundry InP DHBT presented. The multiplicative gain mechanism of these topologies make them particularly attractive, as they make it possible to achieve significantly higher gain-bandwidth product performance, with fewer gain cells than the conventional, additive DA. Both derivative topologies of the SSDA have been described as multiplicative DAs in [1] due to their gain mechanism.

In this paper, we highlight the merits of the SSDA topology,

T. Odedeyi and I Darwazeh are with Department of Electronic and Electrical Engineering, University College London, London, WC1E 7JE, UK (email: t.odedeyi@ucl.ac.uk; i.darwazeh@ucl.ac.uk)

S. Giannakopoulos and H. Zirath are with the Microwaves Electronic Laboratory, Department of Microtechnology and Nanoscience (MC2), Chalmers University of Technology, SE-412 96, Göteborg Sweden (email: stagia@chalmers.se; herbert.zirath@chalmers.se)

Fig. 1: Schematic diagram of the conventional bipolar DA, with N gain stages.  $L_B$  and  $L_C$  are the input and output inductances per gain stage, repectively, required to achieve distributed effect, and  $R_{TERM}$  is the terminating resistance of the input and output ATL.

and its derivative M-SSDA, for the design of ultra-wideband amplifiers by considering its gain, bandwidth and noise potentials. We also report two new monolithic microwave integrated circuit (MMIC) amplifiers, based on an indium phosphide (InP) DHBT process with 250 nm emitter width: an SSDA MMIC with 7.1 dB gain and 200 GHz bandwidth, with a high frequency gain tuning range of 5 dB to 12 dB; and the world's first M-SSDA, a three-tier device, with 12 dB gain and 170 GHz bandwidth. The outline of this paper is as follows: Section II discusses the merits of the SSDA and the M-SSDA for ultrawideband amplification, considering the gain, bandwidth and noise performance. In Section III, the design and measurement of the new SSDA and M-SSDA MMICs are presented. Section IV concludes the paper.

# II. MERIT OF THE SSDA AND THE M-SSDA FOR ULTRA-WIDEBAND AMPLIFICATION

# A. The SSDA

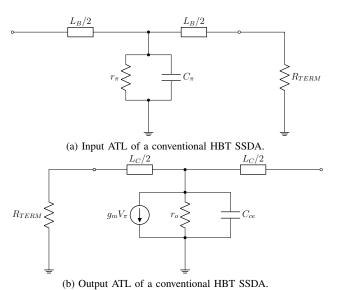

The SSDA topology offers an advantage in achieving ultrawideband performance, when compared to the conventional multi-stage DA. This advantage is attributed to the minimal high-frequency attenuative effects from the shorter lengths of transmission lines required in the SSDA. This merit is even more valuable in the design of DAs based on HBTs, as these have a forward biased PN junction between the base and the emitter, resulting in a complex characteristic impedance on the input ATL, as identified in [20], [21] and shown in Fig. 2 [11], [20], [22], [23]. This complex input nature of HBTs generally results in worse termination mismatch and higher input reflection with additional stages [9], [24]. Furthermore, the gentle frequency response roll-off of the single stage lowpass filters that make up the input and output ATLs of the SSDA is easily compensated for, using available attenuation compensation and bandwidth extension techniques, such as those presented in [24]–[27].

The SSDA, however, has two main limitations: limited gain from the single gain cell and lower signal to noise ratio compared to the conventional multi-stage DA. These limitations and how they may be addressed are discussed subsequently.

Fig. 2: Simplified equivalent circuits of the input and output ATLs of the HBT SSDA.  $C_\pi$  and  $r_\pi$  are the capacitance and dynamic resistance, respectively, at the base-emitter junction;  $C_{ce}$  collectoremitter junction capacitance; and  $r_o$  is the output resistance of the HBT.

1) Gain limitation of SSDAs: The gain  $(G_{DA})$  of the conventional DA is given by [6], [7], [11]

$$G_{DA} = \frac{1}{4} N^2 g_m^2 Z_{o-in} Z_{o-out}, \tag{1}$$

where N is the number of stages,  $g_m$  is the transconductance of the active device, and  $Z_{o-in}$  and  $Z_{o-out}$  are the image impedances of the input and output transmission lines, respectively.

$$Z_{o-in} = \sqrt{\frac{L_B}{C_\pi} \left( 1 - \frac{\omega^2 L_B C_\pi}{4} \right)} \tag{2}$$

$$Z_{o-out} = \sqrt{\frac{L_C}{C_{ce}} \left( 1 - \frac{\omega^2 L_C C_{ce}}{4} \right)}$$

(3)

with  $L_B = R_{TERM}^2 C_\pi$  and  $L_C = R_{TERM}^2 C_{ce}$ .

For a  $50\,\Omega$  SSDA (i.e. N=1),  $G_{DA}$  is limited by  $g_m$ , which is quite low for high  $f_T$  devices. The issue of limited gain has been addressed through multiplicative DA topologies - formed from cascading or arranging SSDAs in a matrix [9], [10], [16], [19], [24], [28]–[30].

2) Noise performance limitation of SSDAs: While the SSDA topology presents notable advantages in wideband performance and design simplicity, with higher gain available from its multiplicative derivatives, it has a poorer signal-to-noise behaviour compared to multi-stage DAs. A notable merit of multi-stage DAs is that with each additional stage, the overall noise figure reduces in the amplifier passband, improving SNR at the output - a merit that the SSDA and its derivative amplifiers do not share [31]–[34]. However, the inherent flexibilities of the DA topology provide options for

noise performance optimisation based on available trade-offs. This may be observed by considering the noise factor (F) of a HBT-based SSDA which is derived as [30]

$$F = 2 + \frac{4}{g_m^2 Z_{\pi b} Z_{\pi c}} + Z_{\pi c} \left[ \left( \frac{i_b g_m^2 Z_{\pi b}}{4} \right)^2 + \left( \frac{i_d}{2} \right)^2 \right], (4)$$

where  $Z_{\pi b}$  and  $Z_{\pi c}$  are the  $\pi$ -image impedances of the input and output transmission lines of the HBT SSDA; and  $i_b$  and  $i_c$  are the base and collector noise generators of the HBT, given respectively by [35], [36],

$$\overline{i_b^2} = 4kT_oBRe(Y_{ebp} - Y_{ce}) + 2kT_oBg_{be}$$

(5)

and

$$\overline{i_c^2} = 2kT_oBg_m \tag{6}$$

where  $Y_{ebp}=gm\sqrt{2j\omega\tau_D}/\tanh\sqrt{2j\omega\tau_D}$  is the hole admittance of the emitter junction;  $Y_{ce}=gm\sqrt{2j\omega\tau_D}/\sinh\sqrt{2j\omega\tau_D}$  is the transfer admittance of the transistor;  $\tau_D$  is the diffusion time through the base region; and  $g_{be}$  is the total input conductance [35], [36]. It may be seen from (4), that F can be reduced by making  $Z_{\pi b}$ , larger. This would also increase the gain of the amplifier but the bandwidth would be reduced commensurately [30], [34]. A similar observation can be made for the FET-based SSDA, where F is derived as [32]

$$F = 2 + \frac{4}{g_m^2 Z_{\pi d} Z_{\pi g}} + \frac{Z_{\pi g} \omega^2 C_{gs}^2 R}{g_m} + \frac{4P}{g_m Z_{\pi g}}, \quad (7)$$

with  $C_{gs}$  being the input (gate-source) capacitance of the active device; R and P are dimensionless coefficients from Van der Ziel's FET noise behaviour model that depend on bias conditions, device geometry and other technological parameters [37]; and  $Z_{\pi d}$  and  $Z_{\pi g}$  being the  $\pi$ -image impedances of the input and output transmission lines of the SSDA. It is also observed that the overall noise factor can be reduced by making  $Z_{\pi g}$ , larger [32].

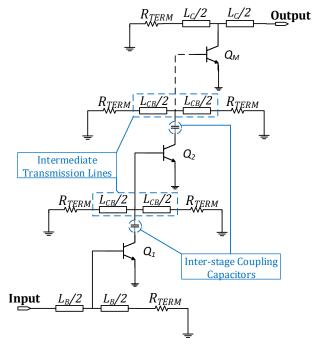

## B. The M-SSDA

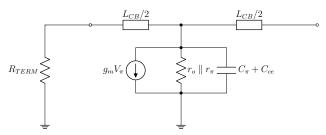

The M-SSDA is essentially two or more single stage distributed amplifiers (SSDA) connected by intermediate transmission lines, forming a  $M \times I$  matrix structure. The schematic of an M-SSDA with M common-emitter gain tiers is shown in Fig. 3. The input and output transmission lines of the M-SSDA are the same as in the SSDA, shown in Fig. 2a and Fig. 2b, respectively. The simplified equivalent circuit of the intermediate transmission line is shown in Fig. 4, where  $L_{CB}$  is the inductance required to achieve distributed effect for the combined capacitance at the intermediate nodes of the matrix amplifier, with image impedance  $Z_{o-int}$  given by [19]

$$Z_{o-int} = \sqrt{\frac{L_{CB}}{C_{\pi} + C_{ce}} \left( 1 - \frac{\omega^2 L_{CB} (C_{\pi} + C_{ce})}{4} \right)}$$

(8)

with  $L_{CB} = R_{TERM}^2(C_{\pi} + C_{ce})$  [7], [38].

Fig. 3: Schematic diagram of a M-SSDA, with M gain tiers, forming an  $M\times 1$  matrix structure.  $L_{CB}$  is the inductance of the intermediate transmission line.

Fig. 4: Simplified equivalent circuits of the intermediate ATLs of the HBT M-SSDA.

The gain of the M-SSDA,  $G_M$ , given by [19]

$$G_M = \frac{1}{4} g_m^2 Z_{o-int}^{2(M-1)} Z_{o-in} Z_{o-out},$$

(9)

The line impedances of the input  $(Z_{in})$ , intermediate  $(Z_{int})$  and output  $(Z_{out})$  transmission lines, are given by (10), (11) and (12), respectively, for the simplified CE M-SSDA:

$$Z_{in} = \frac{j\omega L_B}{2} + \frac{r_{\pi} \left(j\omega \frac{L_B}{2} + R_o\right)}{r_{\pi} + \left(R_o + j\omega \frac{L_B}{2}\right)\left(1 + j\omega r_{\pi}C_{\pi}\right)}$$

(10)

$$Z_{int} = \frac{j\omega L_{CB}}{2} + \frac{r_{\pi} \parallel r_o \left(j\omega \frac{L_{CB}}{2} + R_o\right)}{r_{\pi} \parallel r_o + \left(R_o + j\omega \frac{L_{CB}}{2}\right) \left(1 + j\omega \left(C_{\pi} + C_{ce}\right) r_{\pi} \parallel r_o\right)}$$

$$\tag{11}$$

$$Z_{out} = \frac{j\omega L_C}{2} + \frac{r_o \left(j\omega \frac{L_C}{2} + R_o\right)}{r_o + \left(R_o + j\omega \frac{L_C}{2}\right)\left(1 + j\omega r_o C_{ce}\right)}$$

(12)

The bandwidth of the M-SSDA is dominated by the cut-off frequency of the intermediate transmission line  $f_{c(int)}$ ,

$$f_{c(int)} = \frac{1}{\pi \sqrt{L_{CB} (C_{\pi} + C_{ce})}}$$

(13)

Both the C-SSDA and M-SSDA topologies make it possible to achieve significantly higher gain than is available from the conventional multi-stage DA, for the same number of active devices, while preserving the bandwidth advantage. The merit of the SSDA and its derivative multiplicative DA is highlighted by the fact that some of the DAs with the highest bandwidth and gain-bandwidth product (GBP) of any process technology and topology are based on the SSDA [9], [29], [39].

While the M-SSDA is a functional equivalent of the C-SSDA, in that they both share the same gain mechanism [19], there is a structural distinction. The C-SSDA consists of a number of unique SSDAs with the output of one connected to the input of the other (as shown in Fig. 5) [9], [16], [17]; while the M-SSDA is conventionally a multi-tier single structure, due to the presence of intermediate lines connecting the output of one tier to the input of the next tier [19]. In the design of cascaded DAs, it is essential that the individual amplifiers are designed to give a gain response as flat as possible up to the desired maximum frequency [40]. With matrix amplifiers, the fact that the output transmission line of a lower stage would form the input line of the stage above it, means that the stages cannot be individually optimised and then combined. Hence, these intermediate transmission lines must be designed to distribute the resultant capacitance of both stages that it connects.

The matrix topology, however, offers some advantages when compared to the cascaded topology, such as potentially higher gain, because both the forward and reverse waves on the intermediate transmission lines are amplified by the gain stage in the tier above them, whereas the reverse wave is absorbed by the drain line termination in the cascaded DA [10], [41], [42]; an inherent reverse isolation over wide bandwidths at reduced size [42]; better input and output matching with lower noise figure [33], [43]; reduced MMIC circuit footprint and, consequently, lower production cost [43]; and a potential for significantly less phase delay, when compared to the conventional distributed amplifier - an important feature for applications requiring good phase tracking [43].

In addition to the gain merit of multiplicative DAs, the topology also provides some noise optimisation potentials. The noise performance of the multiplicative DA is also limited by constraints similar to the SSDA, and overall noise marginally increases with additional stages, as opposed to multi-stage DAs. However, the multi-tier structure of multiplicative DAs present trade-offs that may be explored towards achieving gain/bandwidth/noise performance goals. For instance, in [34], it was established that multiplicative DAs follow the noise scaling mechanism of cascaded systems, such that the overall noise factor of the amplifier is primarily determined by the noise factor of the first gain stage. Hence, a viable design approach is to make the noise factor of the first stage of the

Fig. 5: Schematic diagram of a C-SSDA, with M gain tiers.

multiplicative DA as low as possible, at appreciable single stage gain. This may be achieved by designing the input transmission line at a higher image impedance and by adopting a transistor with a wider bandwidth potential i.e lower input capacitance (and correspondingly lower  $g_m$ ) in the first stage. With this approach, the loss in bandwidth from using a higher image impedance input line is offset by the inherent wider bandwidth of the transistor, while from (9), the gain is kept at an appreciable level by increasing  $Z_{o-in}$ .

### III. MMIC AMPLIFIER DESIGN AND MEASUREMENT

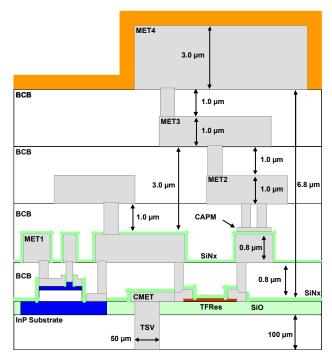

We report the design and measurment of two amplifiers: an SSDA and an M-SSDA. Both amplifiers are based on an InP DHBT process with  $f_T/f_{max}$  of 350 GHz / 600 GHz [44], with a representative schematic shown in Fig. 6 [44].

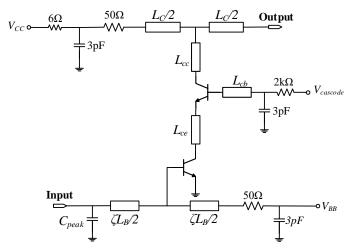

### A. SSDA with 7.1 dB Gain and 200 GHz Bandwidth

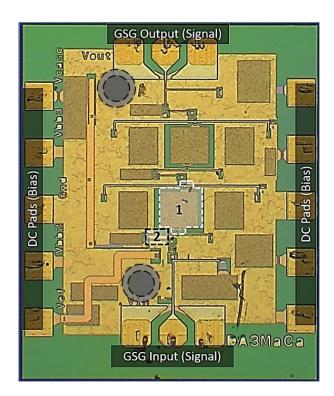

We report a SSDA which is suitable as a gain unit in a multiplicative DA topology. The amplifier features a cascode gain cell with two identical InP DHBTs, each with an emitter area of  $0.25\,\mu\mathrm{m}\times6\,\mu\mathrm{m}$ . The cascode configuration is favoured for the high input-output isolation it offers, as well as the high output impedance which advantageously reduces the loading on the output transmission line of the DA [29], [46]. To improve bandwidth performance, the input transmission line is scaled down by a factor  $\zeta \approx 0.5$  and peaked by a shunt capacitance  $C_{peak} = \frac{1}{2}C_{\pi}$ , where  $C_{\pi}$  is the input (baseemitter junction) capacitance of the active device [24], creating a similar effect to the application of a radial stub [47]. The loss compensation technique described in [24] was employed, involving the addition of peaking inductances  $L_{cc}$  and  $L_{ce}$  to the cascode gain cell, with  $L_{cb}$  added to maintain stability [24], [25]. Fig. 7a shows the SSDA schematic featuring the applied modifications. The fabricated MMIC occupies an area of 460 µm x 620 µm and is shown in Fig. 7b.

Fig. 6: IC interconnect cross-section showing low loss THz microstrip lines and high density thin-film interconnects [44], [45] and through-substrate vias (TSV).

The verification of the amplifiers performance was done via small-signal on-probe measurements. Due to the wide bandwidth of the amplifier, two different measurement setups were required to characterize it. The low frequency response of the amplifier was measured on probe in the band  $100\,\mathrm{MHz}$ - 120 GHz with the VectorStar ME7838A series broadband VNA by Anritsu via 75 µm 145 GHz Infinity probes. The input power was set to  $-20 \, \mathrm{dBm}$  to avoid saturating the amplifier. The high frequency response in the band between 140 GHz -220 GHz was measured with PNA-X N5247A by Keysight using VDI WR-5.1 frequency extenders and WR-5.1 waveguide probes. The input power was set and calibrated at  $-10\,\mathrm{dBm}$ to accommodate for the optimal operation of the frequency extenders. The limitations of the measurement equipment did not allow measurement in the 120 GHz - 140 GHz band. In both setups, the measurement reference plane was calibrated to the probe tips via certified calibration substrates. The SSDA was biased at  $I_B$  =0.63 mA,  $V_{CC}$  =5.2 V,  $V_{cascode}$  =3.5 V and  $I_C = 12.4 \,\mathrm{mA}$ .

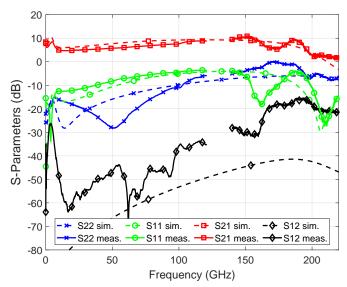

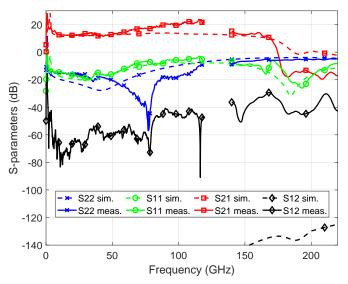

Fig. 8 shows the results of the two measurements along with the simulated performance of the amplifier. There is good agreement between the simulated and the measured forward gain S21 in terms of the bandwidth of  $200\,\mathrm{GHz}$  (the bandwidth is defined as the -3 dB point below the average gain across the amplifier passband [48]). However, with average measured gain at  $7.1\,\mathrm{dB}$ , there is an average shortfall in gain of  $\sim\!2.5\,\mathrm{dB}$  compared to the simulated response across the device bandwidth. The input and output reflection curves show good matching to the predicted results in the lower frequencies. There is also a high reverse isolation, S12, of less than  $-30\,\mathrm{dB}$  up to  $120\,\mathrm{GHz}$ , and less than  $-15\,\mathrm{dB}$  in throughout the

(a) Schematic circuit of SSDA with scaled input line, shunt capacitance and adapted loss compensation.

(b) Microphoto of SSDA. Footprint:  $460\,\mu m\ x\ 620\,\mu m$ . Dashed circles indicate location of through-substrate vias.

Fig. 7: SSDA: Circuit diagram and MMIC microphotograph

passband. In the higher frequency range, the measured results show some ripples on both input reflection (S11) and output reflection (S22) curves around  $150\,\mathrm{GHz}$  and  $200\,\mathrm{GHz}$  as seen in Fig. 8, that were not predicted in pre-fabrication simulations.

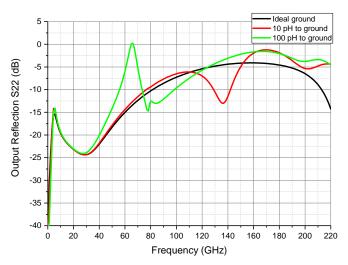

Post-measurement simulations were carried out to assess the effects of ground inductance, with results presented Fig. 9. It was observed that ground inductance (e.g from parasitics from DC bias probes) of  $\geq 10 \, \mathrm{pH}$  could result in S22 ripple between  $160 \, \mathrm{GHz}$  and  $190 \, \mathrm{GHz}$ , as reflected in the measured S22 (Fig. 8). Additionally, full EM simulations of the input and output GSG pads, substrate, ground plane slots, and through-substrate vias revealed that the substrate could sustain resonant modes at  $170 \, \mathrm{GHz}$  and  $190 \, \mathrm{GHz}$ , which also manifest as

Fig. 8: Comparison of simulated and measured responses for the SSDA: simulated response - dashed lines; measured response - solid lines.

Fig. 9: Effects of ground inductance on output reflection coefficient.

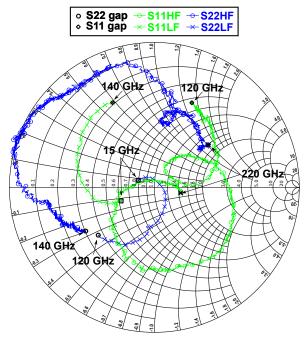

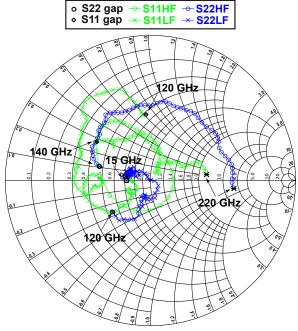

dips in the forward gain curve. The substrate resonant modes resulted from the low density of through-substrate vias on the MMIC. The effect of these resonances in addition to the DC bias probe parasitics account for the output reflection coefficient approaching 0 dB. The Smith chart plot of S11 and S22 are presented in Fig. 10, and also show potential instability within this frequency range. This effect is in accordance to what has been shown in in [49], however due to the use of through-substrate vias and back-plane metallization in the proposed amplifier, it was not possible to use resistive silicon substrate, as prescribed in [49]. In line with design using similar processes, it is expected that both effects would be mitigated by packaging the MMIC, as this would improve both the decoupling and the grounding of the amplifier. A tricode gain cell could also be employed in place of the cascode gain cell, to increase maximum stable gain [50].

A comparison of the amplifier with state-of-the-art DAs in

Fig. 10: Smith chart plot of S11 and S22 of the SSDA. The amplifier is potentially unstable in the upper frequency band, due to resonant modes at frequencies close to  $160\,\mathrm{GHz}$  and  $190\,\mathrm{GHz}$ . LF - Low frequency ( $100\,\mathrm{MHz}$  -  $120\,\mathrm{GHz}$ ); HF - High frequency ( $140\,\mathrm{GHz}$  -  $220\,\mathrm{GHz}$ ); "gap" is the frequency range from  $120\,\mathrm{GHz}$  to  $140\,\mathrm{GHz}$ , which is not covered in the measurement due to equipment limitations.

Table I. Particular focus is given to InP-based DAs; and SSDAs and multiplicative DAs to allow for like-for-like comparison. The bandwidth (BW), gain, GBP, DC power ( $P_{DC}$ ), GBP/ $P_{DC}$  (a figure-of -merit that provides a measure of the DC power efficiency of wideband amplifiers), area of the MMIC chip and DA topology are compared. The SSDA reported in this paper has the highest bandwidth to date of reported single stage designs and is only outperformed by the 2-cascaded-SSDA in [9].

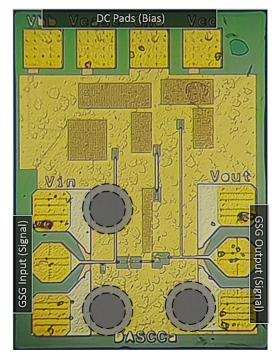

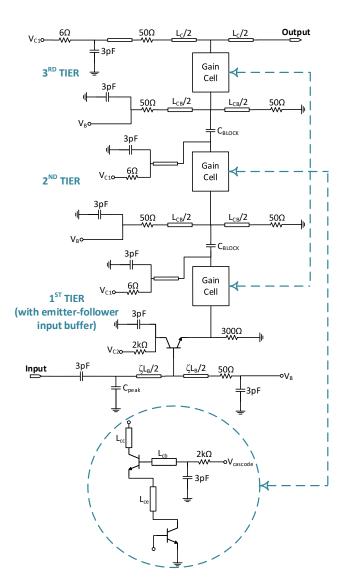

### B. $3 \times 1$ M-SSDA with 12 dB gain and 170 GHz bandwidth

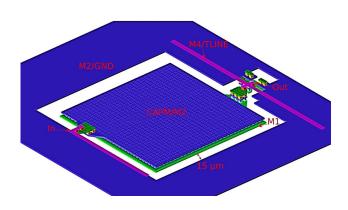

A three-tier M-SSDA has been designed and laid out as a MMIC. This amplifier is also based on the bandwidth optimisation technique adopted for the SSDA, and features an emitter follower (EF) input buffer [19]. A schematic of the 3-M-SSDA is presented in Fig. 11, with an inset showing the modified cascode gain cell. The design is also based on the same InP DHBT IC process used for the SSDA. Relatively large (~3 pF) inter-stage capacitors were used in the circuit to reduce the low-frequency cutoff and improve baseband operation.

Fig. 12 shows the microphotograph of the fabricated MMIC matrix-SSDA, with actual dimension of  $770\,\mu\mathrm{m}\times800\,\mu\mathrm{m}$ . The verification of the amplifier performance was also done via small-signal on-wafer probe measurements using two measurement setups -  $100\,\mathrm{MHz}$  -  $120\,\mathrm{GHz}$ ; and  $140\,\mathrm{GHz}$  -  $220\,\mathrm{GHz}$ , with the same vector network analyzer setups as described in Section III. The M-SSDA required eight voltage sources to bias its three stages: three base voltage sources

TABLE I: Comparison of SSDA with state-of-the-art DAs in literature.

| Technology         | BW<br>(GHz) | Gain<br>(dB)   | GBP<br>(GHz) | (mW) | GBP/P <sub>DC</sub><br>(GHz/mW) | Area (mm²) | DA Topology       | Ref.      |

|--------------------|-------------|----------------|--------------|------|---------------------------------|------------|-------------------|-----------|

| 250 nm InP DHBT    | 241         | $10 \pm 2^*$   | 762          | 387  | 2.00                            | 0.82       | 6-stage Cascode   | [8]       |

| 250 nm InP DHBT    | 207         | $13.5 \pm 2$   | 979          | 210  | 4.66                            | 0.29       | 4-stage Cascode** | [51]      |

| 500 nm InP DHBT    | 175         | $12\pm2^*$     | 697          | 180  | 3.87                            | 0.975      | 5-stage tricode   | [50]      |

| 250 nm InP DHBT    | 182         | $10 \pm 2^{*}$ | 575          | 110  | 5.23                            | 0.33       | 4-stage Cascode   | [52]      |

| 250 nm InP DHBT    | 192         | $7.5 \pm 1$    | 455          | 40   | 11.38                           | 0.24       | SSDA              | [9]       |

| 250 nm InP DHBT    | 235         | $16 \pm 2$     | 1480         | 117  | 12.65                           | 0.41       | 2-Cascaded-SSDA   | [9]       |

| 130 nm SiGe BiCMOS | 170         | $13 \pm 1^*$   | 759          | 74   | 10.26                           | 0.22       | 4-Cascaded-SSDA   | [53]      |

| 130 nm SiGe BiCMOS | 175         | $16 \pm 4$     | 1102         | 360  | 3.06                            | 0.38       | 2-Cascaded-SSDA   | [28]      |

| 250 nm InP DHBT    | 200         | 7.1 ± 3.5      | 455          | 67   | 6.79                            | 0.28       | SSDA              | This Work |

<sup>\*</sup> There were no comments on the gain ripple in these publications, so the gain ripple has been estimated from the s-parameter plot.

\*\* CC: Common collector.

$(V_{BB1},\ V_{BB2}\$ and  $V_{BB3});$  three collector voltage sources  $V_{CC1},\ V_{CC2}$  and  $V_{CC3};$  one voltage source to bias the three common-base transistors forming the cascode of each gain cell (denoted by  $V_{cascode}$ ); and one voltage source to bias the EF input buffer (denoted by  $V_{EF}$ ). This required two additional DC power supply units compared to the measurement setup, used in characterising the SSDA, and an additional  $150\,\mu\mathrm{m}$  pitch DC probe. For ease of tunability, two Keysight ES6312A triple output programmable DC power supply units were used to supply the base bias and cascode voltages, while the DC supply function of an Hewlett-Packard 4145B semiconductor parameter analyzer was used for collector and EF bias.

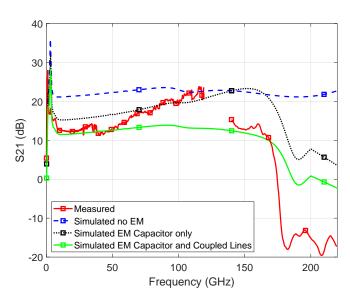

S-parameter measurements from the two measurement setups are presented as solid lines in Fig. 13, with the corresponding simulated curves presented as dashed lines. An average forward of gain of 12 dB and 170 GHz bandwidth was measured with good input and output matching of less than -5 dB all through the measured bandwidth. The amplifier also has high reverse isolation S12 of less than  $-40\,\mathrm{dB}$  up to  $120\,\mathrm{GHz}$ , and less than  $-30\,\mathrm{dB}$  throughout the amplifier passband. A good degree of agreement between the simulated and measured responses may be observed in the S21 (dB), S11 (dB) and S22 (dB) up to  $70\,\mathrm{GHz}$ . A peaking in the S21characterisation from 70 GHz to 120 GHz is attributed to the multiplicative effect of the peaking observed in the the same frequency range for the SSDA, as seen in Fig 8. However, for the higher frequency measurement, while the input and output reflection measurement closely matches prediction, the forward gain slightly deviates from the predicted profile, with a bandwidth-loss of  $\sim 5\%$ .

An electromagnetic (EM) simulation of the inter-stage coupling capacitors  $C_{BLOCK}$  and its peripherals presented in Fig. 14 (region enclosed with white dashed lines and labelled as 1, for tier 1 to tier 2 in Fig. 12) and EM coupling between transmission lines in the circuit revealed these as the main loss and bandwidth-limiting components. This observation is

consistent with what is shown in [54]. Additionally, the large slots in the ground plane required by the inter-stage coupling capacitor structures resulted in significant crosstalk through the substrate which accounts for the gain peaking towards 110 GHz [55]. The region enclosed in black dashed lines (labelled as 2) in Fig. 12 indicates the location of the peaking inductances  $L_{ce}$  and  $L_{cc}$ ; a region with relatively high EM coupling. These effects are shown in Fig. 15, which compares the simulated S21 gain without the EM simulation of the inter-stage capacitors with cases where either only the EM simulated capacitors are included or both the EM simulated capacitors and transmission line couplings are included. The Smith's chart plots of S11 and S22 are presented in Fig. 16, showing unconditional stability throughout the amplifier passband.

Table II presents a comparison of the new M-SSDA with the state-of-the-art matrix distributed amplifiers. The gain, BW, GBP,  $P_{DC}$ , GBP/ $P_{DC}$ , area of MMIC chip and the matrix configuration are compared. It is noted that the new M-SSDA has both the highest bandwidth and GBP of any matrix DA, albeit with a  $10\,\mathrm{dB}$  mid-band peaking, due to parasitic effects from the large inter-stage capacitors.

### IV. CONCLUSIONS

The peculiarities of the SSDA topology make it possible to operate new generation transistor processes close to their bandwidth limit and would be instrumental in making terahertz bandwidth amplification more practical. In this paper, we highlight the merits of the SSDA and its multiplicative derivatives in achieving ultra-wideband amplification, and we describe design approaches for gain, bandwidth and noise performance optimisation. We also present two new MMIC amplifiers: an SSDA and a three-tier M-SSDA. The SSDA amplifier has a measured gain of 7.1 dB and 200 GHz bandwidth and to the authors best knowledge, is the highest bandwidth reported for any SSDA. The three-tier M-SSDA measured a gain of 12 dB

TABLE II: Comparison of the performance of new M-SSDA with other wideband matrix DAs.

| Technology         | Gain<br>(dB)    | Bandwidth<br>(GHz) | GBP<br>(GHz) | (mW) | GBP/P <sub>DC</sub><br>(GHz/mW) | Area (mm²) | Matrix<br>Configuration | Ref.      |

|--------------------|-----------------|--------------------|--------------|------|---------------------------------|------------|-------------------------|-----------|

| 0.18 μm CMOS       | $9.5 \pm 1$     | 50                 | 149          | 420  | 0.35                            | 1.54       | 2 × 4                   | [56]      |

| 0.18 μm CMOS       | $6.7 \pm 3.5^*$ | 45.6               | 99           | 497  | 0.20                            | 1.89       | 2 × 4                   | [57]      |

| 0.25 μm GaAs PHEMT | $19 \pm 1$      | 19.5               | 174          | 270  | 0.644                           | 7          | 2 × 4                   | [58]      |

| 0.25 μm GaAs PHEMT | $18 \pm 2$      | 19.5               | 195          | 500  | 0.39                            | 7          | 2 × 4                   | [58]      |

| 0.09 μm CMOS       | $15.4 \pm 1$    | 21                 | 124          | 12.5 | 9.92                            | 0.41       | 2 × 4                   | [59]      |

| 0.25 μm InP HBT    | 12 ± 10         | 170                | 677          | 183  | 3.70                            | 0.62       | 3 × 1                   | This Work |

<sup>\*</sup>There were no comments on the gain ripple in this publication, so the gain ripple has been estimated from the s-parameter plot.

Fig. 11: Three-tier M-SSDA schematic with scaled input and intermediate transmission lines. Inset shows the modified gain cell. Modified from [19].

and  $170\,\mathrm{GHz}$  bandwidth, which is the highest bandwidth and gain-bandwidth for any matrix amplifier reported in the literature. The M-SSDA results also underscore the critical

compromise between achieving low and high frequency performance that arises from the size and the associated parasitic effects of the inter-stage coupling capacitances required in multiplicative DAs.

Fig. 12: Microphoto of the M-SSDA. Footprint:  $770\,\mu\mathrm{m} \times 800\,\mu\mathrm{m}$ . Region 1 (enclosed by white dashed lines) marks the location of the inter-stage capacitor  $C_{BLOCK}$  between tier 1 and tier 2, and the associated vias and metal connections; region 2 (enclosed by black dashed lines) marks the location of peaking inductances  $L_{ce}$  and  $L_{cc}$ . Dashed circles indicate location of through-substrate vias.

Fig. 13: Comparison of simulated and measured responses for the three-tier M-SSDA: simulated response - dashed lines; measured response - solid lines.

Fig. 15: Bandwidth-limiting effect of inter-stage coupling capacitors.

Fig. 14: Structure and interconnects of the inter-stage ac-coupling capacitors together with the input and output matching transmission lines, used in the E/M simulations.

Fig. 16: Smith chart plot of S11 and S22 of the M-SSDA. The amplifier is unconditionally stable. LF - Low frequency (100 MHz -120 GHz); HF - High frequency (140 GHz - 220 GHz); "gap" is the frequency range from 120 GHz to 140 GHz, which is not covered in the measurement due to equipment limitations.

### ACKNOWLEDGEMENT

The authors would like to acknowledge Teledyne Scientific for providing access to the InP process and for fabrication of the circuits. The support of the Petroleum Technology Development Fund (PTDF) of Nigeria through the sponsorship of T. Odedeyi's PhD program is also acknowledged.

### REFERENCES

- [1] T. Odedeyi, S. Giannakopoulos, H. Zirath, and I. Darwazeh, "Single-stage and multiplicative distributed amplifiers for 200 GHz+ amplification," in 2019 IEEE Asia Pacific Microwave Conference (APMC). IEEE, December 2020.

- S. Kang, D. Kim, M. Urteaga, and M. Seo, "State-of-the-art THz integrated circuits in InP HBT technologies," in *Radio-Frequency Integration Technology (RFIT)*, 2017 IEEE International Symposium on.

- IEEE, 2017, pp. 25–27.

M. Urteaga, Z. Griffith, R. Pierson, P. Rowell, A. Young, J. Hacker, B. Brar, S. Kim, R. Maurer, and M. Rodwell, "THz InP bipolar transistors-circuit integration and applications," in *Compound Semiconductor Integrated Circuit Symposium (CSICS)*, 2017 IEEE. IEEE, 2017, pp. 1–4.

- [4] M. Urteaga, Z. Griffith, M. Seo, J. Hacker, and M. J. Rodwell, "InP HBT technologies for THz integrated circuits," *Proceedings of the IEEE*, vol. 105, no. 6, pp. 1051–1067, 2017.

[5] W. Percival, "Thermionic valve circuits," *British patent*, vol. 460562,

- W. Percival, p. 25, 1937.

- [6] E. L. Ginzton, W. R. Hewlett, J. H. Jasberg, and J. D. Noe, "Distributed amplification," *Proceedings of the IRE*, vol. 36, no. 8, pp. 956–969,

- T. T. Wong, Fundamentals of distributed amplification. Artech House,

- [8] T. Jyo, M. Nagatani, M. Ida, M. Mutoh, H. Wakita, N. Terao, and H. Nosaka, "A 241-GHz-bandwidth distributed amplifier with 10-dBm P1dB in 0.25-μm InP DHBT technology," in 2019 IEEE MTT-S International Microwave Symposium (IMS), June 2019, pp. 1430–1433.

[9] K. Eriksson, I. Darwazeh, and H. Zirath, "InP DHBT distributed ampli-

- fiers with up to 235-GHz bandwidth," *IEEE Transactions on Microwave Theory and Techniques*, vol. 63, no. 4, pp. 1334–1341, 2015.

- G. Nikandish, R. B. Staszewski, and A. Zhu, "The (r)evolution of distributed amplifiers: From vacuum tubes to modern CMOS and GaN ICs," *IEEE Microwave Magazine*, vol. 19, no. 4, pp. 66–83, 2018.

- [11] C. Poole and I. Darwazeh, Microwave Active Circuit Analysis and Design. Academic Press, 2015.

[12] P. Monteiro, A. Borjak, F. da Rocha, J. O'Reilly, and I. Darwazeh, "10-gb/s pulse-shaping distributed-based transversal filter front-end for optical soliton receivers," IEEE Microwave and Guided Wave Letters, 2019, 2011, pp. 446–4500. vol. 8, no. 1, pp. 4-6, 1998.

- [13] I. Darwazeh, P. Moreira, A. Borjak, and J. O'Reilly, "A distributed optical receiver preamplifier with unequal gate/drain impedances," in *IEEE 1995 Microwave and Millimeter-Wave. Monolithic Circuits Symposium.* Digest of Papers, 1995, pp. 199-202.

- A. Borjak, P. P. Monteiro, J. O'Reilly, and I. Darwazeh, "High-speed generalized distributed-amplifier-based transversal-filter topology for optical communication systems," *IEEE Transactions on Microwave Theory*

- tical communication systems," *IEEE Transactions on Microwave Theory and Techniques*, vol. 45, no. 8, pp. 1453–1457, 1997.

[15] G. Nwaogu and C. Aitchison, "A very broadband microwave distributed amplifier using FETs," in *1981 11th European Microwave Conference*, 1981, pp. 609–613.

[16] J. Y. Liang and C. S. Aitchison, "Gain performance of cascade of single stage distributed amplifiers [microwave circuits]," *Electronics Letters*, vol. 31, no. 15, pp. 1260–1261, Jul 1995.

[17] B. Banyamin and M. Berwick, "The gain advantages of four cascaded single stage distributed amplifier configurations," in *2000 IEEE MTT-S International Microwave Symposium Digest (Cat. No. 00CH37017)*, vol. 3. IEEE, 2000, pp. 1325–1328.

- S International Microwave Symposium Digest (Cat. No. 00CH37017), vol. 3. IEEE, 2000, pp. 1325–1328.

[18] J. Y. Liang and C. S. Aitchison, "A proposal of a broadband high gain block using cascaded single-stage distributed amplifiers," in High Performance Electron Devices for Microwave and Optoelectronic Applications, 1995. EDMO., IEEE 1995 Workshop on. IEEE, 1995, pp. 173–178.

[19] T. Odedeyi and I. Darwazeh, "Matrix single stage distributed amplifier design for ultra wideband application," in 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Batumi, Georgia, 2017. IEEE, 2017.

[20] A. Iqbal and I. Z. Darwazeh, "Modelling of the heterojunction bipolar transistor based distributed amplifier," in IEE Colloquium Wideband Circuits Modelling and Techniques, 1996, pp. 511–518.

- transistor based distributed amplifier," in *IEE Colloquium Wideband Circuits, Modelling and Techniques,* 1996, pp. 5/1–5/8.

[21] A. Iqbal and I. Darwazeh, "A 23 GHz baseband HBT distributed amplifier for optical communication systems," in *Microwave Conference, 1998. 28th European,* vol. 1. IEEE, 1998, pp. 6–11.

[22] L. Moura and I. Darwazeh, *Introduction to linear circuit analysis and modelling: from DC to RF.* Elsevier, 2005.

[23] K. W. Kobayashi, R. Esfandiari, and A. K. Oki, "A novel HBT distributed amplifier design topology based on attenuation compensation techniques," *IEEE Transactions on Microwave Theory and Techniques*

- distributed amplifier design topology obsect on attenuation compensation techniques," *IEEE Transactions on Microwave Theory and Techniques*, vol. 42, no. 12, pp. 2583–2589, 1994.

T. Odedeyi and I. Darwazeh, "Bandwidth enhancement technique for bipolar single stage distributed amplifier design," in *2017 IEEE Asia Pacific Microwave Conference (APMC)*. IEEE, Nov 2017, pp. 833–

- S. Kimura, Y. Imai, Y. Umeda, and T. Enoki, "Loss-compensated distributed baseband amplifier IC's for optical transmission systems," *IEEE Transactions on Microwave Theory and Techniques*, vol. 44, no. 10, pp. 1688–1693, Oct 1996.

A. Worapishet, I. Roopkom, and W. Surakampontorn, "Theory and bandwidth aphaneament of caceded double store distributed amplifiers."

- width enhancement of cascaded double-stage distributed amplifiers," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57,

- P. V. Testa, C. Carta, U. Jörges, and F. Ellinger, "IEEE Journal of Solid-State Circuits, vol. 50, no. 10, pp. 2228–2238, 2015.

P. V. Testa, C. Carta, U. Jörges, and F. Ellinger, "Analysis and design of 20 to 220 CUshalarous design of 20 to 220 CUshalar

- a 30-to 220-GHz balanced cascaded single-stage distributed amplifier in 130-nm SiGe BiCMOS," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 5, pp. 1457–1467, 2018.

- no. 5, pp. 1457–1467, 2018.

K. Eriksson, I. Darwazeh, and H. Zirath, "InP DHBT wideband amplifiers with up to 235 GHz bandwidth," in 2014 IEEE MTT-S International Microwave Symposium (IMS2014). IEEE, 2014, pp. 1–4.

T. O. Odedeyi, "Distributed circuit analysis and design for ultrawideband communication and sub-mm wave applications," Ph.D. dissertation, UCL (University College London), 2020.

K. Niclas and B. Tucker, "On noise in distributed amplifiers at microwave frequencies," IEEE Transactions on Microwave Theory and Techniques, vol. 31, no. 8, pp. 661–668, 1983.

C. S. Aitchison, "The intrinsic noise figure of the MESFET distributed amplifier," IEEE Transactions on Microwave Theory and Techniques, vol. 33, no. 6, pp. 460–466, 1985.

K. B. Niclas and A. P. Chang, "Noise in two-tier matrix amplifiers," IEEE Transactions on Microwave Theory and Techniques, vol. 36, no. 1, pp. 11–20, 1988.

- pp. 11–20, 1988.

T. Odedeyi, C. Poole, and I. Darwazeh, "Noise analysis of multiplication of the control of th Tive distributed amplifiers," in 2019 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2019, pp. 1–5.

- A. Van der Ziel and G. Bosman, "Accurate expression for the noise temperature of common emitter microwave transistors," *IEEE Transactions on Electron Devices*, vol. 31, no. 9, pp. 1280–1283, 1984.

- [36] A. Der Ziel, "Theory of shot noise in junction diodes and junction transistors," *Proceedings of the IRE*, vol. 43, no. 11, pp. 1639–1646, 1955

- A. Van der Ziel, "Noise. sources, characterization, measurement," Prentice-Hall Information and System Sciences Series, Englewood Cliffs: Prentice-Hall, 1970, 1970.

- Citys: Prentice-Hall, 1970, 1970.

A. Iqbal and I. Darwazeh, "Analytical modelling of the heterojunction bipolar transistor based distributed amplifier," in *High Frequency Post-graduate Student Colloquium*, 1996., 2nd. IEEE, 1996, pp. 11–16.

K. W. Kobayashi and Y. McCleary, "140GHz SiGe HBT and 100GHz InP DHBT broadband triple-stacked distributed amplifiers with active bias terminations," in 2019 IEEE BiCMOS and Compound semiconductary Internation (Citys). tor Integrated Circuits and Technology Symposium (BCICTS). IEEE,

- 2019, pp. 1–4.

[40] J. B. Beyer, S. Prasad, R. C. Becker, J. E. Nordman, and G. K. Hohenwarter, "MESFET distributed amplifier design guidelines," *IEEE Transactions on Microwave Theory and Techniques*, vol. 32, no. 3, pp. 2022, 275–1824. 268–275, 1984.

- 268–275, 1984.

[41] K. B. Niclas and R. R. Pereira, "The matrix amplifier: a high-gain module for multioctave frequency bands," *IEEE Transactions on Microwave Theory and Techniques*, vol. 35, no. 3, pp. 296–306, 1987.

[42] N. Kumar and A. Grebennikov, *Distributed Power Amplifiers for RF and Microwave Communications*. Artech House, 2015.

[43] S. D'agostino, G. D'inzeo, P. Marietti, and G. Panariello, "A method for computing the noise figure in matrix distributed amplifier," in *Microwave Symposium Digest*, 1990., *IEEE MTT-S International*. IEEE, 1990, pp. 351–354

- [44] J. Hacker, M. Seo, A. Young, Z. Griffith, M. Urteaga, T. Reed, and M. Rodwell, "THz MMICs based on InP HBT technology," in Microwave Symposium Digest (MTT), 2010 IEEE MTT-S International. IEEE, 2010, pp. 1126–1129. T.S.C., Tsc250 v1.0 Design Manual. "Teledyne Scientific Company",

- K. Kobayashi, D. Umemoto, T. Block, A. Oki, and D. Streit, "A wideband HEMT cascode low-noise amplifier with HBT bias regulation," *IEEE Microwave and Guided Wave Letters*, vol. 5, no. 12, pp. 457–459,

- [47] T. Shivan, E. Kaule, M. Hossain, R. Doerner, T. Johansen, D. Stoppel, S. Boppel, W. Heinrich, V. Krozer, and M. Rudolph, "Design and modeling of an ultra-wideband low-noise distributed amplifier in InP DHBT technology," *International Journal of Microwave and Wireless Technologies*, vol. 11, no. 7, pp. 635–644, 2019.

[48] D. Pi, B.-K. Chun, and P. Heydari, "A synthesis-based bandwidth enhancement technique for CMOS amplifiers: Theory and design," *IEEE Lower of Society Communication*, 2021, 402, 2011.

- Journal of Solid-State Circuits, vol. 46, no. 2, pp. 392-402, 2010.

- [49] K. Eriksson, S. E. Gunnarsson, P.-Å. Nilsson, and H. Zirath, "Suppression of Parasitic Substrate Modes in Multilayer Integrated Circuits,"

- pp. 591–594, 2015.

T. Shivan, M. Hossain, R. Doerner, T. K. Johansen, H. Yacoub, S. Boppel, W. Heinrich, and V. Krozer, "Performance analysis of a lownoise, highly linear distributed amplifier in 500-nm InP/InGaAs DHBT technology," *IEEE Transactions on Microwave Theory and Techniques*, vol. 67, pp. 12, pp. 5130–5147, 2019.

- vol. 67, no. 12, pp. 5139–5147, 2019.

[51] S. Giannakopoulos, K. Eriksson, I. Darwazeh, Z. S. He, and H. Zirath, "Ultra-broadband common collector-cascode 4-cell distributed amplifier in 250nm InP HBT technology with over 200 GHz bandwidth," in Mi-

- in 250nm InP HBT technology with over 200 GHz bandwidth," in Microwave Integrated Circuits Conference (EuMIC), 2017 12th European. IEEE, 2017, pp. 142–145.

[52] S. Yoon, I. Lee, M. Urteaga, M. Kim, and S. Jeon, "A fully-integrated 40–222 GHz InP HBT distributed amplifier," IEEE Microwave and Wireless Components Letters, vol. 24, no. 7, pp. 460–462, 2014.

[53] P. V. Testa, R. Paulo, C. Carta, and F. Ellinger, "250 GHz SiGe-BiCMOS cascaded single-stage distributed amplifier," in Compound Semiconductor Integrated Circuit Symposium (CSICS), 2015 IEEE. IEEE, 2015, pp. 1–4

- tor Integrated Circuit Symposium (CSICS), 2015 IEEE. IEEE, 2015, pp. 1–4.

[54] K. Eriksson, V. Vassilev, and H. Zirath, "H-band MMIC amplifiers in 250 nm InP DHBT," in 2012 19th International Conference on Microwaves, Radar & Wireless Communications, vol. 2. IEEE, 2012, pp. 744–747.

[55] K. Eriksson, InP DHBT Amplifiers and Circuit Packaging up to Submillimeter-Wave Frequencies. Citeseer, 2015.

[56] J.-C. Chien, T.-Y. Chen, and L.-H. Lu, "A 9.5-dB 50-GHz matrix distributed amplifier in 0.18-\(\mu\)m CMOS," in VLSI Circuits, 2006. Digest of Technical Papers. 2006 Symposium on. IEEE, 2006, pp. 146–147.

[57] T.-Y. Chen, J.-C. Chien, and L.-H. Lu, "A 45.6-GHz matrix distributed amplifier in 0.18-\(\mu\)m CMOS," in Custom Integrated Circuits Conference, 2005. Proceedings of the IEEE 2005. IEEE, 2005, pp. 119–122.

[58] A. Lamesa, G. Giolo, and E. Limiti, "Design procedure and performance

- ence, 2005. Proceedings of the IEEE 2005. IEEE, 2005, pp. 119–122.

[58] A. Lamesa, G. Giolo, and E. Limiti, "Design procedure and performance of two 0.5-20 GHz GaAs PHEMT MMIC matrix distributed amplifier for EW applications," in Microwave Conference, 2004. 34th European, vol. 1. IEEE, 2004, pp. 9–12.

[59] B. Machiels, P. Reynaert, and M. Steyaert, "Power efficient distributed low-noise amplifier in 90 nm CMOS," in 2010 IEEE Radio Frequency Integrated Circuits Symposium. IEEE, 2010, pp. 131–134.