**GALLIUM ARSENIDE QUANTUM WELL

MODULATORS GROWN ON SILICON SUBSTRATES**

*A thesis by*

**Paul Brooke Barnes**

*submitted to the University of London for the degree of PhD.*

Department of Electronic and Electrical Engineering

University College London

September 1993

ProQuest Number: 10105639

All rights reserved

INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10105639

Published by ProQuest LLC(2016). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code.

Microform Edition © ProQuest LLC.

ProQuest LLC

789 East Eisenhower Parkway

P.O. Box 1346

Ann Arbor, MI 48106-1346

## ABSTRACT

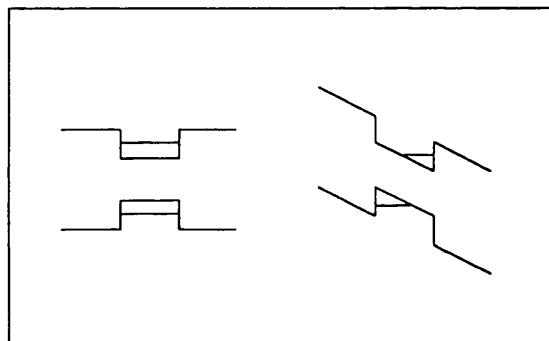

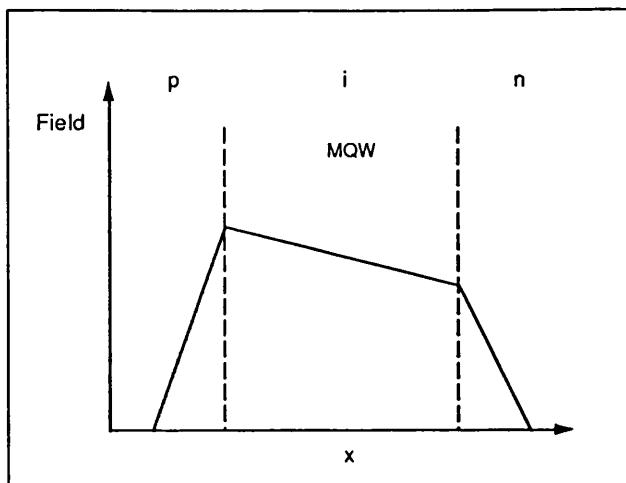

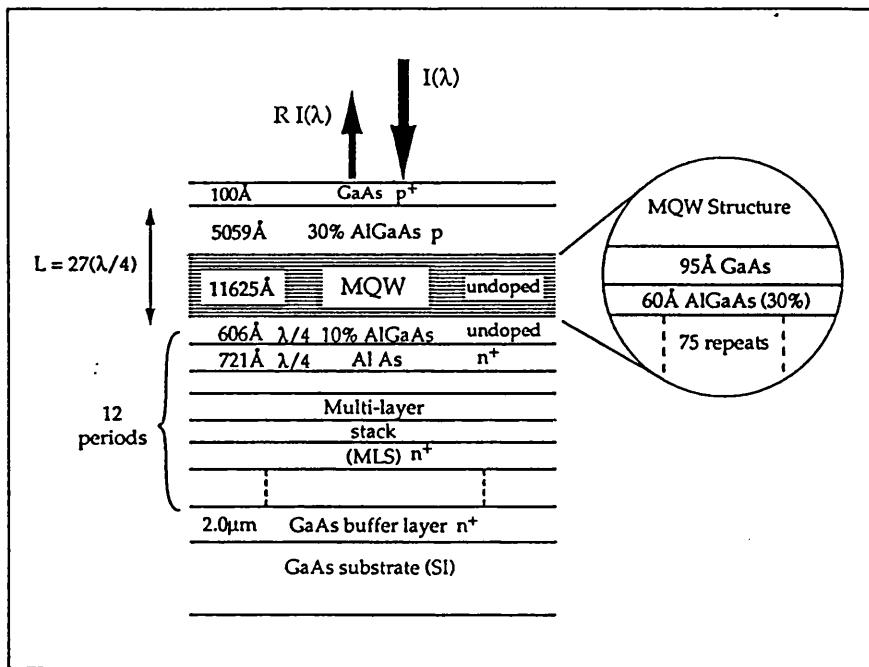

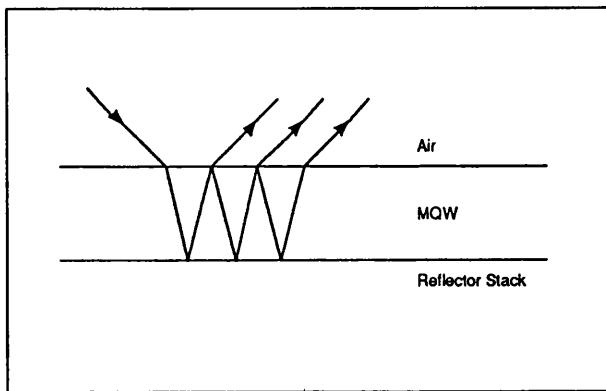

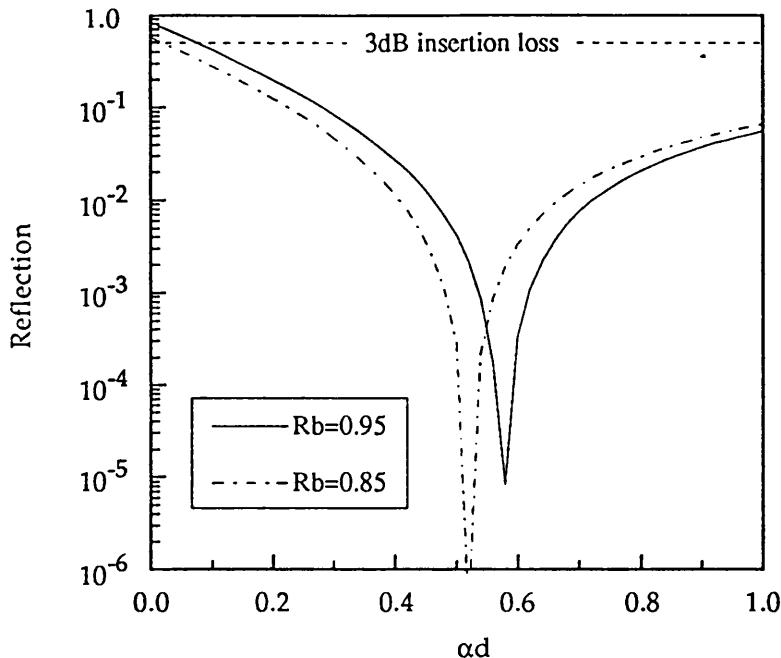

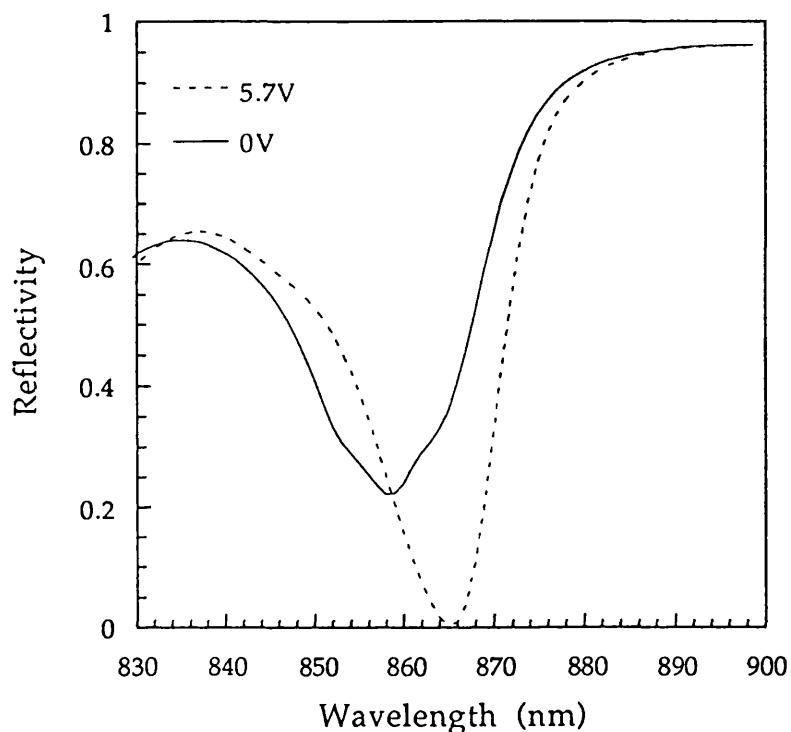

This thesis describes an investigation into GaAs/GaAlAs multiple quantum well (MQW) modulators grown on silicon substrates. The basic device consists of a *pin* diode containing quantum wells within the intrinsic region. Application of a reverse bias voltage to the device causes a change in the absorption of the MQWs. This change may be used to modulate a beam of light incident upon the modulator. By enclosing the device within a Fabry-Perot cavity, resonance effects can be used to enhance the degree of modulation. Such a device is known as an asymmetric Fabry-Perot modulator (AFPM).

The motivations for the integration of GaAs and Si are derived from an appreciation of the merits of the two different materials. For purely electronic systems there may be advantages, but most exciting are the possibilities for new systems using optics to enhance the capabilities of electronics. Chapter 1 introduces these issues and presents a discussion on possible future optoelectronic systems. Given that a high enough level of integration can be achieved, the AFPM is shown to be a promising device for use in such systems. The properties of MQW devices epitaxially grown on silicon have therefore been investigated.

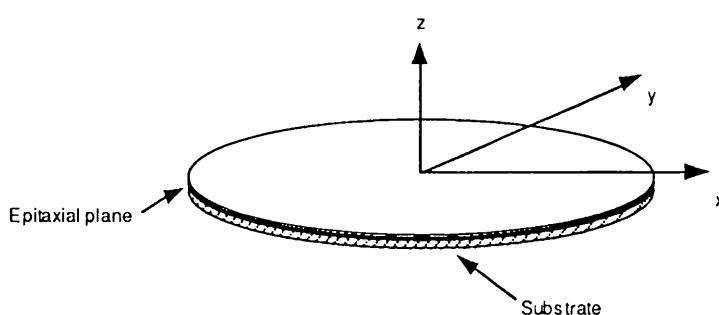

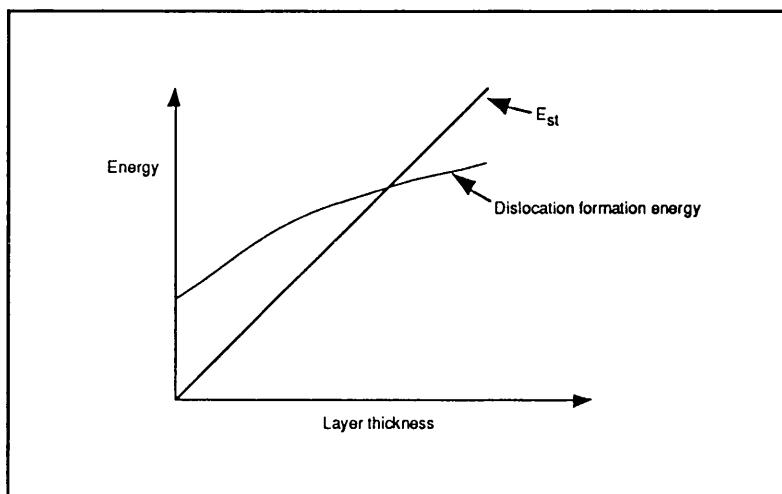

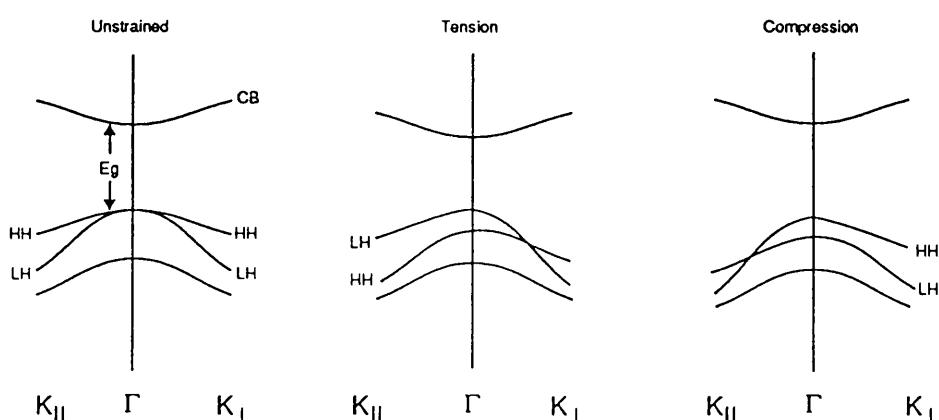

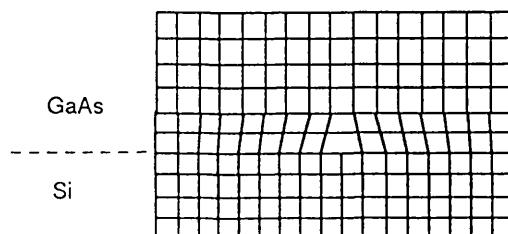

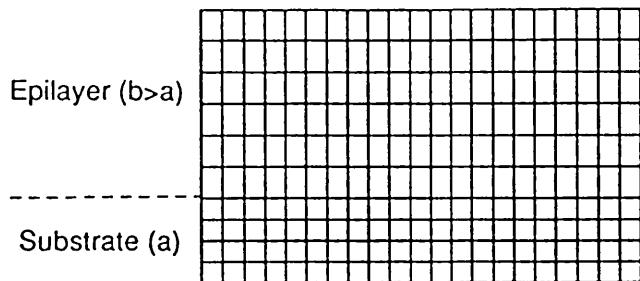

A problem of GaAs on Si growth is the material mismatch, which results in a degree of strain in the epitaxial layer. The effect of this on MQW devices is discussed in Chapter 2. The material mismatch also creates a number of difficulties in the growth process and has an impact on material quality. These issues are discussed in Chapter 3, together with an outline of methods by which material quality could be improved. A study of the material quality of devices grown by both MOCVD and MBE is presented. Substrates used included plain, patterned, and GaAs pre-coated silicon. Material analysis was performed by electron microscopy, optical microscopy, photoluminescence, and optical beam induced current (OBIC) scanning optical microscopy.

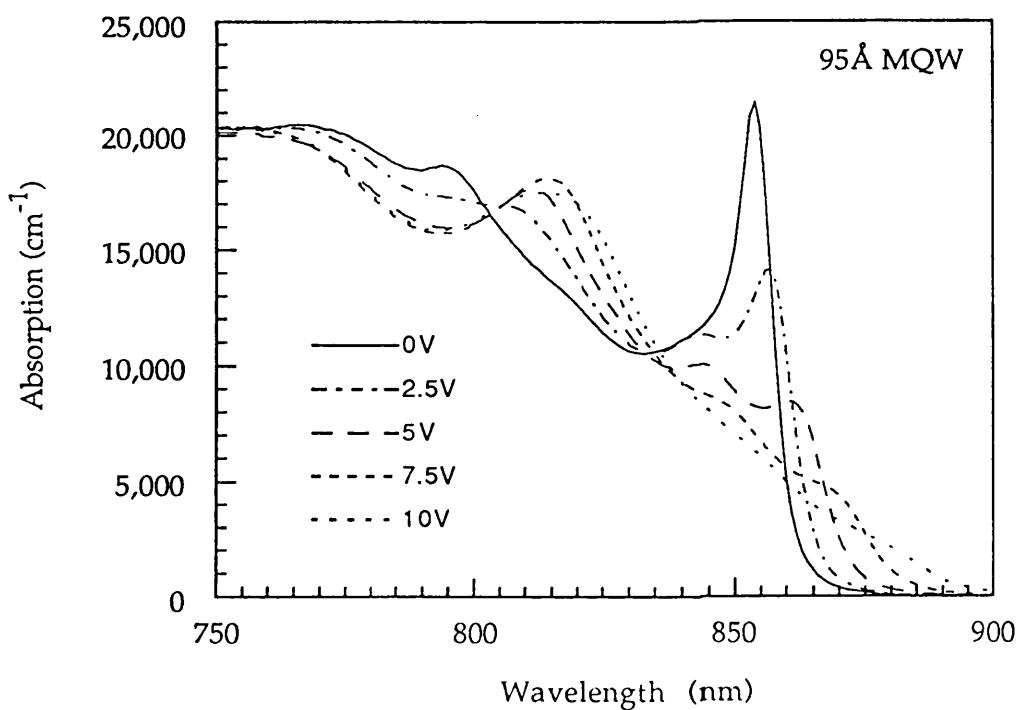

Photocurrent and absorption measurements were made on a number of GaAs on Si MQW *pin* diode test structures and the results described in Chapter 4. Quarter-wave reflector stacks were also grown on silicon and their performance compared to similar devices grown on GaAs. The results of both these studies were used to model the performance of a complete AFPM structure. Experimental results for these modulators are presented in Chapter 5. These include both photocurrent and reflection spectra.

## LIST OF CONTENTS

|                       |          |

|-----------------------|----------|

| <b>Abstract</b> ..... | <b>3</b> |

|-----------------------|----------|

### Chapter 1

#### An Introduction To Gallium Arsenide On Silicon Optoelectronic Devices

|                                                                                               |    |

|-----------------------------------------------------------------------------------------------|----|

| 1.1 Introduction .....                                                                        | 8  |

| 1.2 Materials Comparison Between GaAs and Silicon.....                                        | 8  |

| 1.3 Optics and Electronics .....                                                              | 17 |

| 1.3.1 <i>Optics in Communications</i> .....                                                   | 17 |

| 1.3.2 <i>Properties of Optics</i> .....                                                       | 19 |

| 1.3.3 <i>Energy Comparison of Electrical and Optical Interconnects</i> .....                  | 22 |

| 1.3.4 <i>Potential Devices for Use in Electronic Islands with Optical Interconnects</i> ..... | 25 |

| 1.3.5 <i>Packaging Considerations</i> .....                                                   | 28 |

| 1.3.6 <i>Characteristics of Modulators vis-a-vis Lasers</i> .....                             | 28 |

| 1.3.7 <i>Integrated Waveguide Structures</i> .....                                            | 31 |

| 1.3.8 <i>Self Electrooptic Effect Devices</i> .....                                           | 33 |

| 1.3.9 <i>Optoelectronics in Switching Systems</i> .....                                       | 34 |

### Chapter 2

#### The Effect of Strain in Gallium Arsenide On Silicon Quantum Well Devices

|                                                                        |    |

|------------------------------------------------------------------------|----|

| 2.1 Introduction to Quantum Wells .....                                | 42 |

| 2.2 Quantum Wells and Strain .....                                     | 47 |

| 2.2.1 <i>Calculation of Change in Band-gaps and Band-offsets</i> ..... | 51 |

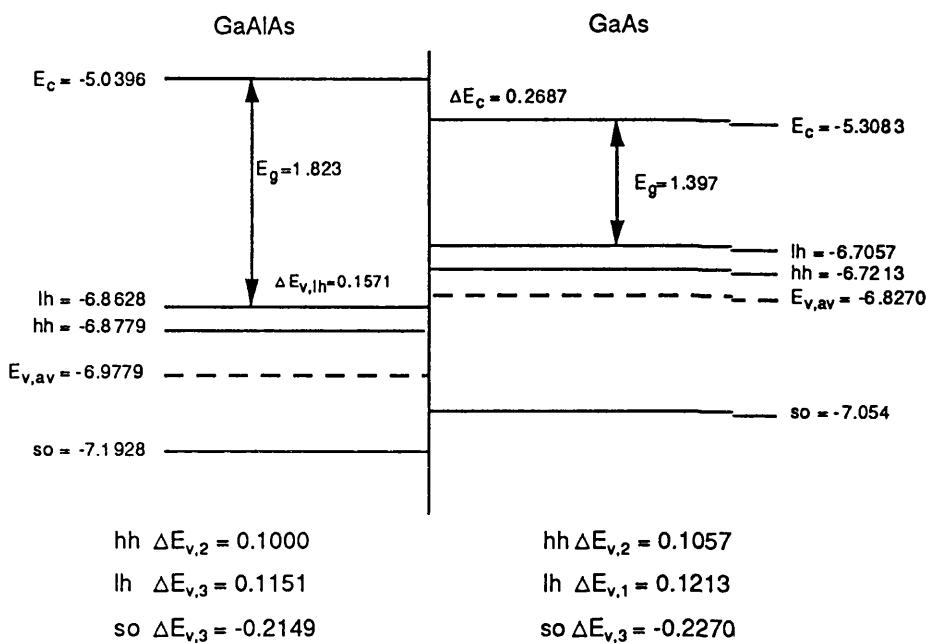

| 2.2.1.1 <i>Tensile Strain</i> .....                                    | 52 |

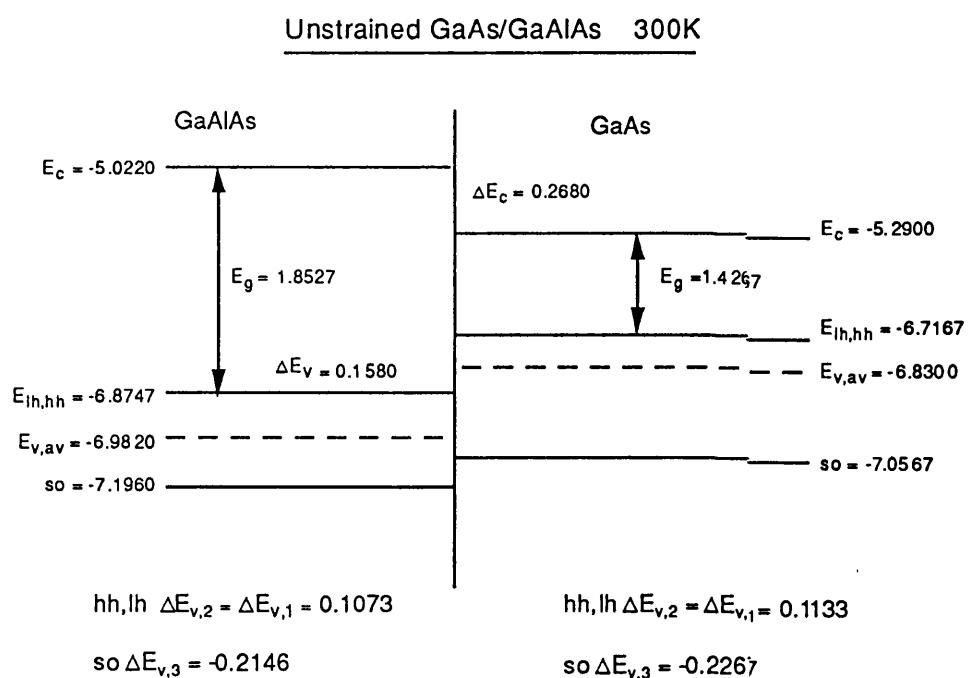

| 2.2.1.2 <i>Unstrained GaAs/GaAlAs</i> .....                            | 55 |

| 2.2.1.3 <i>Compressive Strain</i> .....                                | 55 |

| 2.2.1.4 <i>Band Structure Diagrams</i> .....                           | 56 |

| 2.2.2 <i>Change in Effective Masses Due to Strain</i> .....            | 59 |

| 2.2.3 <i>Transition Energies in Strained Quantum Wells</i> .....       | 62 |

| 2.3 Application of Electric Field to Quantum Well Structures .....     | 63 |

| 2.4 Introduction to AFPMs.....                                         | 66 |

| 2.5 Strained Quantum Wells and AFPMs .....                             | 71 |

### Chapter 3

#### Growth and Material Properties of Gallium Arsenide On Silicon Structures

|                                                                                            |    |

|--------------------------------------------------------------------------------------------|----|

| 3.1 Growth Problems and Dislocations.....                                                  | 78 |

| 3.1.1 <i>Lattice Mismatch</i> .....                                                        | 78 |

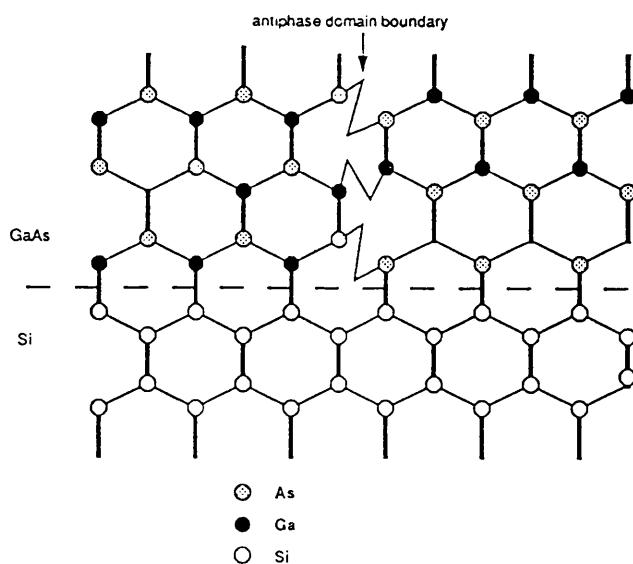

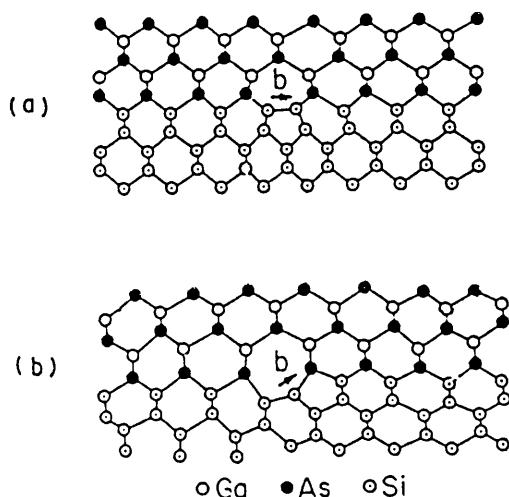

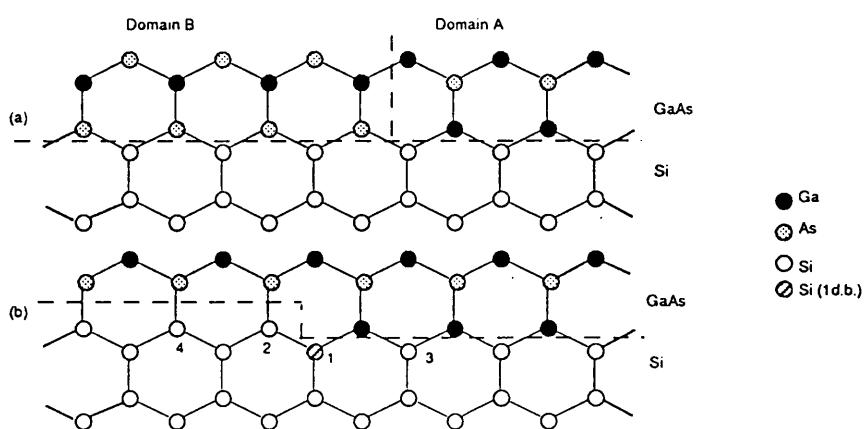

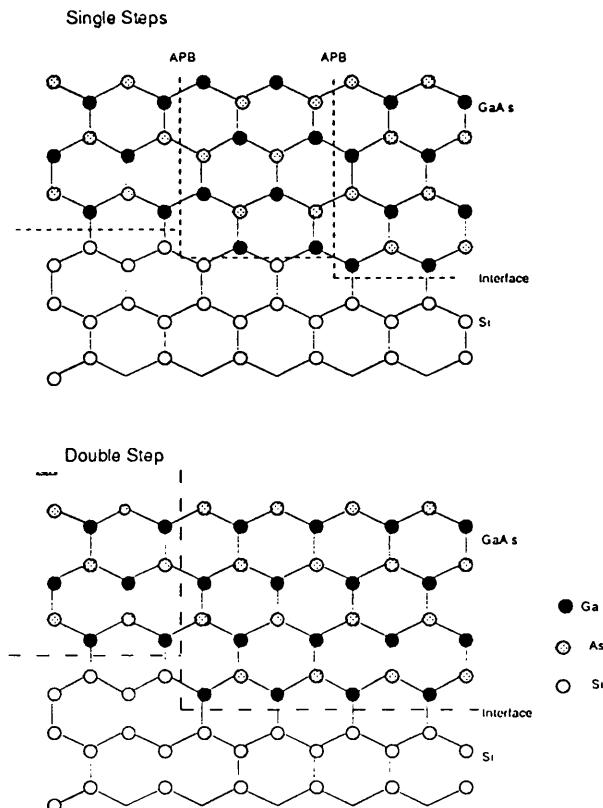

| 3.1.2 <i>Anti-Phase Domains (APDs) and the Problems of Polar on Non-Polar Growth</i> ..... | 82 |

|                                                                                         |     |

|-----------------------------------------------------------------------------------------|-----|

| 3.1.3 <i>Thermal Mismatch</i> .....                                                     | 87  |

| 3.2 Epitaxial Growth of Gallium Arsenide on Si .....                                    | 90  |

| 3.2.1 <i>Introduction</i> .....                                                         | 90  |

| 3.2.2 <i>MBE Growth of GaAs on Silicon Structures</i> .....                             | 92  |

| 3.2.3 <i>MOCVD Growth of GaAs on Silicon Structures</i> .....                           | 94  |

| 3.3 Improvement of Gallium Arsenide on Si Material Quality .....                        | 99  |

| 3.3.1 <i>Introduction</i> .....                                                         | 99  |

| 3.3.2 <i>Optimization of Conventional Growth</i> .....                                  | 101 |

| 3.3.2.1 <i>Nucleation Procedures</i> .....                                              | 103 |

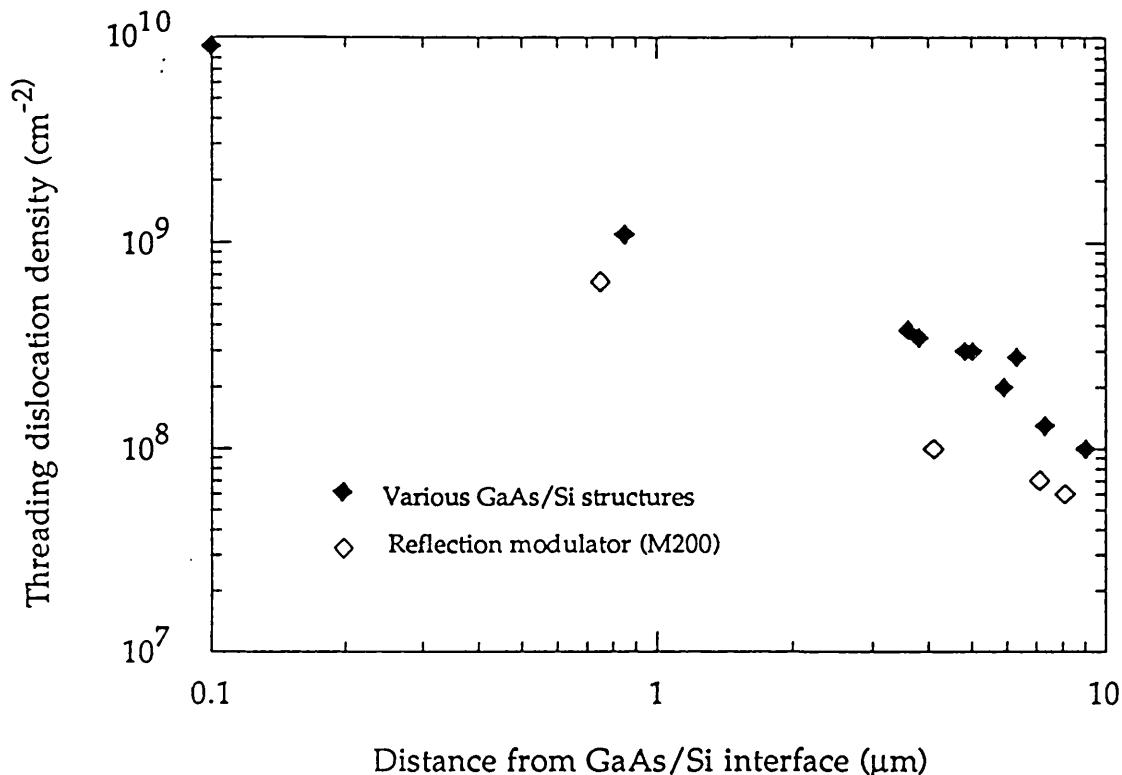

| 3.3.2.2 <i>Effect of Layer Thickness on Material Quality</i> .....                      | 104 |

| 3.3.2.3 <i>Effect of Growth Temperature on Material Quality</i> .....                   | 105 |

| 3.3.3 <i>Improvement of Material Quality by Layer Design</i> .....                      | 106 |

| 3.3.4 <i>Selective Growth</i> .....                                                     | 108 |

| 3.3.4.1 <i>Patterned Substrates</i> .....                                               | 108 |

| 3.3.4.2 <i>Post Growth Patterning</i> .....                                             | 110 |

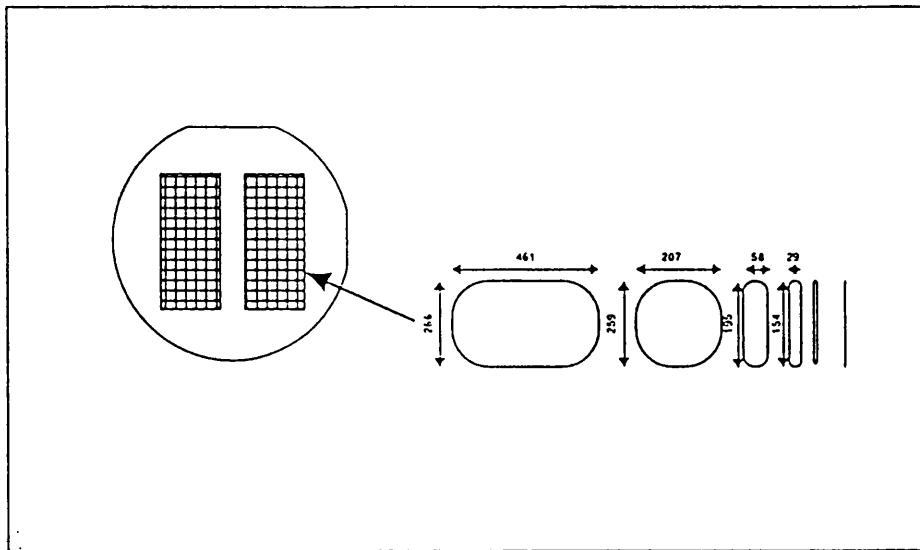

| 3.3.4.3 <i>M488 Patterned Substrate</i> .....                                           | 111 |

| 3.3.5 <i>Alternative Epitaxial Systems</i> .....                                        | 112 |

| 3.3.6 <i>Novel Growth Techniques</i> .....                                              | 114 |

| 3.4 Material Analysis .....                                                             | 116 |

| 3.4.1 <i>Introduction</i> .....                                                         | 116 |

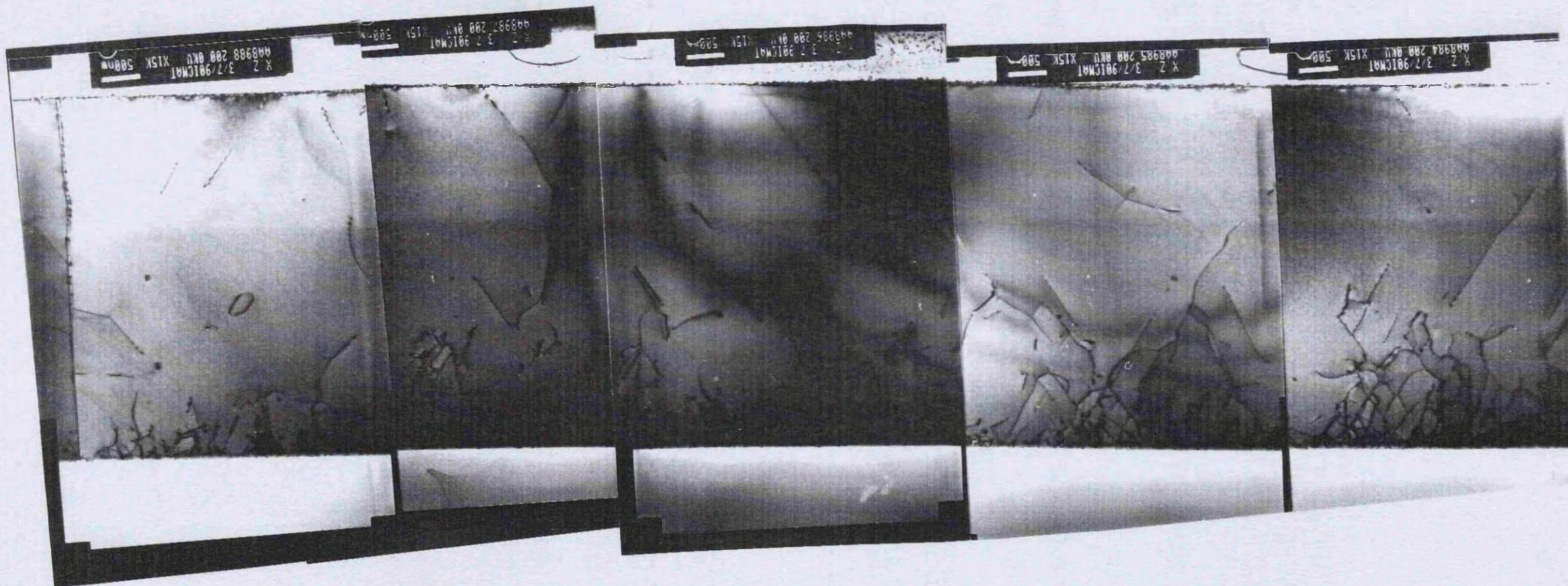

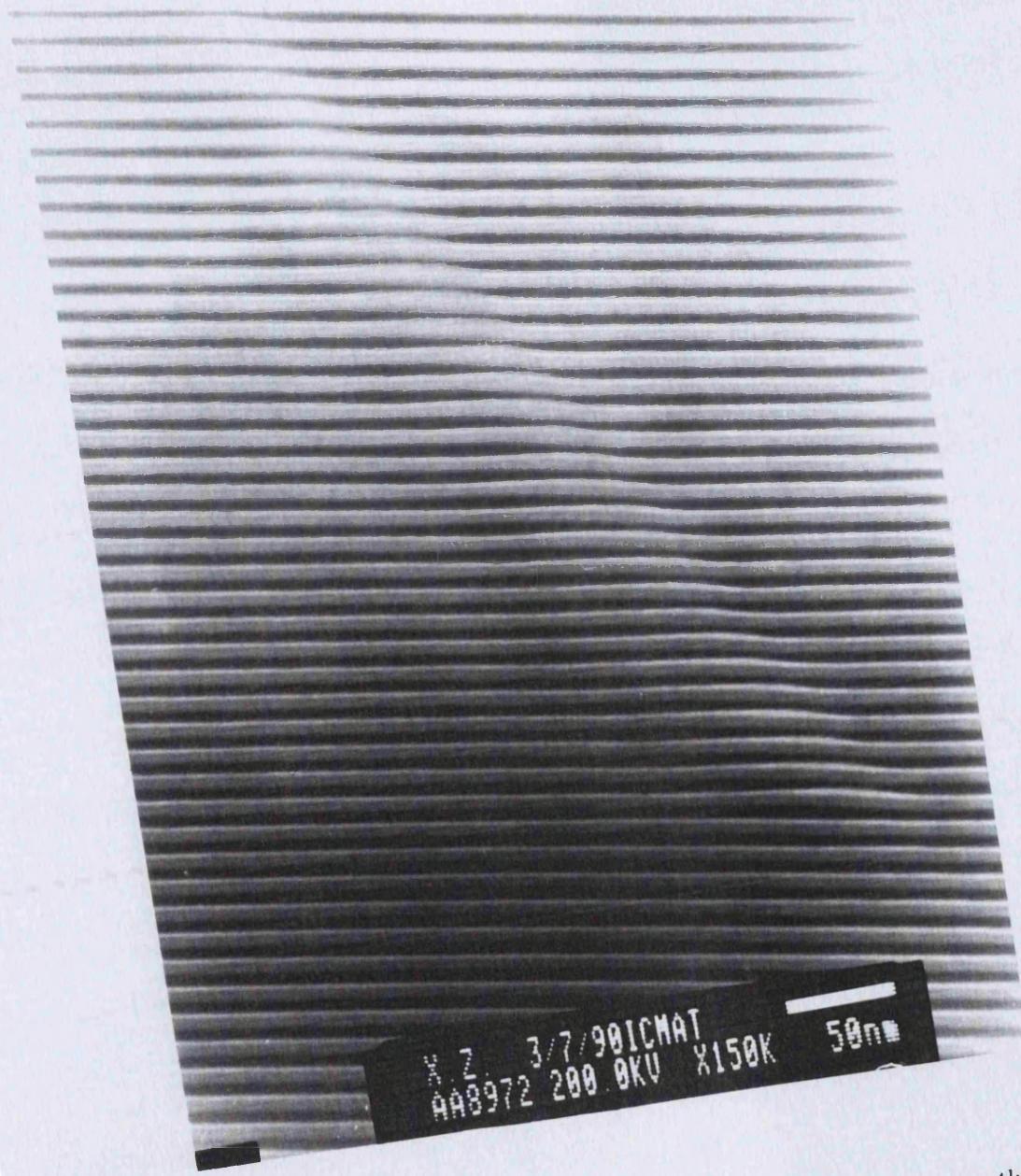

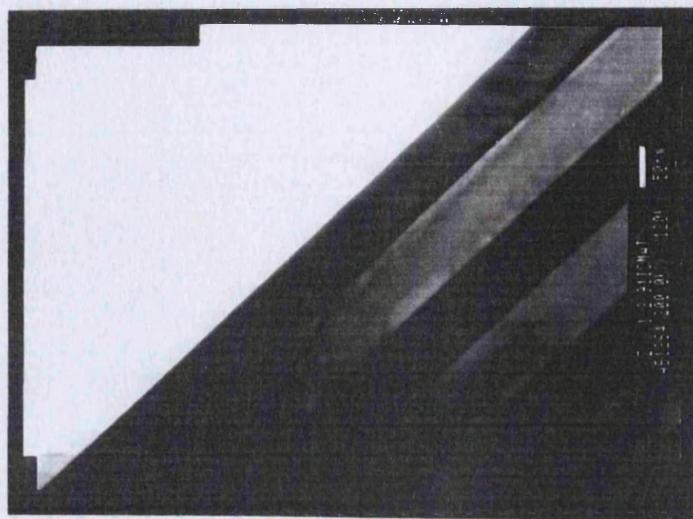

| 3.4.2 <i>Transverse Electron Microscopy</i> .....                                       | 116 |

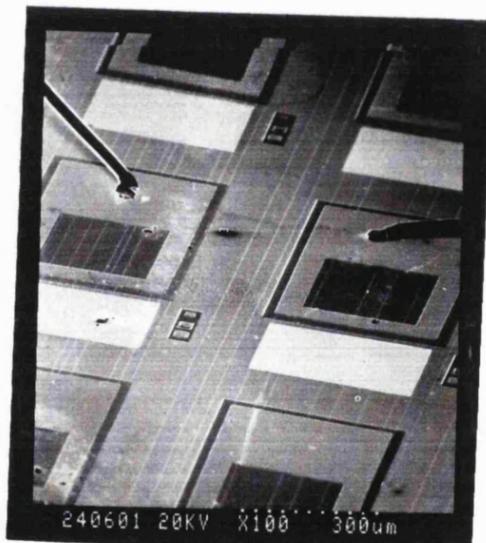

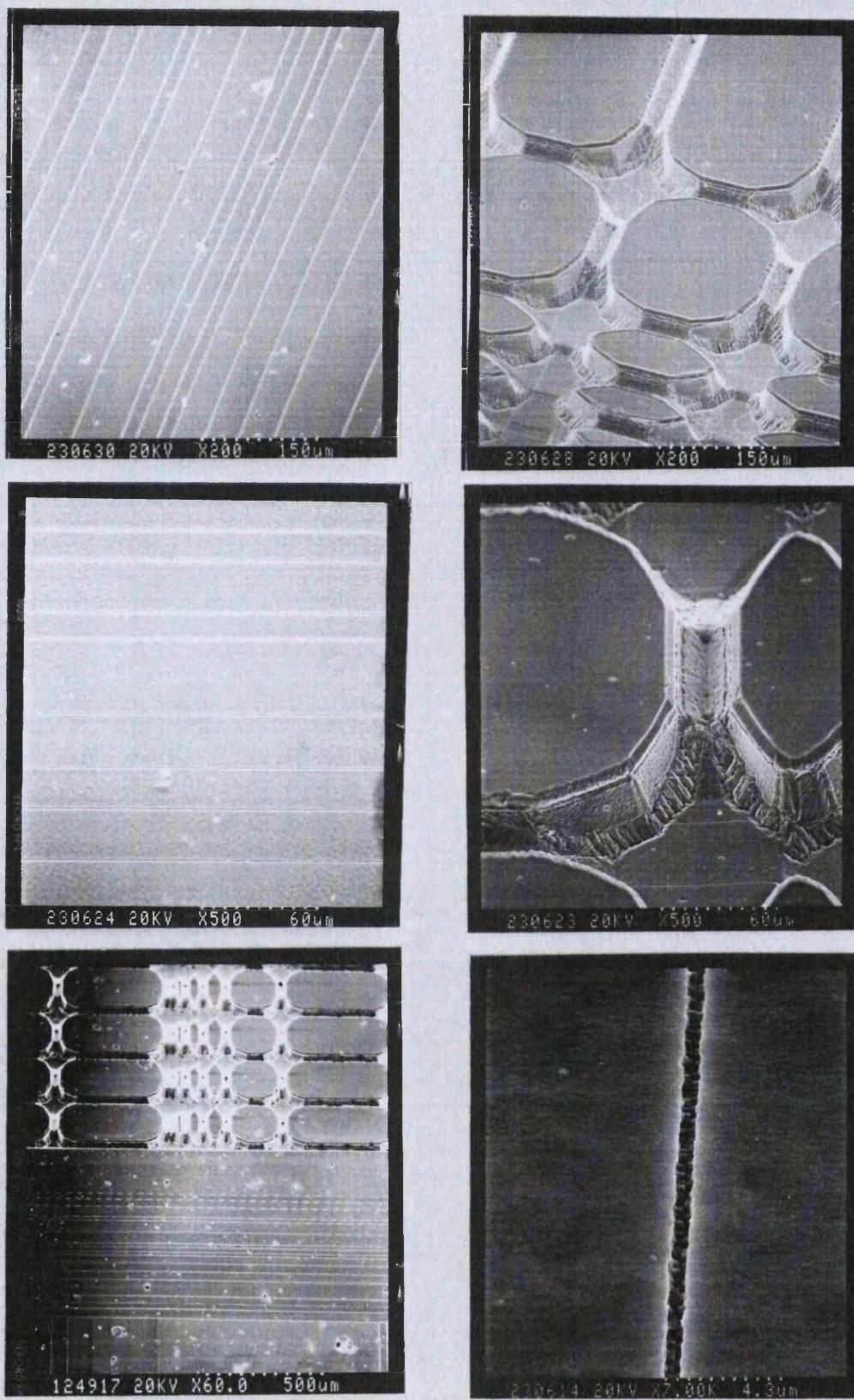

| 3.4.3 <i>Surface Microscopy: SEM and Optical Microscopy</i> .....                       | 122 |

| 3.4.4 <i>Material Analysis of the M488 Patterned Substrates</i> .....                   | 125 |

| 3.4.4.1 <i>Optical Assessment</i> .....                                                 | 125 |

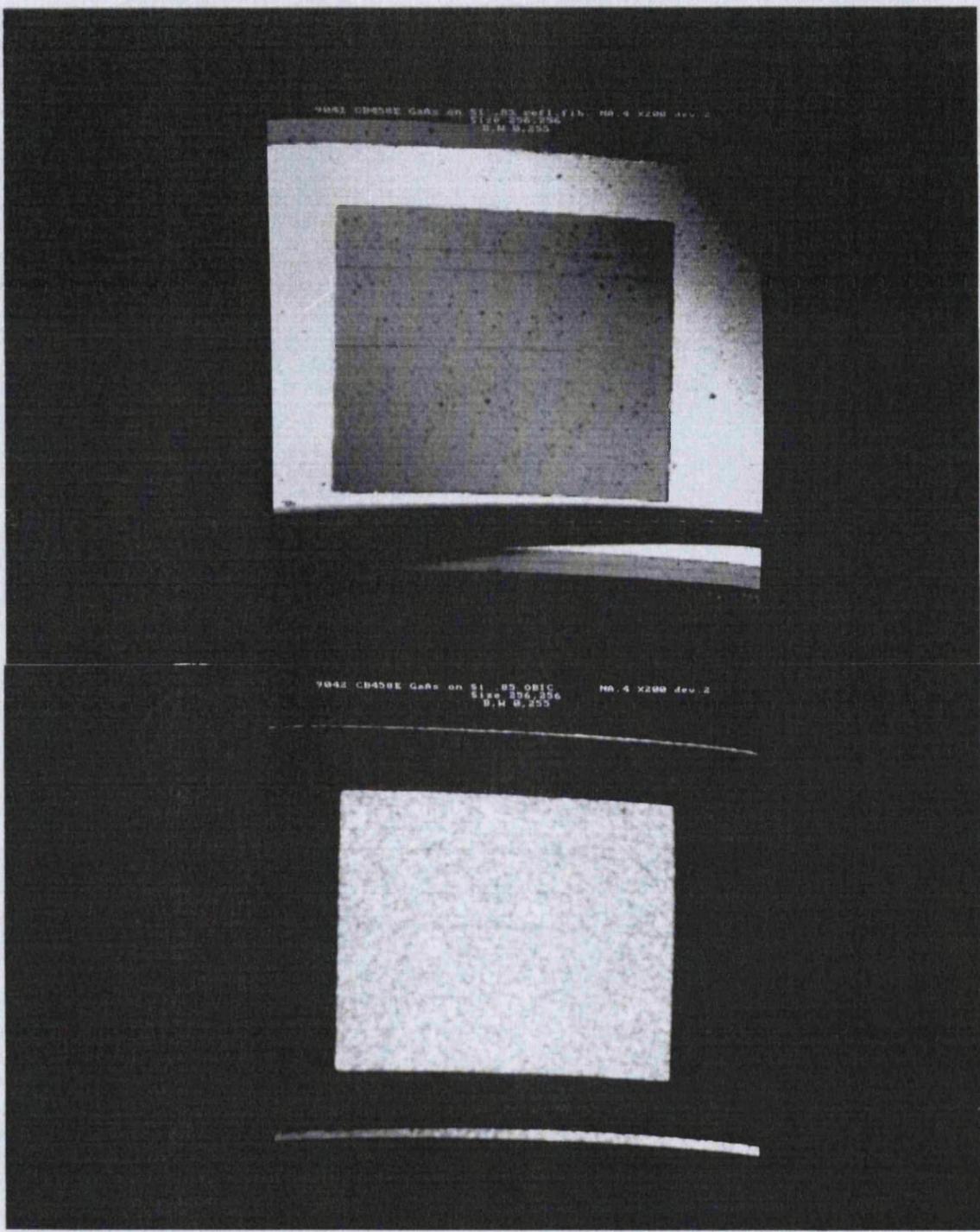

| 3.4.5 <i>Characterization of GaAs on Si Growth by Scanning Optical Microscopy</i> ..... | 128 |

## Chapter 4

### Device Results for GaAs on Silicon MQW *pin* Diode Structures

|                                                                                                                    |     |

|--------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 Introduction .....                                                                                             | 138 |

| 4.2 Structures Tested .....                                                                                        | 139 |

| 4.3 Fabrication .....                                                                                              | 140 |

| 4.4 Electrical Assessment .....                                                                                    | 141 |

| 4.4.1 <i>MBE Grown Structures</i> .....                                                                            | 142 |

| 4.4.1.1 <i>M121: a 75 period 95Å well MQW diode</i> .....                                                          | 142 |

| 4.4.1.2 <i>M488: A 50 period 95Å well MQW diode grown on patterned and unpatterned substrates</i> .....            | 143 |

| 4.4.2 <i>MOVPE Grown Structures</i> .....                                                                          | 146 |

| 4.4.2.1 <i>CB252: A 50 period 40Å well MQW diode grown on Si and GaAs substrates</i> .....                         | 146 |

| 4.4.2.2 <i>CB305 and CB306: 50 period 54Å well &amp; 95Å well MQW diodes grown on Si and GaAs substrates</i> ..... | 146 |

| 4.4.2.3 <i>CB504 and CB505 50 period 41Å well/60Å barrier and 56Å well/60Å barrier</i> .....                       | 148 |

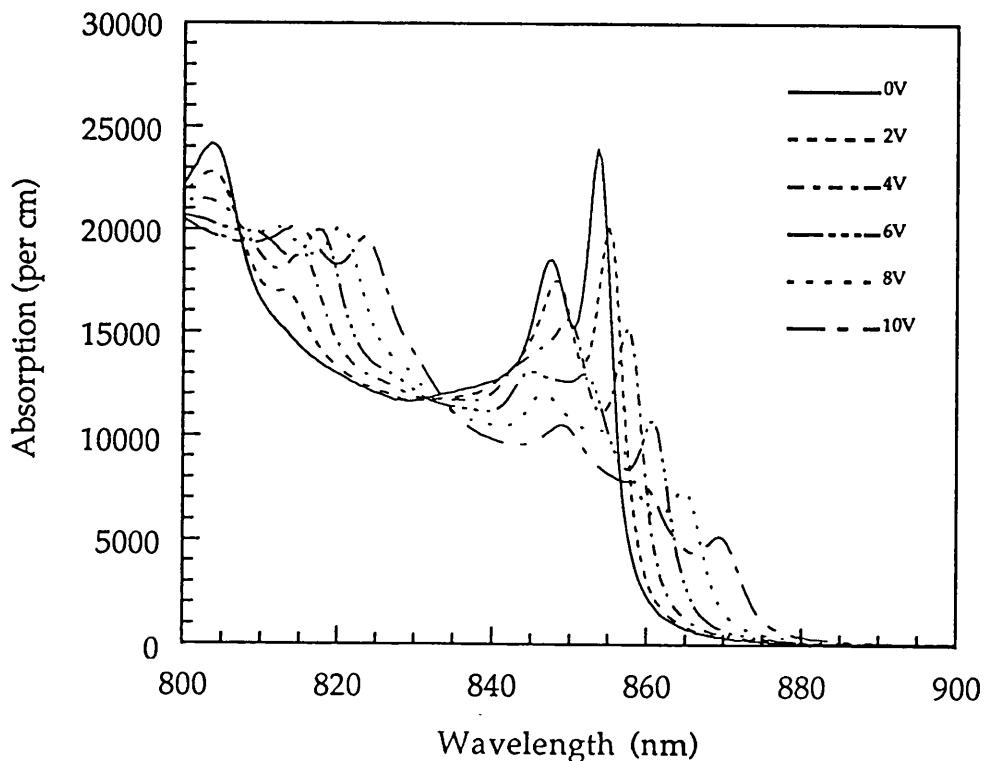

| 4.5 Photocurrent and Absorption .....                                                                              | 148 |

| 4.5.1 <i>Photocurrent Measurement</i> .....                                                                        | 148 |

|                                              |     |

|----------------------------------------------|-----|

| 4.5.2 Measurement of Absorption .....        | 150 |

| 4.5.3 MBE Structures .....                   | 152 |

| 4.5.3.1 M121: a 75 period 95Å well MQW ..... | 152 |

| 4.5.4 MOCVD Structures .....                 | 155 |

| 4.5.4.1 CB252: a 50 period 40Å well MQW..... | 155 |

| 4.5.4.2 CB305: a 50 period 54Å well MQW..... | 157 |

| 4.5.4.3 CB306: a 50 period 95Å well MQW..... | 158 |

| 4.5.5 Discussion .....                       | 164 |

## Chapter 5

### Results for Gallium Arsenide on Silicon Reflector Stacks and Modulator Structures

|                                                                                      |     |

|--------------------------------------------------------------------------------------|-----|

| 5.1 Introduction .....                                                               | 169 |

| 5.2 Design of Reflector Stacks .....                                                 | 169 |

| 5.2.1 Introduction .....                                                             | 169 |

| 5.2.2 Problems of Growth Tolerance.....                                              | 178 |

| 5.3 Performance of Reflector Stacks Grown on Silicon .....                           | 180 |

| 5.3.1 MBE Grown Stacks .....                                                         | 180 |

| 5.3.1.1 M199: A 12 period reflector stack grown on<br>silicon by MBE .....           | 180 |

| 5.3.2 MOCVD Grown Stacks .....                                                       | 181 |

| 5.3.2.1 QT105 and QT145: 15 period stacks grown on<br>silicon by MOCVD .....         | 181 |

| 5.4 Results for Modulator Structures Grown on Silicon.....                           | 184 |

| 5.4.1 Electrical Performance of Modulator Structures.....                            | 185 |

| 5.4.2 Photocurrent and Reflection Measurements of AFPM<br>Modulator Structures ..... | 193 |

| 5.4.2.1 MBE Grown Modulator Structures .....                                         | 193 |

| 5.4.2.2 MOCVD Grown Modulator Structures .....                                       | 202 |

| 5.4.2.3 Summary .....                                                                | 208 |

| Conclusion .....                                                                     | 211 |

| References.....                                                                      | 214 |

| Acknowledgements .....                                                               | 230 |

| List of Publications .....                                                           | 231 |

## *Chapter 1*

# **An Introduction To Gallium Arsenide On Silicon Optoelectronic Devices**

## 1.1 INTRODUCTION

The motivations for the integration of Gallium Arsenide and Silicon are derived from an appreciation of the merits of the two different materials. There are distinct advantages for purely electronic systems, but most exciting are the possibilities for new systems using optics to enhance the capabilities of electronics. For the latter application a solution combining the merits of both GaAs and silicon will be shown to be particularly powerful. Early work concerning GaAs on silicon recognized the optical properties of GaAs that silicon does not possess, however the implications were not considered in great depth. The motivations behind the work lay more in studying the potential for such growth, rather than particular devices or future systems. Therefore when this project began most studies reported in the literature were concerned with simple epitaxial test layers of GaAs on silicon only. Nevertheless, they did clearly recognize the different strengths and the weaknesses of the two material systems, and some of the benefits of combining the best points of each. We will thus start by looking at some of the physical properties of GaAs and silicon, and relating these to both their electronic performance and their benefits in optoelectronic systems.

## 1.2 MATERIALS COMPARISON BETWEEN GaAs AND SILICON

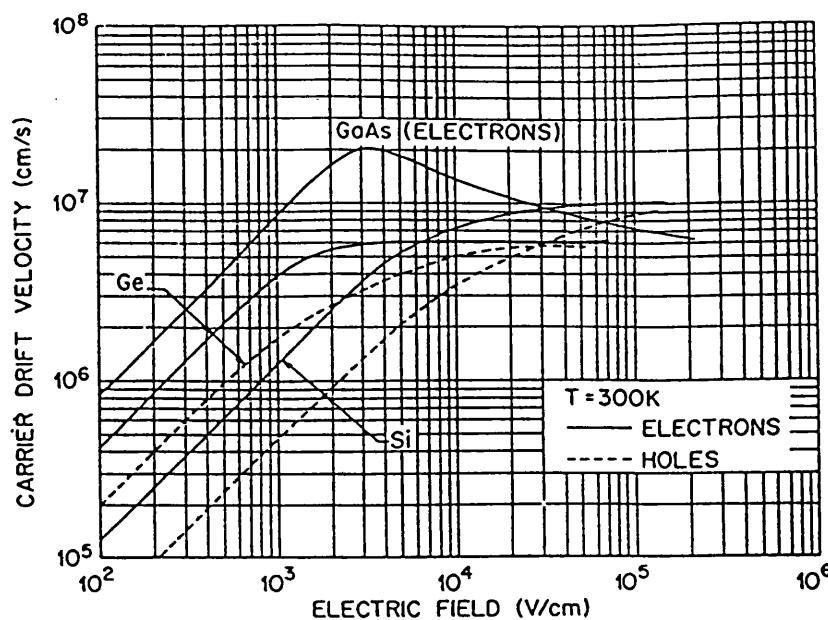

Presented below is a table showing the main physical properties of both GaAs and silicon, at 300K derived from references [Sze], [Wright] and [Landolt&Bornstein]. An interesting point is the higher apparent mobility (about 5 times) of GaAs *vis-a-vis* silicon, however, a clearer view is obtained from looking at the figure of carrier drift velocity versus field, reproduced below in Fig 1.1. Although the mobility of GaAs is, indeed, five times greater than silicon at low field it reaches a peak value at a field strength of  $0.3\text{V}\mu\text{m}^{-1}$ , while that of silicon continues to increase monotonically. As devices continue to decrease in size the high field region becomes increasingly accessible; for example, a gate width of  $0.5\mu\text{m}$  at 1V operation will exceed the field at which GaAs has its maximum carrier velocity. In fact, due to pinch effects, the localized peak field will be even greater, thereby reducing the likely advantage to about 1.1 times for GaAs [Saul].

**Table 1.1** The main physical properties of GaAs and Silicon at 300K.

|                                                                     | <b>GaAs</b>            | <b>Silicon</b>        |

|---------------------------------------------------------------------|------------------------|-----------------------|

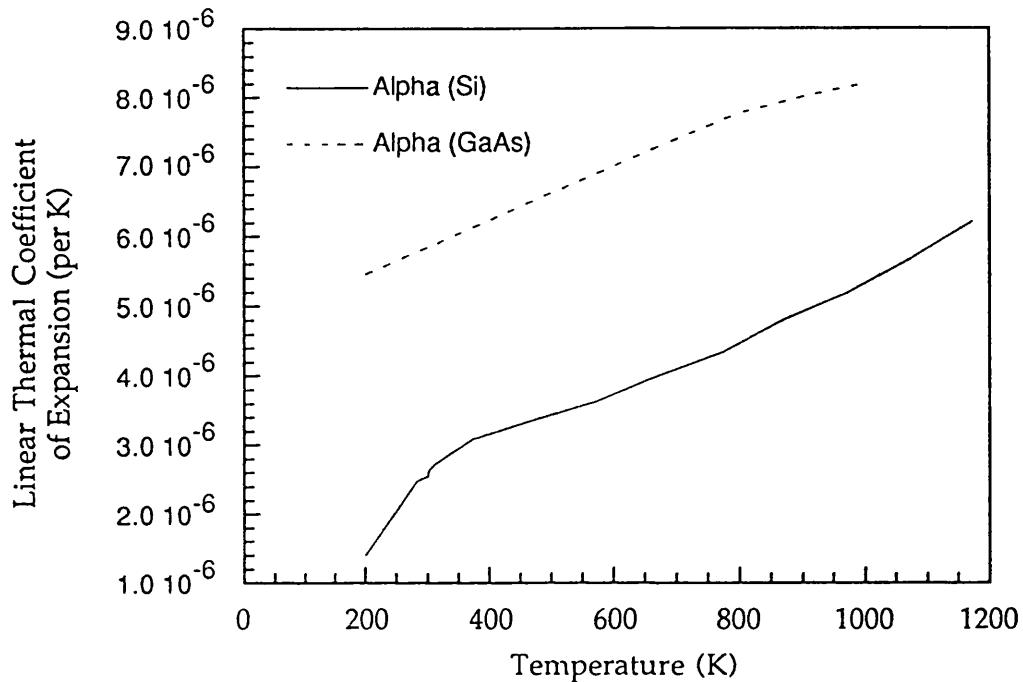

| linear thermal coefficient of expansion ( $^{\circ}\text{C}^{-1}$ ) | $6.86 \times 10^{-6}$  | $2.6 \times 10^{-6}$  |

| atoms/cm <sup>3</sup>                                               | $4.42 \times 10^{22}$  | $5 \times 10^{22}$    |

| atomic weight                                                       | 144.63                 | 28.09                 |

| breakdown field (Vcm <sup>-1</sup> )                                | $4 \times 10^5$        | $3 \times 10^5$       |

| crystal structure                                                   | zincblende (non-polar) | diamond (polar)       |

| density (g/cm <sup>3</sup> )                                        | 5.32                   | 2.328                 |

| dielectric constant                                                 | 13.1                   | 11.9                  |

| effective density of states:                                        |                        |                       |

| in conduction band N <sub>c</sub> (cm <sup>-3</sup> )               | $4.7 \times 10^{17}$   | $2.8 \times 10^{19}$  |

| in valence band N <sub>v</sub> (cm <sup>-3</sup> )                  | $7.0 \times 10^{18}$   | $1.04 \times 10^{19}$ |

| effective mass, m*/m <sub>0</sub> :                                 |                        |                       |

| electrons                                                           | 0.067                  | $m_e^* = 0.98$        |

|                                                                     |                        | $m_t^* = 0.19$        |

| holes                                                               | $m_h^* = 0.082$        | $m_h^* = 0.16$        |

|                                                                     | $m_{th}^* = 0.45$      | $m_{th}^* = 0.49$     |

| electron affinity (V)                                               | 4.07                   | 4.05                  |

| energy gap (eV)                                                     | 1.424 (direct)         | 1.12 (indirect)       |

| intrinsic carrier concentration (cm <sup>-3</sup> )                 | $1.79 \times 10^{16}$  | $1.45 \times 10^{10}$ |

| intrinsic Debye length (μm)                                         | 2250                   | 24                    |

| intrinsic resistivity (Ω-cm)                                        | $10^8$                 | $2.3 \times 10^5$     |

| lattice constant                                                    | 5.653 Å                | 5.431 Å               |

| melting point (°C)                                                  | 1238                   | 1415                  |

| minority carrier lifetime (s)                                       | $\approx 10^{-8}$      | $2.5 \times 10^{-3}$  |

| mobility (drift) (cm <sup>2</sup> /Vs)                              | $\mu_n = 8500$         | $\mu_n = 1500$        |

|                                                                     | $\mu_p = 400$          | $\mu_p = 450$         |

| optical phonon energy (eV)                                          | 0.035                  | 0.063                 |

| phonon mean free path (Å)                                           | 58                     | 76 (electron)         |

|                                                                     |                        | 55 (hole)             |

| specific heat (J/g-°C)                                              | 0.35                   | 0.7                   |

| thermal conductivity (W/cm-°C)                                      | 0.46                   | 1.5                   |

| thermal diffusivity (cm <sup>2</sup> s <sup>-1</sup> )              | 0.24                   | 0.9                   |

|                                                                 |                                                                   |                                                          |

|-----------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------|

| vapour pressure (Pa)                                            | 100 at 1050°C<br>1 at 900°C                                       | 1 at 1650°C<br>10 <sup>-6</sup> at 900°C                 |

| diffusion coefficient (m <sup>2</sup> s <sup>-1</sup> )         | D <sub>n</sub> =0.0220<br>D <sub>p</sub> =0.0010                  | D <sub>n</sub> =0.0039<br>D <sub>p</sub> =0.0012         |

| maximum electron velocity (ms <sup>-1</sup> )                   | 2x10 <sup>5</sup> (3x10 <sup>5</sup> Vm <sup>-1</sup> )           | 10 <sup>5</sup> (at 5x10 <sup>6</sup> Vm <sup>-1</sup> ) |

| bulk modulus (10 <sup>10</sup> dyne cm <sup>-2</sup> )          | 75.5                                                              | 98                                                       |

| Young's modulus (100) (10 <sup>10</sup> dyne cm <sup>-2</sup> ) | 85.5                                                              | 131                                                      |

| Shear modulus (100) (10 <sup>10</sup> dyne cm <sup>-2</sup> )   | 32.6                                                              | 51                                                       |

| Poisson's ratio (100) (10 <sup>10</sup> dyne cm <sup>-2</sup> ) | 0.55                                                              | 0.28                                                     |

| cleaving                                                        | easiest along {110} planes due to slight ionic component in bonds | easiest along {111} planes                               |

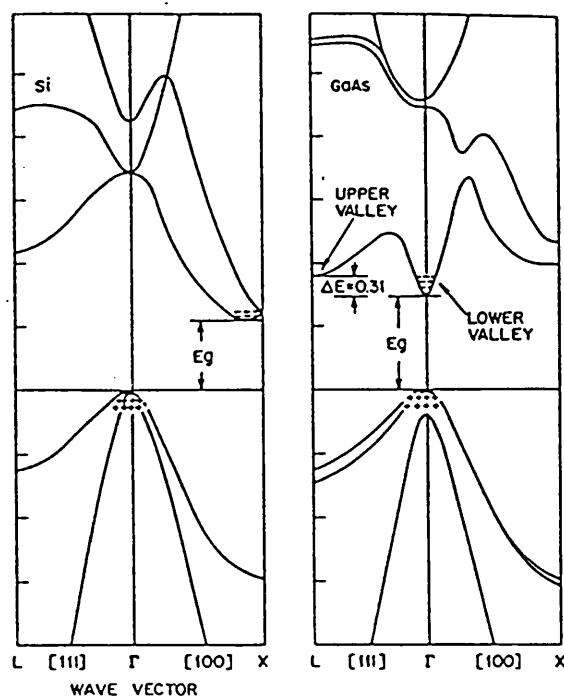

The reason for the peak in GaAs can be seen from the band structure figures for GaAs and silicon shown in Fig 1.2. An upper valley exists for GaAs only 0.31eV above the direct band-gap, into which carriers may be excited by high fields. Here they have a higher effective mass and a correspondingly lower velocity.

The above description applies only to electrons, and in the case of holes the velocity in GaAs is actually lower than that for silicon. This explains the lack of an equivalent to CMOS in GaAs technology, for p-channel devices would be slower than in silicon.

As electronic circuits become ever more highly integrated, with a greater density of devices, the high field region will continue to favour silicon. For example, silicon bipolar devices with a base width of 0.2μm are likely to be competitive with any bulk GaAs devices, although the position is complicated by GaAs/GaAlAs and other compound semiconductor heterojunction devices, which are discussed later on. Silicon's other physical properties also aid its greater capacity for increased levels of integration. For example, its thermal conductivity is, at 1.5W/cm °C, three times greater than GaAs. Consequently, heat dissipation is better, which is a significant factor in high density, high speed circuits. Although GaAs has a higher melting point of 1415°C compared to 1238°C for silicon, the latter is actually better suited to withstanding high temperatures, for GaAs begins to disassociate at well below its melting point, becoming highly toxic. This could potentially pose a

significant problem and is recognized in the stringent safety procedures in growth systems such as MOCVD.

Figure 1.1 Carrier drift velocity versus electric field for high purity GaAs, Si and Ge (after Sze)

Figure 1.2 Energy-band diagrams for GaAs and Si showing upper valley minimum for GaAs (after Sze)

Also significant are the mechanical properties of the two semiconductors. Silicon, at  $2.33\text{g/cm}^3$ , is less than half the density of GaAs ( $5.32\text{g/cm}^3$ ). The advantages of reduced weight could extend from applications as diverse as space systems to highly portable microprocessors. The difference between the two is in fact further compounded by the greater strength of silicon, which allows thinner substrates to be used. This greater strength is also likely to maintain the current reliability advantage of silicon, particularly where large areas are required - either in the growth process, where large wafers can provide higher yields at reduced cost, or in increasingly large integrated circuits.

Whilst some of the advantages of silicon have been stressed, GaAs has the major benefit of a naturally occurring semi-insulating substrate, a corollary of its much lower intrinsic carrier concentration. The result is a reduction in parasitic capacitance, which increases speed and reduces power consumption. It has also made GaAs unsurpassed in its suitability for analogue RF applications, allowing propagation by low loss quasi-TEM mode rather than through the bulk of the 'lossy' semiconductor as would occur on silicon. The RF noise performance of GaAs is also significantly better than silicon. Furthermore, inductors can be fabricated and integrated onto GaAs, which is not possible on silicon. While much research has been directed towards the development of semi-insulating silicon substrates, through the implantation of insulating layers, or by deposition of silicon on sapphire, they are unlikely to become an alternative to GaAs in the RF analogue field. However, they could result in a useful reduction in parasitic capacitance for digital applications.

The greatest difference between GaAs and silicon is, of course, the nature of the energy-band structures, as shown in Fig 1.2 above. The valence band maxima for GaAs and silicon occur at the zero wave vector point ( $\Gamma$ ), and the nature of the bands at this point control the simple hole conduction processes. The conduction band minimum also occurs at  $\Gamma$  for GaAs, but near the X point in silicon. Therefore the electron wave vector has finite magnitude and direction [100] for conduction electrons in silicon. The energy gap can be seen to be larger in GaAs than for silicon, therefore fewer carriers are thermally generated at room temperature, with the result that undoped GaAs is a better insulator than silicon. We have seen how this can reduce parasitic capacitance, but it also has the benefit of increasing the temperature at which thermally generated carriers exceed the intentional doping density, thereby increasing the operating range.

In silicon the difference in wave vector between the conduction band minimum and the valence band maximum means optical absorption and luminescence across the band-gap requires the participation of momentum conserving phonons. This process is thus intrinsically less efficient than it is in GaAs. For GaAs, three valence bands reach their maxima at  $\Gamma=0$ . Two are normally degenerate, and the third is split-off ( $\Delta=0.34\text{eV}$ ) to lower energy. The two degenerate bands have different curvature at  $\Gamma$  and therefore different masses, and are so known as the heavy hole and light hole bands.

The direct band-gap of GaAs, allowing efficient light emission, has opened up a whole host of optoelectronic applications unobtainable at present using silicon technology. Most dramatic of which has been the enormous success of GaAs-based semiconductor lasers. Recently there has been great interest in the strong photoluminescence shown by porous silicon, believed to be due to quantum confinement effects in the thin silicon wires. However, at this stage it is impossible to predict whether it can be used in practical devices, and so present an alternative to GaAs.

Another advantage of GaAs that attracted attention early on its development was its greater radiation hardness compared to silicon, although this would seem to be of minor importance in the great majority of applications.

In addition to considering GaAs and silicon in the context of discrete device performance it is important to look at their performance in large scale integrated circuits. It has become increasingly apparent that these are actually interconnection limited, and that the speed is largely independent of the basic transistor technology. Past performance projections based on straight-line log plots of packing density, speed, and processing power will cease to be valid. This is due to a number of inherent problems. Firstly, there is the physical problem of pin out, in which it becomes increasingly difficult to address with metal tracks all the required inputs and outputs on the chip. Successive generations of more and more complex ICs have attempted to ease this problem by combining the functions of several chips onto a single large one. However, these larger chips present their own problems of interconnectivity between different parts of the circuit within the chip itself, sometimes several centimetres in length. Considerable energy is spent charging and discharging these lines, whether inside or outside the chip, and as operating speeds are increased the problems of crosstalk and clockskew become severe. This may necessitate distribution of clock pulses by precise lengths of cable or

interconnect. The interconnects themselves may also be needed to support, cool, and provide power to devices. Interconnect performance depends on: the "connectivity", or ability to provide sufficient input and output connections; the propagation delay per unit length; and the bandwidth, sometimes specified as either the frequency bandwidth or the bit rate. Before showing how optoelectronic devices, in particular those using GaAs on silicon, will attempt to alleviate these problems it is worth concluding our comparison of the relative benefits of the two materials.

An engineering study should be almost by definition concerned with the most cost effective, efficient solution to a problem. But comparing the likely cost of future systems is notoriously difficult and unreliable. Nevertheless, a few useful comments can be made. Firstly, the inherent strength of silicon means larger wafers are always likely to be easier to fabricate than on GaAs. At present silicon wafers of up to 200mm diameter can be produced without reduction in quality, compared to a 100mm diameter maximum for GaAs. Larger areas result in greater yield and reduced costs. The expense of GaAs is further increased by raw material and refining costs - it being more difficult to produce. The difference in bulk material cost is presently about ten times. Even so, it could be argued that in either case the basic material cost is a minor factor in the cost of the finished product, particularly if one is concerned with highly complex circuits and systems.

Processing costs are difficult to compare due to both the far greater popularity of silicon, and its more advanced state of development. As packing densities continue to increase, costly precision techniques such as lithography have to be correspondingly advanced, whilst comparatively simple processing is used for GaAs where packing densities are generally lower. In the long term, processing complexities, and thus cost, are likely to be comparable. Probably the major factor in future cost is likely to remain the comparative market volumes, so that silicon is likely to have a significant advantage for a number of years to come.

We have so far only considered silicon and GaAs in their bulk forms, but a particularly powerful property of GaAs, and indeed most compound semiconductors, is the possibility of growing new materials combining more than one semiconductor in a series of heterogeneous junctions. Most important of these is the lattice matched growth of GaAs and  $\text{Ga}_x\text{Al}_{1-x}\text{As}$ . If the layers are thin enough it will result in important changes to the optical and electronic performance of the material due to quantum confinement

effects, these are described in more detail in Chapter 2. The result, however, is the ability to fabricate novel materials with the potential to develop new and exciting devices, such as the quantum well modulators described in this thesis.

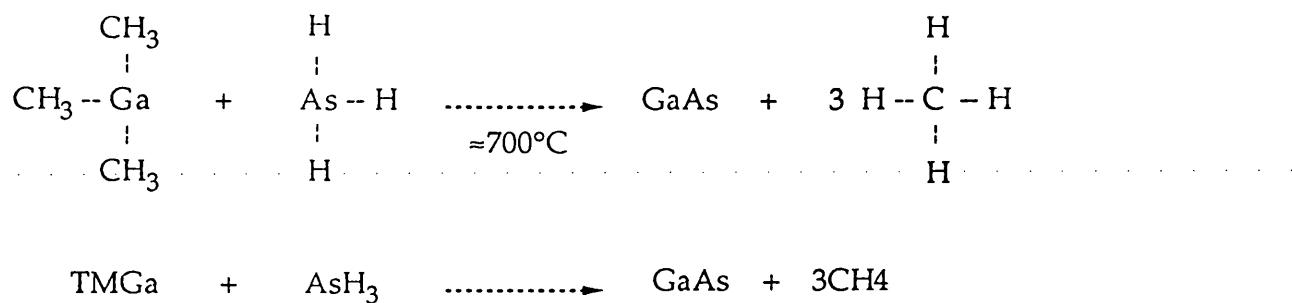

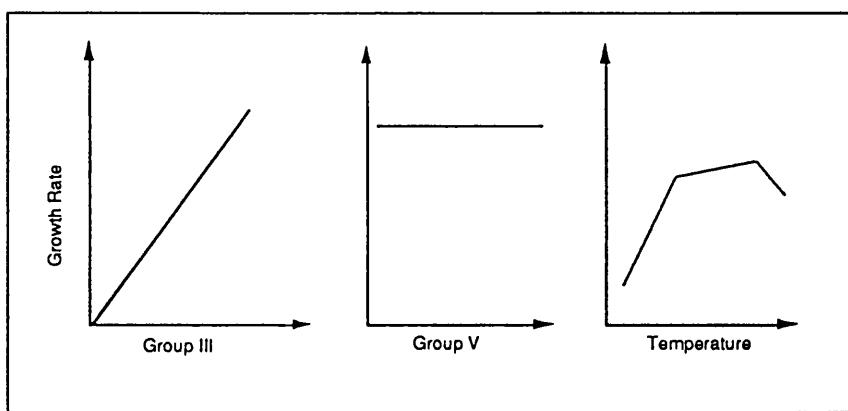

That such structures can be grown is due to the advances in semiconductor growth techniques such as MBE [Cho] and MOCVD [Manasent] which were both employed for this research. The systems used are described in Chapter 3.2. The earliest observations of quantum confinement effects in semiconductors grown by these methods were in 1974 by [Esaki and Chang] and [Dingle *et al* ].

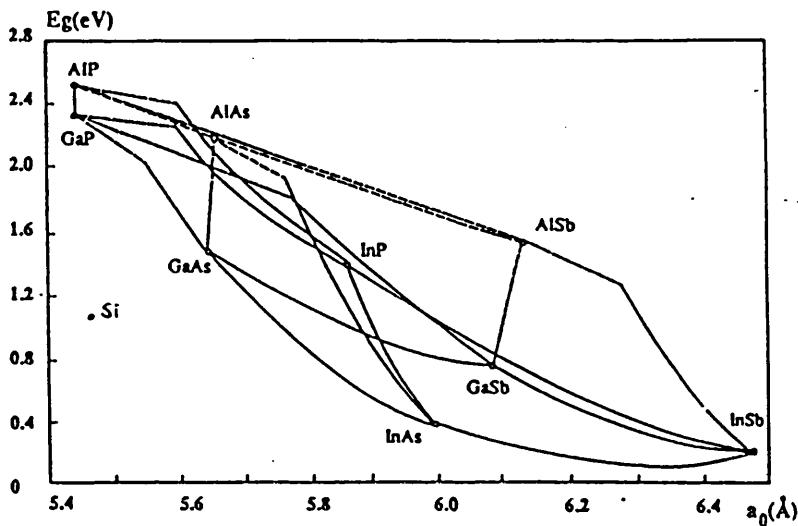

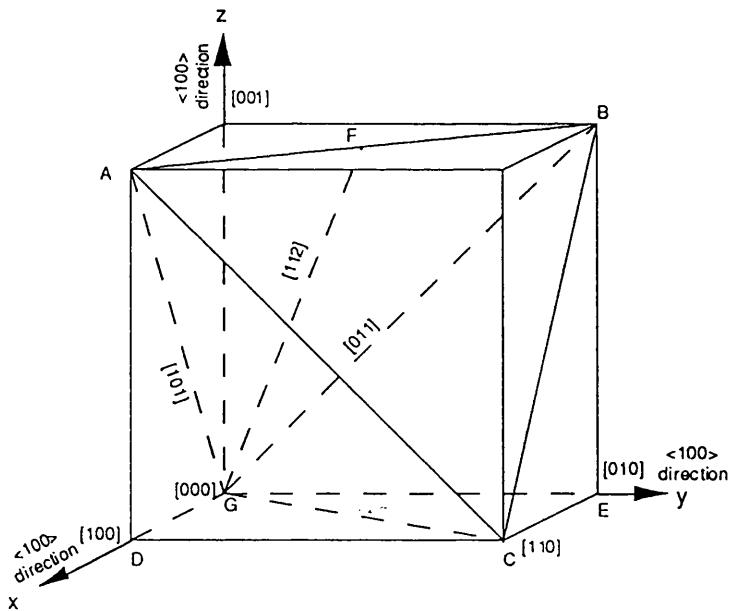

The principle factors involved in matching different semiconductors together are illustrated in Fig 1.3 below. This shows the relationship between lattice spacing, band-gap and cut-off wavelength. The lines between points represent graduated compositions of ternary compounds. Similar lines between compounds without a shared element would represent quaternaries. Originally it was thought that only lattice matched materials were compatible, but it has been found that within certain limits strained layers can also be grown, indeed GaAs on silicon is one such strained material. Strained materials can further increase the range of materials available to the semiconductor designer, but there are also limitations, as discussed in Chapter 3.1.1.

It can be seen that both GaAs and AlAs have virtually the same lattice constant, so any combination of GaAs/  $\text{Ga}_x\text{Al}_{1-x}\text{As}$  can be grown. The corresponding range of cut-off wavelengths extends from about 590nm to 860nm. In order to access the wavelengths at which optical fibre systems are operated ( $\approx 1.5\mu\text{m}$ ) it would be necessary to use, for example,  $\text{In}_{0.53}\text{Ga}_{0.47}\text{As}/\text{InP}$  [Chiu *et al*] [Geusic *et al*]. The lattice constants of these materials are too large to be grown on a silicon substrate, and they add a further level of complexity over and above that of GaAs/GaAlAs based materials. Their performance is also generally poorer. We can thus foresee a divergence in material systems. Firstly, those that are required for integration with long distance optical fibre communications, but not high levels of integration with conventional electronics; and secondly, those that may be used in free space, or short fibre-optic links, and which offer very high levels of integration when combined with silicon electronics.

Figure 1.3 Lattice constant v band-gap phase diagram

Two types of devices employing ultrathin layers of more than one semiconductor have previously received the most attention - heterojunction transistors and semiconductor lasers. Quantum wells were incorporated in the active region of semiconductor lasers. Firstly, to provide a greater range of operating wavelengths, and secondly, to improve the efficiency by increasing the proportion of injected electrons and holes which occupy the lasing state. In a bulk laser there is an infinite continuum of energy levels with a parabolic density of states, therefore there is equal gain for both TE and TM modes. The lasing efficiency is not helped by the preponderance of injected carriers near the conduction and valence bands that do not actually contribute to the lasing wavelength, but serve only to increase the threshold current. By confining the electrons and holes in quantum wells they are restrained from having a wide range of momenta, since the band structure is divided into subbands with discrete energy levels. The heavy and light hole degenerate bands are also split, the heavy hole being predominantly TE, and the light hole primarily TM. This results in only the desired states being pumped, with a concomitant reduction in the threshold current. These improvements have been realised in commercial quantum well lasers both in the GaAs/GaAlAs material system and in  $\text{In}_{0.53}\text{Ga}_{0.47}\text{As}/\text{InP}$  [Geusic *et al*]. It is important to note that there is actually a fourfold improvement from using quantum wells. Firstly, the *power* is increased due to the increased efficiency. Secondly, and for the same

reasons, the output will be more closely related to the drive current which means the *frequency response* or electrical bandwidth of the laser is improved. Thirdly, *chirp* which is caused by the modulating current, and is related to the ratio of change of refractive index to change of gain of the laser medium is reduced. Finally, the *linewidth* itself is reduced.

The problems with such lasers are in the thickness control of the layers and the growth difficulties, the sensitivity to temperature, and the reduction in saturation density caused by the wells. These have been largely overcome and the quantum well laser is likely to play an important part in many future optoelectronic systems.

Much interest in heterojunction transistors has been driven by a perceived weakness in the metal-semiconductor field effect transistor, or MESFET, which forms the basis of much GaAs electronics. This device relies on an n-doped GaAs channel, and, in order to increase the speed, this channel must be made as short as possible. Unfortunately, in addition to the reduction in mobility at high fields described in Section 1.2, the ionised impurities also begin to reduce the carrier mobility. The high electron mobility transistor (HEMT) [Drummond] addresses this problem by spatially separating the electron carrier supply region from the channel itself, which now need be only lightly doped. The carriers are provided from a highly doped GaAlAs layer which forms a heterojunction with the GaAs channel. The carriers from the doped layers fall into the potential well formed at the heterojunction interface, where are they free to move with very high electron velocities.

## 1.3 OPTICS AND ELECTRONICS

In this section it is shown how optics can be used to complement electronics, and that by the application of existing knowledge of the two technologies, a combination of the two should be able to exceed the limitations of either on its own.

### 1.3.1 Optics in Communications

In the comparison between Gallium Arsenide and silicon we mentioned some of the limitations found in electronic systems that were common to both

technologies, in particular the problems of interconnects. The optical properties of GaAs were also stressed, with the semiconductor laser being a particularly successful example of their application. It would thus seem worth examining the possible contribution optics could make to applications that are presently performed by predominantly electronic systems. Already optics are commonplace in telecommunications systems, for example in the use of lasers and optical fibres for transmitting data over long distances. Due to its almost unlimited bandwidth fibre has become the obvious choice transmission medium. Vast amounts of data can be transmitted in this way with very low loss, and with the introduction of fibre amplifiers, data can now be transmitted intercontinentally without conversion back to the electronic domain. Such an amplifier may consist of an Erbium doped fibre having an optical amplification window of around 30nm near the 1550nm minimum attenuation wavelength of the fibre. A 30nm optical window may appear quite small, but it is equivalent to 4000GHz or 13 times the whole electromagnetic spectrum from dc to mm wavelengths. At a lower level, fibres, or other optical waveguides, are already being used in rack-to-rack and board-to-board interconnects. These give sharper pulse edges than electrical interconnects, for there is very little degradation per unit length along the optical fibre, whilst in electrical interconnects resistance causes a risetime degradation that increases as the square of the linelength. An example of a waveguide interconnect is the 60GHz board-board optical interconnect of [Cheng *et al*]. This used polymer optical buses with microprism couplers between the GRIN waveguide buses and the boards. The S/N ratio was 22dB for an interconnect distance of 55cm. An advantage of using the polymer waveguide is that it can be laid down on any type of substrate e.g. either silicon or GaAs. The prisms allow coupling over a much larger wavelength range than, say, holographic elements - approximately 250nm compared to a few nm. However, a disadvantage is the precise adjustment of angle relative to the waveguide to achieve coupling. This is typical of the problems fibre or waveguide based systems have, and it is difficult to see how they could be more highly integrated - i.e. at the chip level. Alignment becomes increasingly tricky and the fibres themselves are too bulky, free space optics may therefore be able to contribute in this area. Nevertheless, the huge potential of fibres - or free space optical pathways - has yet to be fully tapped, for there exists no technology to switch or process the amount of data that could in principle be transmitted. Although currently optical communications are principally point-point, with a unidirectional signal from the transmitter to the receiver,

and at a single wavelength, this need not be true in the future. For example, by wavelength multiplexing (WDM) the amount of data presently transmitted could be increased by a factor of 1000 or more. Such a system could be unidirectional or bidirectional [Bornholdt *et al*] [Koch and Koren]. In the latter case different wavelengths, or groups of wavelengths, are used for the two directions. Bidirectional systems employing more than one wavelength offer the advantage of only requiring a single fibre whilst still providing low crosstalk between the receiver and transmitter. An optical grating would provide separation of the signals.

Coherent techniques used in radio communications could also be applied, but with a huge increase in bandwidth [Koch and Koren]. The system limitations then become not the fibre but the electronic network nodes and switches, it is thus worth considering whether optics can contribute to this area too.

### 1.3.2 *Properties of Optics*

In addition to the ability to transmit multiple wavelengths, or channels, simultaneously, light beams can also cross each other without the input and output beams being altered. This is in obvious contrast to the case of shorting two electrical conductors together. The result is to alleviate the restrictions on interconnect paths that are such a problem in integrated circuits. Furthermore, it opens up the possibility of new architectures, such as 2-d processing for which optics is particularly suitable, in applications such as image mapping and processing. Using the fact that light paths can crossover each other, their paths could be designed to be of equal length and thus eliminate clock-skew. This is helped by the theory which states that all paths in an optical imaging system (for example, in the simplest case, a single lens) have identical time delay or "timeskew". This feature could be used to provide an optical pulse for "clocking" purposes.

To utilize the instantaneous, wideband, 2-d input and output communications pathway conferred by optics would require imaging optics between the receiving and transmitting arrays. These could be provided by conventional lenses or, alternatively, holograms could be designed to perform the same function. There is however a limit to the number of interconnection patterns possible with such optics, and stray light could well be a problem. This would suggest a limit to the processing, rather than interconnect, role

optics could perform. Another limitation in terms of the potential for optical processing is that "light", or more accurately its wavelength, is actually quite large. This limits its potential for very high levels of integration even when compared to the best present day, sub-micron, electronic logic devices. Already  $0.8\mu\text{m}$  CMOS electronics are commonplace, while feature sizes of  $0.2\mu\text{m}$  are not far from the production process. Compare this to a focused optical beam which has a Gaussian spot of diameter  $2w$  at its  $1/e$  points, where  $w = \lambda/0.\pi.n$  at far-field. If  $\lambda/2$  optics are used to provide high quality images then  $\theta$  is limited to  $0.25\text{rad}$  [Midwinter 91]. Assuming the wavelength is  $0.85\mu\text{m}$  and  $n$  is 1 (for free space) then  $w = 1.1\mu\text{m}$ , and the  $1/e$  spot size is  $2.2\mu\text{m}$ , already large compared to the feature size of conventional electronics. Moreover, if this spot was incident upon a receiver, it would be wise to double this to  $4.4\mu\text{m}$  to ensure all the light was collected. Errors due to aberrations, alignment errors, and thermal changes may well require up to an order of magnitude increase in size to be certain of capturing the incident light, and to ensure that the light does not fall upon a neighbouring device. We are therefore presented with a much larger total device size than we are familiar with for individual electronic devices, although it remains small when compared with the conventional input and output bond pads currently employed for connecting chips. Clearly the extremely high levels of integration so common to us in electronics would be impossible in optics, thus if optics are to be of benefit it will not be by replicating electronic systems, but rather by complementing them or by bringing new functionality, perhaps by special architectures.

Essentially optics provide a transmission medium which, at the distances involved in electronic systems, is without loss, crosstalk, distortion and is speed independent. Optics also provide protection against electromagnetic interference, and isolation between different parts of the circuit. A feature that is already found to be useful in simple opto-isolators, stopping the load on one part of a circuit affecting the operation of another.

By comparison, electrical interconnects at high speed suffer from increased losses, pulses are distorted and may be reflected, and crosstalk and clock-skew become problems. At high speed the energy required to transmit data also increases, as the tracks have to be charged and discharged, which in itself requires the further complication of line drivers. An example of the methods one could use to alleviate these problems using conventional techniques is the Thermal Conduction Module [Arjavalingam & Rubin]. This provides interconnections for 100 chips, with 96 connections/chip, in a 90mm

square, 5.5mm thick device. Sixteen wiring layers are required, sandwiched by ceramic laminates, with a wiring density of 2/mm/layer. The module also provides fan-out, power supply distribution, and impedance and coupling control. The intention in such a design is to locate the chips close together, reducing the interconnect lines and propagation delay times. Although the multilayer wiring structure is unusual the interconnects themselves are conventional, giving a propagation delay of 10pS/mm and a risetime of  $\approx$ 1nS. An alternative interconnect is high speed cable which, although too bulky at the required levels of integration, may be used between modules or cards. Typical performance would be a delay of 3.8pS/mm and a risetime of  $\approx$ 200pS. Note that the delay is actually less than that for optical fibre having a refractive index of  $\approx$ 1.5 which would result in a 5.0pS/mm delay, although with negligible rise time. The benefits of optics are not therefore related to the propagation delay itself. In fact comparable propagation delay can be achieved with electrical interconnects having linewidths of as little as 10 $\mu$ m, for instance copper microstrip insulated by a polymer having a low dielectric constant, such as polyimide, also has a propagation delay of 5pS/mm [Arjavalingam & Rubin].

Electrical reflections pose increasing problems as the demands on a system become more severe. These occur when the signal encounters a change in impedance or a discontinuity, for example signal line connected to cable, or the effect of nearby lines locally reducing the signal line's impedance. The discontinuities may be inductive or capacitive. The reflections themselves may be either positive or negative. If one succeeds in reducing the interconnect lengths by judicious redesign, it will as likely as not result in the problems of reflection becoming more severe due to the small delay. For example, consider a signal on a 50 $\Omega$  transmission line encountering a 1pF shunt discontinuity. If it is a 1V signal with a 1nS risetime the reflected signal will be  $\approx$ 25mV; with a risetime of 0.5nS this increases to 50mV. It can be seen that as the speeds increase reflections are likely to cause false switching. Coupled noise (unwanted signals from adjacent active interconnects) can also create similar problems. Compare this to the optical case in which light beams can cross each other without the outputs being affected.

Another form of noise that can cause problems is Delta-I noise. This is a voltage disturbance that occurs when numerous circuits switch simultaneously causing large changes in current, predominantly through the power distribution network. Because of the high currents required to drive transmission lines (20mA to drive a 1V signal in a 50 $\Omega$  line) the simultaneous

switching of many drivers can cause amps of current to change direction in a few nS. With package inductances of tenths of nH, hundreds of mV of noise are possible, which could well cause false switching. Optical paths would act as isolators reducing the likelihood of switching errors.

We have seen how electronic devices have not been able to reach their full potential because of the problems of interconnectivity, both in terms of architecture and purely electrical limitations. It has also been discussed how optics is a particularly suitable transmission medium. It would thus seem sensible to examine in more detail what benefits a system of complementary technologies may have, and how such a system could be constructed. There are a number of factors involved in the performance of a processing system - the speed of the gates or devices themselves, the number of such devices required for a particular function, and the connectivity or processing algorithm. The basic measure of performance will be the cycle time necessary to perform fundamental operations. The interconnections have been seen to alter the cycle time, by preventing the devices operating at their maximum potential.

Although optical components could perform some useful processing functions, for example wavelength multiplexing and demultiplexing by gratings, or the use of couplers and conventional optics in routing data, there is no known way of performing the complex logic functions that are so familiar in electronic systems with anything like the same efficiency. Using electronic logic, discrete gates having switching energies of 10fJ to 1pJ, and speeds in the nS to low pS range, are familiar. Optical switches are by comparison very energy consumptive. An alternative is the use of an optoelectronic device such as the Multiple Quantum Well modulator which, for a 10 $\mu$ m diameter device, would have a capacitance of  $\approx 0.01\text{pF}$ , giving at 3V  $Q=0.03\text{pC}$ . Assuming a responsivity of 1A/W, the device would require an optical input of 0.03pJ [Miller 87 & 89]. These devices will be discussed in more detail later on, the point to note here is that they require energies similar to electronic devices, because in essence their operation is electronic.

### 1.3.3 Energy Comparison of Electrical and Optical Interconnects

An interesting comparison has been made by [Hinton & Miller] with regard to the energy requirements of both electrical and optical interconnects

between electronic circuits. At the core of this comparison is the recognition of the essential duality of light. Its wave nature gives it the properties of an excellent transmission medium, and the ability to image and route two dimensionally. Conversely, its particle nature results in very efficient conversion between the optical and electronic domains. In fact, a single photon can optically excite and free an electron so that detection can fundamentally be with 100% efficiency. This has been termed Quantum Impedance Conversion, for reasons that are clearer when one compares the equivalent case for electrical transmission. Here the metal conductor appears as either a capacitance to be charged and discharged, with power consumption increasing with both modulation frequency and track length, or as a transmission line with a characteristic impedance. The first case requires that a wire or metal track be charged to the operating voltage every time a bit of data is transmitted, using total energy  $E=CV^2$ , or  $1/2CV^2$  for the energy stored in the charged capacitor, and the same amount for dissipation in the resistance during discharging. In a lossy conductor signal diffusion along its length results in delay, typically  $0.1\text{nS}/\text{cm}$ . To reduce time delay low impedance tracks are desirable, but the requirements of the electronic circuits dictate the use of low current, high impedance devices. Consequently, there exists an impedance mismatch between the tracks and the electronic devices. Note that even if a suitable superconductor existed capacitance would remain, the link looking like a stripline, and the connector would reflect unless matched. The use of an optical link would act like an impedance transformer, allowing very high impedance electronic devices to be used.

As an example Miller takes the charging of an electrical line of length 30cm to a voltage 1V. This would require approximately 20pJ, which is 1000 times greater than an electronic switch would require. On the other hand an optical path would not consume any measurable energy itself, although of course it is necessary to consider the whole interconnect, i.e. the additional requirements of the transmitter and the detector. In the case of the transmitter a low power light source is necessary. This could be either a low threshold microlaser which would operate as the transmitter itself, or an external laser could be used with a reflection modulator on the chip acting as the data transmitter. The detector could be a conventional *pin* diode or, as we shall see, a dual-purpose modulator that may operate as either transmitter or detector. The key issue is how much energy such an optoelectronic interconnect would use.

For a photodetector the minimum optical energy required to generate a voltage change  $V$  is [Miller 89]:-

$$E = \frac{\hbar\omega VC}{\beta e} \quad \text{Eqn. 1.1}$$

where  $\beta$  is the quantum efficiency,  $C$  is the capacitance,  $e$  is the electronic charge and  $\hbar\omega$  is the photon energy. Such a detector could operate at, or near, the quantum limit of one electron per incident photon. Similarly, an ideal emitter should emit one photon per excited electron. Lasers can operate very efficiently at high currents, but they first have to overcome the lasing threshold current. They must also be able to operate efficiently at low powers. This puts great demands on the laser design, and although microlasers are making great advances through the use of smaller gain volumes and higher reflectivities, it may be better to look to optical modulators to provide the required levels of integration, efficiency and energy consumption. These devices, which may also function as detectors, modulate an external light source by the absorption of photons. For each photon absorbed an electron flows, so we have exactly the same "quantum impedance conversion" as described for the photodiode. The energy required by such a device, if it was also in the form of a *pin* diode, would be the energy to charge the capacitance,  $CV^2$ ; and the energy associated with the photocurrent generated, which is proportional to the incoming optical power.

Given that a high enough level of integration can be achieved, and if the device size is small enough ( $10 \times 10\mu\text{m}$ ), then Miller calculates that the breakeven point at which an optical interconnect would require less energy than an electrical one would be for distances greater than  $\approx 1\text{mm}$ . Below this length metal tracks provide low energy, wide band communications; above it optical interconnects use less power and have a greater bandwidth. In both cases the *propagation* delay is similar, but signal diffusion proportional to the track length occurs for the electrical signal slowing the transmission rate. Because optics does away with the problem of impedance mismatch it would retain its advantage even if one had superconducting electrical lines. If the breakeven value can be achieved then the potential exists for use of optics on an intra-chip as well as an inter-chip level. At this level of integration one can imagine the optical interconnection of electronic islands, preferably utilising the advantages of two-dimensional architectures. The optical interconnects would release the full performance potential of electronic devices, whilst bringing greater flexibility in the ways they could be connected, the electronic

islands still performing the basic logic functions. Such a system is illustrated schematically in the figure below.

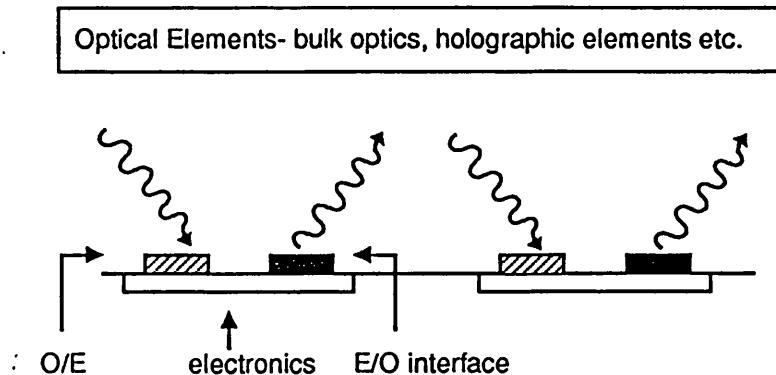

Figure 1.4 *Optically interconnected electronic islands.*

#### 1.3.4 Potential Devices for Use in Electronic Islands with Optical Interconnects

Whether such a system as proposed above would be practicable is to a large extent dependent on a means of providing both the high levels of integration required and an adequate level of optical performance. The GaAs on Silicon asymmetric Fabry-Perot quantum well modulator would be a particularly attractive device for such an application for the following reasons:-

- i) We have seen how silicon electronics are likely to remain the preferred choice in the majority of digital applications in the future;

- ii) Electronic systems are presently limited by the interconnect technology and not the fundamental electronic device performance;

- iii) GaAs based semiconductors have optical properties that silicon does not possess;

- iv) The asymmetric Fabry-Perot modulator is a most promising device to provide both the necessary optical performance and the low energy requirements.

- v) Growth of GaAs on Silicon modulators would satisfy the final requirement for high levels of integration, bringing optics into the intra- and inter-chip domains.

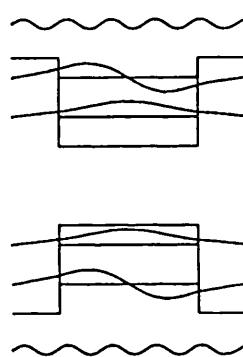

The basic properties of quantum wells and the operation of the asymmetric Fabry-Perot quantum well modulator (AFPM) are described in Chapter 2. It would be useful, however, to summarize the key points at this stage. For quantum wells the optical absorption spectrum shows a clear series of steps, resulting from the confinement of electrons and holes in GaAs "wells" by GaAlAs "barriers", with the layer thicknesses being  $\approx 100\text{\AA}$ . At the edges of the steps the absorption is enhanced by excitonic effects, which are observed at room temperature due to the confinement in the wells. Application of an electric field shifts the optical absorption edge, including the exciton absorption peaks, to longer wavelengths. As a result one can fabricate a semiconductor electroabsorption modulator. Furthermore, the performance of such a device can be enhanced by enclosing it in a Fabry-Perot resonator (see Chapter 2.4), resulting in a measured 20dB contrast ratio and a change in reflectivity of 43% at 9V [Whitehead *et al* 89(1)].

The electric field can be applied by locating the quantum wells in the intrinsic region of a *pin* diode which is then reverse biased. The energy required to modulate the light beam is  $1/2 CV^2$ , where  $C$  is the device capacitance and  $V$  the operating voltage. This results in energies of  $\text{fJ}/\mu\text{m}^2$  which are of the same order as electronic devices. Let us now consider the energies associated with the absorption process itself. The power dissipation in these absorptive modulators consists of *intrinsic* and *non-intrinsic* contributions [Woodward *et al*]. The first is simply the absorbed optical power. The second results from the work done in moving the photogenerated carriers through the applied electric field. This photocurrent is essentially a parasitic effect if one is interested only in optical absorption modulation. Minimizing the dissipation would result in a greater device packing density and maximize the allowed optical input power. For example, consider a MQW modulator operating at 5V absorbing a single photon. The intrinsic energy is approximately the band-gap energy ( $\approx 1.5\text{eV}$ ), while the non-intrinsic energy is 5eV, the work done as the electron traverses the field. The latter thus dominates the dissipation at moderate values of bias, while the two are comparable in value even at zero applied bias due to the built-in field. The only way to reduce the dissipation is to prevent the carriers moving under the influence of the applied field. Even when no external field is applied the built-in field due to the MQW *pin* structure results in an electron velocity of about  $10^7\text{cm/s}$  for a  $1\mu\text{m}$  intrinsic region. It thus takes an electron about 10pS to traverse the intrinsic region and another 1-100pS to escape from the quantum well. This compares to a carrier lifetime in good material of  $>1\text{nS}$  which,

being much larger, means that the carriers will always manage to traverse the gap. One could increase the carrier escape time by deepening the wells, but this results in a reduced saturation intensity and slows the potential operating speed of the device. The other option may therefore be to reduce the carrier lifetime - for example by controlled proton implantation; deep level impurities, e.g. O; or the introduction in the growth process of excess As. The same effect is sometimes observed with GaAs on Si due to the dislocations found in this material, although this is often perceived as a disadvantage due to the adverse effect it has on laser performance. Consequently there is a performance trade-off between carrier lifetimes and optical performance. The same trade-off is observed for proton implantation - for a dose of  $1 \times 10^{13} \text{ cm}^{-2}$  absorption modulation is maintained, with only a slight broadening of the exciton, beyond this the modulation performance is reduced [Woodward *et al*]. Of course proton implantation is a more flexible and selective method, and may be applied post-growth. Experimental results show that at 4V the quantum efficiency was  $\approx 1$  for unimplanted devices, but fell to 35% for a dose of  $1 \times 10^{13} \text{ cm}^{-2}$  [Woodward *et al*]. The quantum efficiency is reduced due to a reduction in the carrier lifetime, which in turn results from the introduction of a large number of non-radiative recombination centres by the proton implantation. As the bias is increased the quantum well escape time and the traverse time are reduced, thereby reducing the likelihood of non-radiative recombination and increasing the quantum efficiency. What was previously seen as a detrimental quality, i.e. a low quantum efficiency, is thus observed to have some potential advantages and it is useful to keep this in mind when assessing the photocurrent spectra of MQW structures.

The reduction in energy dissipation is accompanied by an improvement in saturation intensity, for fewer carriers build-up across the device, reducing space-charge effects. By connecting two modulators in series, one implanted, the other unimplanted, optical gain has also been demonstrated [Woodward *et al*] which may prove useful for fanout and improved drive capacity.

The successful integration of an asymmetric Fabry-Perot quantum well modulator device with silicon would therefore represent a substantial step towards meeting the requirements for an optoelectronic interconnect described above.

### 1.3.5 Packaging Considerations

The trade-off distance at which optical interconnects would be favourable is clearly dependent on the size of the devices, which in turn requires a great deal of attention to be paid to the design and fabrication of the complete system.

The fabrication of a complete package would require additional optical components such as lasers, mirrors, lenses and holographic elements. It is worth looking at some of the progress that has been made in these areas, particularly the integration of various devices. Much of the motivation for research has come from the needs of long distance optical communications, rather than the possibilities for the future discussed above. This, however, is not unexpected as a more immediate need is being addressed, and it does not necessarily affect the conclusions that can be drawn. Indeed, processing the huge amounts of data that could be transmitted by fibre would be a key requirement of future systems. Whichever approach is taken the greater complexity of systems will demand higher levels of integration for reasons of cost, robustness, and isolation/coupling. We will now discuss some of the devices that may be used in such systems.

### 1.3.6 Characteristics of Modulators vis-a-vis Lasers

One example is that of the integrated laser and optical modulator. In a directly modulated laser chirp occurs, a wavelength shift causing dispersive signal distortions. This occurs to a lesser extent in quantum well modulators, therefore a combination of a constant power laser modulated by a quantum well device may have advantages. However, the modulator itself may create some degree of phase modulation. This is because it makes use of electroabsorption - the change in optical absorption coefficient  $\alpha$  with electric field - which is related to the imaginary part of the index of refraction by:-

$$\alpha = \frac{4\pi n_{\text{imag}}}{\lambda} \quad \text{Eqn. 1.2}$$

The Kramers-Kroenig relationship links  $n_{\text{imag}}$  and  $n_{\text{real}}$ , therefore a change in  $\alpha$  results in an electrooptic effect. If  $\Delta n$  is large, phase modulation would occur in the modulator output, a similar effect to chirp in directly modulated lasers. Conversely, such an effect could be useful in constructing phase

modulators or couplers. In fact calculation of  $\Delta n$  by the Kramers-Kroenig relationship from MQW electroabsorption spectra show that the effect is relatively small in the region of high absorption changes, i.e. near the exciton peak, but larger at longer wavelength where the background absorption is smaller. Another parameter that concerns phase modulation is the linewidth enhancement factor,  $\alpha_{LEF}$ , given by:-

$$\alpha_{LEF} = \frac{\Delta n_{real}}{\Delta n_{imag}} \quad \text{Eqn. 1.3}$$

Which would be zero for a purely absorptive medium and infinite for a purely electrooptic one. Measured values have been reported as equal to 1 for MQW modulators, and 3-6 for directly modulated lasers [Wood]. This indicates that the modulator will show less phase modulation.

Chirp may not be of great importance over short distances but the use of a separate, single laser with a number of modulators is attractive for other reasons. This is an important issue on which there is at present no common consensus, for some would argue that thousands of microlasers would be more suitable in an optoelectronic system than would the MQW modulators. The laser is a low impedance, current driven device, the source being shunted by the laser's contact and substrate resistance, perhaps  $3-10\Omega$ . In a simple approximation it is this resistance that gives the  $R$  in the frequency response  $1/2\pi RC$  [Wood]. On the other hand an MQW modulator is a high impedance, voltage driven device, and the  $R$  in the frequency response is that of the drive source, perhaps  $50\Omega$ . The effect of parasitic capacitances will thus in general be much less severe in the case of lasers. However, the capacitance itself may be less for modulators, because they can be more easily reduced in area (although the latest VCSEL microlasers may negate this advantage); and because they are operated in reverse bias. This effectively increases the "plate separation" in the parallel plate approximation of the device capacitance, due to the increased depletion width. A similar effect can be achieved by physically increasing the width of the intrinsic region, but this reduces the field and therefore involves a trade-off with increased operating voltage in order to maintain the same modulation performance.

The benefits of modulators are, however, significant. Firstly, integration of lasers on silicon is more difficult than modulators due to material problems discussed in Chapter 3. A laser of relatively high power could be mounted off-chip where its design need be less compromised. It could, for example, be a quantum well semiconductor laser operating well

above threshold, it would therefore be more efficient than thousands of microlasers on-chip, each with its own threshold current requirement. The off-chip laser could be of virtually any design or orientation, whilst those on-chip would need to be vertical cavity surface emitting lasers (VCSELs). The off-chip laser would also be operating at constant current, therefore without chirp, and would be able to dissipate heat away from the chip. Reliability would also be a major factor, a single off-chip laser operating at constant current is likely to be more reliable than thousands of microlasers operating at very high switching speeds. If a fault was to develop replacement may be possible with a single off-chip laser but would be impossible with integrated lasers.

Of interest to either approach may be the phase locking of two dimensional arrays of quantum well VCSELs, demonstrated in the InGaAs/GaAs system by [Orenstein *et al*]. A 27x27 array was fabricated by patterning the reflectivity of the laser back mirrors. This both defines the array elements and allows interelement coupling. This coupling phase-locks the lasers into a single coherent spatial mode, useful as a high brightness source or in beam steering applications. This may allow some degree of reconfigurability to the optics. The devices are similar in construction to the AFPM, having a quantum well region sandwiched between two epitaxially grown Bragg mirrors. The lower one containing 20 GaAs/AlAs layers, and the top reflector 12 periods plus the patterned metal layer.

An alternative approach to the AFPM, which uses absorption modulation, is to consider phase modulation in a MQW, this may also be useful in beam steering applications. The conventional approach is to operate well away from the band-gap, on the long wavelength side, so as to reduce absorption. Then the change in refractive index, linked to the change in absorption by the Kramers-Kroenig relationship, changes the path length and thus the phase of the optical beam. However, because one operates at a region of low absorption the changes in refractive index tend to be weak, this usually requires the use of waveguide geometries in order to obtain adequate modulation. A novel approach is to use the vertical geometry of an AFPM [Pezeshki *et al*]. The equation governing the total reflectivity of the AFPM at resonance is given by:-

$$R_T = \left[ \frac{\left( \sqrt{R_f} - \sqrt{R_b} \right)}{\left( 1 - \sqrt{R_f R_b} \right)} \right]^2 \quad \text{Eqn. 1.4}$$

$$\begin{aligned} \text{where } R_b &= \text{effective back reflectivity} \\ &= R_b e^{-2\alpha l} \end{aligned}$$

The absorption is varied until  $R_T$  goes through a minimum equal to zero, at which point the front reflectivity equals the effective back reflectivity. On one side of the matching condition the loss due to absorption is too low to balance the equation, on the other too large. However, the reflected beams to the left and right of the matching condition differ in phase by  $180^\circ$ . This is because  $R_f$  and  $R_b$  are out of phase, and  $R_f$  dominates when the absorption is high and  $R_b$  dominates when the absorption is low. At a particular applied bias, and thus change in absorption, it is possible to change phase whilst maintaining a reflectivity of constant optical intensity. Large phase changes with low values of applied bias are thus possible. The disadvantage of this approach, using absorption changes to produce a phase change, is the insertion loss, although this will be comparable to AFPM absorption modulators. It is important to note that in a conventional AFPM there will also be some phase change, although as one is not *crossing* the matching point it will be greatly reduced. It has been estimated by [Pezeshki *et al*] to be  $\approx 20^\circ$ . This would still result in less chirp than waveguide devices.

We previously discussed how wavelength multiplexing could vastly increase the quantity of information transmitted. A step towards such a system is an integrated wavelength demultiplexer receiver, which has been demonstrated in GaInAsP/InP [Bornholdt *et al*]. This used two wavelengths routed by an integrated symmetric directional coupler. It may well be that the MQW could also be used as a wavelength demultiplexer since its responsivity is governed by the bias-dependent absorption spectra. One could then operate it as a voltage tuneable, wavelength dependent photodetector.

### 1.3.7 Integrated Waveguide Structures

While figure 1.4, above, shows free space optical interconnects, which would be in two dimensions, the use of optics could actually be extended into three dimensions by introducing optical waveguides in the plane of the electronic islands. These waveguides would be an almost direct optical analog to metal tracks. At present free-space optics and waveguided optics remain on the whole separate fields of research, this is, however, principally due to the

enormous amount of work still to be done in either area. In the future these technologies are likely to prove complementary, so it is worthwhile looking briefly at waveguide integrated optics and how they may relate to future optoelectronic systems.

The waveguide used may typically be a buried heterostructure in which the light is tightly confined by two semiconductors of different refractive index, and the dimensions may be  $\approx 0.2 \times 1 \mu\text{m}$  wide. The loss per cm is only a few percent per centimetre of propagation distance, and would therefore not be a problem within an integrated circuit. The waveguide can also be absorbing, in which case it is termed active, and may then be used to form a modulator or laser within the plane of the chip. The use of corrugated waveguide gratings (or Distributed Bragg Reflectors) as laser cavity resonators eliminates the need for cleaved facets, and has led to the distributed feedback laser. The same type of gratings may also be used as filters in multiple-wavelength systems. By injecting a current across the DBR one can create a change  $\Delta N$  which will change the reflectivity band.

An example of what can be achieved is the Multisection MQW-DBR laser [Koch and Koren] This has an output of 20-30mW, a minimum  $\Delta\lambda$  of 1-2MHz, and allows 1GHz tuning (80Å) at  $1.53 \mu\text{m}$ . Such a device offers the potential for multichannel, coherent networks with quantum limited detection sensitivity. These channels could be detected, filtered and then routed to the processing optoelectronics, all by waveguide technology.

Integrated waveguide devices are now also being made using silicon technology. An example is the narrow band Bragg reflection grating made with phosphorus doped silica on silicon waveguides, demonstrated by AT&T [Adar *et al*]. This functions as a narrow band optical filter which may have applications in multichannel optics, for example wavelength division, optical feedback, and laser stabilization. If we return to the concept of electronic islands, located on silicon motherboards, and interconnected by 2d optical arrays, we may want to consider expansion and interconnectivity with other processor arrays. At this level fibres would be an obvious choice, and the silicon-based reflectors and waveguides can be matched to these, with reflectivities of up to 60% giving bidirectional links. Thus communications signals could be fed directly into the motherboards, distributed by silica waveguides, and processed by 2d optoelectronic arrays.

### 1.3.8 Self Electrooptic Effect Devices

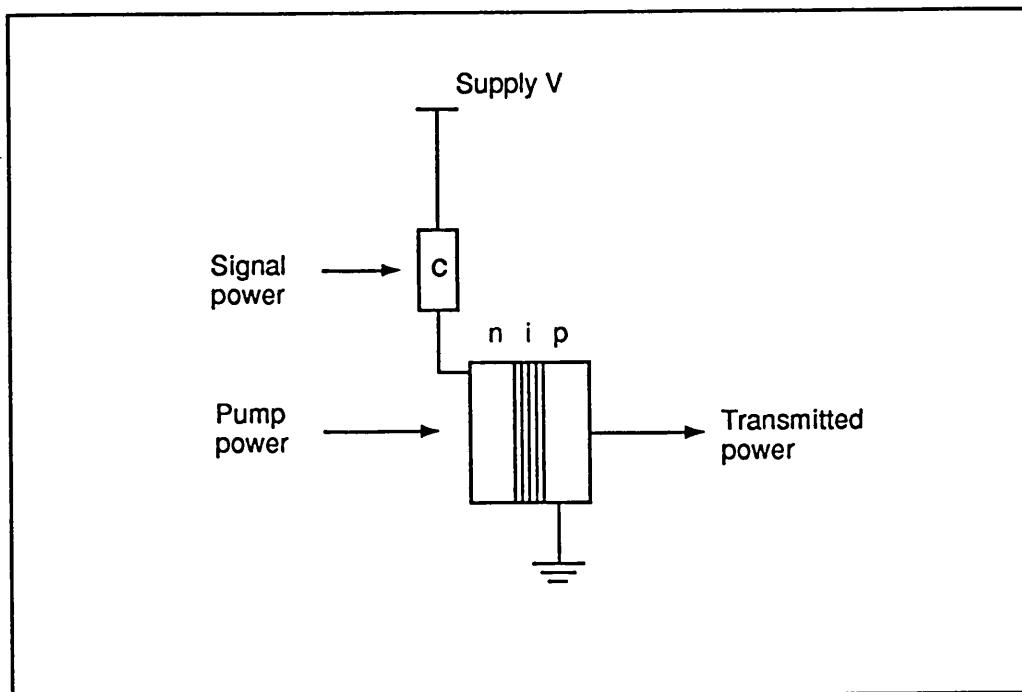

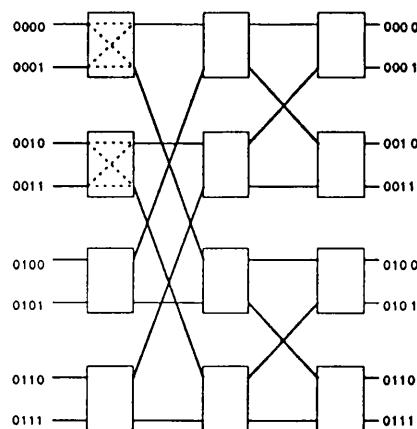

To take a step nearer the system in Fig 1.4, consisting of two dimensional electronic arrays with free space interconnecting optics, it would be useful to first research the properties of two dimensional arrays. One approach is to build a 2-d array having optical inputs and outputs only, i.e. to dispense with the electronic processing stages. This brings the fabrication to within the limits of present day technology, and also allows the properties of 2-d arrays to be better understood, so that the appropriate electronics can then be designed. Such a system has been constructed using SEEDs (Self Electro-optic Effect Devices). The simplest form of such devices is shown below.

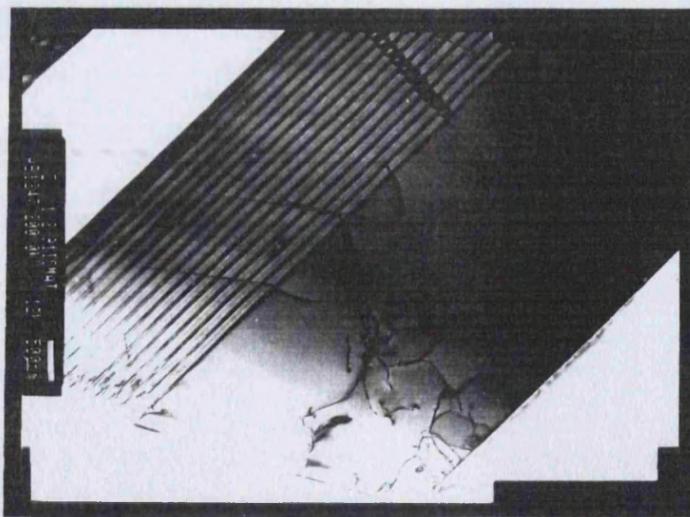

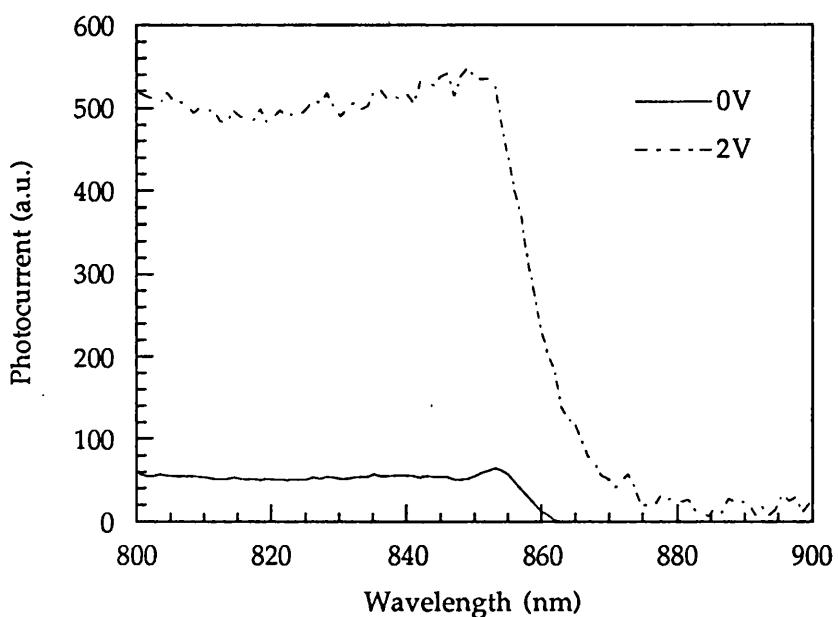

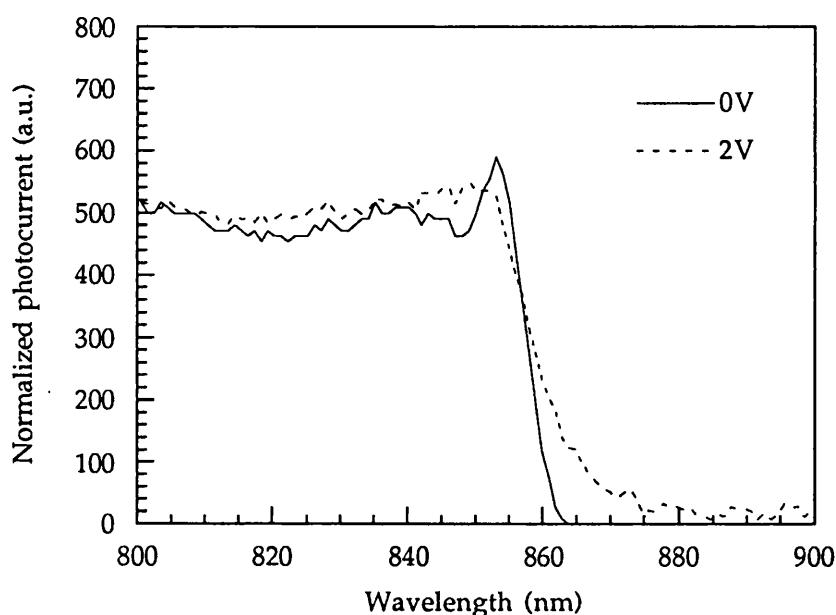

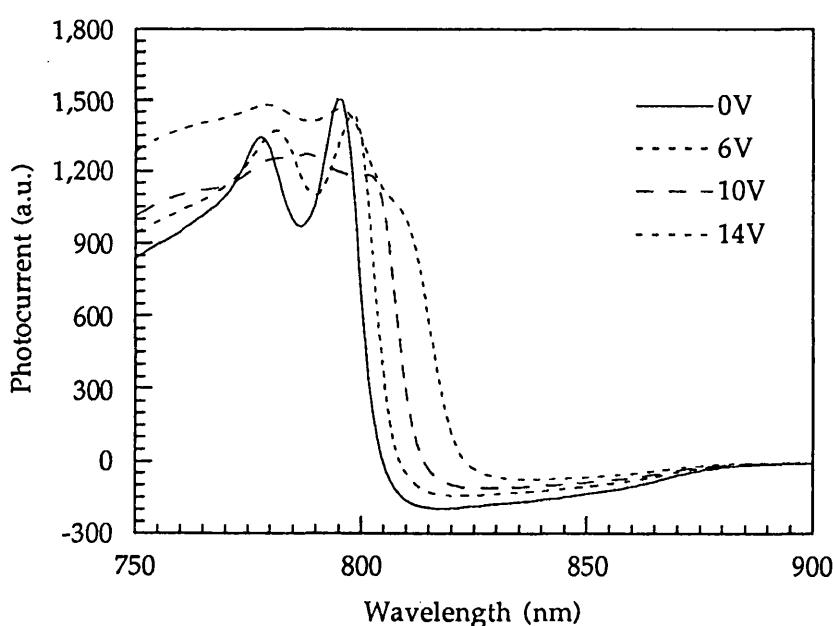

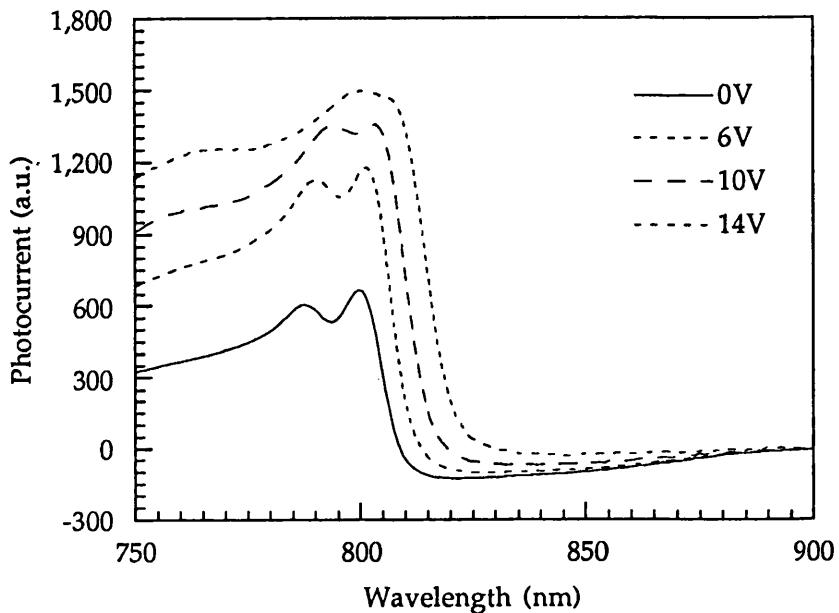

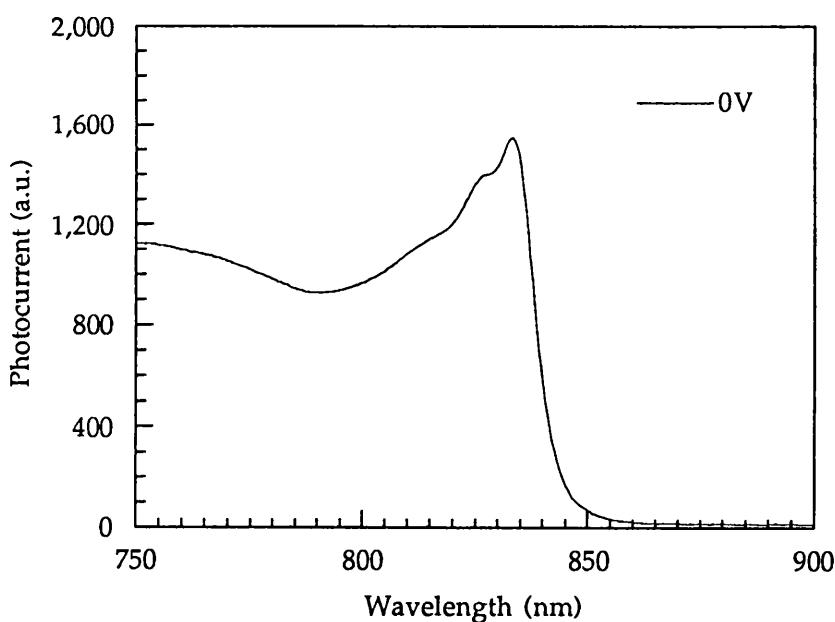

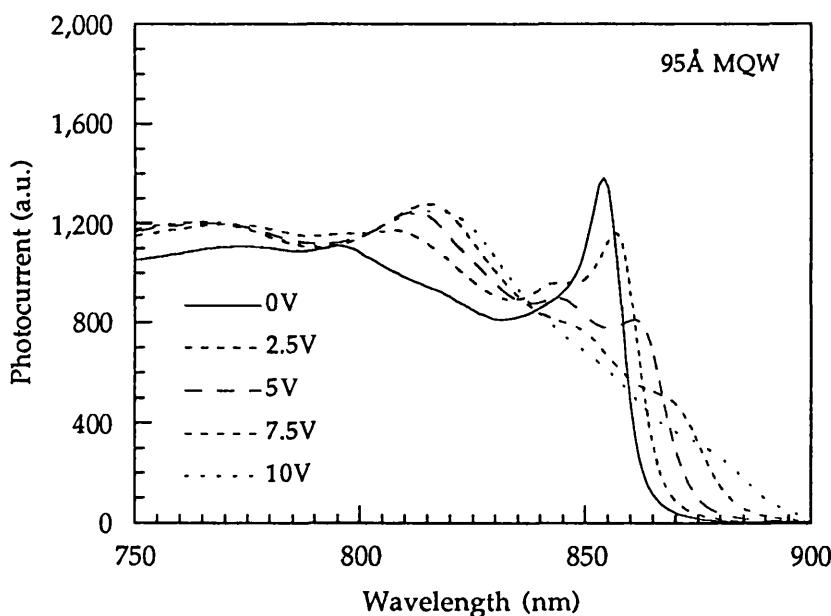

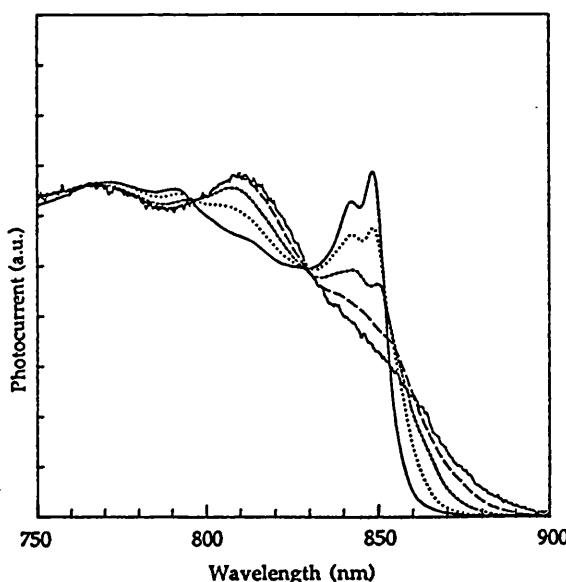

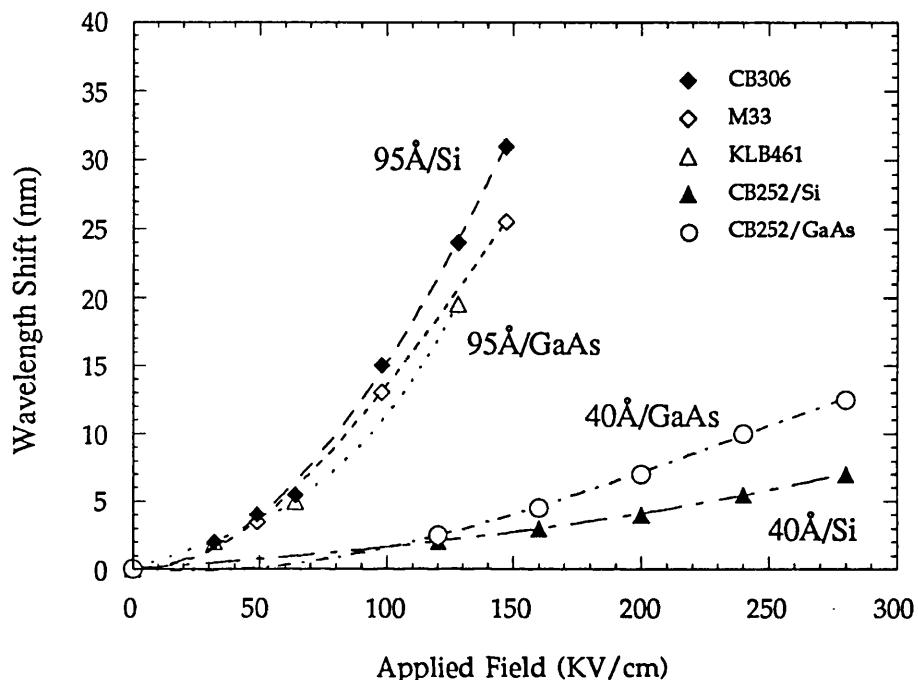

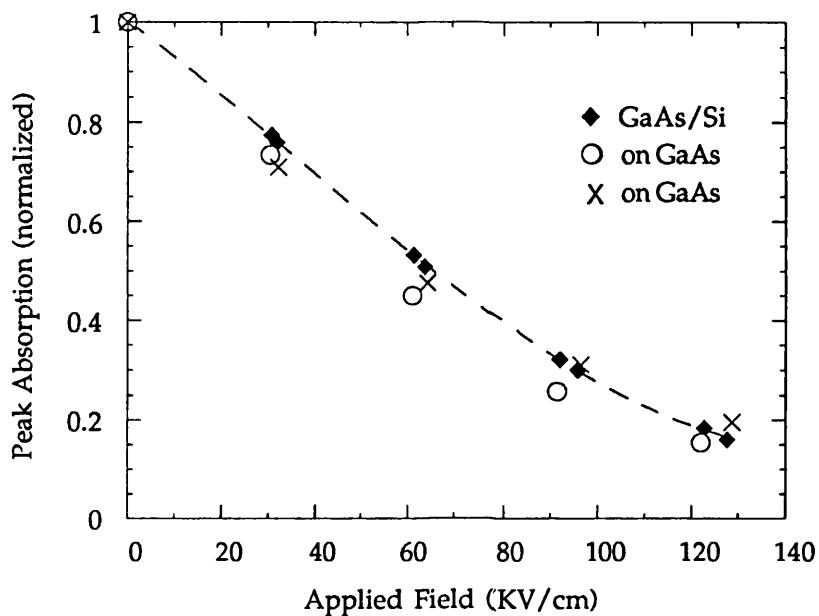

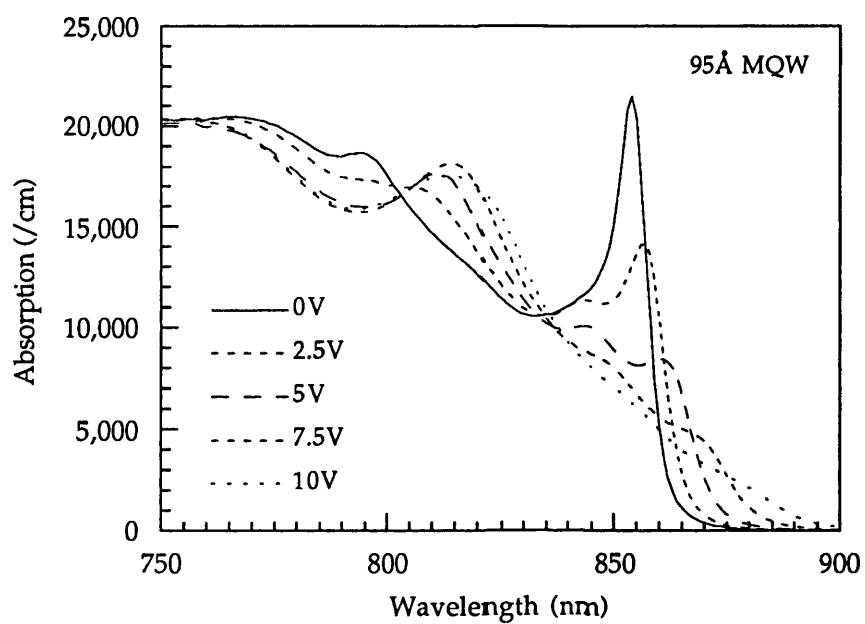

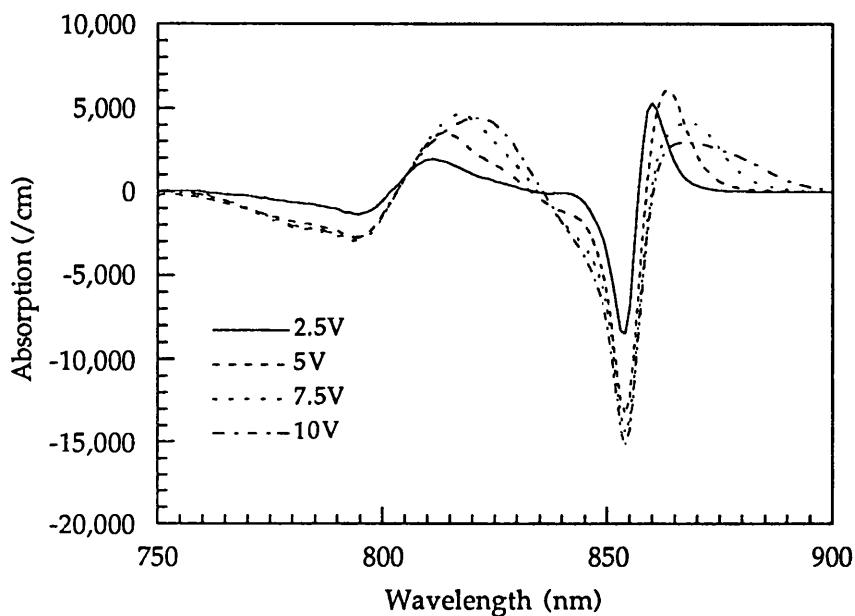

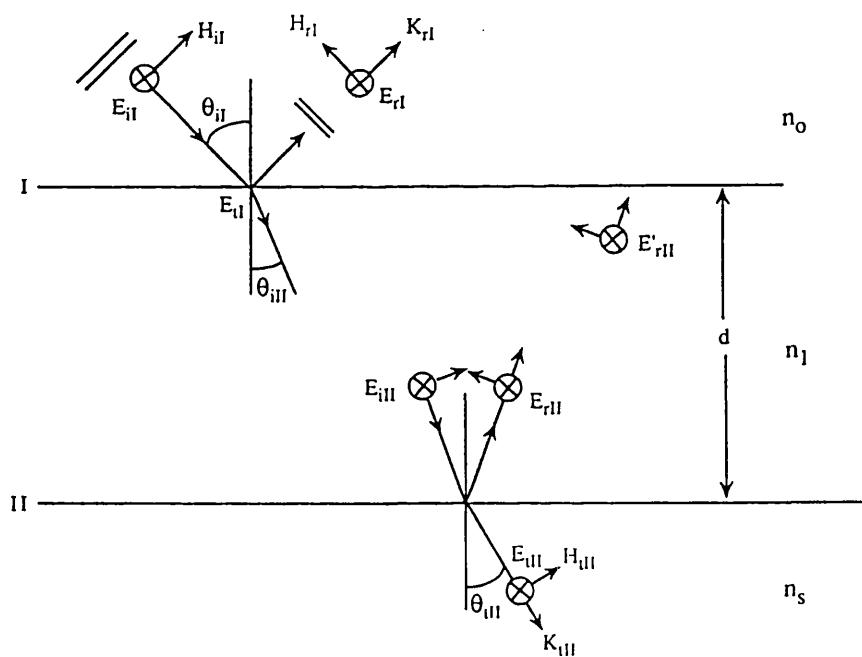

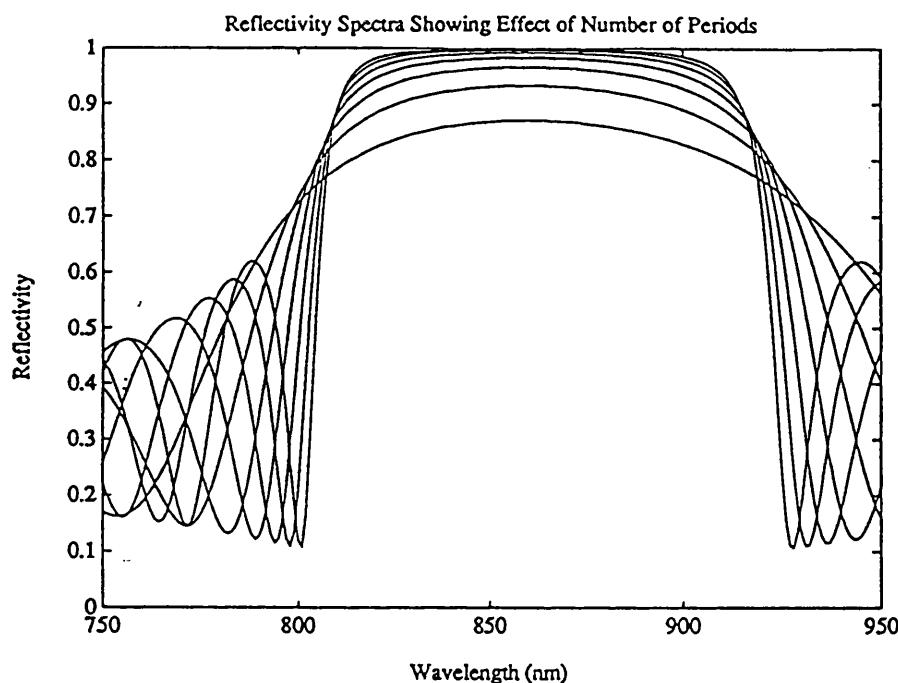

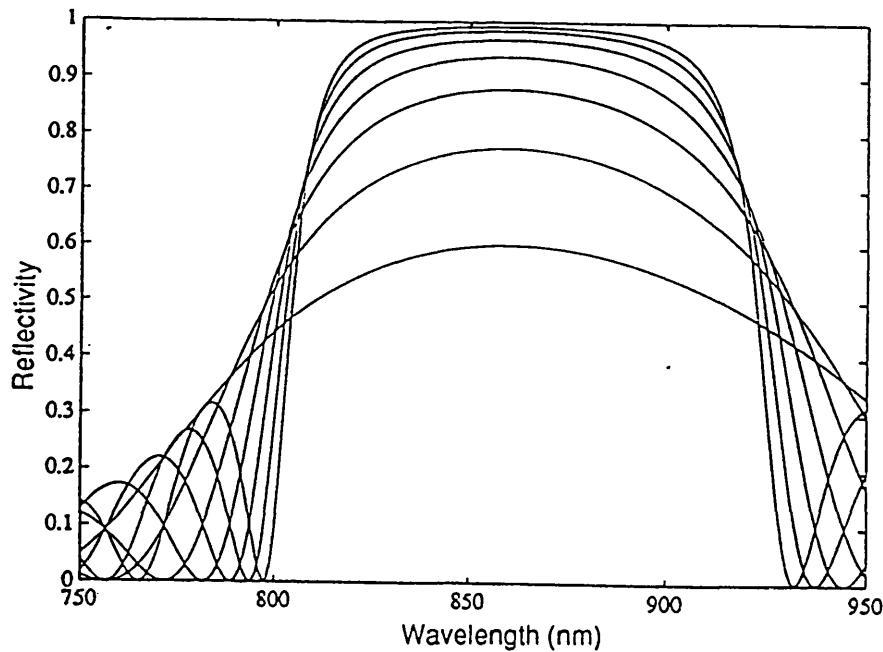

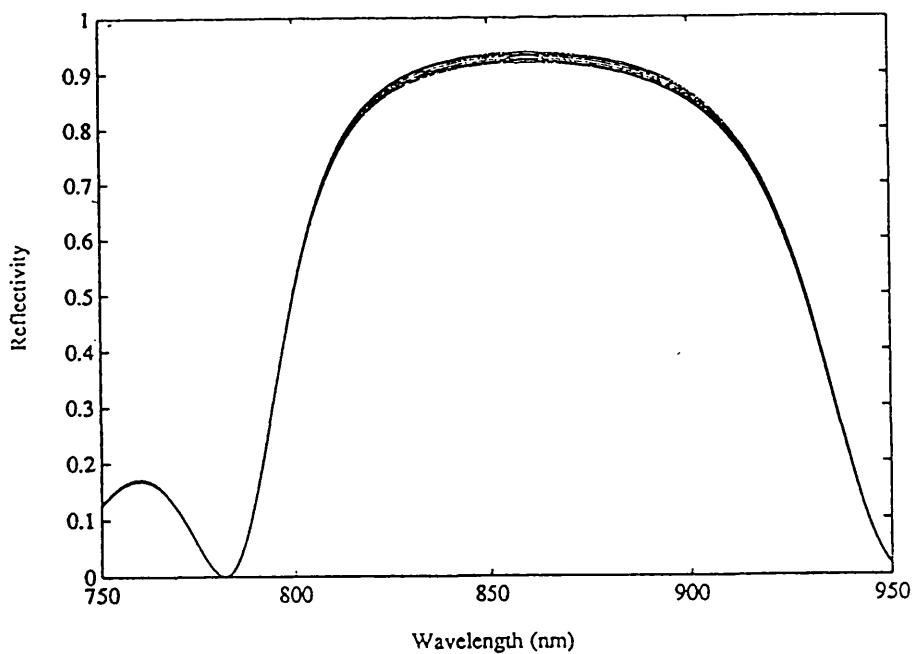

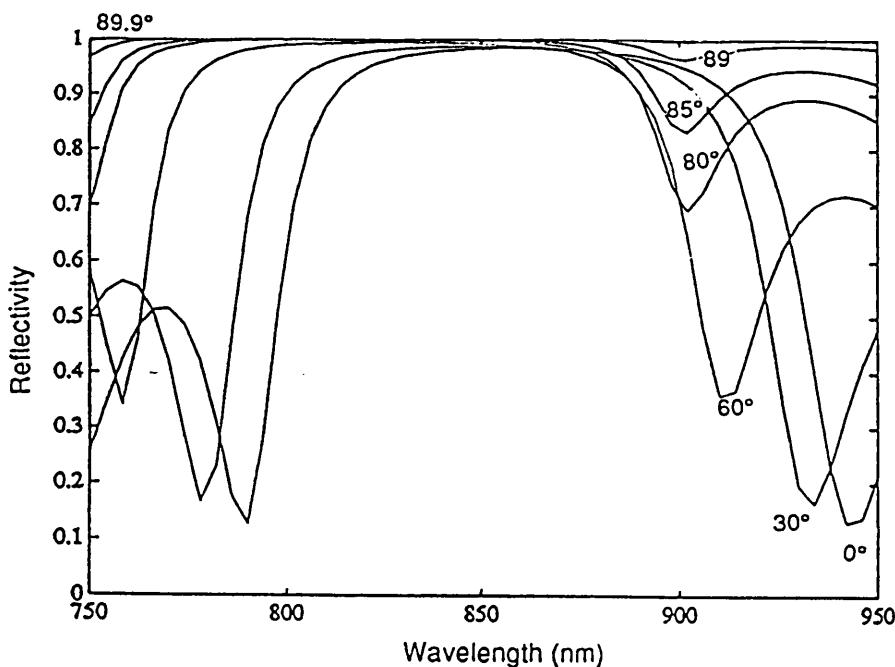

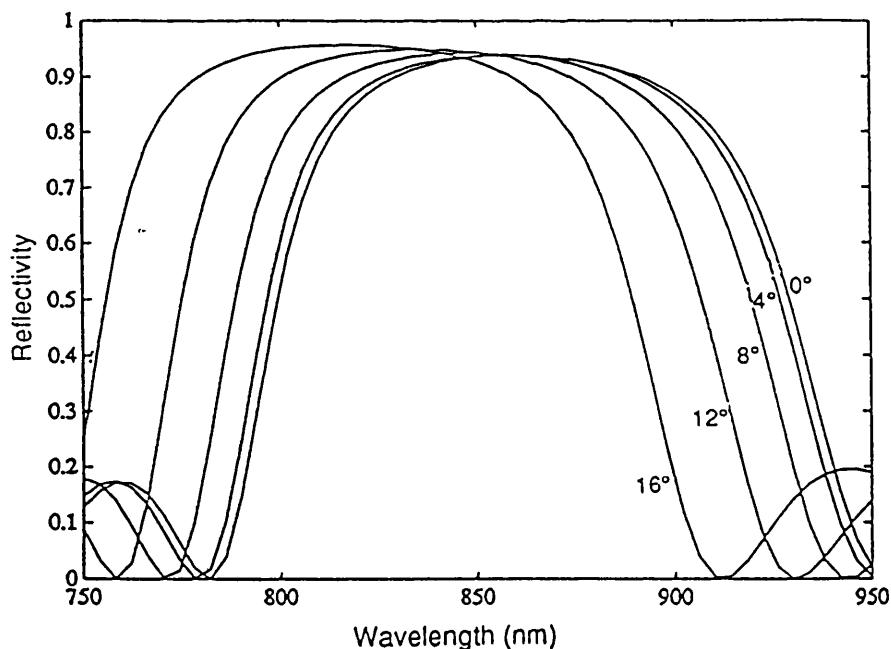

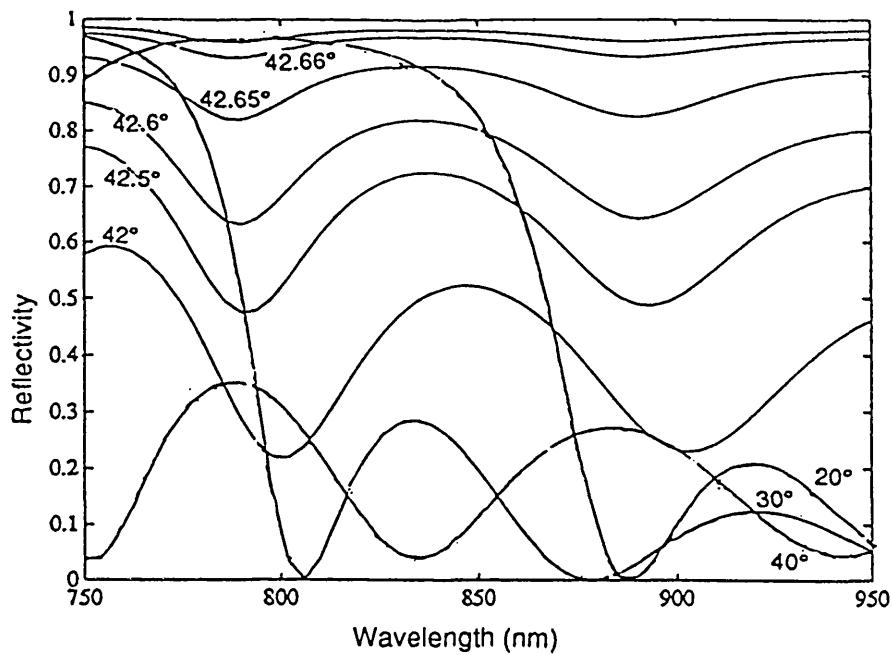

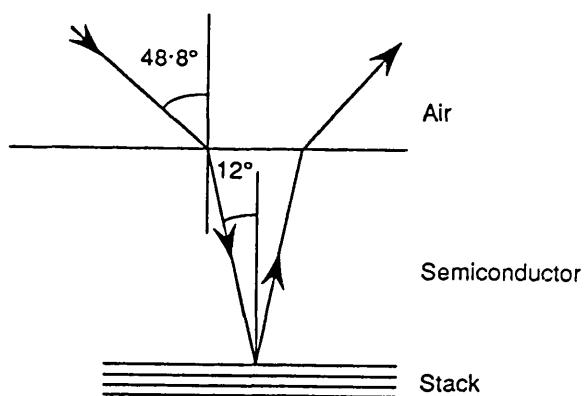

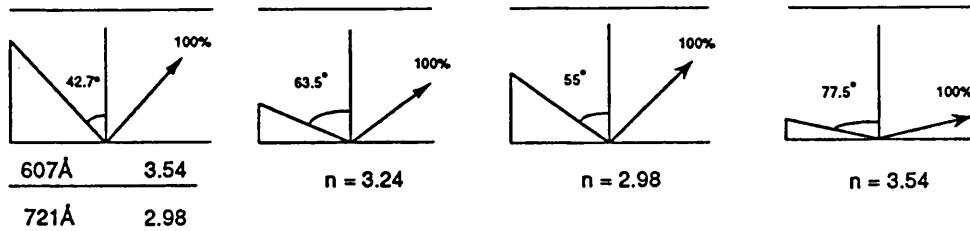

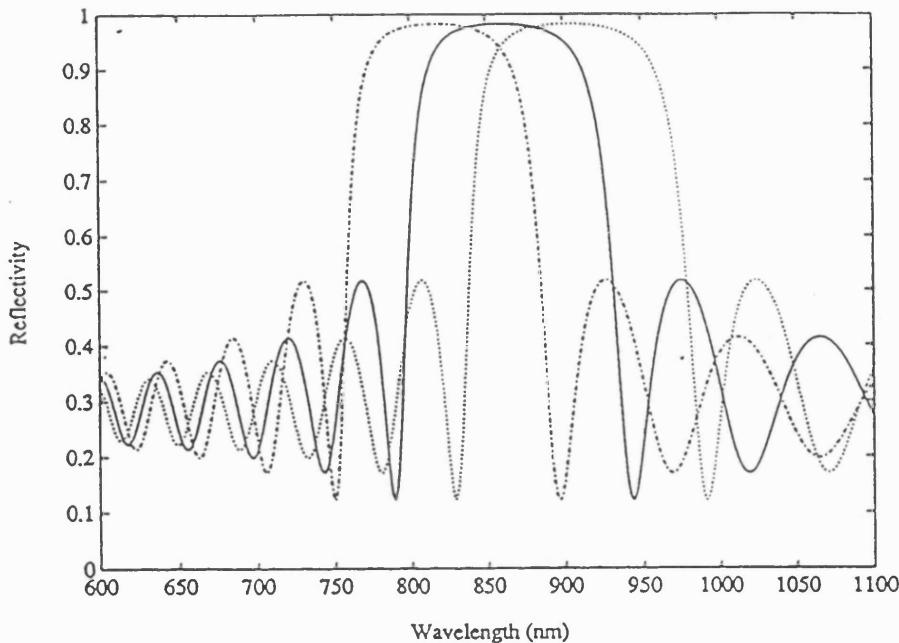

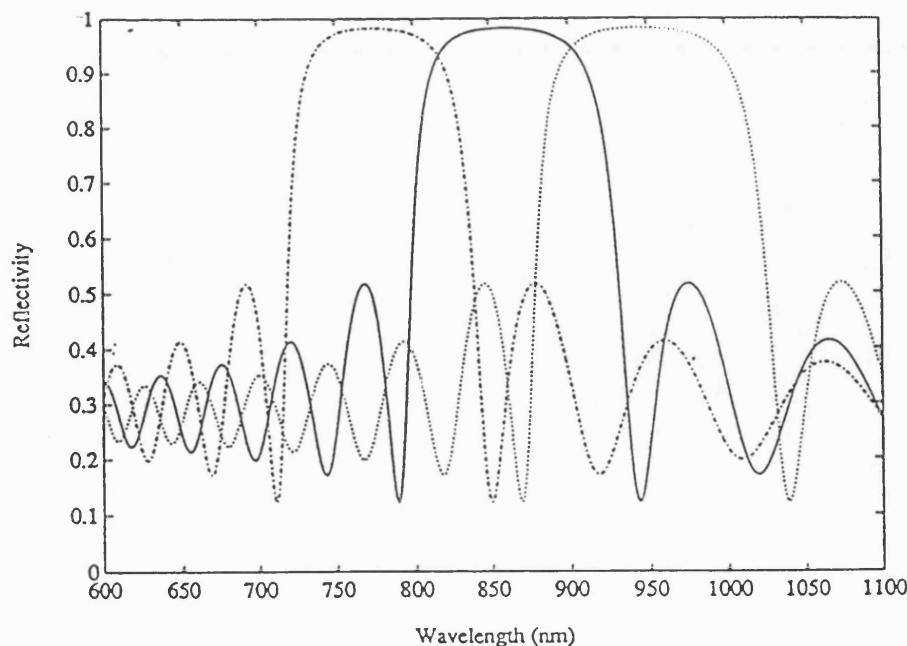

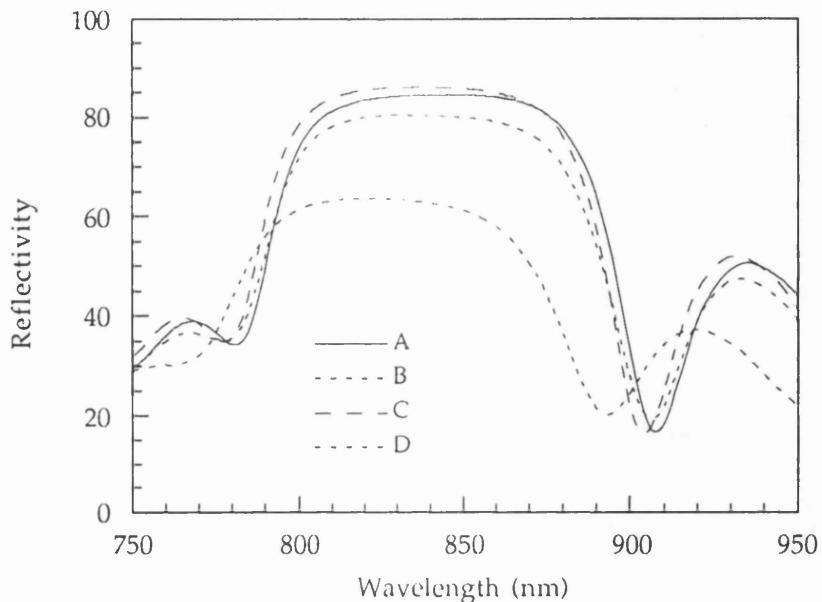

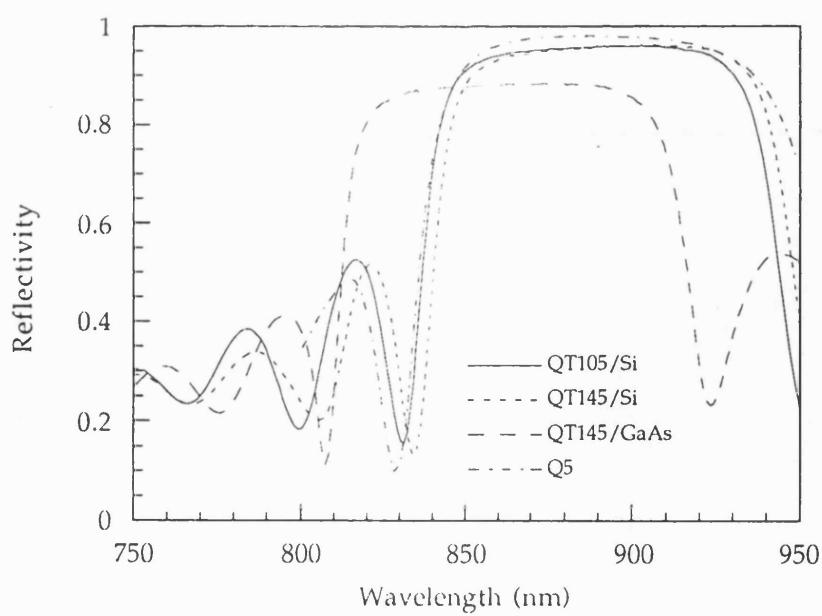

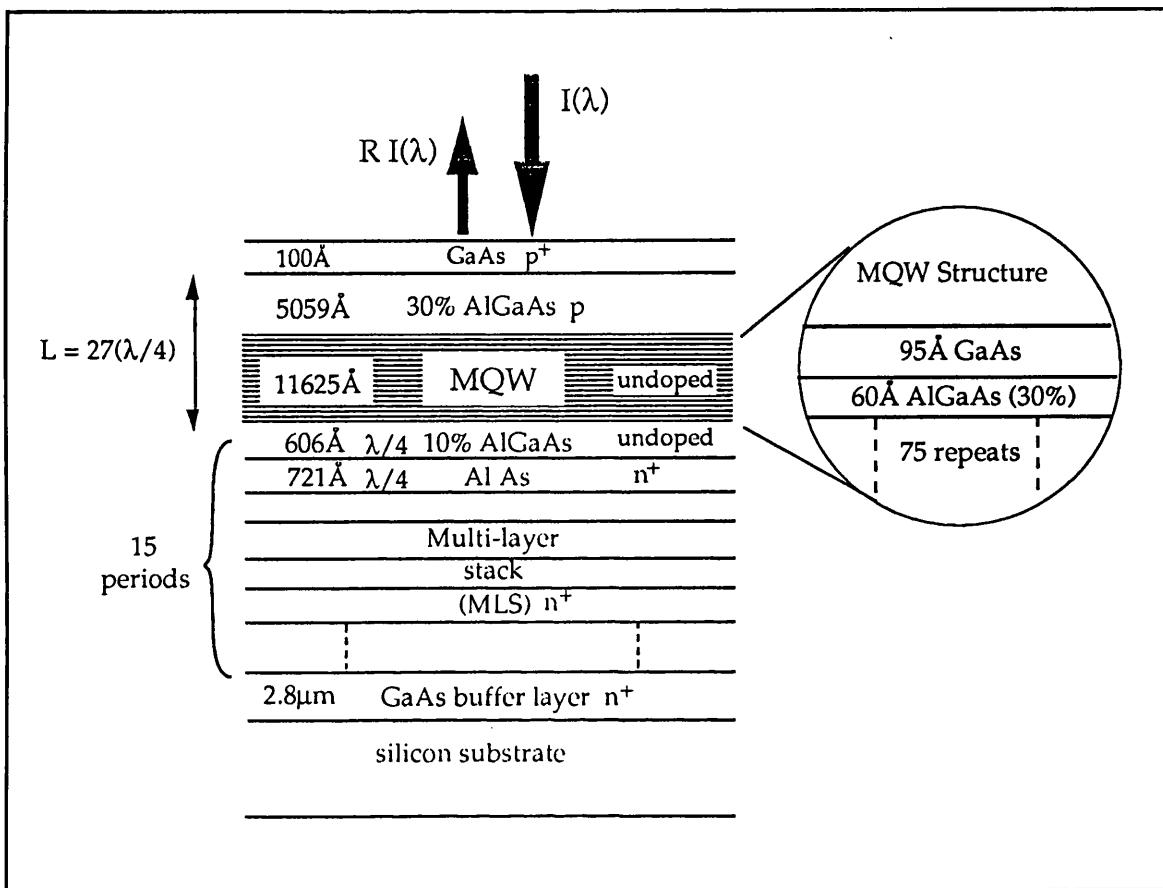

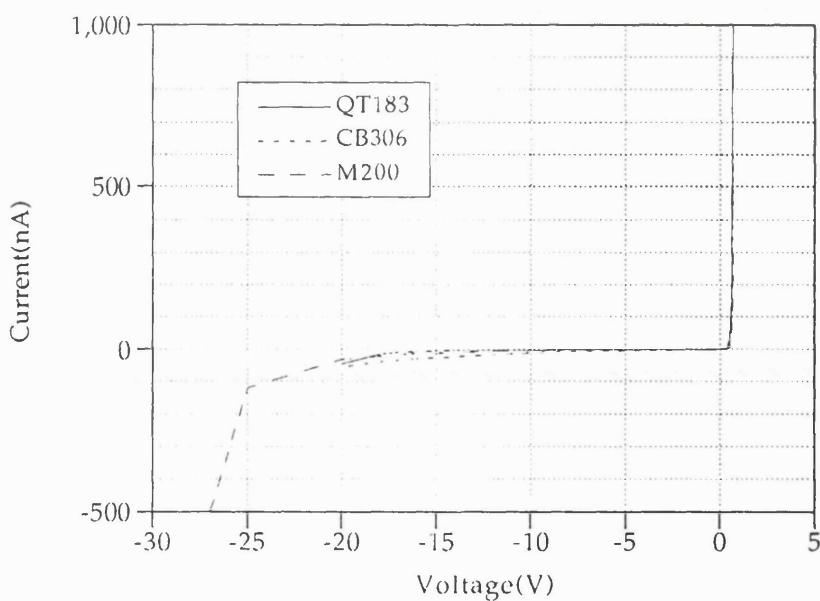

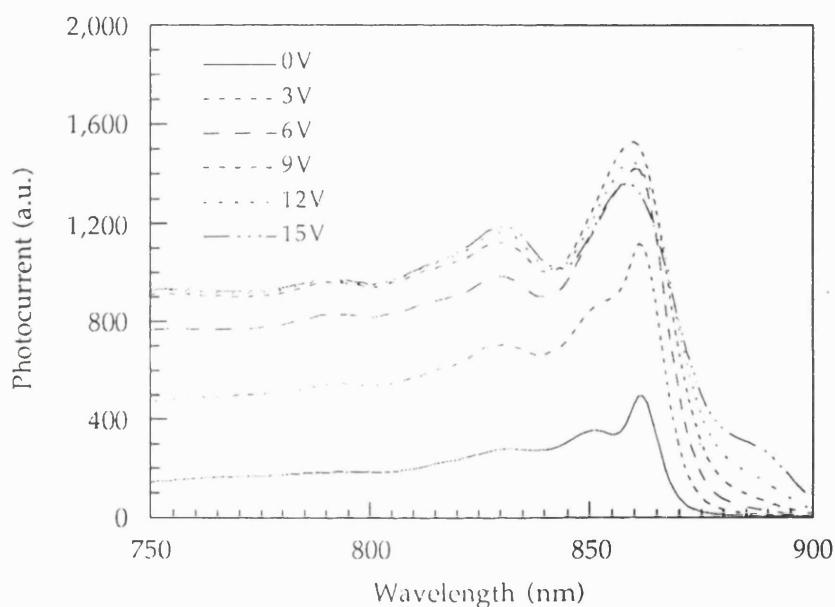

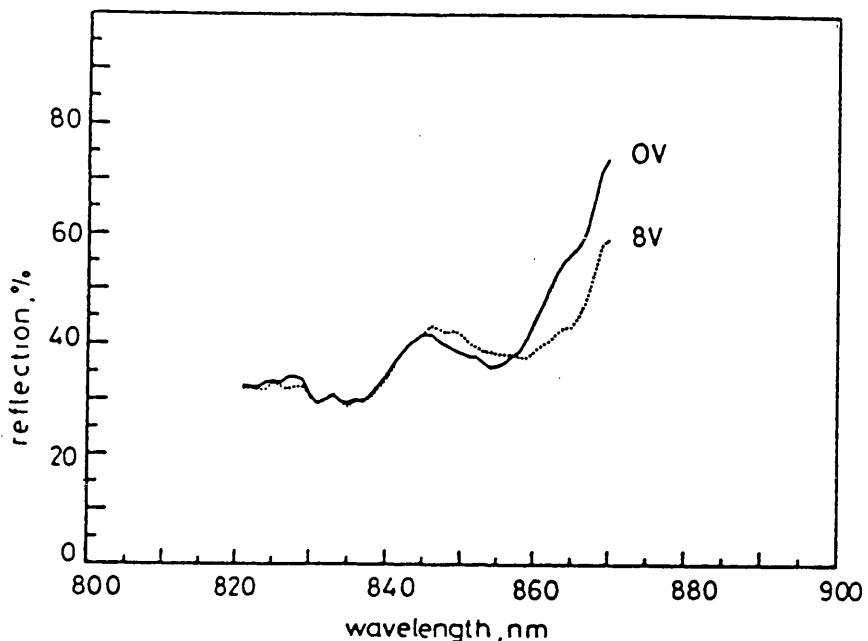

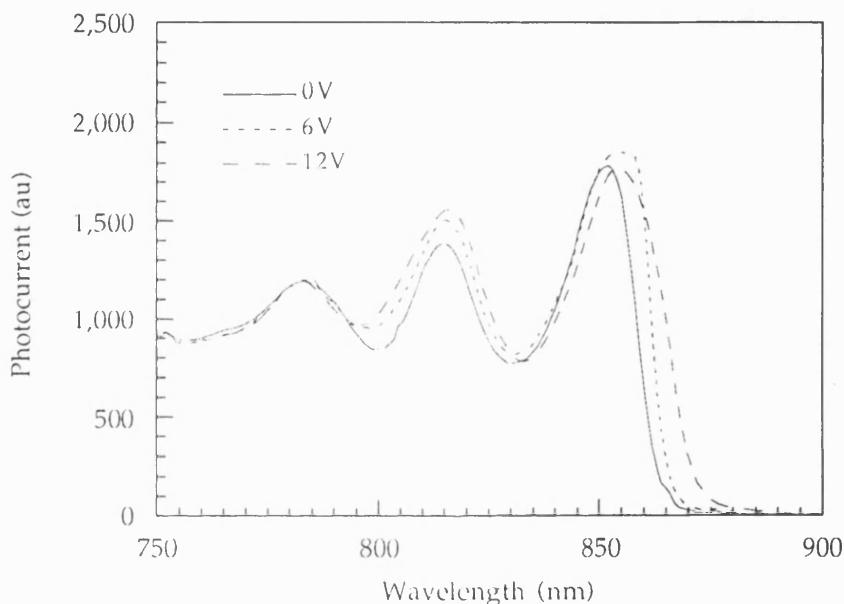

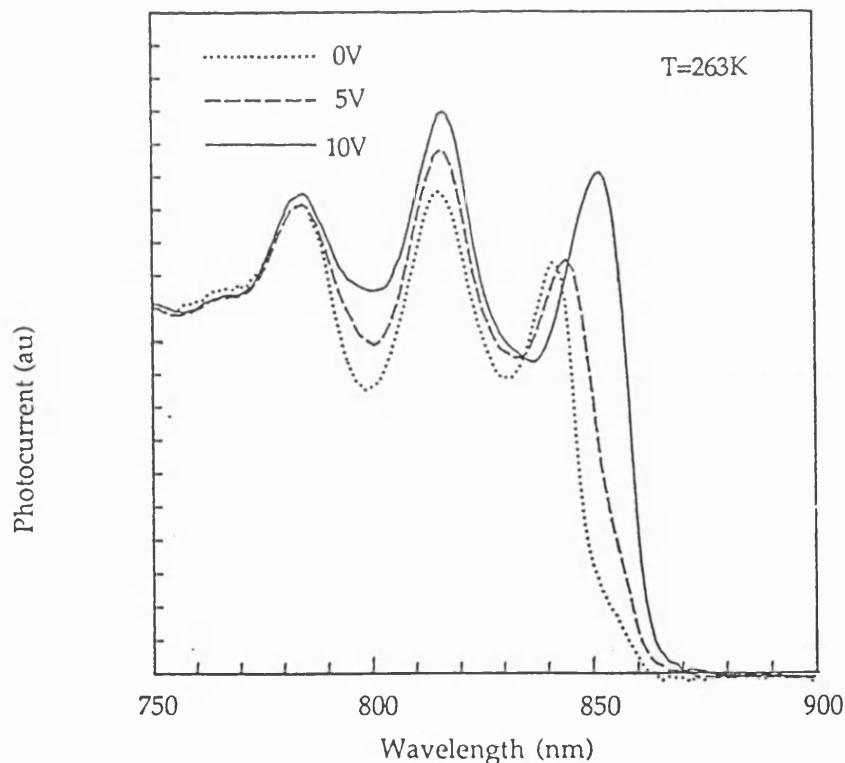

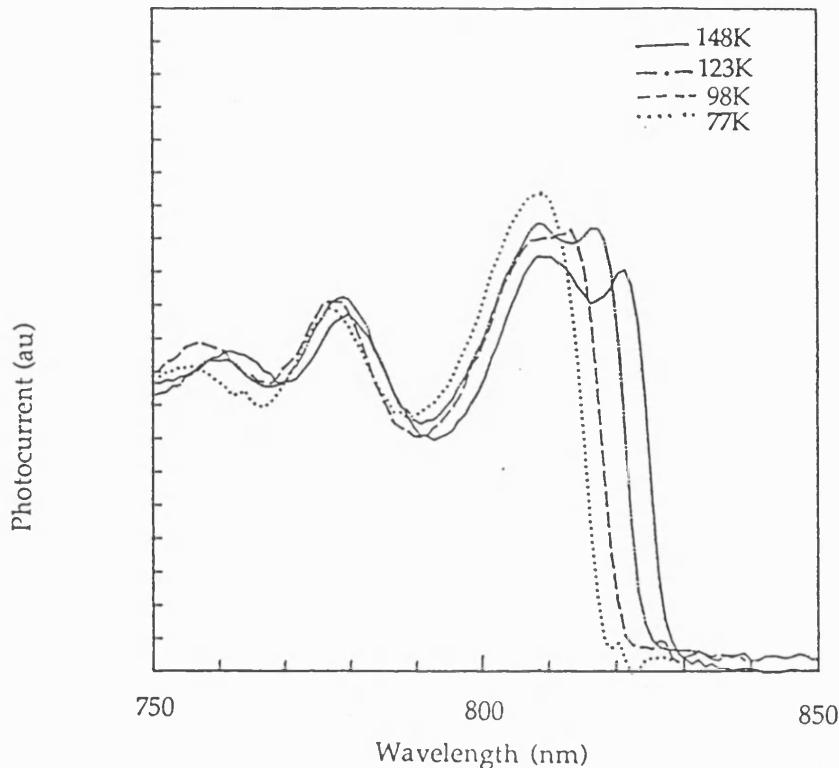

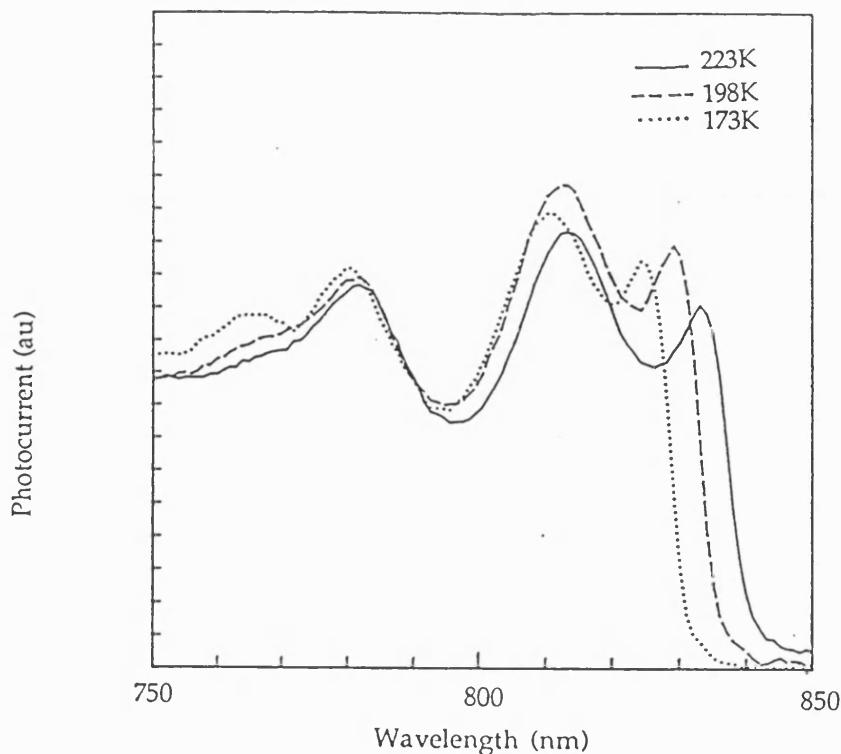

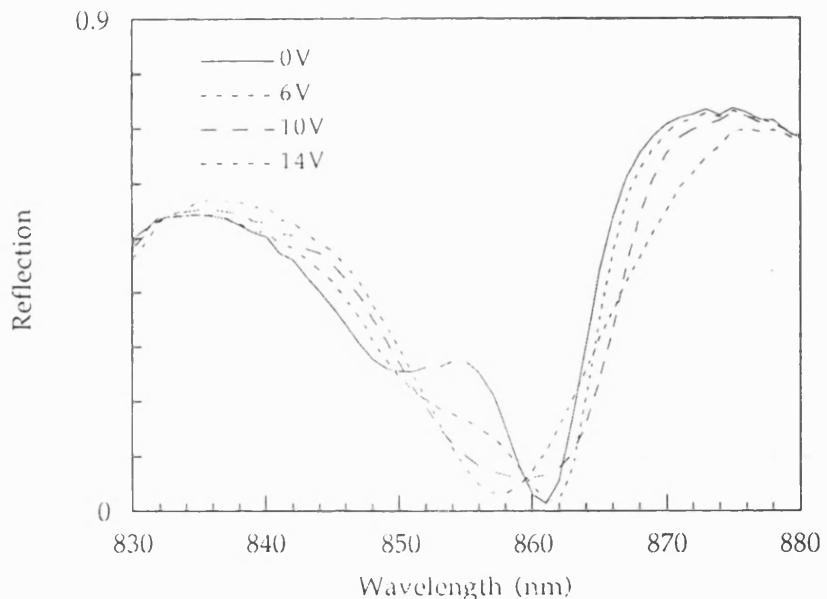

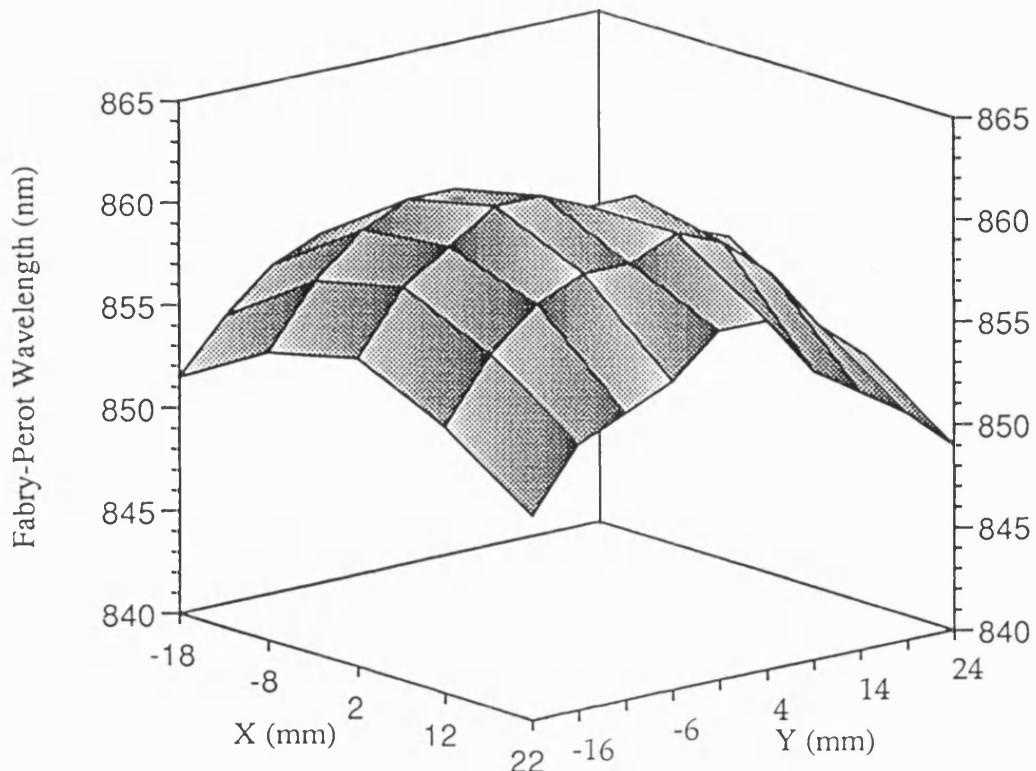

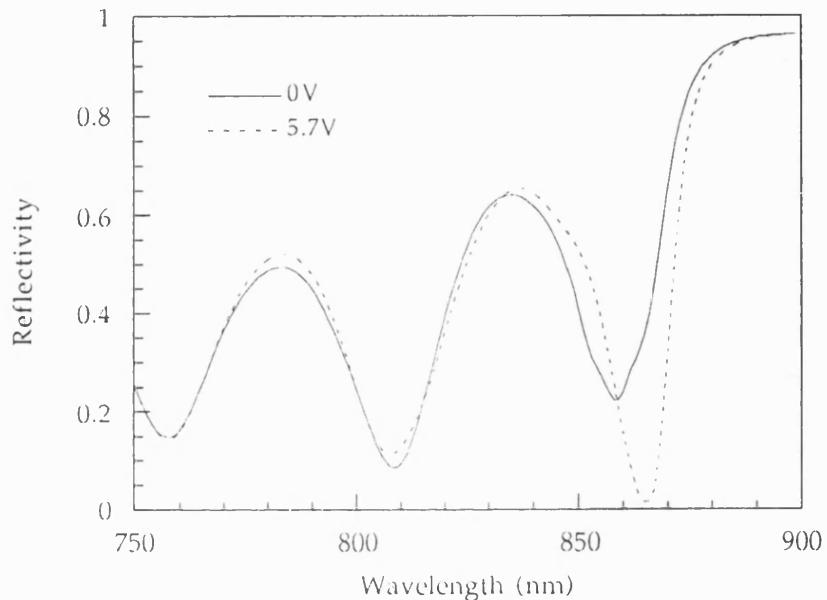

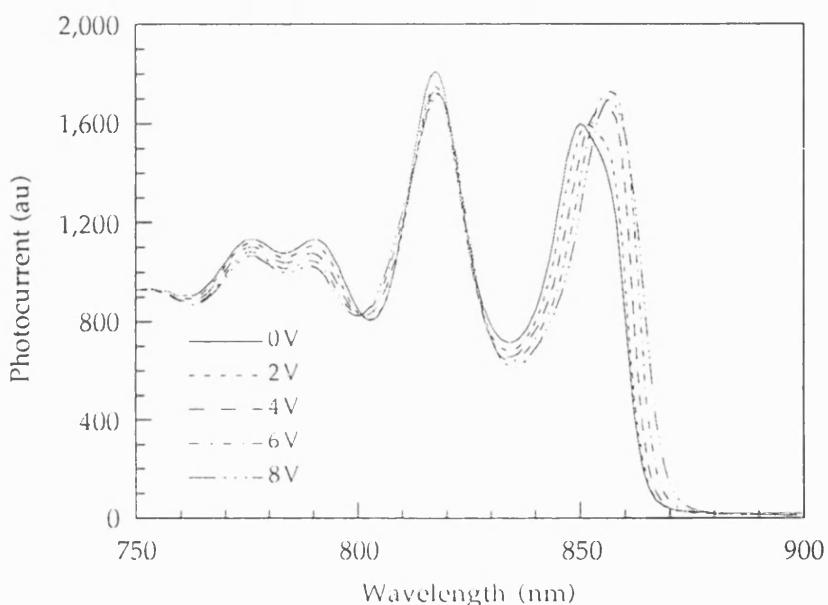

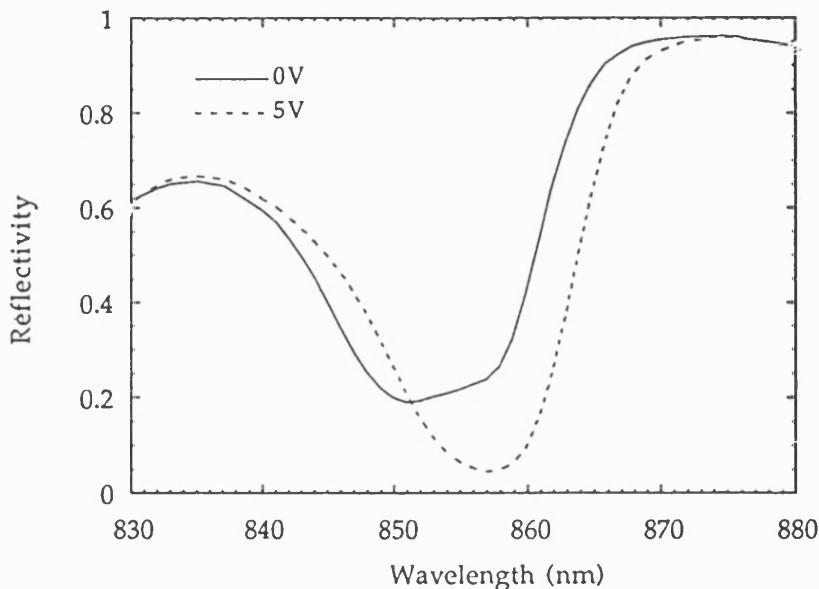

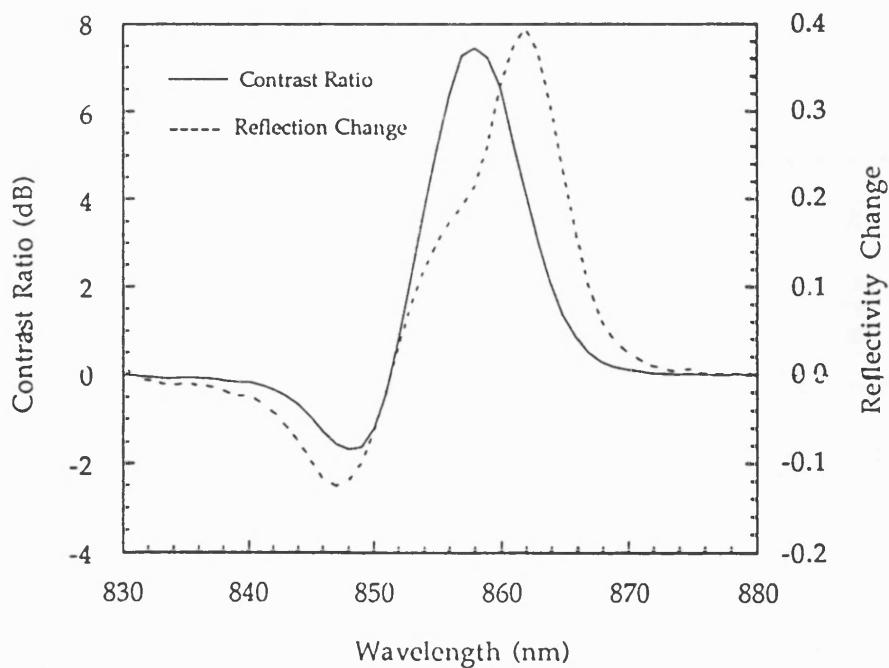

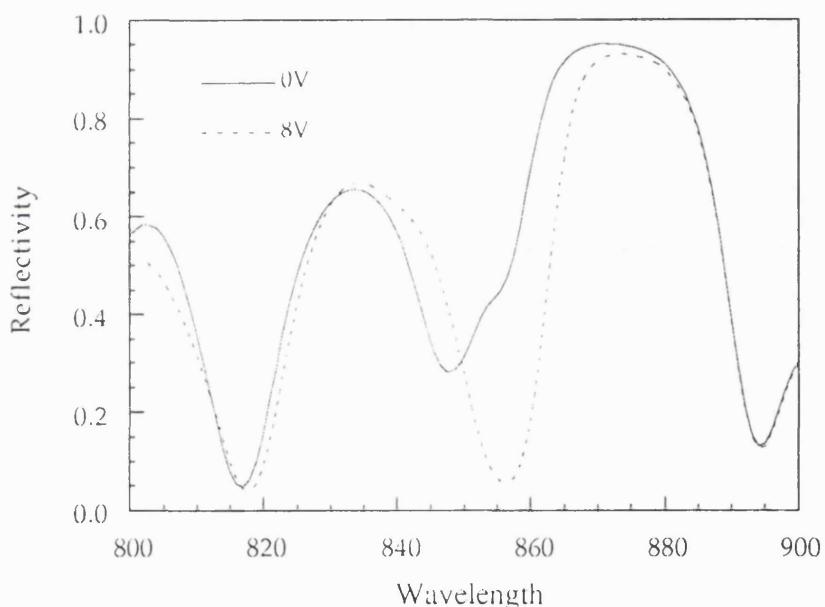

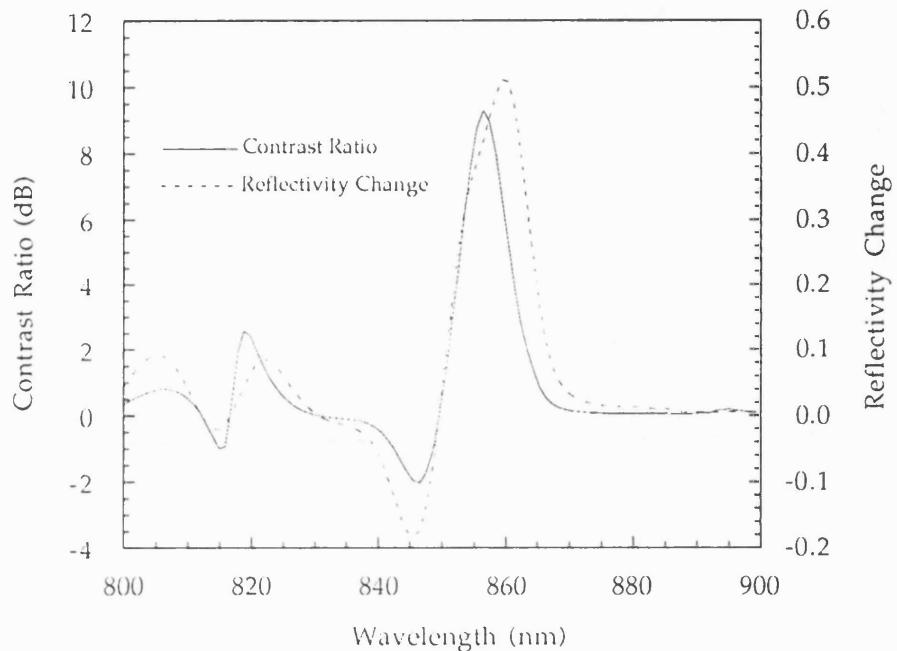

**Figure 1.5** Diagram showing the operation of a basic self electro-optic effect device (SEED).