# Developments in Channel Coding for Error and Spectral Control

A thesis submitted for the degree of

Doctor of Philosophy

in Electronic and Electrical Engineering

March 1997

Simon Fragiacomo

Department of Electrical and Electronic Engineering

University College London

ProQuest Number: 10055383

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10055383

Published by ProQuest LLC(2016). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code. Microform Edition © ProQuest LLC.

> ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### Summary

This thesis is concerned with channel coding. Channel coding consists of error control coding and *line coding* (LC). The basic definitions and concepts of both *error correcting codes* (ECCs) and LC are initially examined, followed by the presentation of a number of existing coding algorithms. Where appropriate, computer simulation is used to establish their limitations. Certain new codes are then devised which offer improved performance.

Finally, following on what is now an established trend, error correcting and line codes are combined to form *error correcting line codes* (ECLCs), which may offer superior performance compared to the use of a cascaded scheme.

Specifically, the first chapter contains some basic definitions, the thesis outline and a summary of the contributions.

Chapter 2 introduces the basic concepts behind *error correcting codes* and *soft decision decoding* (SDD) together with a brief description of the well-established Chase algorithms. Their advantages and limitations will be examined and used **to** generate novel SDD algorithms in chapter 5.

The basic concepts of line coding are introduced in chapter 3. In addition, a new family of single added bit line codes is also presented. This offers reasonably good line characteristics with very small compromise to rate.

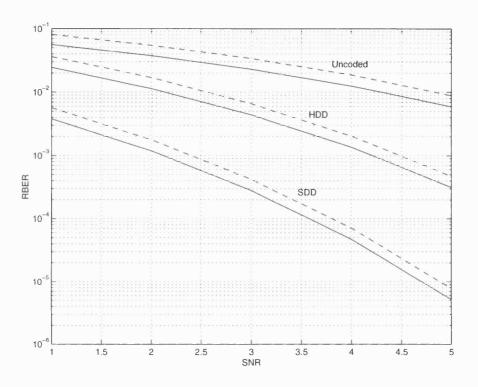

Chapter 4 is concerned with simulation as a means of evaluating the performance of coded systems. A conventional simulation technique is initially presented and used for assessing the performance of BCH codes. This proves inadequate for simulating the very low error rates of modern communication systems, especially when SDD is used. Two novel simulation acceleration algorithms are therefore introduced to alleviate this problem. These will only simulate code words that affect the *residual bit error rate* (RBER) and simply calculate the effects of the code words which are correctly decoded. The novel simulator algorithms are used in subsequent chapters to determine the performance of the proposed new codes.

Chapter 5 introduces the new generalised Chase (GC) algorithms, followed by the adaptive immediate decision (AID) and test pattern elimination (TPE) algorithms. These can be used to offer near maximum likelihood (ML) performance with minimum increase in complexity.

Chapter 6 is concerned with combined EC and line codes to form ECLCs. These can offer both tight line coding characteristics and good decoding performance. Some emphasis is placed on implementation appropriate to very high bit rate systems.

Finally chapter 7 brings the thesis to a conclusion and provides recommendations for future work.

#### **Statement of Originality**

Unless otherwise stated in the text, the work presented in this thesis was carried out by the candidate. It has not been presented previously for any degree, nor is at present under consideration by any other degree awarding body.

Candidate:

Simon Fragiacomo

Director of Studies:

Professor J. J. O'Reilly

#### Acknowledgements

I wish to express my gratitude to Professor John J. O'Reilly for his guidance and support throughout the course of this study and the preparation of this thesis. I would also like to thank him for his friendship and moral support, for which I am deeply indebted.

I would also like to thank a number of people for their contributions, discussions and encouragement: Drs Andrew Popplewell and Yi Bian for their patience and advice. Also a special 'thanks' should go to Chris 'there's at least six ways you can do this' Matrakidis for many fruitful conversations.

I would also like to thank all my friends at UCNW, BT labs and everybody at the UCL Telecoms group, for making these last years so enjoyable.

Last, but certainly not least, I would like to thank my family for their support throughout all these years. To my Father and Mother

# Contents

| 1 | Intr | roduction                                            | 1  |

|---|------|------------------------------------------------------|----|

|   | 1.1  | Introduction                                         | 1  |

|   | 1.2  | Thesis Organisation                                  | 4  |

|   | 1.3  | Summary of Main Contributions                        | 6  |

| 2 | Cha  | annel Coding                                         | 10 |

|   | 2.1  | Introduction                                         | 10 |

|   | 2.2  | Error Control Codes                                  | 10 |

|   |      | 2.2.1 Forward error correction                       | 12 |

|   | 2.3  | Generating Linear Binary Block Codes                 | 13 |

|   |      | 2.3.1 A simple ECC example                           | 16 |

|   | 2.4  | Decoding a Simple ECC                                | 17 |

|   | 2.5  | Soft Decision Decoding                               | 21 |

|   |      | 2.5.1 The Chase algorithms                           | 22 |

|   |      | 2.5.2 Mechanics of the Chase algorithms              | 25 |

|   |      | 2.5.3 Test pattern set generation                    | 27 |

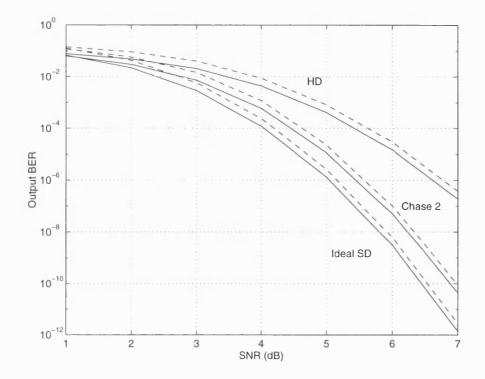

|   |      | 2.5.4 Performance comparison of the Chase algorithms | 28 |

|   | 2.6            | Summary                                                                                         | 30 |

|---|----------------|-------------------------------------------------------------------------------------------------|----|

| 3 | Line           | e Coding                                                                                        | 33 |

|   | 3.1            | Introduction                                                                                    | 33 |

|   | 3.2            | Line Coding                                                                                     | 34 |

|   |                | 3.2.1 A simple line code                                                                        | 36 |

|   | 3.3            | The $nB1X$ Class of Line Codes $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 38 |

|   |                | 3.3.1 The $nB1P$ , $nB1C$ and $nB1I$ line codes                                                 | 40 |

|   |                | 3.3.2 Improving the $nB1I$ code $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$              | 42 |

|   |                | 3.3.3 The $nB1D$ and $nB1R$ line codes $\ldots \ldots \ldots \ldots \ldots \ldots$              | 42 |

|   |                | 3.3.4 The $nB1DR$ line code $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$      | 43 |

|   |                | 3.3.5 Improving the $nB1DR$ code $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$          | 46 |

|   | 3.4            | Summary of Code Performance                                                                     | 49 |

|   |                | 3.4.1 Decoding performance of the single added bit codes                                        | 49 |

|   | 3.5            | Spectral Properties of Selected $nB1X$ codes $\ldots$ $\ldots$ $\ldots$ $\ldots$                | 52 |

|   | 3.6            | Direct Calculation of the Power Spectrum                                                        | 53 |

|   |                | 3.6.1 Analysing the Manchester code                                                             | 55 |

|   |                | 3.6.2 Analysing the $nB1D$ code $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$       | 56 |

|   |                | 3.6.3 Analysing the $nB1C$ code $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$  | 58 |

|   | 3.7            | Summary                                                                                         | 58 |

| 4 | $\mathbf{Sim}$ | ulation                                                                                         | 63 |

|   | 4.1            | Introduction                                                                                    | 63 |

|   | 4.2            | A Communications System Model                                                                   | 65 |

|   |                | 4.2.1 Model components                                                                          | 67 |

|   |      | 4.2.2   | Data source and encoder                                                   | 68  |

|---|------|---------|---------------------------------------------------------------------------|-----|

|   |      | 4.2.3   | Channel simulation                                                        | 69  |

|   |      | 4.2.4   | Hard decision decoder                                                     | 72  |

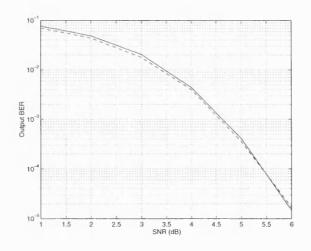

|   | 4.3  | Simula  | ation Verification and Validation                                         | 75  |

|   | 4.4  | The N   | leed for Accelerated Simulation Techniques                                | 77  |

|   | 4.5  | Simula  | ation Acceleration Techniques                                             | 79  |

|   | 4.6  | First A | Acceleration Technique                                                    | 79  |

|   | 4.7  | Second  | d Acceleration Technique                                                  | 84  |

|   | 4.8  | SDD a   | and the Simulation Acceleration Techniques                                | 88  |

|   | 4.9  | Other   | Performance Evaluation Programs                                           | 89  |

|   |      | 4.9.1   | Line code performance                                                     | 90  |

|   |      | 4.9.2   | Power spectrum                                                            | 91  |

|   | 4.10 | Summ    | ary                                                                       | 91  |

| 5 | Gen  | eralise | ed Chase and the AID Algorithm                                            | 95  |

|   | 5.1  | Introd  | luction                                                                   | 95  |

|   | 5.2  | Gener   | alised Chase Algorithms                                                   | 96  |

|   |      | 5.2.1   | $N_{GC}$ selection and TP generation $\ldots \ldots \ldots \ldots \ldots$ | 97  |

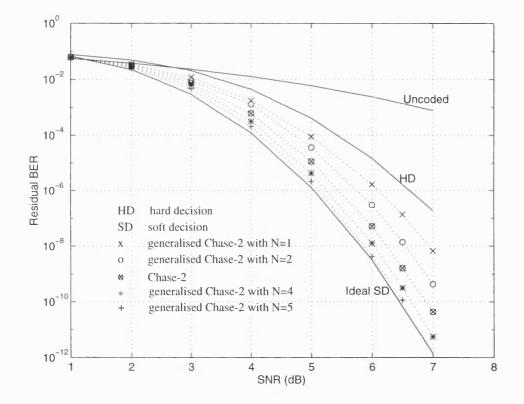

|   |      | 5.2.2   | Simulation results                                                        | 102 |

|   |      | 5.2.3   | Generalised Chase 3                                                       | 105 |

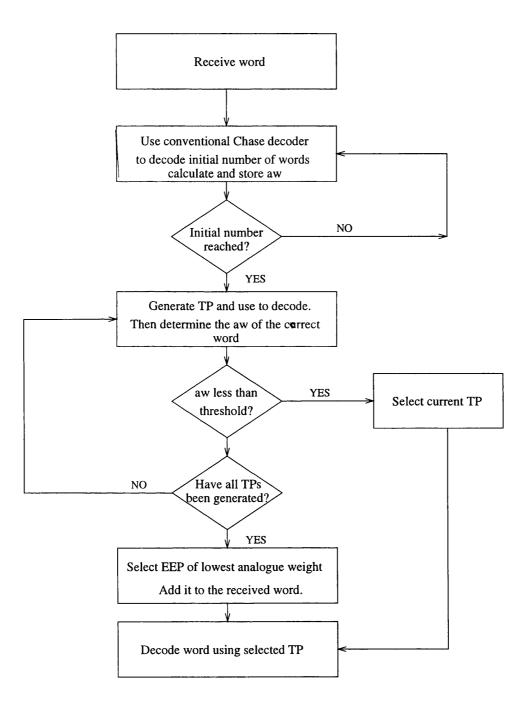

|   | 5.3  | Adapt   | tive Immediate Decision Algorithm                                         | 107 |

|   |      | 5.3.1   | Description of the AID algorithm                                          | 107 |

|   |      | 5.3.2   | Threshold decision                                                        | 108 |

|   |      | 5.3.3   | Optimal value of $\alpha$                                                 | 111 |

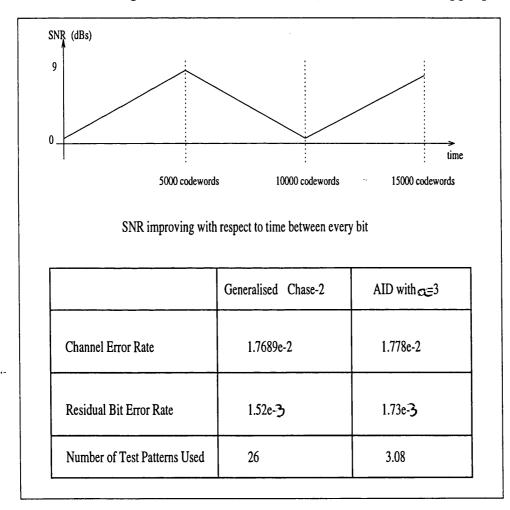

|   |      | 5.3.4 Simulation results for the AID algorithm                                          |

|---|------|-----------------------------------------------------------------------------------------|

|   |      | 5.3.5 Variable noise simulations                                                        |

|   | 5.4  | Improving the Chase and AID Algorithms                                                  |

|   |      | 5.4.1 Decoding bounded algorithm                                                        |

|   | 5.5  | Summary                                                                                 |

| 6 | Con  | bining Error Control and Line Coding with Soft Decision De-                             |

|   | codi | ng 125                                                                                  |

|   | 6.1  | Introduction                                                                            |

|   | 6.2  | The Need for Error Correcting Line Codes                                                |

|   | 6.3  | Generating ECLCs                                                                        |

|   | 6.4  | Proposed Codes                                                                          |

|   | 6.5  | The $nB1X$ Family of ECLCs                                                              |

|   |      | 6.5.1 The $nB1P$ ECLC                                                                   |

|   |      | 6.5.2 $nB1C$ , $nB1D$ and $nB1R$ codes $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 138 |

|   | 6.6  | Bi-modal ECLCs                                                                          |

|   | 6.7  | Enhanced Flag Protection                                                                |

|   |      | 6.7.1 An example EFP code                                                               |

|   | 6.8  | CAB Algorithm Description                                                               |

|   |      | 6.8.1 CAB N algorithm                                                                   |

|   | 6.9  | Simulation Results of the $nB1X$ ECLCs                                                  |

|   | 6.10 | N=2 ECLCs                                                                               |

|   |      | 6.10.1 Improvements on the N=2 codes                                                    |

|   |      | 6.10.2 Simulation results for the N=2 codes                                             |

|   |      | 6.10.3 Manchester ECLC                                                  | 163 |

|---|------|-------------------------------------------------------------------------|-----|

|   | 6.11 | Calculating the Decoding Performance of the Single Flag Codes $\ . \ .$ | 171 |

|   | 6.12 | Calculating the Decoding Performance of the EFP Codes $\ldots$ .        | 173 |

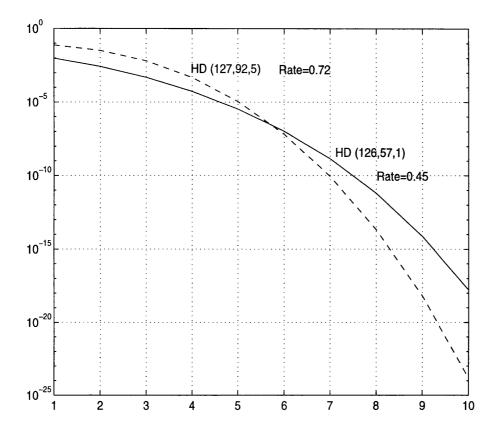

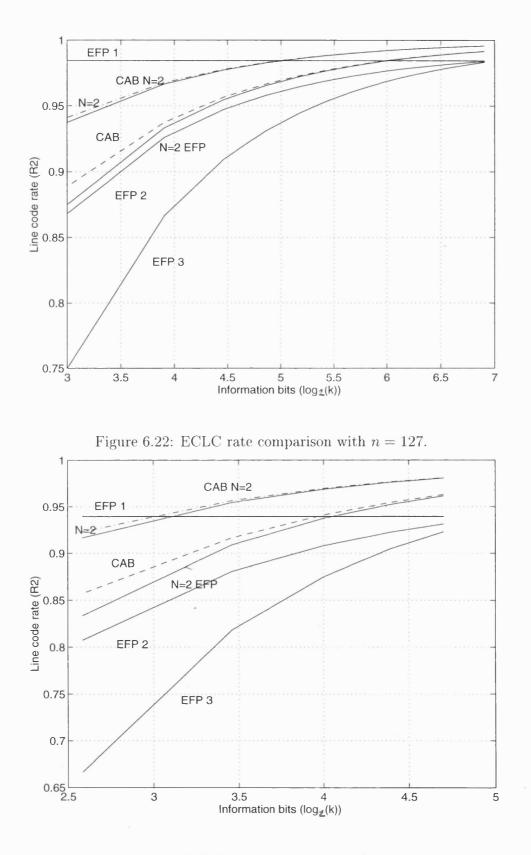

|   | 6.13 | Rate Considerations                                                     | 176 |

|   |      | 6.13.1 Line code rate                                                   | 179 |

|   | 6.14 | Summary                                                                 | 182 |

| 7 | Con  | clusions                                                                | 186 |

|   | 7.1  | Contributions                                                           | 187 |

|   | 7.2  | Concluding Remarks                                                      | 189 |

| A | Calo | culating the Power Spectrum                                             | 190 |

|   | A.1  | Introduction                                                            | 190 |

|   | A.2  | Calculating the Power Spectral Density                                  | 190 |

|   |      | A.2.1 Determining $R_{yy}(j)$ at $j = 0$                                | 191 |

|   |      | A.2.2 Determining $R_{yy}(j)$ at $j \neq 0$                             | 191 |

|   | A.3  | Power spectrum of the Manchester Code                                   | 193 |

|   | A.4  | Power Spectrum of the $nB1D$ Code                                       | 194 |

# List of Figures

| 1.1  | Coding tree diagram.                                                 | 3  |

|------|----------------------------------------------------------------------|----|

| 2.1  | Error correcting code tree diagram.                                  | 13 |

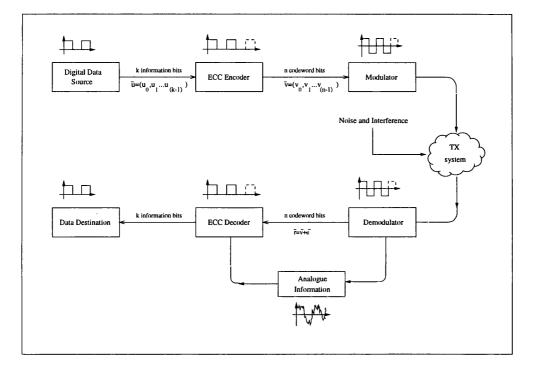

| 2.2  | Block diagram of a communications system.                            | 14 |

| 2.3  | Communications system (with SDD) block diagram                       | 22 |

| 2.4  | Flow diagram of the Chase algorithms.                                | 24 |

| 3.1  | AMI state diagram                                                    | 37 |

| 3.2  | AMI power spectrum                                                   | 38 |

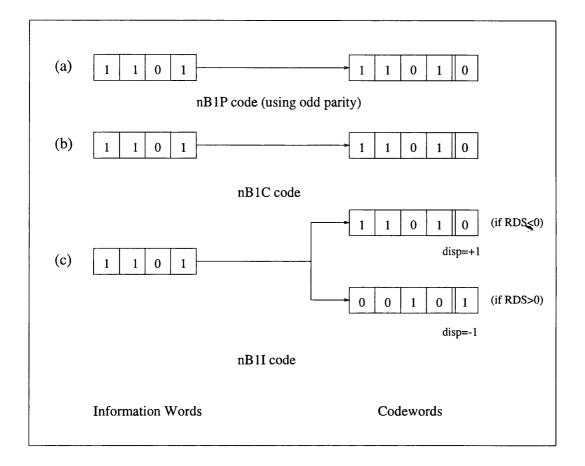

| 3.3  | Examples of the $P, C$ and $I$ codes, for $n = 4$                    | 41 |

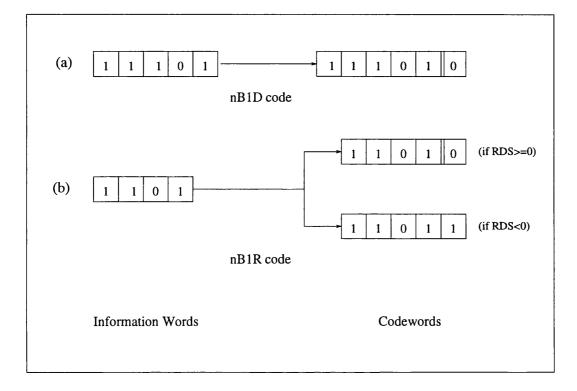

| 3.4  | Examples of the $D$ and $R$ codes                                    | 43 |

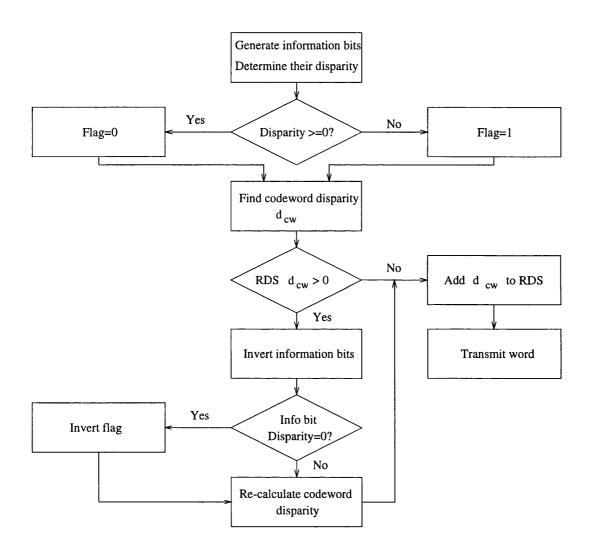

| 3.5  | Flow diagram of the $nB1DR$ code                                     | 45 |

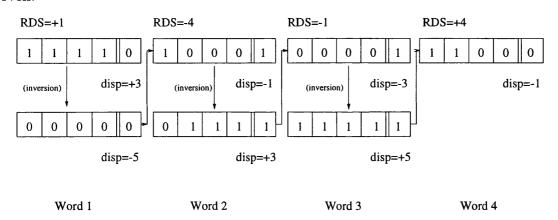

| 3.6  | Worst case runlength for the $4B1DR$ code                            | 48 |

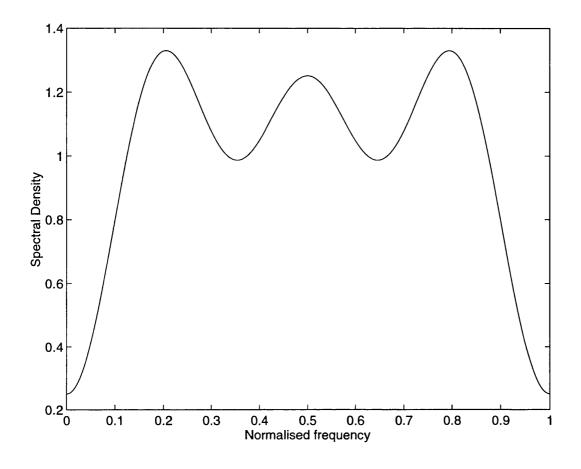

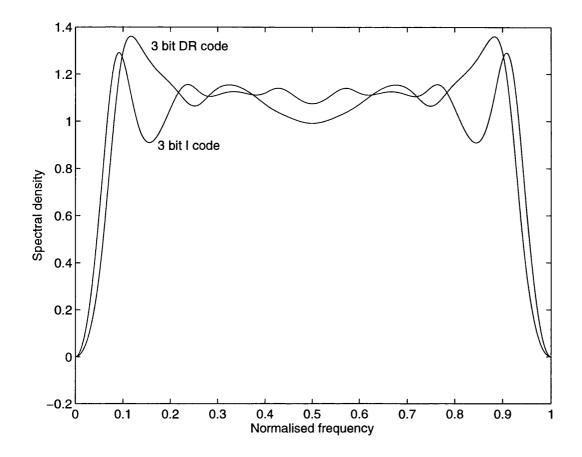

| 3.7  | Power spectrum for the $nB1D$ code with $n = 3. \ldots \ldots$       | 53 |

| 3.8  | Power spectrum for the $nB1DR$ and $nB1I$ codes                      | 54 |

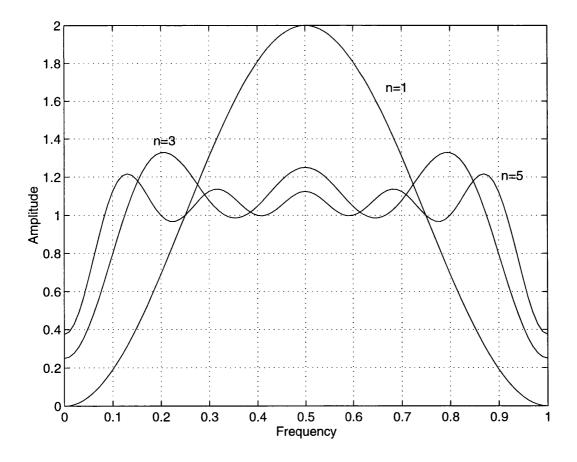

| 3.9  | Power Spectrum of the $nB1D$ code with various values of $n. \ldots$ | 57 |

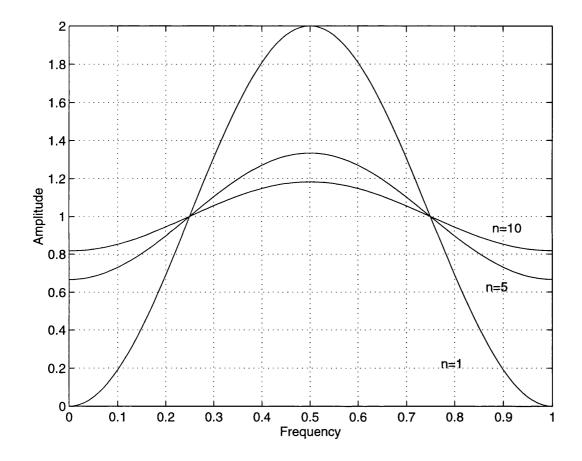

| 3.10 | Power Spectrum of the $nB1C$ code with various values of $n. \dots$  | 59 |

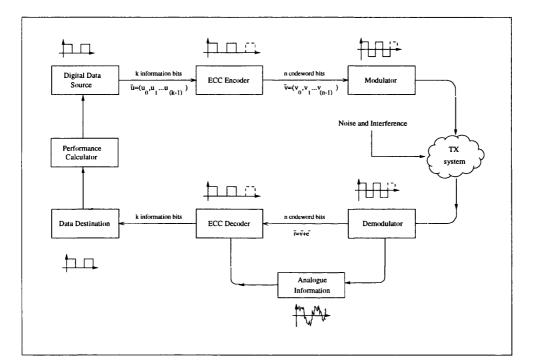

| 4.1  | Communication system simulator outline                               | 66 |

| 4.2  | Noise function shape.                                                 | 72  |

|------|-----------------------------------------------------------------------|-----|

| 4.3  | Validation of (127, 106) BCH code.                                    | 76  |

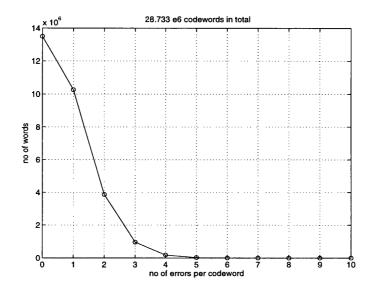

| 4.4  | BCH (127,106) at SNR=5 simulated error distribution                   | 86  |

| 5.1  | Simulation of a BCH (127,106) error correcting code with various      |     |

|      | values of $N$                                                         | 104 |

| 5.2  | AID algorithm flow diagram                                            | 110 |

| 5.3  | Performance comparison between the GC-2 and AID for a $(127, 106)$    |     |

|      | BCH code, with sloping noise functions.                               | 117 |

| 6.1  | Conventional cascaded error correcting line code implementation.      | 127 |

| 6.2  | Error correcting line code block diagram.                             | 129 |

| 6.3  | Tree diagram of the presented ECLCs.                                  | 133 |

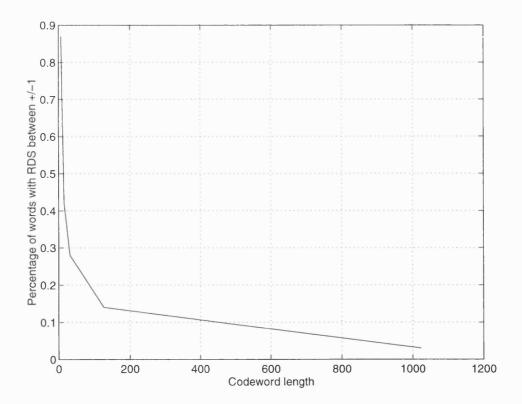

| 6.4  | Percentage of code words with RDS values within $\pm 1$ versus code   |     |

|      | word length $n$                                                       | 137 |

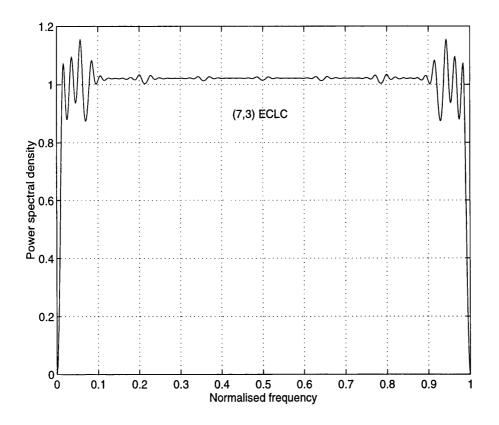

| 6.5  | Power spectrum of a (7,3) ECLC                                        | 141 |

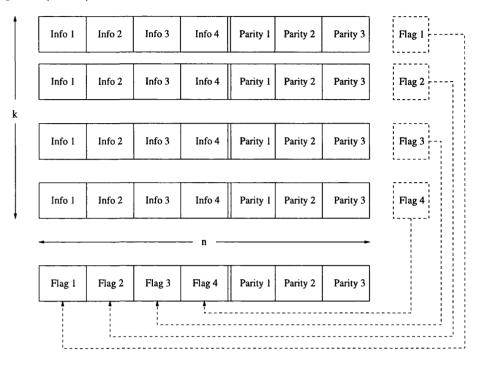

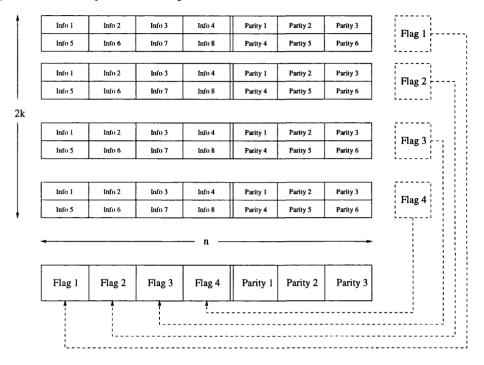

| 6.6  | Cascaded added bit ECLC matrix.                                       | 148 |

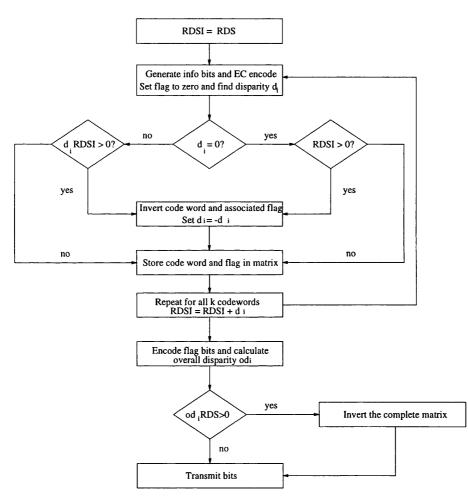

| 6.7  | CAB flow diagram.                                                     | 149 |

| 6.8  | Cascaded added bit ECLC with grouped (N=2) code words                 | 151 |

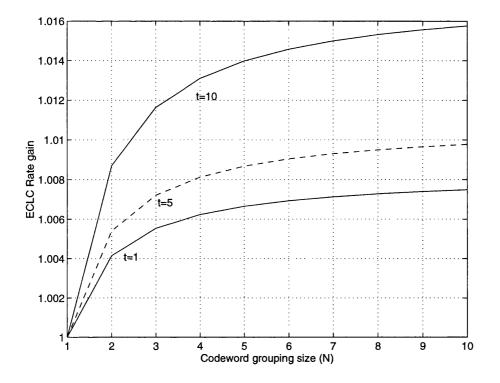

| 6.9  | CAB ECLC rate gain for various group sizes, using a $n=127~{\rm BCH}$ |     |

|      | parent code with varying values of $t$                                | 152 |

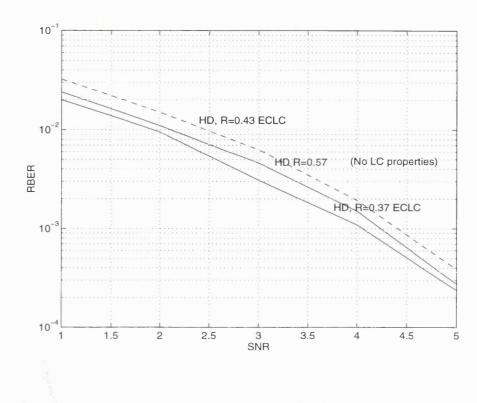

| 6.10 | HDD performance using a parent BCH $(7, 4)$ ECC with and without      |     |

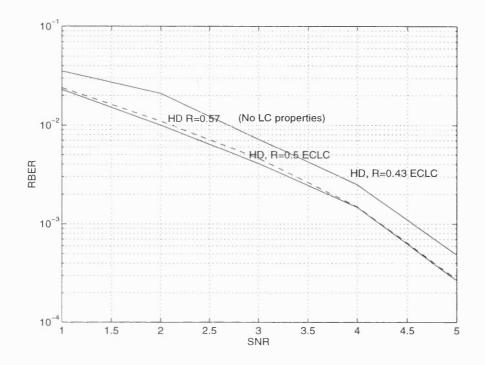

|      | ECLC properties.                                                      | 155 |

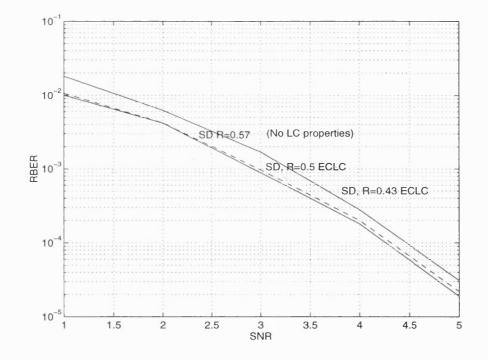

| 6.11 | SDD performance using a parent BCH $(7, 4)$ ECC with and without      |     |

|      | ECLC properties.                                                      | 155 |

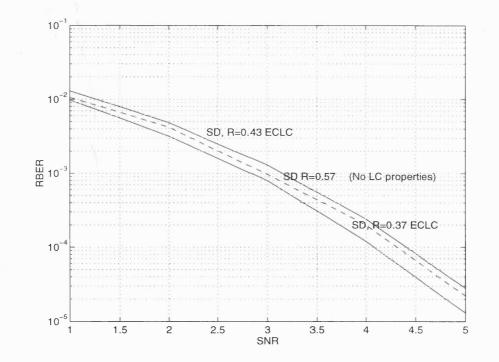

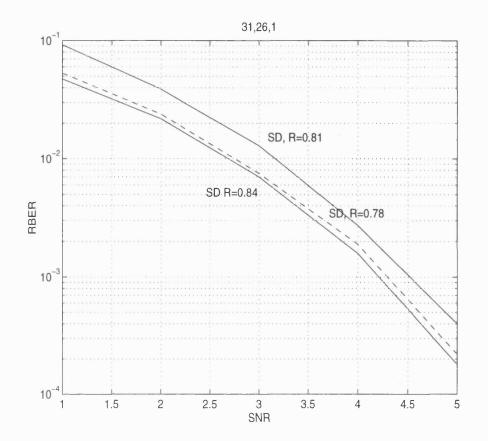

| 6.12 | SDD performance using a parent BCH $(31, 26)$ ECC with and with-    |     |

|------|---------------------------------------------------------------------|-----|

|      | out ECLC properties                                                 | 156 |

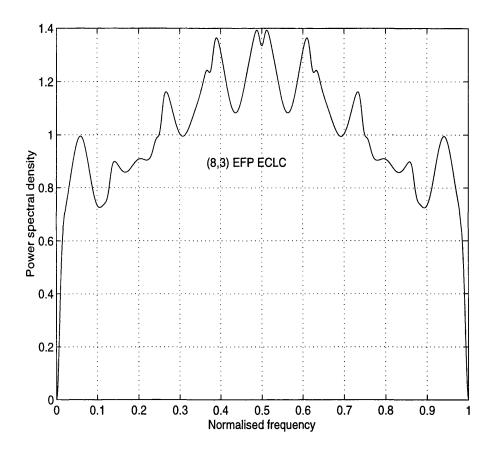

| 6.13 | Power spectrum of a $(8,3)$ ECLC                                    | 157 |

| 6.14 | HDD performance of $N=2$ error correcting line coding code, using a |     |

|      | (7,4) parent ECC                                                    | 164 |

| 6.15 | SDD performance of $N=2$ error correcting line coding code, using a |     |

|      | (7,4) parent ECC                                                    | 164 |

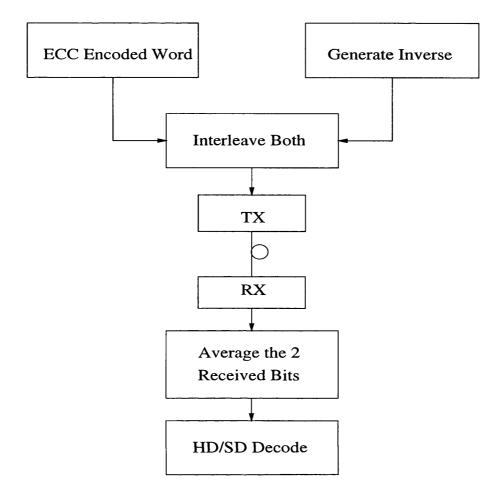

| 6.16 | Block diagram of third algorithm.                                   | 166 |

| 6.17 | Decoding performance of the third algorithm.                        | 168 |

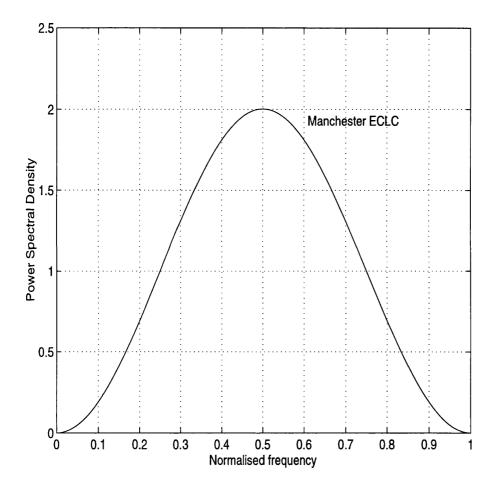

| 6.18 | Spectral densities of the Manchester ECLC.                          | 170 |

| 6.19 | CAB decoding performance for a (127, 106) BCH code with SDD. $$ .   | 174 |

| 6.20 | Decoding performance for a (7,3) EFP ECLC                           | 176 |

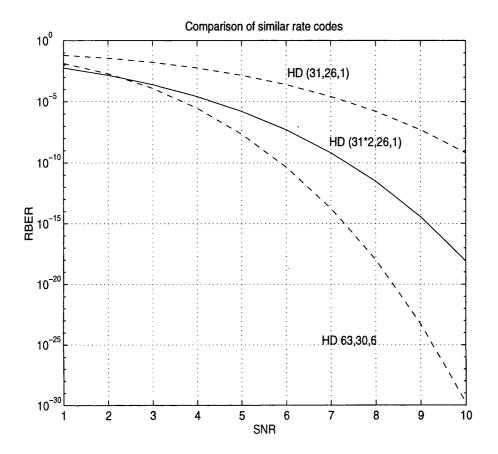

| 6.21 | Rate comparison of similar codes.                                   | 178 |

| 6.22 | ECLC rate comparison with $n = 127. \dots \dots \dots \dots$        | 181 |

| 6.23 | ECLC rate comparison with $n = 31$                                  | 181 |

# List of Tables

| 2.1 | Linear block code with $k = 4$ information bits and $n = 7$ code word  |    |

|-----|------------------------------------------------------------------------|----|

|     | bits                                                                   | 18 |

| 2.2 | Number of TPs for a $n = 63$ BCH code with various values of $d_{min}$ |    |

|     | decoded using the Chase algorithms.                                    | 29 |

| 3.1 | Encoding dictionary for the AMI code.                                  | 37 |

| 3.2 | State table for the $3B1DR$ code. The resultant disparity of each      |    |

|     | code word is shown in the brackets                                     | 47 |

| 3.3 | RDS bounds for the $nB1X$ class of codes                               | 50 |

| 3.4 | Maximum runlength characteristics of the $nB1X$ class of codes         | 51 |

| 4.1 | Number of words and simulator time required for obtaining 1000         |    |

|     | residual errors for varying SNRs.                                      | 78 |

| 4.2 | Simulator time required for obtaining 1000 residual errors at varying  |    |

|     | SNRs using the first acceleration algorithm, compared with conven-     |    |

|     | tional simulation results.                                             | 83 |

| 4.3 | Number of words and simulator time required for obtaining 1000         |    |

|     | residual errors at varying SNRs                                        | 87 |

| 5.1  | Defining TPs according to the inverted LCB positions.                  | 98   |

|------|------------------------------------------------------------------------|------|

| 5.2  | Single error correcting performance using 2 TPs                        | 100  |

| 5.3  | Single error correcting performance using 4 TPs                        | 101  |

| 5.4  | Probability of incorrectly decoding a word for various numbers of      |      |

|      | received errors.                                                       | 102  |

| 5.5  | BCH (63,51) ECC at SNR=4 dB with various values of N (channel          |      |

|      | BER = $1.2 \times 10^{-2}$ )                                           | 106  |

| 5.6  | BCH (127,106) ECC at SNR=5 dB with various values of N (channel        |      |

|      | BER = $5.9 \times 10^{-3}$ )                                           | 106  |

| 5.7  | Decoding performance versus average number of TPs for a (127, 106)     |      |

|      | BCH ECC code at SNR=4dB.                                               | 115  |

| 5.8  | Decoding performance versus average number of TPs for a $(63, 51)$     |      |

|      | BCH ECC code at SNR=5dB.                                               | 115  |

| 5.9  | Code performance simulation results                                    | 116  |

| 5.10 | Number of times decoder is used for a BCH $(127, 106)$ ECC at a        |      |

|      | SNR of 3 dB.                                                           | 119  |

| 6.1  | (8,4) Parity code words, together with their corresponding disparities | .136 |

| 6.2  | Dictionary arrangement for a (7,3) BCH ECLC. The numbers in the        |      |

|      | brackets indicate the disparity of each code word                      | 142  |

| 6.3  | Runlength performance and rates of various ECLC codes                  | 158  |

| 6.4  | Comparison between rate and LC characteristics of various ECLC         |      |

|      | codes                                                                  | 179  |

### Chapter 1

## Introduction

#### 1.1 Introduction

A major aim of communication theory is to devise methods with which signals can be transmitted though imperfect media with the highest possible degree of reliability and efficiency.

In order to achieve this, the signal format at the transmitting end must be chosen so that it will offer maximum resistance to the channel impairments. Additionally, the receiver must be able to recover as much of the original signal as possible. The application of coding is one method of achieving increased reliability.

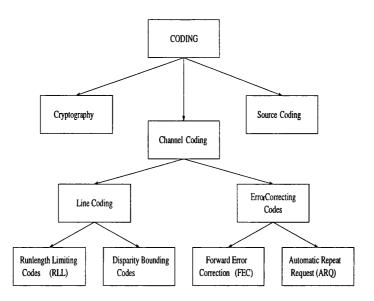

Generally, coding is a form of mapping whereby a given string of information bits is converted into another sequence which | may have added redundancy. We can divide coding into three major areas:

1. Source coding, which has two functions: first to transform a message source into a string of digital symbols and second, to remove any redundancy from the word thus increasing efficiency.

- Cryptographic coding, which is used to increase the security level of a signal by concealing the message. This is done to ensure that only authorised recipients can decode and obtain the transmitted information.

- 3. Finally, channel coding which aims to increase the reliability of a channel by using added redundancy.

This thesis is concerned with channel coding, which can be further divided into two main sub-areas:

1. Line coding (LC), in which the extra information is used to tailor the transmitted signal in such a way as to match the characteristics of the communications link.

Line coding can be used, for example, to modify the spectral characteristics of the signal, (e.g. by placing constraints on the *running digital sum* (RDS)), or to place bounds on the runlength.

2. Error control coding, whereby extra bits introduced at the transmitter are utilised at the receiver to detect and possibly correct any errors that may have occurred. This is further sub-divided into *automatic repeat request* (ARQ) and *forward error correction* (FEC). Both ARQ and FEC will be examined in more detail in the next chapter.

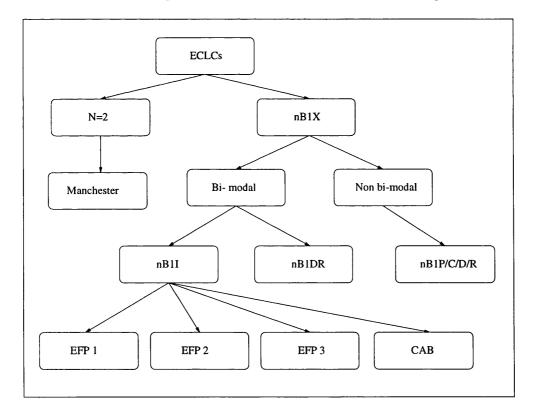

Figure 1.1 summarises the structure of the coding field, as described above.

Figure 1.1: Coding tree diagram.

Even though line and error control coding are two distinct operations they both aim to increase the reliability of a system [1, 2, 3]. With the introduction of digital systems in all aspects of modern life, the issue of data integrity is becoming increasingly more important. Channel coding is a very attractive way of achieving this.

This thesis concentrates on channel coding. A number of existing line and error correcting codes will be presented and simulated, to identify their shortcomings. In a number of cases, new codes will be introduced addressing these limitations. The codes used will be very general in nature and simple to implement.

The basic concepts behind channel coding are initially presented. These are then used to build more complex line and error control codes. However, it is not uncommon for a designer to incorporate both aspects of channel coding in a system. Thus, if a conventional cascaded scheme is used, the data goes first through an *error correcting* (EC) encoder and then through a line encoder. The process is reversed at the decoder. It will be shown that this cascaded scheme can be inefficient and reduces the overall decoding performance. For these reasons combined *error correcting line codes* (ECLCs) have been devised which offer improved performance [4, 5].

Finally, the concept of *soft decision decoding* (SDD) will also be introduced. This is a technique which combines the demodulation and decoding processes. A number of the codes presented in this thesis can be improved by the use of SDD. The latter increases the complexity of the receiver but offers increased decoding power without adding extra redundancy.

A particular feature of the thesis is an exploration of the benefits that arise from employing SDD with ECLCs. This enables significant improvements in both rate and decoding power to be realised. There is currently considerable interest in channel coding for high bit rate systems, such as undersea optical telecommunications transmissions, which provided the original motivation for this study. For this reason only low complexity codes (which allow high bit rates to be realised) will be considered.

#### **1.2** Thesis Organisation

The structure of this thesis can be briefly summarised as follows:

Following this introduction, chapter 2 contains the fundamentals of error control coding together with examples of various simple codes. This chapter is used as a basis for the introduction and development of more advanced codes which are presented in later chapters. In addition, the well-established Chase SDD algorithms are extensively examined due to their critical role in the following chapters, and especially in chapter 5.

Chapter 3 presents the basics of line coding together with a family of simple 'added bit' codes. These offer tight runlength and disparity bounds while being very simple to implement. A number of the added bit codes are used in chapter 6 to form error correcting line codes.

In chapter 4, the need for simulation in channel coding is presented together with a basic ECC simulation. The latter is used as a basis for developing two new simulation acceleration algorithms which are used throughout the thesis to validate theoretical results. These work by 'eliminating' a large number of code words without affecting the accuracy of the simulation.

Chapter 5 introduces three novel SDD algorithms which offer significant performance improvements. Specifically, the *generalised Chase* (GC) utilises an increased number of *test patterns* to achieve improved decoding performance; the AID algorithm then uses threshold decoding to reduce the average number of test patterns without affecting the decoding performance. Finally, the TPE algorithm reduces the number of test patters required for SDD, by eliminating those that produce the same *estimated error pattern* (EEP).

In chapter 6, existing concatenated and ECLCs are presented together with the reason behind the need for error correcting line codes. These are used as a basis for the generation of novel codes, which also utilise SDD to provide better performance with minimal increase in complexity.

Finally, chapter 7 brings the thesis to a conclusion and provides some recom-

mendations for future work.

#### **1.3 Summary of Main Contributions**

The research presented in this thesis examines channel coding schemes suitable for high bit rate systems. The major contributions fall into four main interlinked areas and can be summarised as follows:

- New line codes: a new family of 'added bit' line codes was introduced, which resulted in the harmonisation into a single identifiable family of the disparate nB1X codes.

- Improved simulation techniques, where two novel simulation acceleration techniques are developed. These significantly reduce the amount of time required for obtaining statistically accurate results without compromising accuracy.

- Novel SDD algorithms: a number of novel SDD algorithms are introduced which offer improved decoding performance and increased decoding speed without significantly increasing the complexity of the decoder.

- New error correcting line codes: SDD was combined with conventional error correcting line codes thus producing novel codes which can offer both acceptable decoding performance and reasonably good line coding characteristics.

A number of conference papers have been accepted for presentation and publication. These are the following:

- Y. Bian, J. O'Reilly, A. Popplewell, S. Fragiacomo: "New Simulation Techniques for Evaluation Telecommunications Transmission Systems with FEC", *Fifth IEE Conference on Telecommunications*, March 1995, UK.

- S. Fragiacomo, Y. Bian, A. Popplewell, J. O'Reilly: "A New Low Complexity Near ML Soft Decision Decoding Algorithm for Linear Block Codes", *IEE Singapore International Conference on Communication Systems*, IEEE ICCS/ISPACS '96, 25-29 November 1996, Singapore.

- Y. Bian, A. Popplewell, J. O'Reilly, S. Fragiacomo, R. Blake: "FEC for Future Trans-Oceanic Optical Systems", *Fifth IEE Conference on Telecommunications*, Brighton, March 1995, UK.

- 4. S. Fragiacomo, C. Matrakidis, J. O'Reilly: "Exploiting Soft Decision Decoding for Error Correcting Line Codes", *IEE Singapore International Conference on Communication Systems*, IEEE ICCS/ISPACS '96, 25-29 November 1996, Singapore.

- S. Fragiacomo, C. Matrakidis, J. O'Reilly: "A Novel Error Correcting Line Code", *Third Communication Networks Symposium*, 8-9 July 1996, Manchester, UK.

- S. Fragiacomo, C. Matrakidis, J. O'Reilly: "A New Error Correcting Line Code", ITS/IEEE ROC&C '96 International Telecommunications Symposium, October 28-31 1996, Acapulco, Mexico.

- 7. S. Fragiacomo, C. Matrakidis, J. O'Reilly: "A Novel Error Correcting Line Code", Networks and Optical Communications (NOC) - Post-Deadline Ses-

sion, June 25-28 1996, Heidelberg, Germany.

- S. Fragiacomo, C. Matrakidis, J. O'Reilly: "Soft Decision Error Correcting Line Code for Optical Data Storage", 9th Annual Meeting, LEOS 96, 18-21 November 1996, Boston, USA.

- S. Fragiacomo, C. Matrakidis, A. Popplewell, Y. Bian, J. O'Reilly: "An Accelerated Simulation Technique for Evaluating Communication Systems Utilising FEC", Networks and Optical Communications (NOC), June 17-20 1997, Antwerp, Belgium.

- S. Fragiacomo, C. Matrakidis, J. O'Reilly: "A Class of Low Complexity Line Codes", International Symposium on Information Theory, ISIT 97, 29 June 1997, Ulm, Germany.

- S. Fragiacomo, C. Matrakidis, J. O'Reilly: "Performance Aspects of a Class of Low Complexity Line Codes", International Conference on Signal Processing, ICSPAT 97, September 1997, San Diego, USA.

In addition, a number of journal papers have been submitted. The next chapter begins by presenting some basic concepts of error control coding and soft decision decoding.

## Bibliography

- K. W. Cattermole: "Mathematical Foundations for Communication Engineering", Volume 2, Pentech Press, 1986.

- [2] S. Lin, D. Costello: "Error Control Coding", Prentice Hall, 1983.

- [3] "Algebraic Coding Theory and Applications", Edited by G. Longo, Springer-Verlag.

- [4] A. Popplewell: "Combined Line and Error Control Coding", PhD Thesis, University of Wales, Bangor, 1990.

- [5] A. Kokkos: "Contributions to Modulation and Coding", PhD Thesis, University of Wales, Bangor, 1990.

### Chapter 2

### **Channel Coding**

#### 2.1 Introduction

In this chapter a brief overview of *forward error control* (FEC) and *soft decision decoding* (SDD) will be presented. As discussed before, channel coding can be divided into two main categories: FEC and *line coding* (LC). This chapter introduces the basic concepts behind FEC, while chapter 3 presents the basic concepts of line coding.

#### 2.2 Error Control Codes

In general, error control codes can be divided into two types [1]:

Automatic repeat request (ARQ), whereby the receiver can only detect errors. If these occur, then a feedback path is used to request the re-transmission of the erroneous data. ARQ systems can be divided into two main categories: stop-and-wait ARQ and continuous ARQ. With stop-and-wait ARQ the transmitter will only send the next word if the received word contains no errors. Continuous ARQ will send words and receive acknowledgements continuously. If errors are detected the offending code word will be retransmitted. ARQ systems can be simple to implement since they only require error detecting codes and are efficient in high *signal to noise ratio* (SNR) communication links. However, a number of disadvantages are also present:

- They require a feedback path to send the repeat request. This means that stop-and-wait ARQ requires a half-duplex channel while continuous ARQ requires a full-duplex channel.

- They can be very inefficient, especially if high channel error rates exist because a high number of repeat requests will be made.

- In high bit rate or long distance systems where a significant delay exists, continuous ARQ will be used. This can be more efficient but will require large buffering systems.

For the above reasons ARQ systems are not considered here.

2. The second error control strategy is forward error correction (FEC). This utilises codes which can detect and correct errors at the receiver, termed error correcting codes (ECCs). Such codes are more complicated to implement but do not require feedback paths. In addition, they are better suited to relatively low SNR applications. For these reasons, FEC is examined in more detail in this study.

#### 2.2.1 Forward error correction

The theoretical basis for error correcting codes was developed during the late 1940's by Shannon [2]. He suggested that the elimination of errors in a received digital bit stream was possible, if the latter was properly encoded. Encoding usually requires the introduction of redundancy. Shannon also proved that any number of errors can be corrected, provided the block length is large enough.

The challenge in coding theory is to discover codes which can correct a large number of errors while minimising redundancy and complexity.

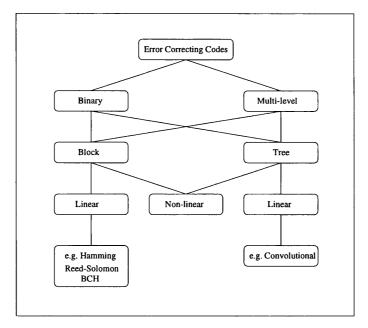

Error correcting codes can be divided into binary and multi-level codes. If the encoded data stream at the transmitter can only obtain two distinct values then our code is a binary one, otherwise it is a multilevel one. Both these types of code can be further sub-divided into block or tree codes. Block codes, which are of interest here, were introduced by Hamming in the 1950's [3]. They differ from tree codes in that there is no 'memory' during the encoding process and the produced bits depend only on the current information word.

Finally, either of these codes can be linear or non-linear. A binary block code is linear if the modulo-2 sum of any two of its code words is also a code word. The best known linear block codes are cyclic, where a cyclic shift of any code word also produces a code word. The most frequently used ones are the BCH codes which include the Reed-Solomon and Hamming families. The most common tree codes are convolutional codes, where the check bits are mixed with the information bits in a continuous manner.

Figure 2.1 presents the family of error correcting codes.

Figure 2.1: Error correcting code tree diagram.

This thesis aims to develop error correcting and line codes appropriate for modern high bit rate systems. For this reason, only linear binary block codes will be considered as they are likely to be the simplest to implement and usually require a minimal amount of decoding time. A widely used group of such codes are the *Bose-Chaudhuri-Hocqenghem* (BCH) codes, introduced in 1960 [4]. These will be used as an example whenever a specific code example is required.

#### 2.3 Generating Linear Binary Block Codes

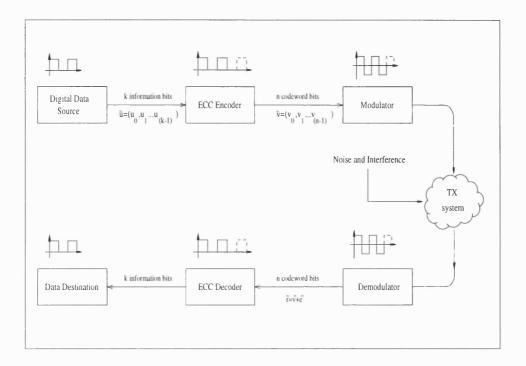

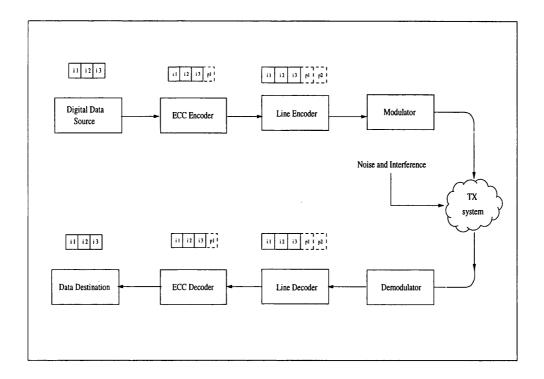

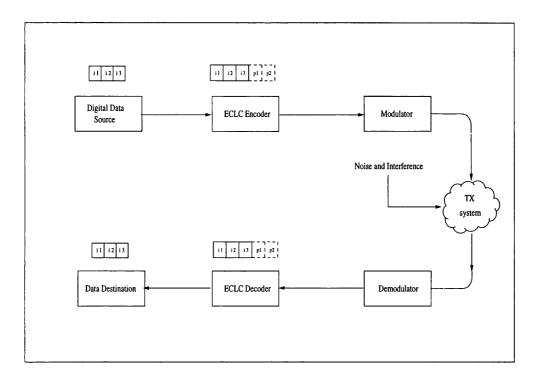

Figure 2.2 is intended to make linear block error correcting codes easier to appreciate. This represents the block diagram of a complete communications system, utilising an (n, k) ECC encoder.

The digital data source will generate a continuous stream of information bits. The error correcting code encoder will divide this stream into blocks of k bits each.

Figure 2.2: Block diagram of a communications system.

These are represented by a binary k-tuple  $\bar{u} = (u_0, u_1, \dots, u_{k-1})$  called a *message*. This implies that for a binary code there are  $2^k$  possible messages.

The encoder 'contains' the generator matrix G which has as rows a set of k linearly independent code words. These are called the 'basis code words' and make the row space of G the linear code. If all the linear combinations of the basis code words are taken ( $\bar{v} = \bar{u} \cdot G$ ) then  $2^k$  *n*-bit code words will be generated.

The error correcting capabilities of a code depend on the Hamming distance (d)separating the code words. The Hamming distance of two code words of length n(where k < n) is defined as the number of places in which their bits differ [5]. The minimum distance  $(d_{min})$  of a code is defined as the smallest possible Hamming distance between any two code words. For BCH codes  $(d_{min})$  is an odd number. Such a code can detect and correct up to  $t = \frac{(d_{min}-1)}{2}$  errors and t is therefore termed the 'error correcting capability' of the code.

At the output of the encoder the k-bit information vector will therefore be transformed to an n-bit code word which now has error correcting properties. The added (n-k) bits are called the parity check digits, or parity bits. The n-bit code word is then modulated and transmitted. The same process is repeated for the next k information bits. An (n, k) code of minimum distance  $(d_{min})$  has therefore been generated.

At the receiver, the received waveform is initially demodulated. This produces a binary stream of code words. If no errors have occurred then the received vector  $\bar{r}$  will equal the transmitted one, i.e.  $\bar{r} = \bar{v}$ . If errors have occurred, then it can be assumed that they will have formed the error vector  $\bar{e}$ . In such a case  $\bar{r} = \bar{v} \oplus \bar{e}$ , where  $\oplus$  indicates modulo-2 addition.

It is up to the decoder to attempt to detect and possibly correct the errors that may have occurred. To do this it uses the parity check matrix H. This is a  $((n-k) \times n)$  matrix where any vector in the row space of G is orthogonal to the rows of H. Therefore, for any  $\bar{v}$  we get  $\bar{v} \cdot H^T = 0$ , where  $H^T$  is the transpose of H. In order to detect if errors have occurred,  $\bar{r}$  is multiplied by  $H^T$ . If  $\bar{r} \cdot H^T = 0$  then either no errors have occurred, or the error correcting capability (t) of the code has been exceeded.

If error correction (as opposed to error detection) is also required, then the previous formula must be expanded. At the receiver  $\bar{r}$  is multiplied by  $H^T$ , i.e.

$$\bar{r} \cdot H^T = (\bar{v} + \bar{e}) \cdot H^T = \bar{v} \cdot H^T + \bar{e} \cdot H^T$$

Since  $\bar{v}$  is always a valid code word,  $\bar{v} \cdot H^T = 0$ , so  $\bar{r} \cdot H^T = \bar{e} \cdot H^T$ . This

product is called the *syndrome* (S) and only depends on the error pattern. If the syndrome is zero then no errors have occurred;  $2^{(n-k)}$  unique syndromes exist, each corresponding to a specific error vector. Using the syndrome information the error position can be located. Since our codes are binary there are only two possible distinct bit states, a logic 1 or a logic 0. Therefore if the positions of the errors in the code word are known, error correction is also possible by performing a simple inversion of those positions.

#### 2.3.1 A simple ECC example

To provide an illustrative framework for some basic definitions, an example of a very simple linear binary (7, 4) code with a minimum Hamming distance  $d_{min} = 3$  will be considered. This has k = 4 information bits encoded into n = 7 code word bits. Therefore,  $2^k$  possible distinct messages will be encoded into  $2^n$  code words using a one-to-one correspondence. The generator matrix G of such a code is of the following form:

$$G = \begin{bmatrix} g_0 \\ g_1 \\ g_2 \\ g_3 \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 1 \end{bmatrix}$$

(2.1)

while the parity check matrix H will be the following:

$$H = \begin{bmatrix} 1 & 0 & 0 & 1 & 0 & 1 & 1 \\ 0 & 1 & 0 & 1 & 1 & 1 & 0 \\ 0 & 0 & 1 & 0 & 1 & 1 & 1 \end{bmatrix}$$

(2.2)

Assume that a message  $\bar{u} = (1101)$  must be transmitted using the above code. To achieve this, the message must be multiplied with the generator matrix so that the code word vector  $\bar{v}$  is produced, i.e.

$$\bar{v} = \bar{u} \cdot G = (1101) \cdot G = 1 \cdot g_0 + 1 \cdot g_1 + 0 \cdot g_2 + 1 \cdot g_3 =$$

(1101000) + (0110100) + (1010001) = 0001101

Thus the transmitted EC code word will be 0001101. Because the (7, 4) code is a systematic one, the four last bits contain the original message in the correct order, while the initial three bits are the parity bits required for error detection and correction at the receiver. Table 2.1 contains the mappings for all possible four bit information words.

#### 2.4 Decoding a Simple ECC

In the previous section, a 4-bit information message was encoded into a 7-bit code word using a linear block code. In this section, the received word will be decoded and up to t errors will be corrected. Since  $t = \frac{(d_{min}-1)}{2}$  and for our code  $d_{min} = 3$ then t = 1, i.e. it is a single error correcting code.

Assume that  $\bar{r} = (r_0, r_1, r_2, r_3, r_4, r_5, r_6)$  is the received vector. The syndrome S is defined as

| Information word | (7,4) code words |

|------------------|------------------|

| 0000             | 000 0000         |

| 0001             | 101 0001         |

| 0010             | 011 0010         |

| 0011             | 010 0011         |

| 0100             | 011 0100         |

| 0101             | 110 0101         |

| 0110             | 010 0110         |

| 0111             | 001 0111         |

| 1000             | 110 1000         |

| 1001             | 011 1001         |

| 1010             | 001 1010         |

| 1011             | 100 1011         |

| 1100             | 101 1100         |

| 1101             | 000 1101         |

| 1110             | 010 1110         |

| 1111             | 111 1111         |

Table 2.1: Linear block code with k = 4 information bits and n = 7 code word bits.

$$S = \bar{s} = \bar{r} \cdot H^T = (s_0, s_1, \dots, s_{(n-k-1)}).$$

(2.3)

From this it is deduced that the syndrome is simply the sum of the received parity digits and those re-computed at the decoder. Thus if  $S \neq 0$  an error has been detected.

Using equation 2.3 in our example (7, 4) code the following equation is obtained:  $\bar{s} = (s_0, s_1, s_2) = \bar{r} \cdot H^T = (\bar{u} + \bar{e}) \cdot H^T = \bar{u} \cdot H^T + \bar{e} \cdot H^T = 0 + \bar{e} \cdot H^T = \bar{e} \cdot H^T$ Assuming that the vector  $\bar{r} = (1001001)$  has been received, i.e. a single error

exists in bit position 5 the syndrome will be equal to:

$$S = \bar{r} \cdot H^{T} = (1001001) \cdot \begin{bmatrix} 100\\010\\001\\110\\011\\111\\111\\101 \end{bmatrix} = (111)$$

(2.4)

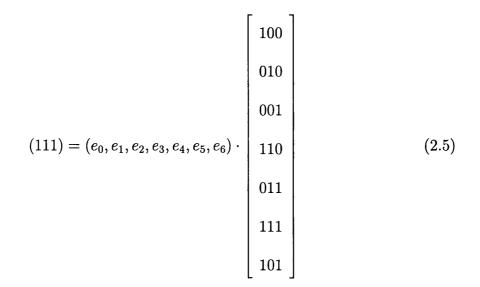

Therefore  $S \neq 0$  and an error has been detected. In order to detect the error position it is noted that

$$S = (s_0, s_1, s_2) = (1, 1, 1) = \bar{e} \cdot H^T \Rightarrow$$

Using equations 2.4 and 2.5 the following error vectors are derived:

$$l = e_0 + e_3 + e_5 + e_6 \tag{2.6}$$

$$1 = e_1 + e_3 + e_4 + e_5 \tag{2.7}$$

$$1 = e_2 + e_4 + e_5 + e_6 \tag{2.8}$$

A number of possible solutions exist that satisfy the above equations. If maximum likelihood decoding is used for error location then the error pattern with the minimum number of corrected positions is selected. In this case, this is the (0000010) error vector. If this is added to our received vector the transmitted vector will be obtained.

In chapter 4, Berlekamp's iterative algorithm will be briefly presented. This is an algorithm for generating the error locator polynomial, appropriate for more complex and powerful codes. It is a well-established technique which lends itself to software implementation.

### 2.5 Soft Decision Decoding

In the previous sections it was demonstrated how the information bits could be encoded and decoded so that error detection and correction were possible. At the receiver, only the algebraic properties of the code were utilised to locate any possible errors. This is termed *hard decision decoding* (HDD).

In this section, the basic principles of soft decision decoding (SDD) are presented. SDD uses the analogue information to try to increase the error correcting capability of the code. As has been mentioned before, a code of minimum distance  $d_{min}$  can correct up to t errors. The use of SDD allows this limit to be exceeded, under certain conditions. The penalty is the increased complexity of the decoder and the fact that the t-error correcting capability may not be guaranteed anymore.

SDD techniques are not suitable for very noisy systems. However, modern telecommunication and data storage systems usually have very low error rates and can thus benefit from the application of such techniques.

A modified communications system which includes SDD, is shown in figure 2.3.

Here extra information is provided to the decoder in the form of the analogue values of the received bits. These values are provided by the demodulator and are used to facilitate the decoding process by indicating possible error positions.

SDD algorithms can be grouped into two broad classes:

(a) Minimum distance (or minimised sequence error rate) decoding algorithms, based on [6].

(b) Trellis decoding algorithms, adapted for block codes.

A number of SDD algorithms exist, such as [8, 9, 10, 11], but the most widely

Figure 2.3: Communications system (with SDD) block diagram.

used are the Chase algorithms. This is because they can offer a balance between decoding power and complexity. In the following sections the Chase algorithms will be examined in detail. Their shortcomings will be identified and then addressed in chapter 5.

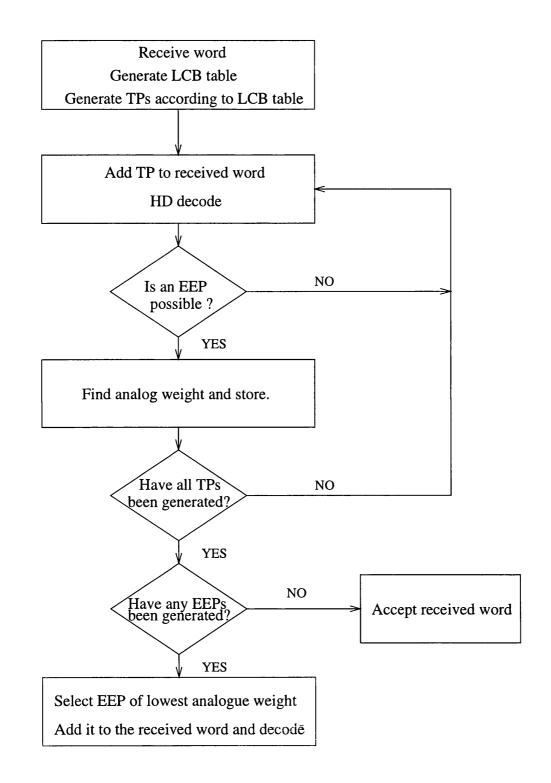

### 2.5.1 The Chase algorithms

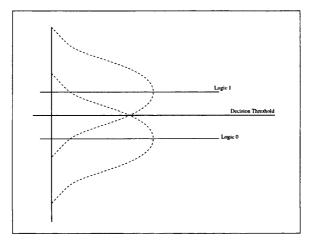

In 1972, D. Chase [7] suggested three different SDD algorithms of type (a), each of which provided a different number of test patterns, allowing a trade-off between performance and complexity. Specifically, the Chase decoder generates a set of possible error patterns, called the *test patterns* (TPs). These are then sequentially perturbed with the received word and taken through a conventional HDD decoder. This may result in a possible error pattern being generated, termed an *estimated*  error pattern (EEP). The EEP is used to indicate the bit positions which are deemed to contain an error and each is assigned a confidence value, provided by the analogue information. After HDD of all possible patterns has taken place, the one with the highest confidence value is selected and added to the received word to provide the corrected word.

Chase suggested three different algorithms, each examining a different number of TPs. The TPs are used to invert a number N of *least confidence bit* (LCB) positions. These are defined as the bit positions closest to the decision threshold. The reason behind the use of TPs is that if the voltage value of a received bit is very close to the decision threshold, this bit is very likely to be in error. Thus if the syndrome calculations indicate that the received code word contains errors, these are more likely to be in the LCB positions than anywhere else. By systematic inversion of different combinations of these positions, the errors within a code word could be corrected.

An ECC utilising HDD can correct upto  $\lfloor \frac{d_{min}-1}{2} \rfloor$  errors. The use of an SDD algorithm, in conjunction with an ECC, allows a higher average number of errors per code word to be corrected. However, unlike a conventional ECC, the use of any SDD algorithm may not guarantee the correction of up to t errors within a code word.

The flow diagram of the decoding process for the Chase algorithms is shown in figure 2.4 and is explained in more detail in the following section.

Figure 2.4: Flow diagram of the Chase algorithms.

#### 2.5.2 Mechanics of the Chase algorithms

Assume that for a given communication system the transmitted word is defined as  $\overline{v} = v_0, v_1, \dots v_{(n-1)}$  and the received word as  $\overline{r} = r_0, r_1, \dots r_{(n-1)}$ , where  $r_i = v_i + no_i$ for  $0 \le i \le (n-1)$  and  $no_i$  is defined as the noise amplitude. Let t be the error correcting capability of the (n, k) ECC.

The resultant error pattern (EP) indicates the bit positions where  $\overline{v}$  and  $\overline{r}$ differ.  $\overline{e} = e_0, e_1, \dots e_{n-1}$  is termed the error vector and is defined by  $e_i = v_i \oplus r_i$ for  $0 \leq i \leq (n-1)$  while the binary weight of  $\overline{e}$  is termed  $W(\overline{e})$  and defined as the total number of non-zero elements in the sequence. A decoder will try to find a code word that satisfies  $W(\overline{e}) \leq (\frac{d_{min}-1}{2})$  where  $d_{min}$  is the minimum Hamming distance of the code.

In the Chase algorithms, a test pattern  $TP = tp_0, tp_1, \dots tp_{(n-1)}$  for  $0 \le i \le (n-1)$  of length *n* is initially generated. This is done by selecting a number  $(N_{Chase})$  of LCBs and producing a set of *n*-bit sequences containing possible permutations of these  $N_{Chase}$  positions. This generates a set of up to  $2^{N_{Chase}}$  TPs. The initial TP will always be the all zero word.

Each TP is then modulo-2 added to the received word  $\overline{r}$  and the resultant sequence  $\overline{r}' = \overline{r} \oplus TP$  is conventionally decoded using any suitable HD decoder. Since the addition of the TPs has the effect of inverting a number of LCB positions it is likely that some of the resultant sequences will have a reduced number of errors compared to the received code word.

If a conventional HD error correcting decoder was used and the initial number of errors exceeded t then the decoding operation would fail. With the addition of the TP procedure, it is possible that the total number of errors is reduced (or even eliminated) thus allowing conventional decoding to take place.

The received word with the added TP will be taken through the EC decoder, which will either produce a *decoder error pattern* (DEP) or fail to decode. The DEP will then be added to the TP to produce an n-bit sequence termed *estimated error pattern*. Thus,  $EEP = (eep_0, eep_1, \dots eep_{(n-1)}) = TP \oplus DEP$ . If the addition of the TP has introduced more errors (instead of eliminating them) it is possible that the decoding will fail. In such a case no EEP will be produced. This is the reason for always starting with the all zero word as the initial TP; if the error pattern contains t or less errors the all zero TP will allow the decoder to operate properly. If not, then only the removal of errors will allow decoding. The latter can only be accomplished by using appropriate TPs and for this reason the process is repeated for the whole TP set.

Once all possible EEPs have been produced, one must be selected. It should be noted that not every TP will create an EEP and not all EEPs will be distinct. The selection will be done using the analogue weight of each EEP which is defined as:

$$aw_{EEP} = \sum_{i=0}^{n-1} a_i \times eep_i \tag{2.9}$$

where  $a_i$  is the analogue value of the i - th bit position of the EEP.

The EEP with the smallest analogue weight will be modulo-2 added to the received word and the resulting sequence will be accepted as the corrected word. The EEP of minimum analogue weight is selected because equation 2.9 determines the pattern which has inverted the least confident bits. If all errors have been corrected then the EEP should equal the EP.

### 2.5.3 Test pattern set generation

It should be clear that the generation of the TP set is a very important task. If this is correctly generated then the total number of errors in a code word may be reduced, otherwise it will be increased. For this reason, the introduction of channel measurements may not guarantee anymore the correction of a minimum number of t received errors. However, if the total number of errors is above t, the decoder may have the ability to correct them. The three algorithms for selecting the TPs as suggested by Chase are the following:

- 1. The first algorithm (Chase 1) examines all possible TPs. Therefore, for an n-bit code with a minimum distance between code words of  $d_{min}$ , a total of  $\left( \lfloor \frac{n}{d_{min}} \right)$  possible combinations exist. For other than very small values of n this is impractical to implement in hardware or indeed to simulate down to the RBERs of interest. A considerable reduction in complexity is obtained if the test patterns that produce identical error patterns are ignored, but even with this improvement, the algorithm is not very efficient.

- 2. The second algorithm (Chase 2) considers only the set of error patterns containing  $N_{Chase} = \lfloor \frac{d_{min}}{2} \rfloor$  lowest channel measurements (i.e. the bits with the highest probability of error). The test patterns generated in this case are those where any combination of inverted positions is allowed within the set of lowest measurements. Thus  $2^{\lfloor \frac{d_{min}}{2} \rfloor}$  TPs are examined.

3. Chase 3 examines N<sub>Chase</sub> = (⌊dmin 2 ⊢ 1) possible patterns. Once more the inverted positions are assigned to the *i* positions of lowest confidence. If d<sub>min</sub> is even, *i* takes the values *i* = (0, 1, 3, ... *d* − 1). If d<sub>min</sub> is odd then *i* = (0, 2, 4, ... *d* − 1). This algorithm gives best results for codes with large values of d<sub>min</sub>.

Chase does not give the reason for differentiating between odd and even values of  $d_{min}$  and work done on the simulator indicates that it is unnecessary. Specifically, the performance of a code decoded using Chase 3 with i = (0, 2, 4, ..., d - 1) never exceeds the performance of the same code using Chase 3 but with i = (0, 1, 3, 5, ..., d - 1).

#### 2.5.4 Performance comparison of the Chase algorithms

Each of the three Chase algorithms utilises a different sized set of TPs for decoding. Clearly, if the TPs are sensibly chosen, the larger the set of TPs the more decoding power the code will have. However a large set of TPs will require more time to decode since a decoding operation for each TP is required.

Clearly, for large n (even for a relatively small  $d_{min}$ ) algorithm 1 is too complex to employ in practice, since it will examine  $\binom{n}{\lfloor \frac{d}{2} \rfloor}$  possible error patterns. The second Chase algorithm will examine  $2^{(\lfloor \frac{d}{2} \rfloor)}$  possible error patterns. Finally, using the third Chase algorithm  $(\lfloor \frac{d}{2} \rfloor + 1)$  possible test error patterns must be examined.

The above figures indicate that the complexity of Chase 2 and 3 depends on the minimum distance d only and not on the code word length. Therefore they offer clear benefits whenever long code words are used. These results can be seen

| t | Chase 1 | Chase 2 | Chase 3 |

|---|---------|---------|---------|

| 1 | 63      | 2       | 2       |

| 2 | 1953    | 4       | 3       |

| 3 | 39711   | 8       | 4       |

| 4 | 595665  | 16      | 5       |

| 5 | 7028847 | 32      | 6       |

in table 2.2 where the total number of TPs needed for each Chase algorithm are shown for various values of  $d_{min}$ , for an n = 63 BCH code.

Table 2.2: Number of TPs for a n = 63 BCH code with various values of  $d_{min}$  decoded using the Chase algorithms.

In terms of decoding power, Chase 1 will provide results which will closely approach the *maximum likelihood* (ML) limit. The latter is the best possible decoding result soft decision decoding can offer. Simulation results indicate that Chase 2 performs reasonably well when compared to Chase 1, particularly at the low error rates of importance for this study. A significant reduction in the number of TPs is effected while an acceptable decoding performance is maintained. Chase 3 involves a loss in performance compared to the second algorithm due to the reduced number of TPs.

A disadvantage of all 3 algorithms is the fact that the complete set of TPs needs to be generated and used before one can be selected. This can prove to be too time consuming, especially for high bit rate operations.

### 2.6 Summary

In this chapter, the basic definitions and concepts of error control coding (which included both hard and soft-decision decoding algorithms) were introduced. The Chase SDD algorithms were then described in detail and a critical assessment of their performance was made. Thus the second Chase algorithm was found to be the most promising choice for implementation in practical high rate systems. This is because it offers a balanced solution in terms of decoding power and simplicity. The latter is very important both because it allows improvements to be made and also because of the potential application on high bit rate systems.

Having introduced some key ideas relating to error correcting codes we now turn our attention in the following chapter to line coding. We will begin by reviewing the basic principles and then progress to the consideration of some novel low-complexity codes suitable for high bit rate applications.

# Bibliography

- [1] S. Lin, D. Costello: "Error Control Coding", Prentice Hall, 1983.

- [2] C. Shannon: "The Mathematical Theory of Communication", Bell Systems Technology Journal, 1948.

- [3] R.W. Hamming: "Error detecting and Correcting Codes", Bell Systems Technology Journal, Vol. 29, pp. 147-160, April 1950.

- [4] R. Bose, D. Ray-Chaudhuri: "On a Class of Error Correcting Binary Group Codes", Information and Control, Vol 3, March 1960.

- [5] The Open University: "Codes", TM 361 14, 1982.

- [6] G. D. Forney, "Generalised Minimum Distance Decoding", IEEE Transactions on Information Theory, Vol IT-12, pp. 125-131, April 1966.

- [7] D. Chase: "A Class of Algorithms for Decoding Block Codes With Channel Measurement Information", *IEEE Transactions On Information Theory*, Vol IT-18, pp. 167-170, January 1972.

- [8] O. Olanyian: "Implementable Soft-Decision Decoding Schemes", International Journal Of Electronics, Vol 66, 1989.

- [9] J. Eiguren, I. Dumer, P. Farrell: "Split Syndrome Soft-Decision Decoding For Block Codes", Coding and Cryptography Conference, December 1993.

- [10] J. Wolf: "Efficient Maximum Likelihood Decoding Of Linear Block Codes Using a Trellis", *IEEE Transactions On Information Theory*, Vol 24, January 1978, pp. 76-80.

- [11] W. H. Thesling, F. Xiong: "Pragmatic Approach to Soft decision Decoding of Linear Block Codes", *IEE Proceedings on Communications*, Vol 142, No. 1, pp. 40-47, February 1995.

## Chapter 3

## Line Coding

### 3.1 Introduction

In the previous chapter, the basic concepts of *forward error correction* (FEC) were presented. *Soft decision decoding* (SDD) was then introduced which offered greater *error correcting* (EC) capabilities but at the expense of increased complexity. A number of existing SDD algorithms were presented and critically evaluated.

In this chapter, *line coding* (LC) will be introduced. Specifically, the need for LC will be presented together with some basic definitions and concepts. Those will be followed by the presentation of a new family of line codes which are very simple to implement, yet offer reasonably tight bounds for both the maximum runlength and the disparity. Since they are single added bit codes, the overall rate is not significantly reduced which makes them well suited to high bit rate applications.

The chapter begins with a presentation of the basics of line coding, a simple line code being used as an example to illustrate the main concepts. The nB1X

family of line codes is then introduced followed by a detailed examination of its performance. We conclude by presenting two methods for determining the power spectrum of a line code.

### 3.2 Line Coding

The principal function of a line code is to match the transmission signal to the communication channel characteristics. Therefore, line coding is introduced to overcome the physical impairments of the channel used. This is usually achieved by limiting or eliminating the low frequency content of a signal and/or by reducing the maximum runlength. Both of these factors require added redundancy.

The low frequency content must be restricted since most channels cannot achieve sufficient signal to noise ratio in that area of the spectrum [1]. For example, magnetic recorders do not respond well to low frequency signals, so that a signal that contains such components will have an increased number of errors. These can be corrected by using FEC. However, a simpler technique is to code the data so that distortion is minimised. This can be achieved by line coding [2].

In addition, for practical reasons, many channels are AC coupled. This implies that the DC and low-frequency content of a signal must be suppressed [3, 4]. This can be achieved by bounding the *digital sum variation* (DSV), which is the difference between the largest and smallest values of the *running digital sum* (RDS) [5], defined as where  $d_i$  is defined as the disparity (i.e. the difference in ones and zeros) of each one of the k code words.

Additionally, it is common for the receiver to be synchronised by extracting timing information from the received waveform. It is thus necessary to have an adequate number of transitions within a given amount of time. This is achieved by limiting the maximum runlength  $(RL_{max})$  of a bit stream. The latter is defined as the maximum number of consecutive identical bits in a code word.

Recent experimental data suggest that significant gains in error performance can be achieved in some systems by limiting the maximum runlength of a transmitted word. Specifically, in a 232km optical fibre system, 4dB of equivalent coding gain was present simply by limiting the maximum runlength from  $RL_{max} = 31$  to  $RL_{max} = 7$  [6].

Generally speaking, a line code will map a block of k symbols which have p levels into a block of m symbols with r levels. In most cases the use of the line code will introduce some redundancy, so that  $r^m \ge p^k$ . The rate R of a code is defined as

$$R = \frac{k \log_2 p}{m \log_2 r}.$$

A disadvantage of most line codes is known as 'error extension'. This is a phenomenon whereby errors along the channel give rise to a larger number of errors in the decoder. An example of error extension will be presented in the following sections with the introduction of the bi-modal codes.

The following evaluation factors can be used to compare various line coding schemes:

- 1. Power Spectrum: This usually is one of the most important factors, indicating the extent of any DC or low frequency contents. The low frequency region of the power spectrum is related to the running digital sum bounds.

- Synchronisation: In most applications, the receiver utilises signal transitions to synchronise itself with the transmitter so that optimal sampling is effected. Therefore, a code which offers a high number of transitions is preferred. Synchronisation is determined by the maximum runlength.

- 3. Signal degradation: Very frequent transitions can in some instances (e.g. bandwidth limited channel) cause *inter-symbol interference* (ISI) between adjacent symbols.

- 4. Reduction in the overall bit rate R, due to the introduction of the line code.

- 5. Complexity of implementation and cost.

Various existing and new line codes will be presented in this chapter with the areas mentioned above forming a basis for assessing their suitability for use.

#### 3.2.1 A simple line code

One of the simplest line codes is the alternate mark inversion (AMI) code. Such a code is not very useful for optical transmission systems since the three transition levels required are not suited to on-off keying techniques. However, AMI will be used to demonstrate, by way of example, the basic concepts behind line coding. The AMI code will encode a binary zero as a ternary 0 and a binary one as a  $\pm 1$

| Information Word | Code word |       |

|------------------|-----------|-------|

|                  | RDS=0     | RDS=1 |

| 0                | 0         | 0     |

| 1                | +1        | -1    |

alternately. Thus long runs of ones will be avoided while long runs of zeros can still exist. The encoding dictionary for this code is shown in table 3.1.

Table 3.1: Encoding dictionary for the AMI code.

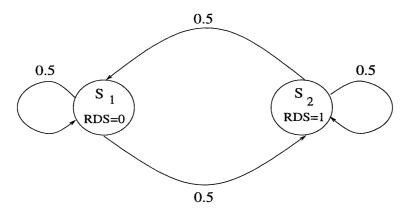

Figure 3.1 presents the state diagram of the AMI code. A state diagram is a convenient way of showing the possible states a code can have (represented by a circle) and the probability of transferring from one state to another. Figure 3.1 indicates that in the AMI code there is an equal probability of transferring between different states or remaining in the same state.

Figure 3.1: AMI state diagram.

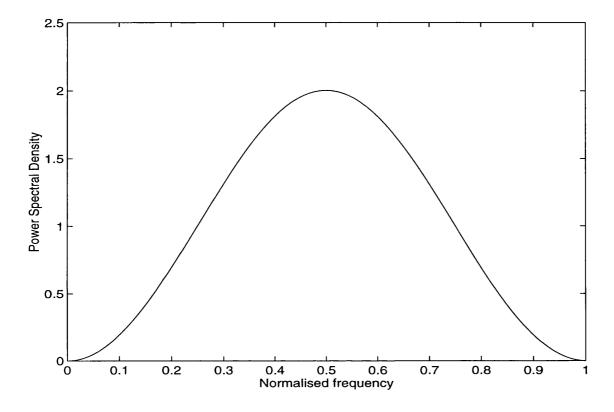

Finally, the power spectrum of a line code is very important. As has been mentioned before, one of the reasons behind the use of a line code is the suppression of the low frequency content and the elimination of the DC component. The power

spectrum presents the power spectral density versus frequency for a given code. In our case this was achieved by using the Cariolaro and Tronca algorithm [7]. The power spectrum of the AMI code is illustrated in figure 3.2, where it is seen that indeed the lower frequencies are suppressed and the DC content is zero.

Figure 3.2: AMI power spectrum.

In the following sections a unified family of line codes, termed nB1X, is examined. This is simple to implement and can offer very good line coding characteristics.

### **3.3** The nB1X Class of Line Codes

A binary block line code can be considered as a member of the nBmB family. Such codes have n binary information bits which are encoded to m binary code word bits. A widely used subset of these codes are those where m = (n + 1), i.e. a single bit has been added to every n information bit block. The added bit can be used to achieve either error detection or line coding properties. The nB1Xline codes introduced here are a subclass of this family [4, 8, 10]. These are very simple to implement and relatively effective but, like all line codes, they reduce the overall code rate, which becomes equal to  $R = (\frac{n}{m}) = (\frac{n}{n+1})$ , and under certain circumstances, may introduce error extension.

The major advantages of the nB1X codes can be summarised as follows:

- They can provide tight runlength and disparity bounds.

- The reduction in rate (especially for large values of n) is minimal.

- They can be very simple to encode and decode.

- They use state-independent decoding. This means that the decoder does not utilise the RDS information so error propagation between line code words is impossible.

- Finally, most added bit line codes can be converted into *error correcting line codes* (ECLCs).

This chapter introduces a number of novel single added bit codes. These are combined with existing line codes, to form the nB1X family. Each member of this family is presented in detail, together with any possible improvements, in the following sections.

### **3.3.1** The nB1P, nB1C and nB1I line codes

The nB1P code is a single bit insertion code where the added bit is a parity bit. It offers odd number error detection by forcing the code word to have either odd or even parity. If an odd number of errors is present then this will be detected and the word can be ignored or a re-transmission requested.

The nB1P code can not place bounds on disparity but it can place runlength constraints if odd parity is used when n = odd. In such a case the maximum runlength will be equal to 2n. If n = even and even (odd) parity is used then there are no runlength bounds since the number of zeros (ones) is unbounded, while the number of ones (zeros) is limited to 2n. An example 4B1P encoded word, using odd parity, is shown in figure 3.3 (a).

The nB1C code [11] inserts an extra bit at the end of each word, the value of which is the inverse (complement) of the value of the previous bit. The runlength is thus limited to a maximum value of (n+1). Figure 3.3 (b) uses a 4B1C encoded word as an example.

It should be noted that if n = 1 on the nB1C code, then each bit is followed by its inverse, i.e. a 'Manchester' dipulse code has been derived. This has zero DC content, suppressed low frequencies and is very simple to implement. In addition, it is suitable for use as an ECLC and is thus presented in more detail in chapter 6.

Finally, the nB1I [12] is a bi-modal code where the added bit indicates whether the word is inverted or not. Inversion is effected if both the code word disparity  $(d_{cw})$  and the RDS have the same sign, i.e. if  $d_{cw} \times RDS > 0$ . This ensures that RDS bounds are placed. The initial value of the flag bit is set to zero. If the word

Figure 3.3: Examples of the P, C and I codes, for n = 4.

is subsequently inverted then the value of the flag will become equal to one and this will indicate to the receiver that inversion has taken place. This code offers the best line coding performance of all three codes presented in this section, in terms of disparity reduction. Figure 3.3 (c) presents a 4B1I encoded word as an example.

The RDS of this code can be between the values of (-n-1) and (n-1) if n is odd and between (-n-1) and (n) if n is even. The maximum runlength for ones is  $\frac{(5n+3)}{2}$  and for zeros  $\frac{(5n+1)}{2}$ , if n is odd. The equivalent numbers if n is even are both  $\frac{(5n+2)}{2}$ . A disadvantage of the nB1I code is the fact that error extension is present. If, for example, an error occurs on the flag bit then the information bits will be incorrectly decoded.

#### **3.3.2** Improving the nB1I code

The state diagram of the nB1I code was used to determine the word combination that generated the worst runlength of ones, if n is odd. This was found to occur when zero disparity words existed and since these can be inverted without affecting the RDS, a modified algorithm was created, termed nB1I Improved (I). The latter will invert zero disparity words if the first  $\frac{(n+1)}{2}$  bits of the current zero disparity word equal the last bit of the previous one. This technique slightly reduces the maximum runlengths of ones down to  $\frac{(5n+1)}{2}$  if n is odd. The maximum runlength of zeros and the DSV were not affected. By placing an extra constraint a reduction in the maximum runlength without reducing the rate has been achieved.

#### **3.3.3** The nB1D and nB1R line codes

The nB1D code consists of an n bit (where n is odd) information word coupled to a single bit flag. The value of the flag depends on the disparity of the information word and aims to reduce it. As an example consider that the all-zero information word is to be transmitted in [] continuous blocks of three bits each. If the nB1Dcode is to be used, a flag bit with a value of 1 will be added in every block. Thus a four bit block will be generated which will have a reduced disparity compared to the uncoded version. The flag bit primarily aims to reduce the average DSV value but since it consists of a single bit, it will never manage to place bounds on the RDS. Figure 3.4 (a) presents an example of a 5B1D code. It should be also noted that while this code primarily aims to reduce the average DSV this will also have the effect of reducing the maximum possible runlength, see Table 3.4.

Figure 3.4: Examples of the D and R codes.

The nB1R code aims to reduce the overall RDS value by using a flag bit of the opposite sign, i.e. if RDS > 0 then the flag bit is equal to zero, otherwise it equals one. The advantage of this coding scheme is that the *average* DSV is more tightly bound than before. However, no bounds are placed on either the runlength or DSV. Figure 3.4 (b) presents an example of a 4B1R code.

### **3.3.4** The nB1DR line code

The nB1DR is the final code of this class [13]. Similarly to the nB1I algorithm presented previously, it also is a bi-modal code but uses the flag bit to either reduce

the disparity of the code word or to indicate that an inversion of the information bits has taken place. The encoder flow diagram for this code is shown in figure 3.5.

Initially the disparity of the information block is calculated and the extra bit is appended at the end. The value of the latter aims to reduce the overall disparity of the code word, in a similar manner to the nB1D code. If n is even it is possible that the code word disparity will be zero. In such a case the flag will be set to zero as well.

The disparity of the whole word (including the flag bit) termed  $d_{cw}$  in figure 3.5 is then calculated. If  $(d_{cw} \times RDS) > 0$  (i.e. the code word disparity has the same sign as the RDS) then the information bits are inverted before transmission, otherwise the word is simply transmitted. The value of the RDS is then updated and the process is repeated.

This concludes the algorithm if n is odd. However if n is even, then an extra step must be added which compensates for possible zero disparity words. The information bit disparity once inversion has taken place is re-evaluated and if it is found to be equal to zero then the flag is inverted as well.