# OPTICALLY CONTROLLED ANALOGUE TO DIGITAL CONVERTERS

Thesis submitted to the University of London for the degree of Doctor of Philosophy

#### **Richard Mason**

Department of Electronic and Electrical Engineering

University College

Gower Street

LONDON

July 1994

ProQuest Number: 10017778

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10017778

Published by ProQuest LLC(2016). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code.

Microform Edition © ProQuest LLC.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

### **ABSTRACT**

This thesis is concerned with the design of analogue to digital converters (ADCs) with high sample rates (in excess of 2Gsample/s) and moderate to high resolution (at least 8-bits). This goal is beyond the capability of current electronic technology, due principally to problems caused by clock timing jitter. To overcome this problem, optoelectronic techniques are examined, which can utilise the inherent low jitter available from modern laser sources and optical clock distribution schemes.

A novel optoelectronic technique is proposed which uses an interleaved ADC architecture and optical clock distribution to obtain the required performance. A key component in this system is an optically triggered sample and hold circuit (OS/H). A range of fully integrated OS/Hs have been fabricated using a standard GaAs MESFET technology. These circuits combine both electronic and optical components on a common substrate and demonstrate the use of a standard electronic technology for optoelectronic applications. Measurements on these circuits have demonstrated their effectiveness for this application.

A discussion of the effects of timing errors (both static and dynamic) in interleaved sampling systems leads to the description of a technique for correcting the effects of clock skew. The implementation of this is very straightforward, involving only the adjustment of DC bias voltages.

The system has been designed so that it can employ current optoelectronic integration technology, and in particular the clock distribution and delay can be realised using integrated optical waveguides.

# CONTENTS

| ABSTRACT                                                          | 2    |

|-------------------------------------------------------------------|------|

| TABLE OF CONTENTS                                                 | 3    |

| LIST OF FIGURES                                                   | 8    |

| ACKNOWLEDGEMENTS                                                  | 15   |

| 1. Introduction                                                   | 17   |

| 1.1 General Introduction                                          | 17   |

| 1.2 Background to ADCs and Sample and Hold Circuits               | 18   |

| 1.2.1 Flash Conversion                                            | 20   |

| 1.2.2 Interleaved ADCs                                            | 22   |

| (i) Correction for voltage mismatches                             | 23   |

| (ii) High speed clock distribution and the effect of timing error | s in |

| the interleaved ADC                                               | 23   |

| (iii) Sample and filter method                                    | 26   |

| 1.3 Optical Techniques for A/D Conversion                         | 27   |

| 1.3.1 Electro-Optic Diffraction Modulator ADC                     | 27   |

| 1.3.2 Mach-Zehnder Interferometric A/D Conversion                 | 30   |

| 1.3.3 Electro-Optic Time-Interleaved A/D Conversion               | 33   |

| 1.3.4 Oversampled Optical ADC                                     | 36   |

| (i) Fundamentals of oversampled A/D conversion                    | 36   |

| (ii) Optical oversampled A/D conversion                           | 39   |

| 1.4 The Hybrid Approach to A/D Conversion                         | 40   |

| 1.4.1 Modern Laser Sources                                        | 40   |

| 1.4.2 Optical Clock Distribution                                  | 42   |

| (i) Index Guided Interconnections                                 | 43   |

| (ii) Free Space Interconnections                                  | 44   |

| 1.5 Proposed Optically Triggered ADC                              |      |

| 1.6 Organisation of Thesis                                        |      |

|    | 1.7 Statement of Originality                                               | 48         |

|----|----------------------------------------------------------------------------|------------|

| 2. | GAAS DEVICES AND MODELS                                                    | 51         |

|    | 2.1 The Physics of GaAs                                                    | 51         |

| •  | 2.1.1 The Attraction of GaAs for High Speed Applications                   | 51         |

|    | 2.1.2 The Energy Band Structure of GaAs                                    | <b>5</b> 3 |

|    | 2.1.3 Metal Semiconductor Contacts                                         | 55         |

|    | (i) The Schottky contact                                                   | 56         |

|    | (ii) Ohmic contacts                                                        | 57         |

|    | 2.2 GaAs MESFETs                                                           | 58         |

|    | 2.2.1 Modelling of GaAs MESFETs                                            | 58         |

|    | (i) DC Models                                                              | 59         |

|    | (ii) AC Models of GaAs MESFETs                                             | 64         |

|    | 2.3 GaAs Optical Devices                                                   | 68         |

|    | 2.3.1 Identification of Suitable Photodetectors                            | 69         |

|    | 2.4 Metal-Semiconductor-Metal Photodetectors                               | 70         |

|    | 2.4.1 Energy Band Description                                              | 70         |

|    | 2.4.2 Optical Properties                                                   | 72         |

|    | 2.4.3 Pulse response                                                       | <b>7</b> 3 |

|    |                                                                            |            |

| 3. | CIRCUIT DESIGN                                                             |            |

|    | 3.1 Fundamentals of Sample and Hold Circuits                               | 76         |

|    | 3.2 Series Photoconductive OS/H                                            | 79         |

|    | 3.3 Series MESFET Sample and Hold Circuit                                  | 81         |

|    | 3.3.1 Detailed Analysis of Pass Transistor Circuit                         | 84         |

|    | (i) Analogue bandwidth and acquisition time                                |            |

|    | (ii) Pedestal                                                              | 85         |

|    | (iii) Sampling Time Adjustment                                             | 87         |

|    | 3.4 Diode Bridge Sample and Hold Circuit                                   | 88         |

|    | 3.4.1 Principle of the Current-Steering Diode-Bridge S/H Circuit           | 8          |

|    | 3.4.2 Optically Controlled Diode Bridge S/H                                | 90         |

|    | 3.4.3 Fully Integrated Diode Bridge OS/H                                   | 92         |

|    | 51216 2 411. J 21116 2 1 1 4 6 6 6 7 1 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |            |

|    | 3.4.4 Detailed Description of the Diode Bridge Circuit                     |            |

|    | (ii) Acquisition Time                         | 97  |

|----|-----------------------------------------------|-----|

|    | (iii) Pedestal                                | 99  |

|    | (iv) Sampling Time Adjustment                 | 101 |

|    | 3.5 Current Sources                           | 102 |

|    | 3.5.1 Simple Current Source                   | 102 |

|    | 3.5.2 Cascoded Current Source                 | 103 |

|    | 3.5.3 Diode Biased Current Source             | 104 |

|    | 3.5.4 Tuneable Negative Current Sources       | 105 |

|    | 3.5.5 High Impedance Negative Current Sources | 106 |

|    | 3.6 Unity Gain Buffer                         | 108 |

|    |                                               |     |

| 4. | IC FABRICATION                                |     |

|    | 4.1 The GEC-Marconi F20 GaAs Foundry Process  |     |

|    | 4.1.1 GaAs MMIC Devices                       | 111 |

|    | (i) The GaAs MESFET                           | 111 |

|    | (ii) Inductors                                |     |

|    | (iii) Capacitors                              |     |

|    | (iv) Resistors                                |     |

|    | 4.2 IC Layout                                 |     |

|    | 4.2.1 Unity Gain Buffer                       | 114 |

|    | 4.2.2 Series Photoconductor OS/H              |     |

|    | 4.2.3 Series MESFET OS/H                      | 116 |

|    | 4.2.4 Diode bridge OS/H                       | 117 |

|    | 4.2.5 Electronic test structures              | 119 |

|    | 4.2.6 Optical test structures                 |     |

|    | 4.3 Packaging and PCBs                        | 120 |

| 5  | MEASURED RESULTS                              | 122 |

| ٥. | 5.1 Circuit Building Blocks                   |     |

|    | 5.1.1 Unity Gain Buffer                       |     |

|    | (i) Frequency Response                        |     |

|    | (ii) Step Response                            |     |

|    | (iii) Output Impedance                        |     |

|    | (iv) Harmonic Distortion                      |     |

|    | (10) Thirmonic Distortion                     |     |

| 5.1.2 Current Sources                            | 128 |

|--------------------------------------------------|-----|

| 5.1.3 MSM Photodetectors                         | 129 |

| (i) DC response                                  | 129 |

| (ii) Pulse response                              | 130 |

| 5.2 Optically Triggered Sample and Hold Circuits | 131 |

| 5.2.1 Series Photoconductor OS/H                 | 133 |

| (i) Analogue Bandwidth                           | 133 |

| (ii) Pulsed Measurements                         | 134 |

| 5.2.2 Series MESFET OS/H                         | 135 |

| (i) Simulation of Operation at 250Ms/s           | 136 |

| (ii) Measured Operation at 250Ms/s               | 137 |

| (iii) Simulation of Harmonic Distortion          | 139 |

| (iv) Measured Harmonic distortion                | 140 |

| (v) Simulated Pedestal                           | 141 |

| (vi) Measured Pedestal and droop                 | 142 |

| (vi) Simulated Bandwidth                         | 143 |

| (vii) Measured Bandwidth                         | 143 |

| (ix) Simulated Acquisition Time                  | 144 |

| (x) Measured Acquisition Time                    | 145 |

| (xi) Simulated Sampling Time Adjustment          | 147 |

| (xii) Measured Sampling time adjustment          | 148 |

| (xiii) Aperture jitter                           | 149 |

| 5.2.3 Diode Bridge OS/H                          | 150 |

| (i) Simulation of Operation at 250Ms/s           | 151 |

| (ii) Simulation of Harmonic Distortion           | 152 |

| (iii) Pedestal                                   | 152 |

| (iv) Frequency Response                          | 153 |

| (v) Acquisition Time                             | 154 |

| (vi) Sampling time adjustment                    | 154 |

| 5.2.4 Measured Performance of Diode Bridge OS/H  | 155 |

| 5.3 Summary and Conclusions                      | 157 |

| NONUNIFORMLY SAMPLED SIGNALS:                    | 158 |

| 6.1 Spectra of Sampled Signals                   | 158 |

| 6.1.1 Spectrum of N-path Interleaved Sampler     | 160 |

6.

| 6.1.2 Sampling with non-uniform intervals                 | 162 |

|-----------------------------------------------------------|-----|

| 6.2 Sampling Time Offset Estimation Algorithm             | 164 |

| 7. OPTOELECTRONIC INTEGRATION                             | 168 |

| 7.1 Waveguides on GaAs                                    | 169 |

| 7.1.1 Lattice Matched Waveguides                          | 169 |

| 7.1.2 Polymer Waveguides                                  | 171 |

| 7.1.3 Coupling of Integrated Waveguides to Photodetectors | 172 |

| 7.2 Integrated Optic Spiral Delay Lines                   | 172 |

| 7.3 Conclusions                                           | 175 |

| 8. CONC! USIONS AND SUGGESTIONS FOR FURTHER WORK          | 176 |

| 8.1 Summary and Conclusions of Thesis                     | 176 |

| 8.2 Suggestions for Further Work                          | 179 |

| 8.2.1 Optically Triggered S/H Circuits                    | 179 |

| 8.2.2 N-path Optically Triggered ADC                      | 184 |

| 8.2.3 Optoelectronic integration                          | 184 |

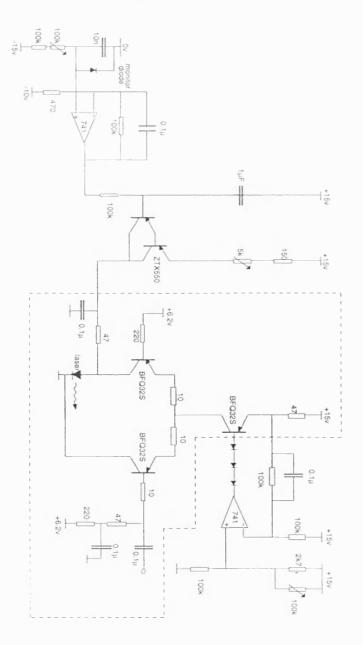

| APPENDIX 1: LASER DRIVE CIRCUIT                           | 185 |

| APPENDIX 2: TERMINOLOGY RELATED TO THE PERFORMANCE OF S/H |     |

| CIRCUITS                                                  | 186 |

| A2.1 Sample Period                                        | 186 |

| A2.2 Acquisition Time                                     | 186 |

| A2.3 Settling Time                                        | 186 |

| A2.4 Aperture Time and Aperture Uncertainty               | 187 |

| A2.5 Effective Sampling Instant and Aperture Jitter       | 187 |

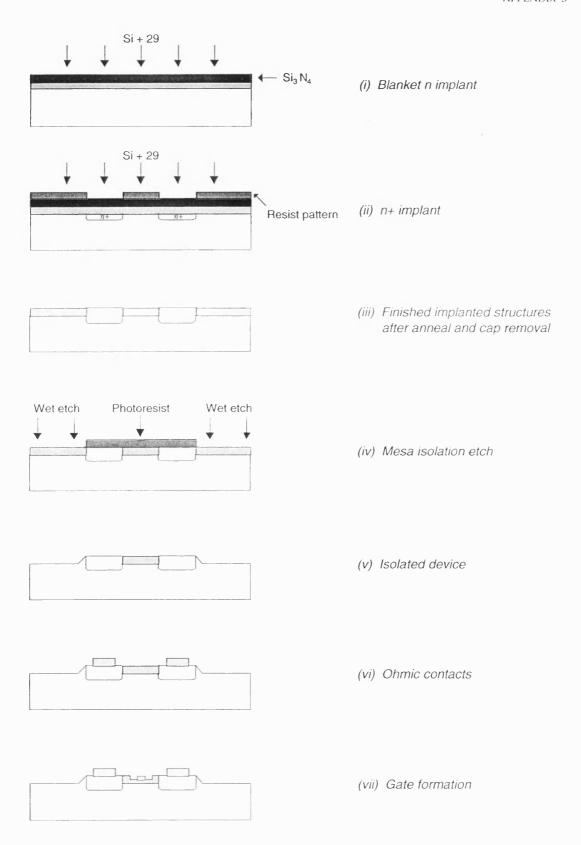

| APPENDIX 3: GEC-MARCONI F20 FOUNDRY PROCESS               | 188 |

| A3.1 Process Description                                  | 188 |

| Paraparage                                                | 100 |

# LIST OF FIGURES

### CHAPTER 1

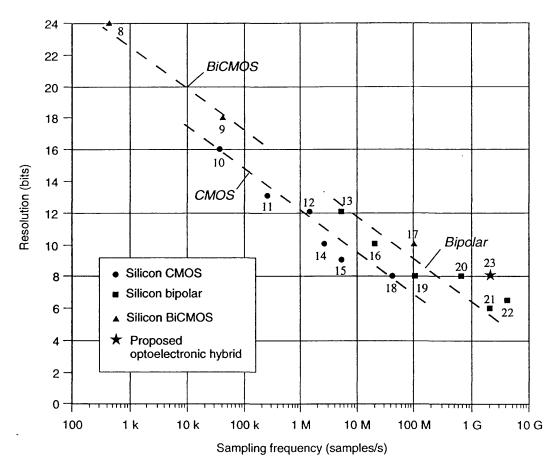

| Fig 1.1  | Comparison of high-performance ADCs in terms of resolution versus sampling             |            |

|----------|----------------------------------------------------------------------------------------|------------|

|          | frequency, for various technologies. Ref. [23] shows the performance which should      |            |

|          | be attainable from the proposed hybrid optoelectronic A/D converter                    | 19         |

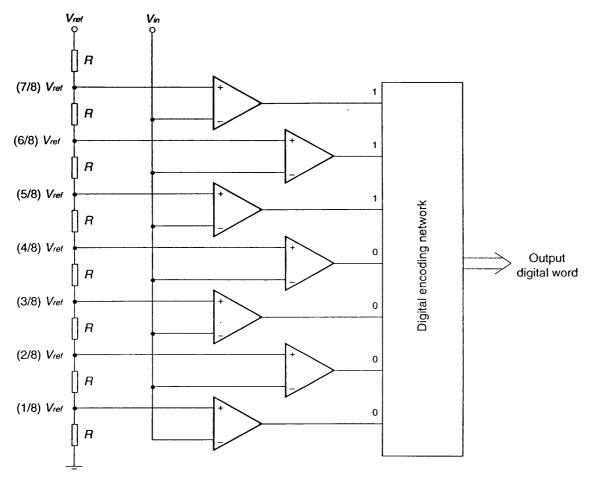

| Fig 1.2  | A 3-bit parallel A/D converter. This compares the input signal with the chain of       |            |

|          | reference voltages and produces a digital output in a single clock cycle2              | 21         |

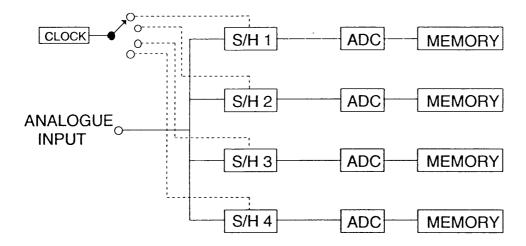

| Fig 1.3  | Time interleaved analogue to digital converter. The input signal is sampled by         |            |

|          | each S/H circuit in turn, effectively increasing the sample rate by the number of      |            |

|          | paths. After the digitised signals are stored, the outputs from the memories can be    |            |

|          | recombined and manipulated as required2                                                | 22         |

| Fig 1.4  | Typical issues important in high speed electrical layout topology2                     | <u>2</u> 4 |

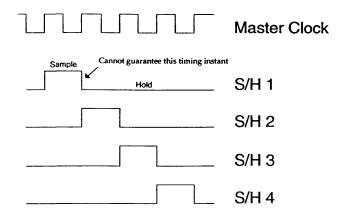

| Fig 1.5  | Clocking scheme of a 4-path ADC. Electronic counters and delays driven by a            |            |

|          | single clock provide the timing for each of the paths. This introduces noise which     |            |

|          | contributes to timing jitter.                                                          | 25         |

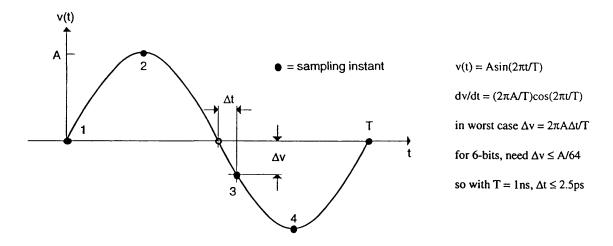

| Fig 1.6  | Effect of uneven sampling in an interleaved ADC. By sampling at a time $\Delta t$ away |            |

|          | from the correct sampling instant, an error $\Delta v$ is introduced                   | 25         |

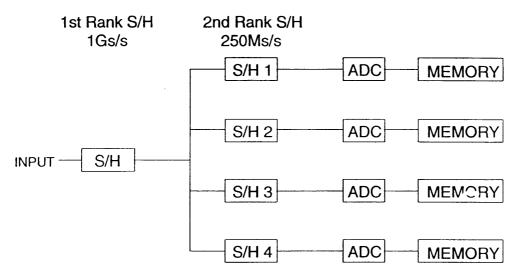

| Fig 1.7  | Two rank interleaved ADC. The 1st rank S/H circuit relaxes the timing                  |            |

|          | requirements                                                                           | 26         |

| Fig 1.8  | Plot of the squared Bessel functions of 0th and 1st order. These are the intensities   |            |

|          | that are received by the photodetectors at the 0th and 1st order diffraction patterns  |            |

|          | in the electro-optic diffraction modulator ADC.                                        | 28         |

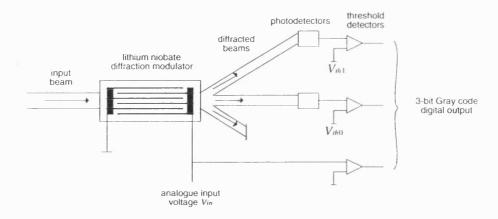

| Fig 1.9  | Electro-Optic ADC based on a diffraction modulator. By thresholding the output         |            |

|          | from the photodetectors, a digital representation of the input signal is produced 2    | 29         |

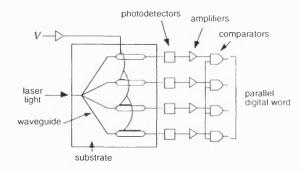

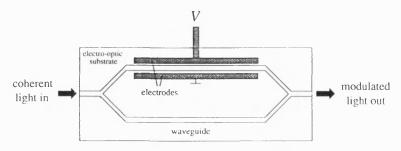

| Fig 1.10 | Mach-Zehnder optical ADC. This consists of four interferometric modulators with        |            |

|          | electrodes which increase in length in a binary sequence                               | 30         |

| Fig 1.11 | Mach-Zehnder interferometric modulator. This is the basic component of the             |            |

|          | interferometric A/D converter                                                          | 30         |

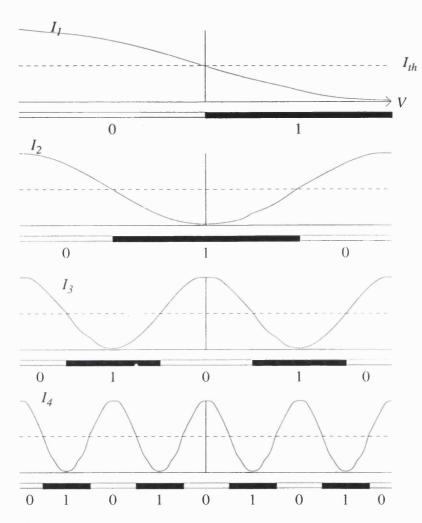

| Fig 1.12 | Intensity versus voltage plot for a 4-bit Mach-Zehnder ADC with Gray code              |            |

|          | output.                                                                                | 31         |

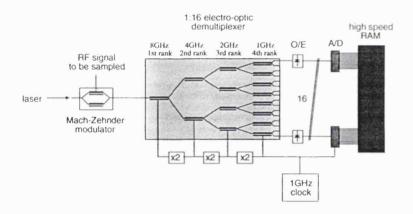

| Fig 1.13 | Electro-optic ADC based upon an optical time division multiplexer                      | 13         |

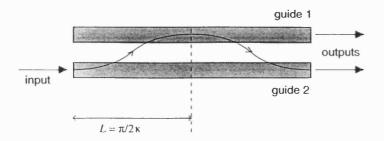

| Fig 1.14 | Electro-optic directional coupler (electrodes not shown)                               | 34         |

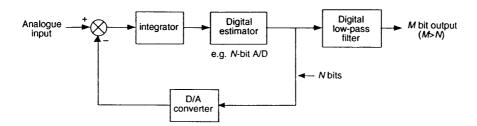

| A basic oversampled ADC block diagram. This generates a course in bit digital                                                                |                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| estimate at a very high sampling rate which is then converted to a high resolution                                                           |                                                                                                                                                                             |

| representation at a lower sampling rate by the digital low-pass filter.                                                                      | . 36                                                                                                                                                                        |

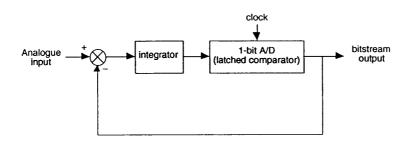

| 1-bit sigma-delta converter. This is a simplified version of the N-bit modulator                                                             |                                                                                                                                                                             |

| shown in Fig 1.15                                                                                                                            | . 37                                                                                                                                                                        |

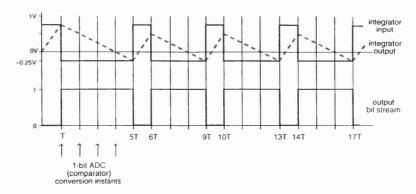

| Timing diagram of the 1-bit $\Sigma$ - $\Delta$ with a DC input. The 0.75V input produces a                                                  |                                                                                                                                                                             |

| bitstream output whose time average value is 0.75V                                                                                           | . 3                                                                                                                                                                         |

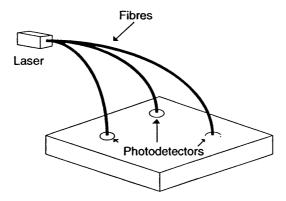

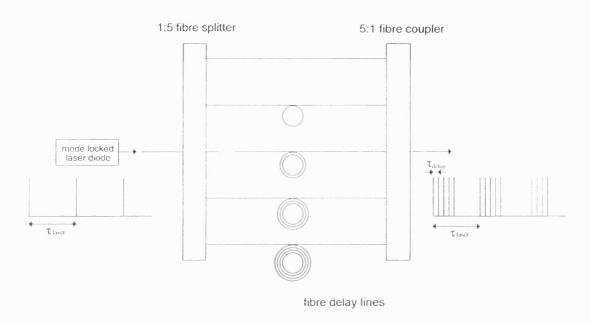

| Distribution of an optical clock signal by means of fibres.                                                                                  | . 43                                                                                                                                                                        |

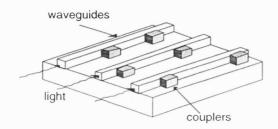

| Distribution of clock by means of integrated optical waveguides.                                                                             | . 4                                                                                                                                                                         |

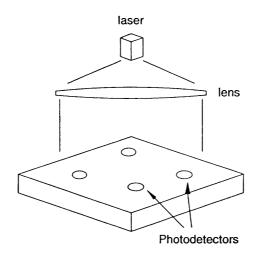

| Free-space optical clock distribution.                                                                                                       | . 4                                                                                                                                                                         |

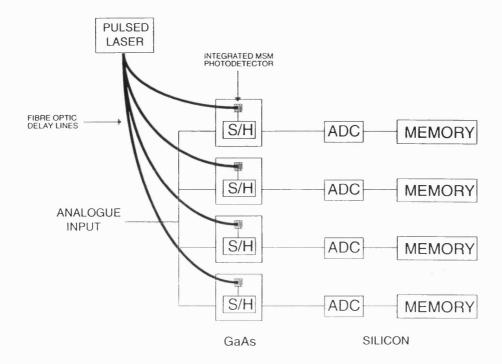

| Proposed optically triggered ADC. By replacing the electronic clock with an optical                                                          |                                                                                                                                                                             |

| clock distribution scheme problems with timing jitter are largely eliminated                                                                 | . 46                                                                                                                                                                        |

|                                                                                                                                              |                                                                                                                                                                             |

| TER 2                                                                                                                                        |                                                                                                                                                                             |

|                                                                                                                                              |                                                                                                                                                                             |

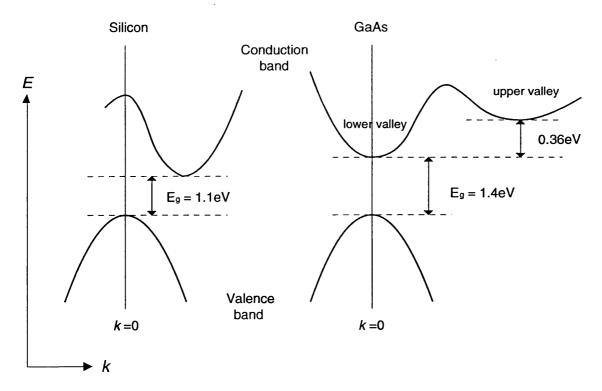

|                                                                                                                                              | . 53                                                                                                                                                                        |

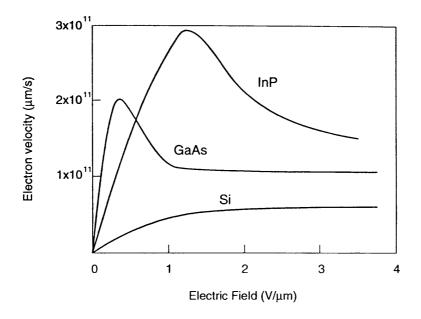

| Drift velocity as a function of electric field for Si, GaAs and InP. This shows that at                                                      |                                                                                                                                                                             |

| E-fields above $1V/\mu m$ the electron velocity in GaAs is only about 1.4 times that in                                                      |                                                                                                                                                                             |

| silicon                                                                                                                                      | -55                                                                                                                                                                         |

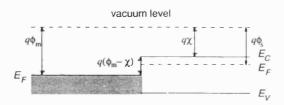

| Energy band diagrams of a metal and a semiconductor in isolation                                                                             | 56                                                                                                                                                                          |

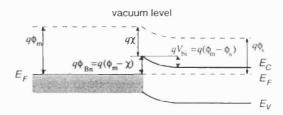

| Energy band diagram of a metal-semiconductor contact                                                                                         | . 50                                                                                                                                                                        |

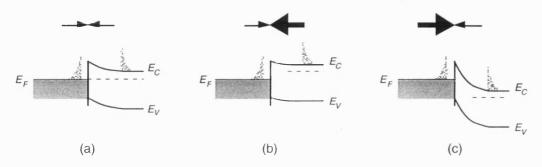

| Current transport across a metal-semiconductor junction by thermionic emission                                                               |                                                                                                                                                                             |

| process                                                                                                                                      | . 52                                                                                                                                                                        |

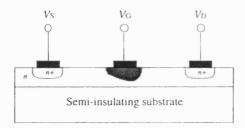

| Schematic of a MESFET. Application of a negative voltage at the gate forms a                                                                 |                                                                                                                                                                             |

| depletion region which progressively restricts channel conduction.                                                                           | . 58                                                                                                                                                                        |

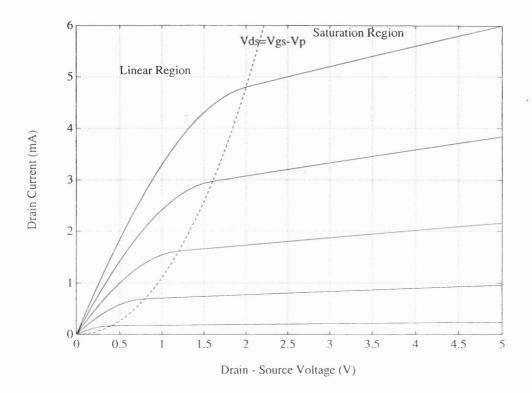

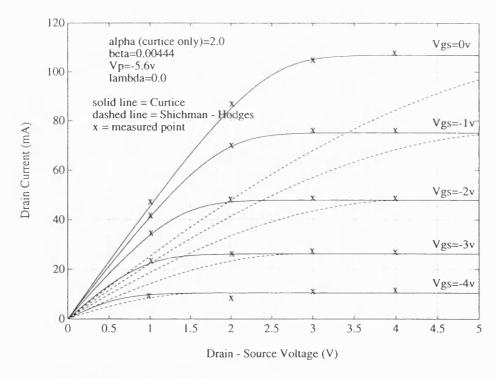

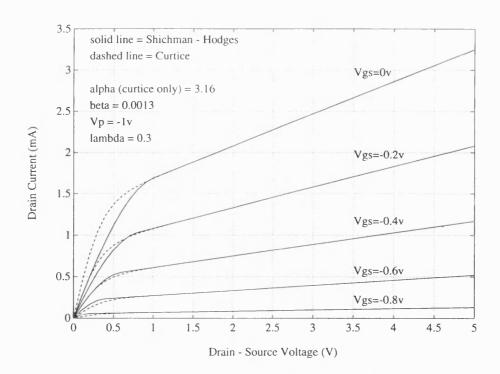

| Shichman-Hodges model of FET. This is a graphical representation of equations                                                                |                                                                                                                                                                             |

|                                                                                                                                              |                                                                                                                                                                             |

| (2.5 – 2.7), showing the linear and saturation regions. ( $\beta = 1 \text{mA/V}^2$ , $\lambda = 0.1 \text{ V}^{-1}$ ,                       |                                                                                                                                                                             |

|                                                                                                                                              | 60                                                                                                                                                                          |

| (2.5 – 2.7), showing the linear and saturation regions. ( $\beta = 1 \text{mA/V}^2$ , $\lambda = 0.1 \text{ V}^{-1}$ ,                       | 60                                                                                                                                                                          |

| (2.5 – 2.7), showing the linear and saturation regions. ( $\beta = 1 \text{mA/V}^2$ , $\lambda = 0.1 \text{ V}^{-1}$ , $V_p = -2 \text{V}$ ) |                                                                                                                                                                             |

| (2.5 – 2.7), showing the linear and saturation regions. ( $\beta$ = 1mA/V², $\lambda$ = 0.1 V <sup>-1</sup> , $V_p$ = –2V)                   |                                                                                                                                                                             |

| (2.5 – 2.7), showing the linear and saturation regions. ( $\beta$ = 1mA/V <sup>2</sup> , $\lambda$ = 0.1 V <sup>-1</sup> , $V_p$ = -2V)      |                                                                                                                                                                             |

| (2.5 – 2.7), showing the linear and saturation regions. ( $\beta$ = 1mA/V², $\lambda$ = 0.1 V <sup>-1</sup> , $V_p$ = –2V)                   |                                                                                                                                                                             |

|                                                                                                                                              | representation at a lower sampling rate by the digital low-pass filter.  1-bit sigma-delta converter. This is a simplified version of the N-bit modulator shown in Fig 1.15 |

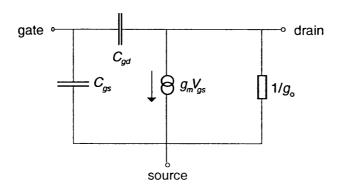

| Fig 2.10                                                                                           | MESFET small signal equivalent circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64                                                 |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

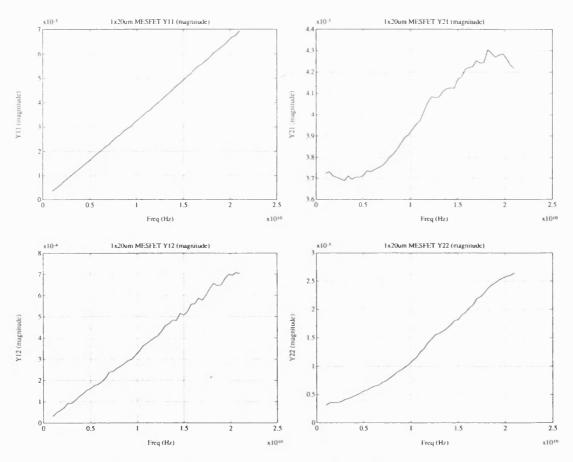

| Fig 2.11                                                                                           | Measured Y-parameters of a 20µm MESFET fabricated with the GEC-Marconi F20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |

|                                                                                                    | process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66                                                 |

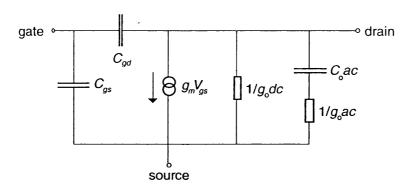

| Fig 2.12                                                                                           | Dispersive small-signal equivalent circuit. The components $C_0ac$ and $g_0ac$ simulate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |

|                                                                                                    | the low frequency transient effects observed in GaAs MESFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67                                                 |

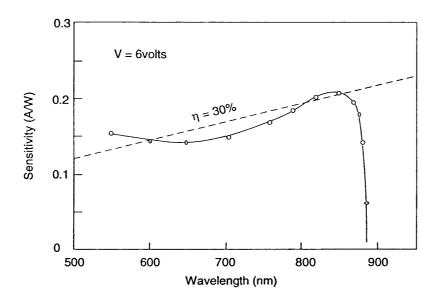

| Fig 2.13                                                                                           | Spectral response of a GaAs MSM-PD showing long wavelength cut-off at ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |

|                                                                                                    | 870nm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69                                                 |

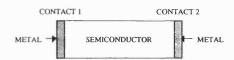

| Fig 2.14                                                                                           | Structure of a metal-semiconductor-metal diode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71                                                 |

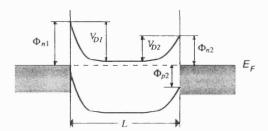

| Fig 2.15                                                                                           | Energy band diagram of an MSM diode showing the formation of potential barriers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |

|                                                                                                    | at the metal-semiconductor junctions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71                                                 |

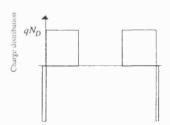

| Fig 2.16                                                                                           | Charge distribution of an MSM diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>7</b> 1                                         |

| Fig 2.17                                                                                           | Field distribution in an MSM diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>7</b> 1                                         |

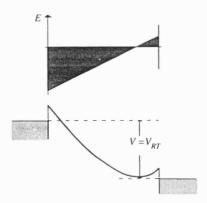

| Fig 2.18                                                                                           | MSM diode at the reach through voltage VRT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>7</b> 1                                         |

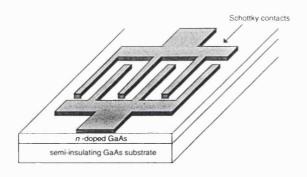

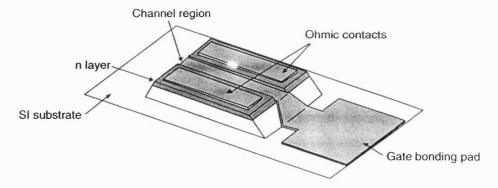

| Fig 2.19                                                                                           | Planar MSM photodetector, consisting of Schottky metal fingers placed directly on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                    |

|                                                                                                    | the lightly doped substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72                                                 |

| OTT A DO                                                                                           | rep 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |

| CHAP                                                                                               | IERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |

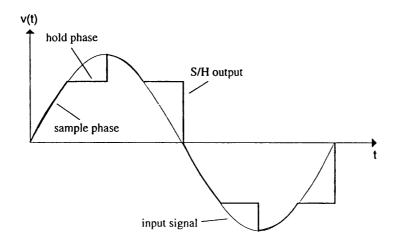

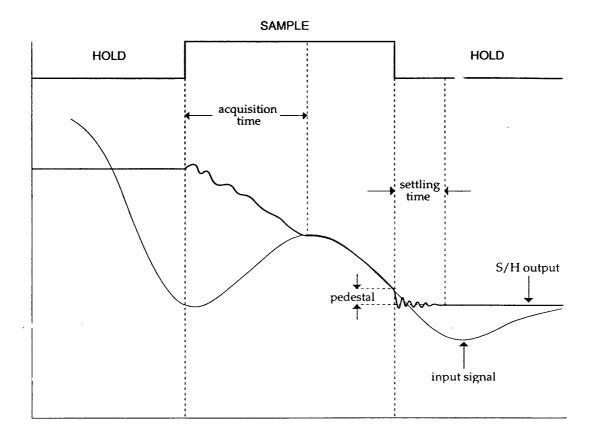

| Fig 3.1                                                                                            | The operation of an ideal sample and hold circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <i>7</i> 7                                         |

|                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |

| Fig 3.1                                                                                            | The operation of an ideal sample and hold circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

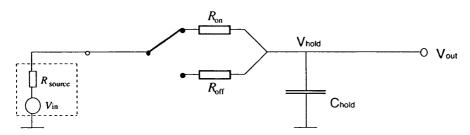

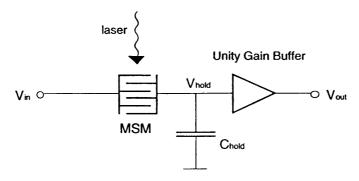

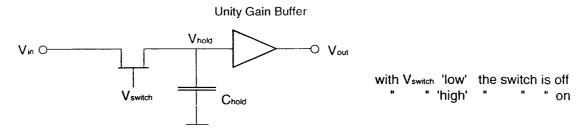

| Fig 3.1<br>Fig 3.2                                                                                 | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77                                                 |

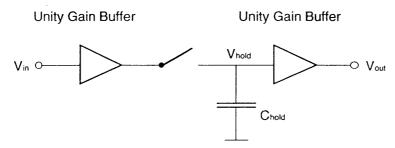

| Fig 3.1<br>Fig 3.2                                                                                 | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77                                                 |

| Fig 3.1<br>Fig 3.2<br>Fig 3.3                                                                      | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the output load, and provides a low impedance source to drive the sampling gate                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77<br>78                                           |

| Fig 3.1<br>Fig 3.2<br>Fig 3.3                                                                      | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the output load, and provides a low impedance source to drive the sampling gate  Common terminology used to describe the performance of S/H circuits. A more                                                                                                                                                                                                                                                                                                                                                          | 77<br>78<br>79                                     |

| Fig 3.1<br>Fig 3.2<br>Fig 3.3<br>Fig 3.4                                                           | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the output load, and provides a low impedance source to drive the sampling gate  Common terminology used to describe the performance of S/H circuits. A more detailed account can be found in appendix 2 and in [148].                                                                                                                                                                                                                                                                                                | 77<br>78<br>79<br>80                               |

| Fig 3.1 Fig 3.2 Fig 3.3 Fig 3.4 Fig 3.5                                                            | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the output load, and provides a low impedance source to drive the sampling gate  Common terminology used to describe the performance of S/H circuits. A more detailed account can be found in appendix 2 and in [148]  Series photoconductive optoelectronic sample and hold circuit                                                                                                                                                                                                                                  | 77<br>78<br>79<br>80<br>81                         |

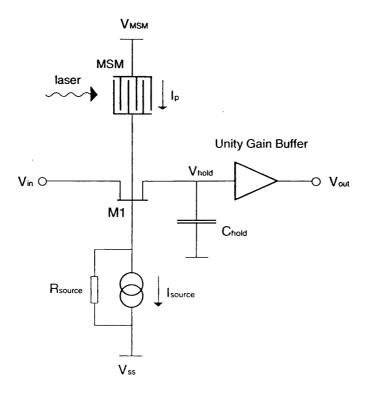

| Fig 3.1 Fig 3.2 Fig 3.3 Fig 3.4 Fig 3.5 Fig 3.6                                                    | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the output load, and provides a low impedance source to drive the sampling gate  Common terminology used to describe the performance of S/H circuits. A more detailed account can be found in appendix 2 and in [148]  Series photoconductive optoelectronic sample and hold circuit                                                                                                                                                                                                                                  | 77<br>78<br>79<br>80<br>81<br>83                   |

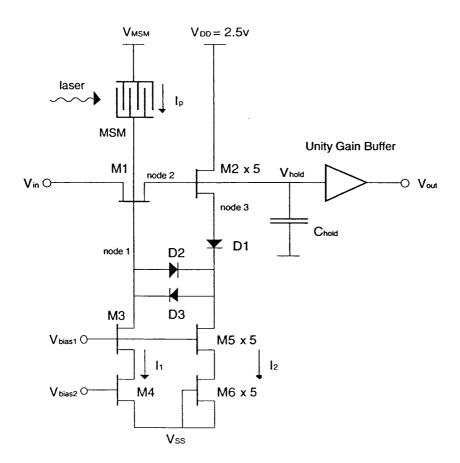

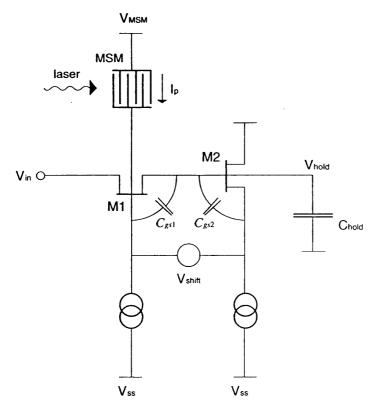

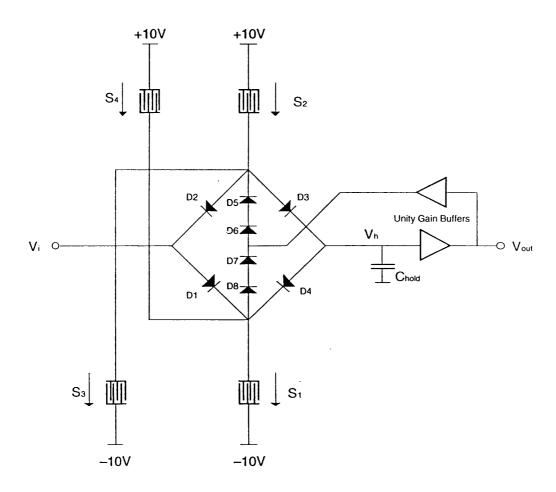

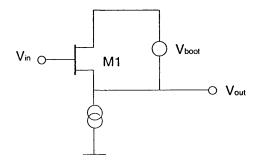

| Fig 3.1 Fig 3.2 Fig 3.3 Fig 3.4 Fig 3.5 Fig 3.6 Fig 3.7                                            | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the output load, and provides a low impedance source to drive the sampling gate  Common terminology used to describe the performance of S/H circuits. A more detailed account can be found in appendix 2 and in [148].  Series photoconductive optoelectronic sample and hold circuit.  Simplest all-electronic sample and hold circuit.                                                                                                                                                                              | 77<br>78<br>79<br>80<br>81<br>83<br>83             |

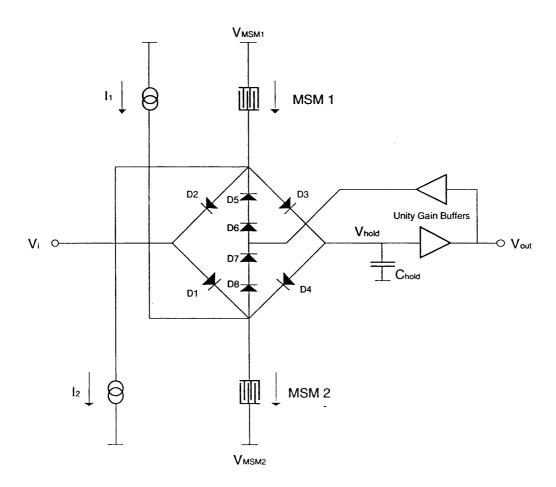

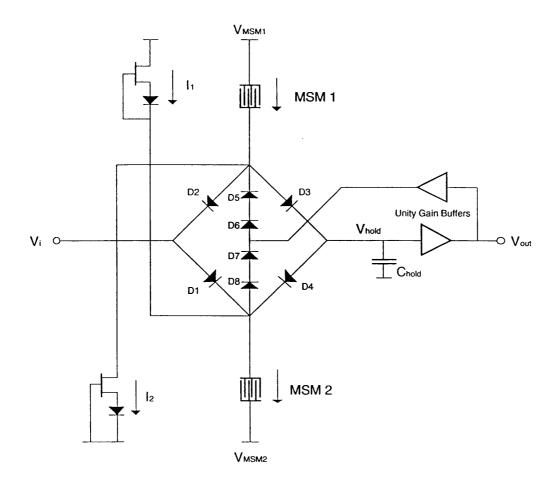

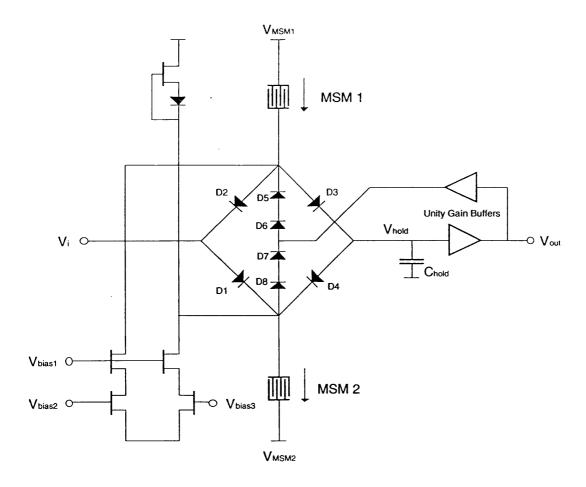

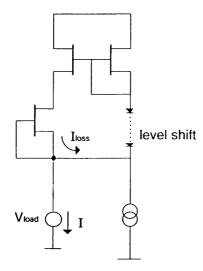

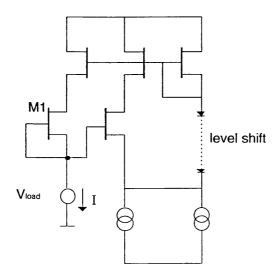

| Fig 3.1 Fig 3.2 Fig 3.3 Fig 3.4 Fig 3.5 Fig 3.6 Fig 3.7 Fig 3.8                                    | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the output load, and provides a low impedance source to drive the sampling gate  Common terminology used to describe the performance of S/H circuits. A more detailed account can be found in appendix 2 and in [148]  Series photoconductive optoelectronic sample and hold circuit.  Optically controlled series MESFET S/H circuit.  Series MESFET OS/H with diode clamping.                                                                                                                                       | 77<br>78<br>79<br>80<br>81<br>83<br>83<br>86       |

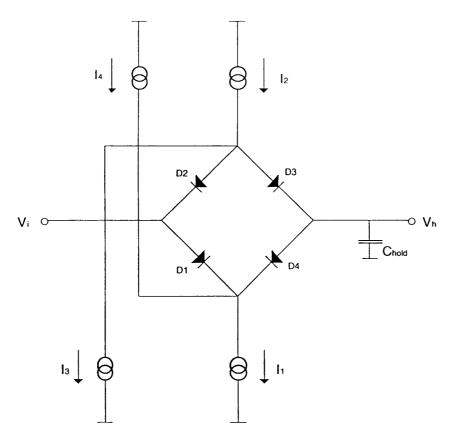

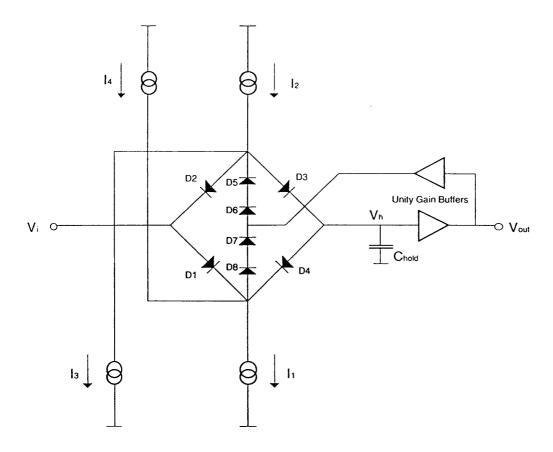

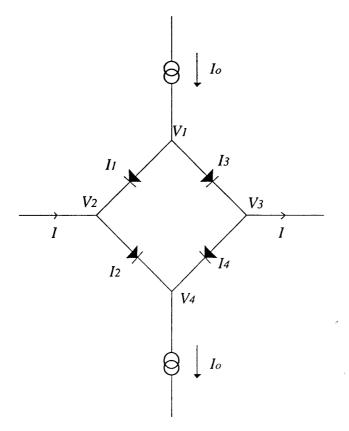

| Fig 3.1 Fig 3.2 Fig 3.3 Fig 3.4 Fig 3.5 Fig 3.6 Fig 3.7 Fig 3.8 Fig 3.9                            | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the output load, and provides a low impedance source to drive the sampling gate                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77<br>78<br>79<br>80<br>81<br>83<br>83<br>86<br>88 |

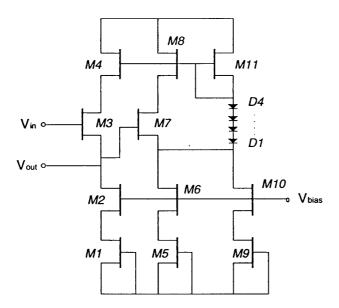

| Fig 3.1 Fig 3.2 Fig 3.3 Fig 3.4 Fig 3.5 Fig 3.6 Fig 3.7 Fig 3.8 Fig 3.9 Fig 3.10                   | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the output load, and provides a low impedance source to drive the sampling gate  Common terminology used to describe the performance of S/H circuits. A more detailed account can be found in appendix 2 and in [148].  Series photoconductive optoelectronic sample and hold circuit.  Simplest all-electronic sample and hold circuit.  Optically controlled series MESFET S/H circuit.  Series MESFET OS/H with diode clamping.  Simplified circuit for calculation of pedestal.  Simple diode bridge S/H circuit. | 77<br>78<br>79<br>80<br>81<br>83<br>86<br>88<br>90 |

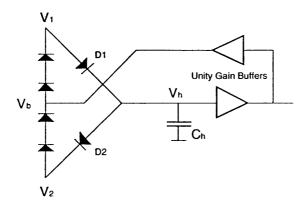

| Fig 3.1 Fig 3.2 Fig 3.3 Fig 3.4 Fig 3.5 Fig 3.6 Fig 3.7 Fig 3.8 Fig 3.9 Fig 3.10 Fig 3.11 Fig 3.12 | The operation of an ideal sample and hold circuit.  Simplest sample and hold realisation.  Buffered sample and hold circuit. This prevents discharging of Chold through the output load, and provides a low impedance source to drive the sampling gate                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77<br>78<br>79<br>80<br>81<br>83<br>86<br>88<br>90 |

| Fig 3.15 | Diode bridge OS/H with tuneable current sources.                                  | . 94  |

|----------|-----------------------------------------------------------------------------------|-------|

| Fig 3.16 | Simplified diode bridge S/H for circuit analysis.                                 | . 96  |

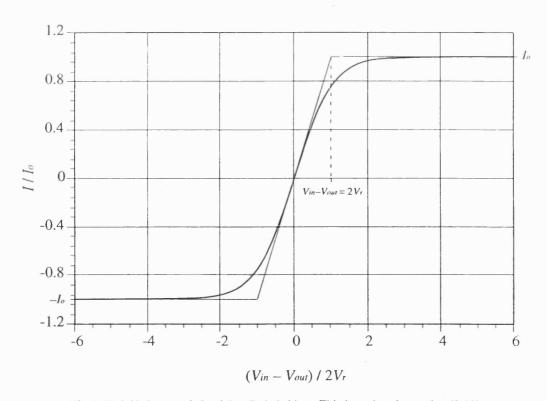

| Fig 3.17 | I–V characteristic of the diode bridge. This is a plot of equation (3.16)         | . 97  |

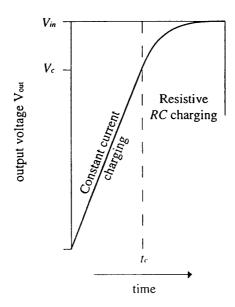

| Fig 3.18 | Response of the diode bridge S/H to a step input.                                 | . 98  |

| Fig 3.19 | Diode bridge half-circuit for calculation of pedestal.                            | . 100 |

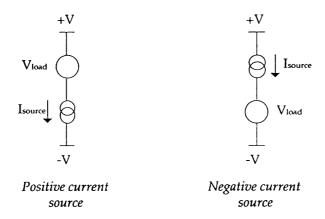

| Fig 3.20 | Definition of positive and negative current sources.                              | 102   |

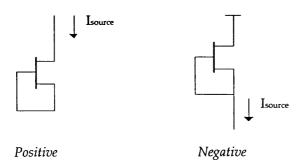

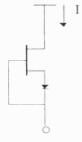

| Fig 3.21 | Simple MESFET current sources.                                                    | 102   |

| Fig 3.22 | Cascoded current source.                                                          | . 103 |

| Fig 3.23 | Cascoded current source used as negative source.                                  | 104   |

| Fig 3.24 | Diode biased current source.                                                      | 104   |

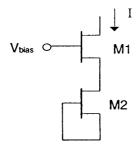

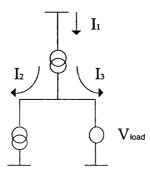

| Fig 3.25 | Tuneable negative current source. The lower source sinks I2, so the current       |       |

|          | through $V_{load}$ , $I_3 = I_1 - I_2$ .                                          | .105  |

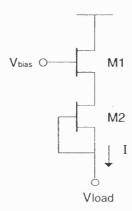

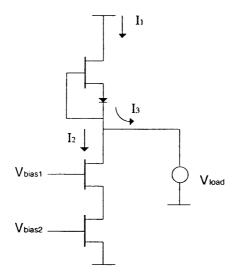

| Fig 3.26 | Complete tuneable negative current source.                                        | 106   |

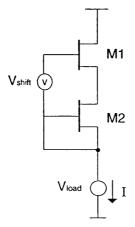

| Fig 3.27 | Bootstrapped current source.                                                      | 106   |

| Fig 3.28 | Current source bootstrapped using a diode level shift.                            | 107   |

| Fig 3.29 | Complete bootstrapped negative current source.                                    | 107   |

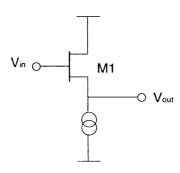

| Fig 3.30 | The simplest possible follower arrangement.                                       | 108   |

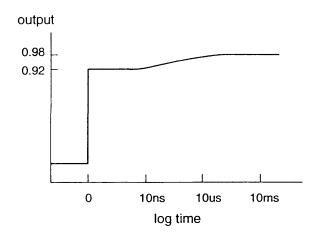

| Fig 3.31 | Time Domain step response of the simple follower circuit of Fig. 3.30             | 109   |

| Fig 3.32 | Bootstrapped Follower. This prevents the slow transient gain error of the simple  |       |

|          | follower circuit.                                                                 | 109   |

| Fig 3.33 | Final realisation of a bootstrapped follower circuit.                             | 110   |

| Снар     | ΓER 4                                                                             |       |

| Fig 4.1  | Schematic of a typical MESFET structure suitable for fabrication in a planar GaAs |       |

|          | MMIC process.                                                                     | 112   |

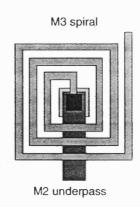

| Fig 4.2  | Spiral inductor suitable for fabrication in a planar GaAs MMIC process            | 112   |

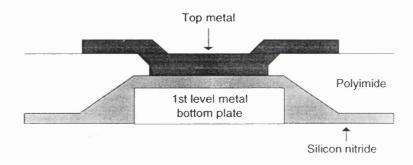

| Fig 4.3  | Section through a silicon nitride MIM capacitor                                   | 113   |

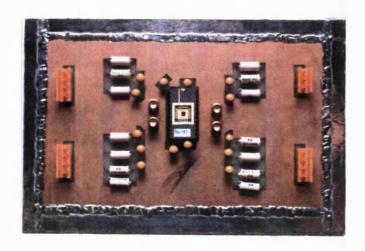

| Fig 4.4  | Photomicrograph of unity gain buffer.                                             | 115   |

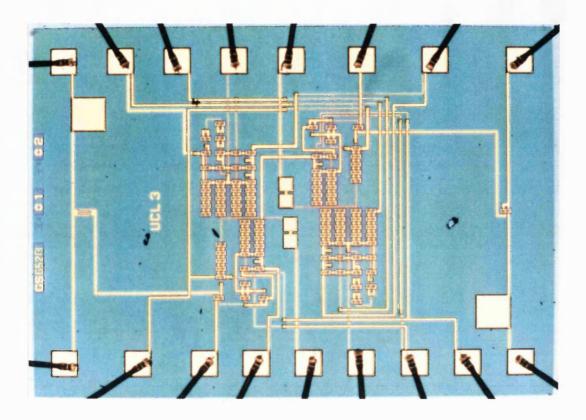

| Fig 4.5  | Photomicrograph of Auston switch OS/H IC                                          | 116   |

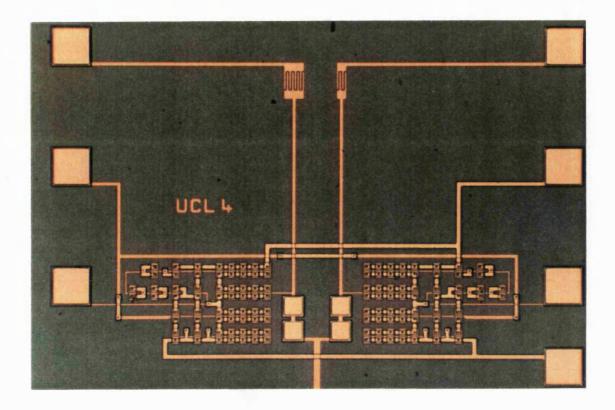

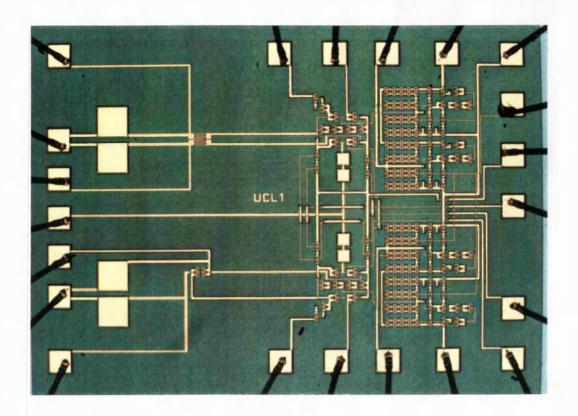

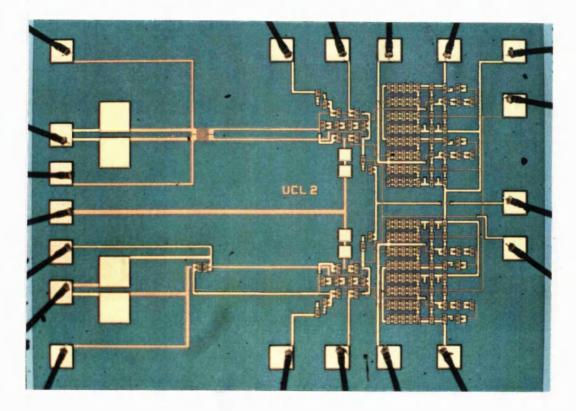

| Fig 4.6  | Photomicrograph of series MESFET OS/H IC.                                         | 117   |

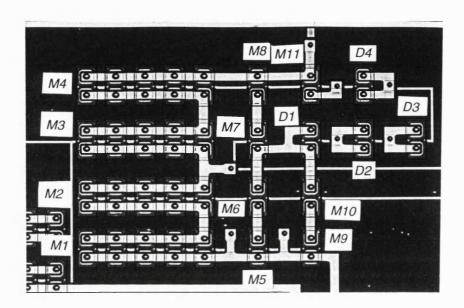

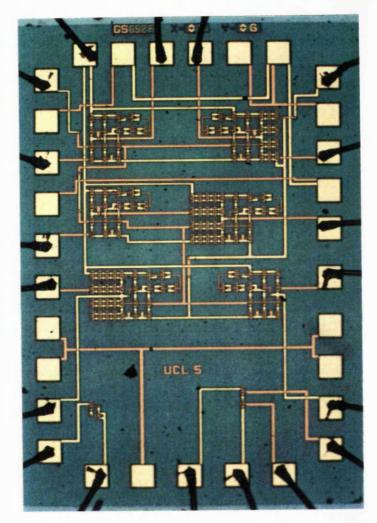

| Fig 4.7  | Photomicrograph of diode bridge OS/H IC (tuneable current sources)                | 118   |

| Fig 4.8  | Photomicrograph of diode bridge OS/H IC (fixed current sources)                   | 118   |

| Fig 4.9  | Photomicrograph of electronic test IC.                                            | 119   |

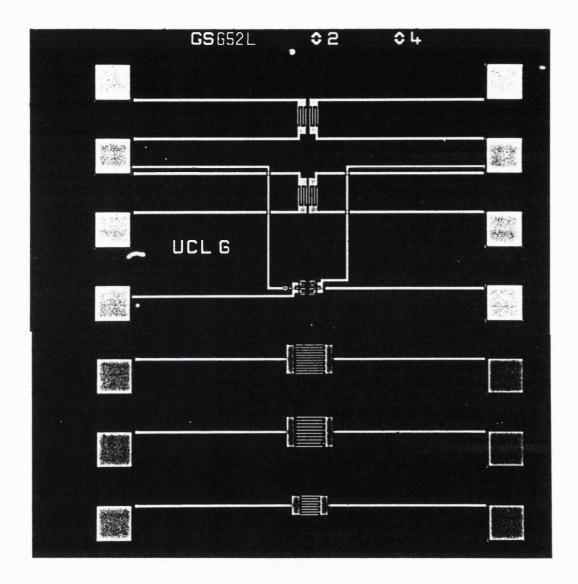

| Fig 4.10  | Photomicrograph of optical test IC.                                                                  | 120         |

|-----------|------------------------------------------------------------------------------------------------------|-------------|

| Fig 4.11a | Top side of a typical PCB used for testing the OS/H circuits.                                        | 122         |

| Fig 4.11b | Bottom side of a typical PCB used for testing the OS/H circuits                                      | 122         |

| Снар      | TER 5                                                                                                |             |

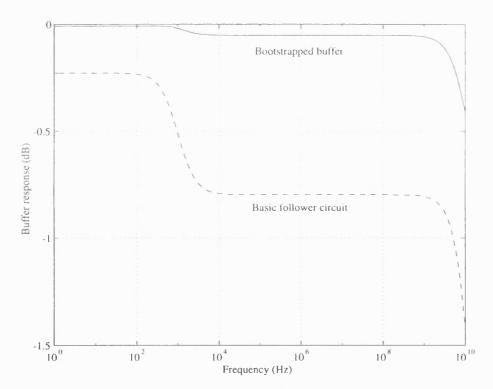

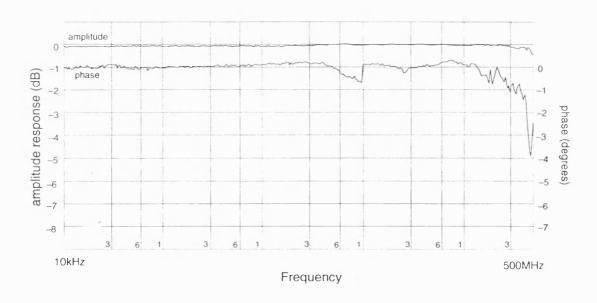

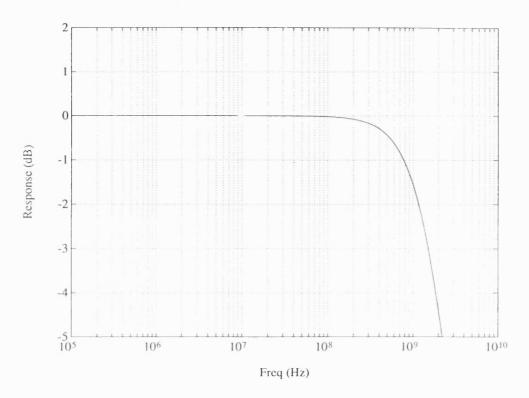

| Fig 5.1   | Simulated frequency response of the unity gain buffer. This shows the effect of                      |             |

|           | frequency dependent drain conductance                                                                | 124         |

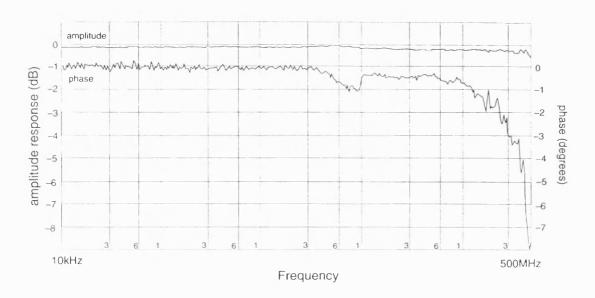

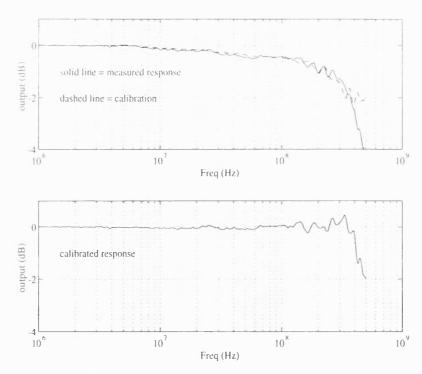

| Fig 5.2   | Measured Frequency response of buffer. The intrinsic buffer response can be found                    |             |

|           | by subtracting the calibration curve from the uncalibrated curve.                                    | <b>12</b> 5 |

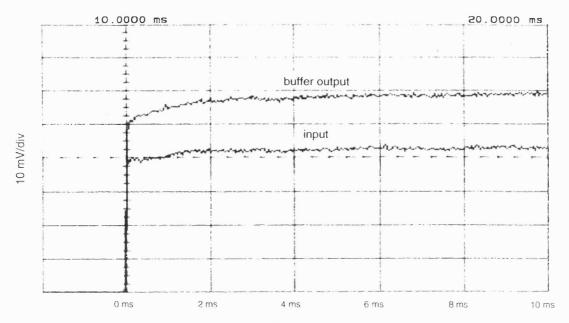

| Fig 5.3   | Step response of buffer. The output rises by < 0.75% over 10ms,                                      | 127         |

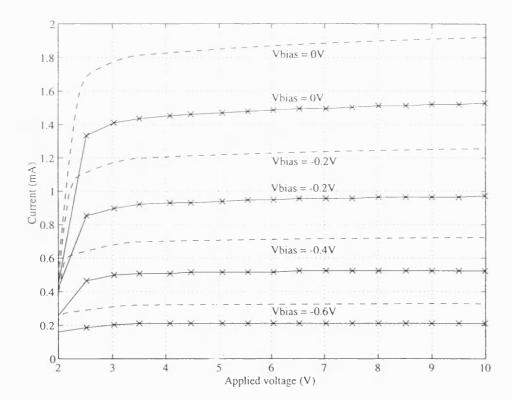

| Fig 5.4   | DC response of cascoded current source, solid line = measured response, dashed                       |             |

|           | line = simulated response. The slight difference between these suggests that the                     |             |

|           | actual value of MESFET beta is ~20% lower than expected                                              | 128         |

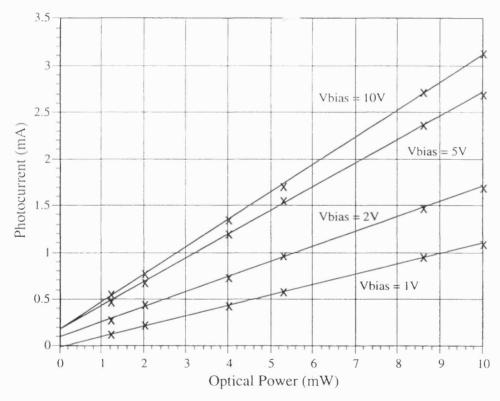

| Fig 5.5   | DC Response of a 60µm x 60µm MSM Photodetector.                                                      | <b>12</b> 9 |

| Fig 5.6   | Response of a 60µm x 60µm MSM to a 100MHz laser source.                                              | 130         |

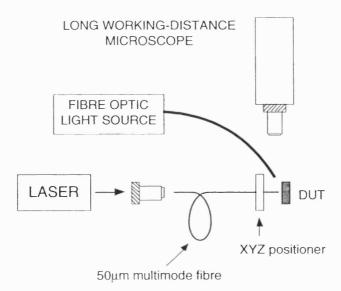

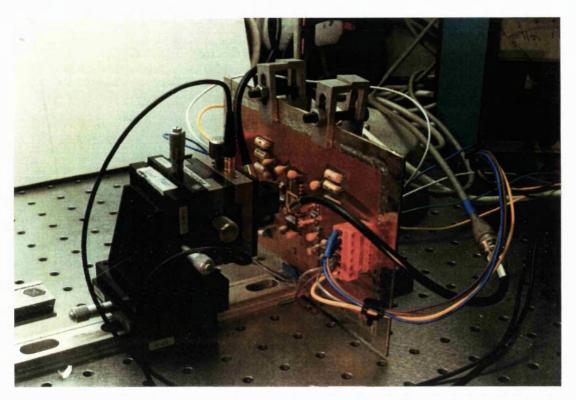

| Fig 5.7   | Experimental arrangement for OS/H measurements.                                                      | 131         |

| Fig 5.8   | Alignment of optical fibre with a test chip using piezo-electric positioners. The                    |             |

|           | long working-distance microscope is removed for clarity.                                             | 132         |

| Fig 5.9   | Series photoconductor OS/H shown sampling a 1MHz sinusoid at 5Ms/s. This is                          |             |

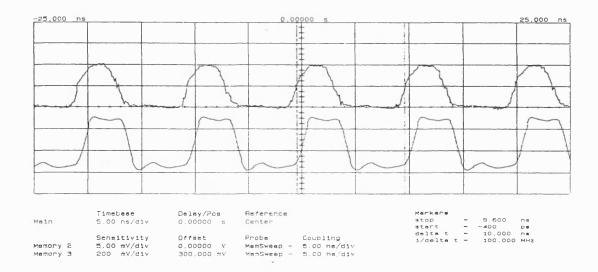

|           | the maximum rate at which the circuit can operate effectively.                                       | 134         |

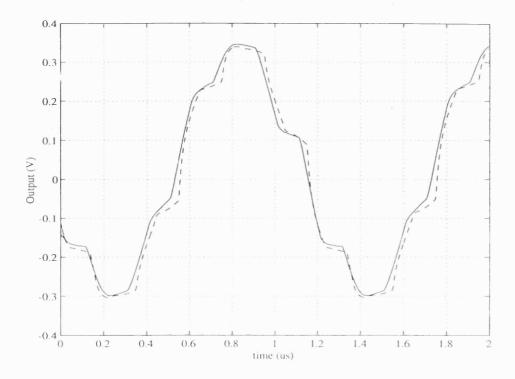

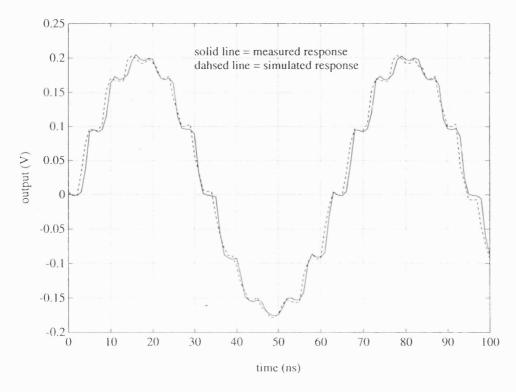

| Fig 5.10  | This shows the series photoconductor OS/H sampling a $833kHz$ signal at $5Ms/s$ , as                 |             |

|           | recorded by a digitizing oscilloscope. The solid trace is the measured response and                  |             |

|           | the dashed trace is a simulation.                                                                    | <b>13</b> 5 |

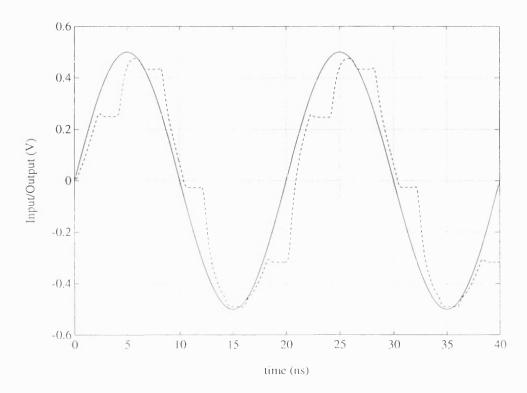

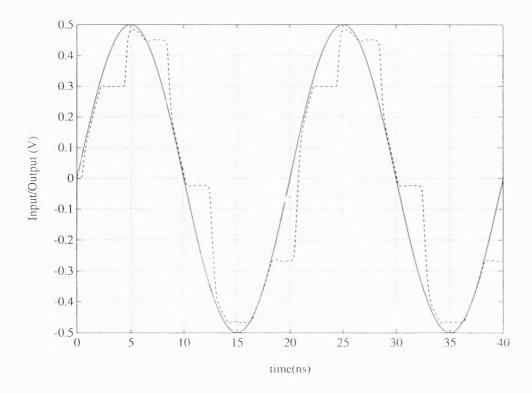

| Fig 5.11  | $\label{thm:main} \mbox{HSPICE simulation showing the series MESFET OS/H sampling a 50MHz sinusoid}$ |             |

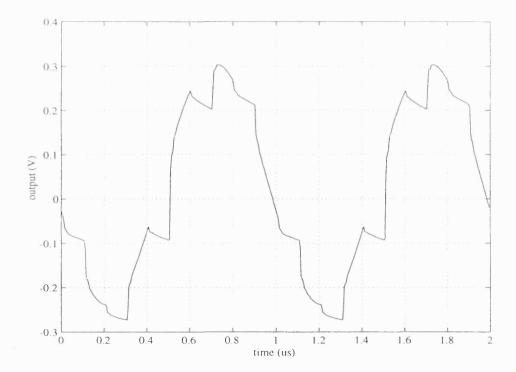

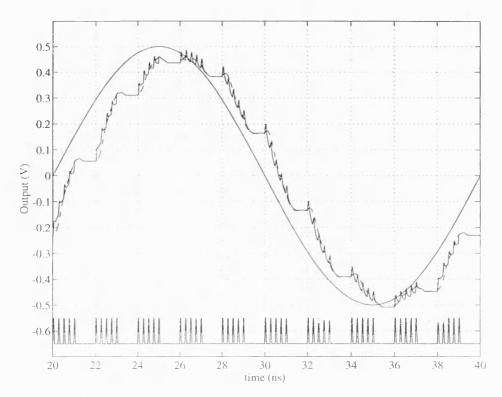

|           | at 250Ms/s                                                                                           | 136         |

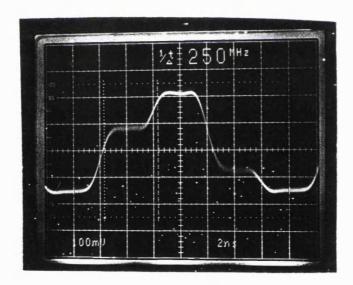

| Fig 5.12  | Scope photo of series MESFET OS/H sampling a 62.5MHz 0.4V input sinusoid at                          |             |

|           | 250Ms/s                                                                                              | 137         |

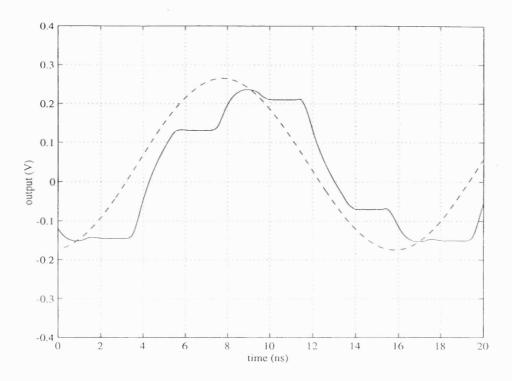

| Fig 5.13  | Simulation of series MESFET OS/H sampling a 62.5MHz input at 250Ms/s. This                           |             |

|           | shows very close agreement to the measured result in Fig. 5.13.                                      | 138         |

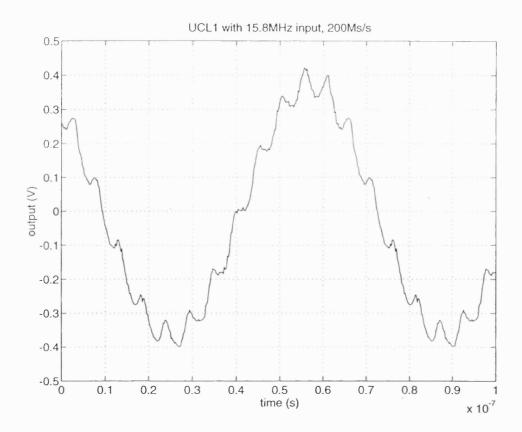

| Fig 5.14  | Digital scope record of the series MESFET OS/H sampling a 16.67MHz signal at                         |             |

|           | 200Ms.s                                                                                              | 138         |

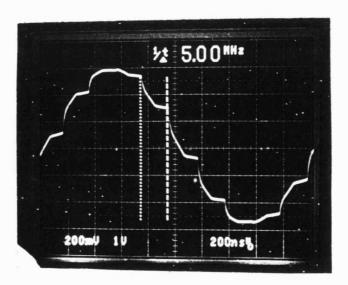

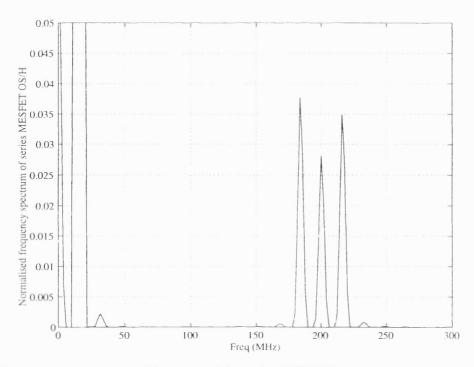

| Fig 5.15  | Frequency spectrum of the output of the series MESFET OS/H when sampling a                           |             |

|           | 16.67MHz signal at 200Ms/s. This clearly shows 2nd harmonic distortion at                            |             |

|          | 33MHz and clock feedthrough 200MHz.                                             | . 139 |

|----------|---------------------------------------------------------------------------------|-------|

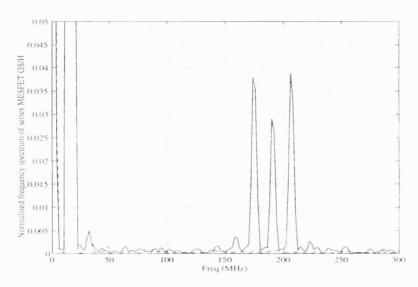

| Fig 5.16 | Measured frequency spectrum of the series MESFET OS/H with a 16.67MHz input     |       |

|          | sampled at 190Ms/s (the dashed line shows the circuit held in sample mode)      | . 140 |

| Fig 5.17 | Simulation of series MESFET OS/H sampling a 1MHz sinusoid at 5Ms/s              | . 141 |

| Fig 5.18 | Measured pedestal and droop of series MESFET OS/H                               | 142   |

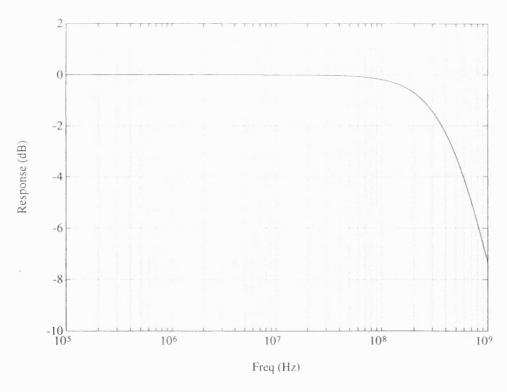

| Fig 5.19 | Simulation of the frequency response of the series MESFET OS/H in the sample    |       |

|          | mode                                                                            | . 143 |

| Fig 5.20 | Measured frequency response of the series MESFET OS/H.                          | . 144 |

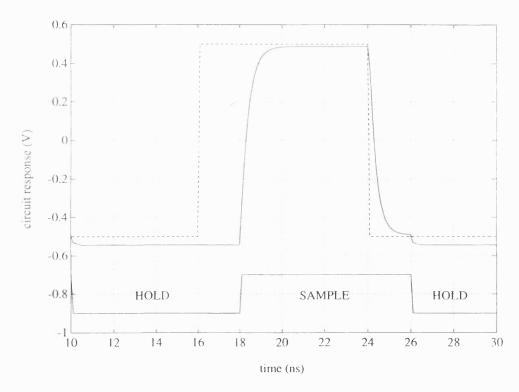

| Fig 5.21 | Simulation showing the acquisition of a 1V peak to peak square wave.            | 145   |

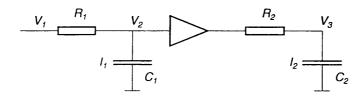

| Fig 5.22 | Equivalent circuit used to de-embed the OS/H time constant from the measuring   |       |

|          | system                                                                          | . 146 |

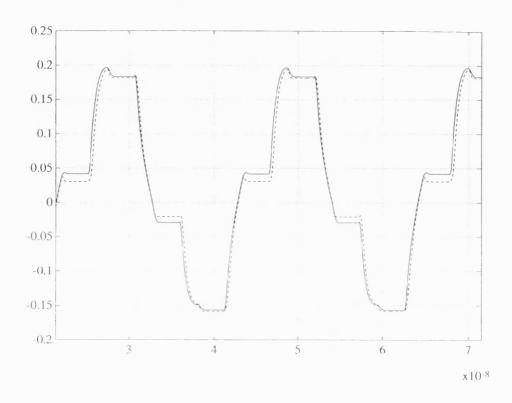

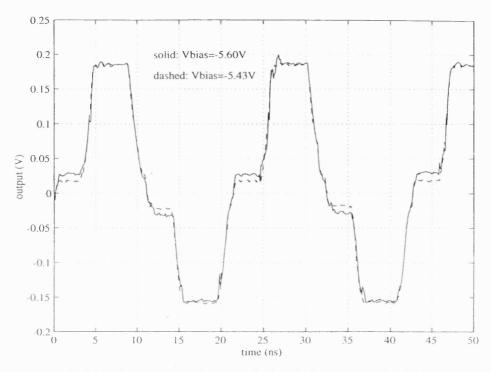

| Fig 5.23 | Simulation of sampling time adjustment of series MESFET OS/H                    | 148   |

| Fig 5.24 | Measured sampling time adjustment of series MESFET OS/H.                        | 149   |

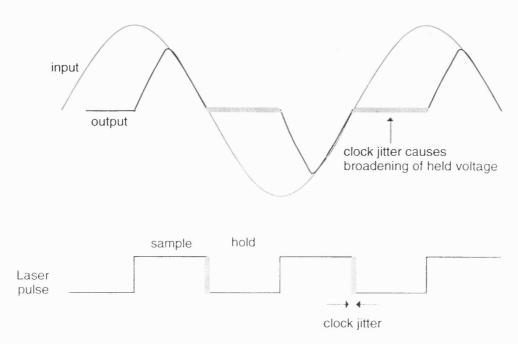

| Fig 5.25 | Measurement of timing jitter.                                                   | 150   |

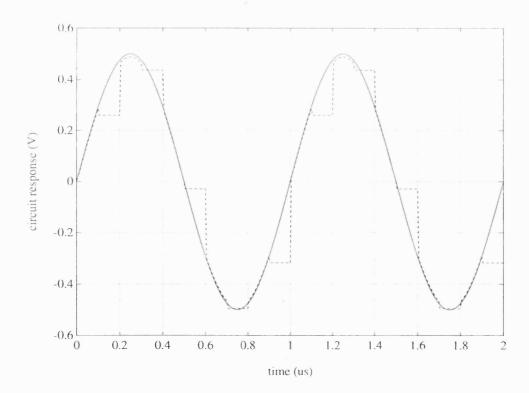

| Fig 5.26 | HSPICE simulation of diode bridge OS/H sampling a $50 \mathrm{MHz}$ sinusoid at |       |

|          | 250Ms/s                                                                         | 151   |

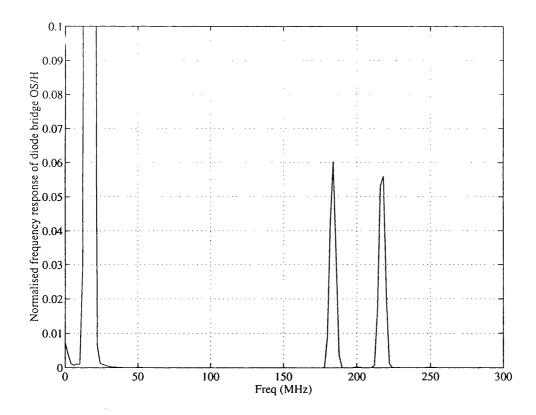

| Fig 5.27 | Simulated frequency spectrum of the output of the diode bridge OS/H             | 152   |

| Fig 5.28 | HSPICE simulation of the diode bridge OS/H sampling a 1MHz sinusoid at 5Ms/s $$ |       |

|          | (solid line = bootstrapped circuit, dashed line = bootstrapping removed). This  |       |

|          | simulation is used to highlight the effect of pedestal                          | 153   |

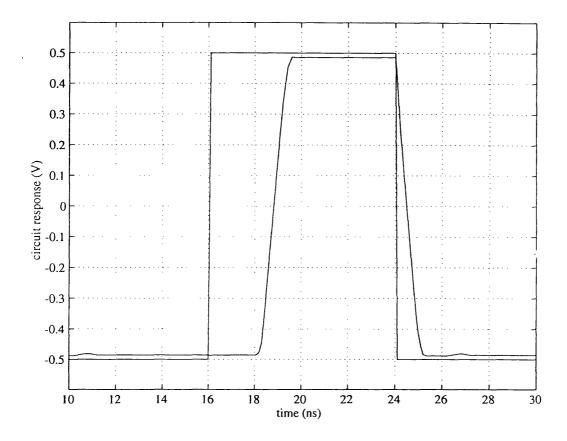

| Fig 5.29 | HSPICE simulation of frequency response of diode bridge OS/H                    | 154   |

| Fig 5.30 | HSPICE simulation of diode bridge OS/H showing acquisition of a 1V peak to      |       |

|          | peak square wave input signal.                                                  | 155   |

| Fig 5.31 | Measured response of the diode bridge OS/H sampling a 16MHz input at            |       |

|          | 200Ms/s. Although a sample and hold action is clearly taking place, this is     |       |

|          | distorted by severe clock feedthrough.                                          | 156   |

| Снарт    | TER 6                                                                           |       |

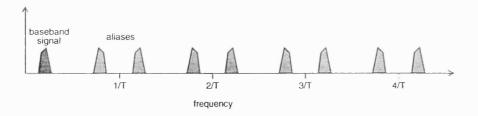

| Fig 6.1  | Frequency spectrum resulting from sampling with a frequency of 1/T              | 160   |

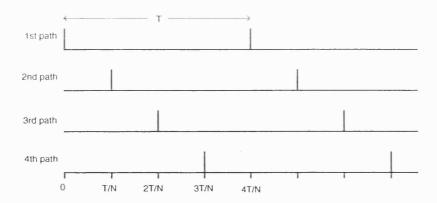

| Fig 6.2  | Timing intervals of N-path interleaved sampler.                                 | 160   |

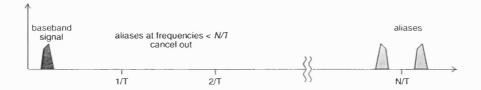

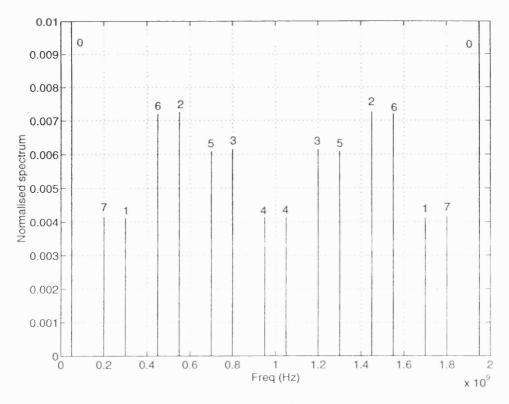

| Fig 6.3  | Frequency spectrum of N path interleaved sampler.                               | 162   |

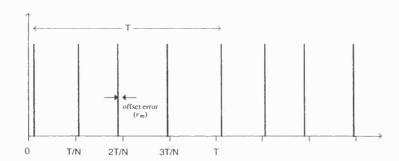

| Fig 6.4  | Sampling intervals of an N-path sampler with offset errors given by rmT/N and   |       |

|          | N-4                                                                             | 162   |

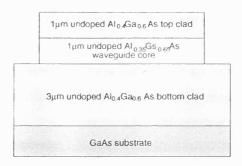

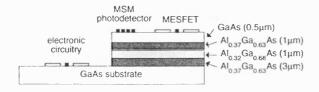

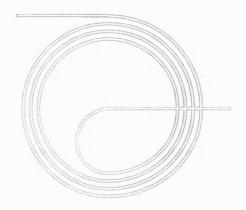

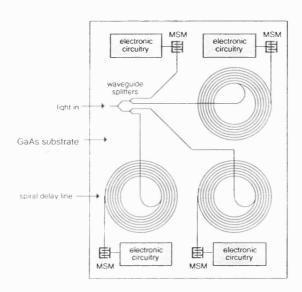

| . 170<br>. 170<br>. 173<br>. 175 |

|----------------------------------|

| . 170<br>. 173                   |

| . 170<br>. 173                   |

| . 173                            |

| . 173                            |

|                                  |

|                                  |

| . 175                            |

|                                  |

|                                  |

|                                  |

|                                  |

| . 181                            |

|                                  |

|                                  |

|                                  |

| 183                              |

|                                  |

| . 185                            |

| . 189                            |

|                                  |

| . 52                             |

| . 61                             |

| . 61                             |

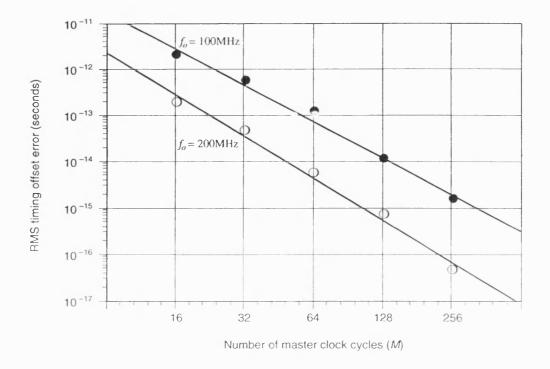

| . 163                            |

|                                  |

| . 166                            |

|                                  |

# **ACKNOWLEDGEMENTS**

I have heard it said that doing a PhD involves fumbling around in the dark for much of the time, eventually seeing the light just when you think there is no hope. In doing an optics project this has been more true for me than most. The hours spent alone in a darkened laboratory could have made my PhD a very lonely experience. I consider myself very fortunate, then, to have met and worked with so many people who have helped make my PhD so enjoyable.

First, I would like to thank Dr John Taylor for introducing me to this project and for supporting me throughout the difficult times. The transition from a spoon-fed degree to self directed research is very difficult, but John helped me steer this rocky course relatively smoothly. He also taught me the value of communicating ideas — I only hope that a little of his talent has rubbed-off on me. I would also like to thank Professor Gareth Parry for helping me through the occasional moments of self doubt that I had, and for being incredibly supportive throughout my project. In spite of his very busy schedule Gareth remains one of the most approachable and helpful people one could wish to meet.

Reflecting on my time at UCL my overwhelming memories are of the people I have met and worked with. Pask Visocchi was the first person to make the effort to talk to me when I arrived, and he has been talking ever since! With his characteristic unbounded generosity, Pask would leave aside anything if he thought he could be of assistance. It was Pask who I turned to for advice more than anyone else. Hassan Shaffeeu and Dave Grant were also there from the beginning, and together with Pask we developed a camaraderie that helped make the bad times good and the good times unforgettable. The Sun Inn will always have a special place in my heart.

Of course there are many other people I must thank, including Jorge, Mohan, Dave and everyone else in room 621. I feel privileged to have been able to call these people my friends, and look forward to many years of 621 Club reunions.

Life as a PhD student isn't all work and no play and so my friends outside of UCL have been very important in making the last few years so enjoyable. Derk and Martin have managed to live with me for many years without complaining,

and have shown me some of the joys an exuberant lifestyle can bring. I hope that now this thesis is finished I will be able to catch up on all the visits to the pub I have had to miss. Simon and Dave have also been very good friends and I often reflect on the good times we enjoyed in Acton and on our many sojourns to drinking establishments.

On a sunny day in 1985 I arrived in London from the wilds of the North to start my first degree. That was almost nine years ago, and since that time I have been almost totally reliant on my parents for their support. This extends way beyond the financial support I have received (although without this, things would have been practically impossible) to the enormous encouragement they have given me throughout the whole of these many years. This was probably the major factor in enabling me to pursue my studies to completion.

Finally, saving the most important until last, I would like to thank Lola. Her constant nagging has been a major driving force behind the completion of this thesis.

# CHAPTER 1

## **INTRODUCTION**

#### 1.1 GENERAL INTRODUCTION

Modern signal processing and instrumentation systems require increasingly high-speed sampling and analogue to digital conversion. For example, we would like to build oscilloscopes which can accurately record transient events generated by high speed electronic circuits. The gate delays of advanced technologies are typically around 100ps [1], so capture of these transients requires sample rates in excess of 20Gs/s. Similarly, the 10Gb/s communication system is fast becoming a reality [2], and so diagnostic equipment of similar or higher speed is in great demand. In the field of optics, sub-picosecond pulses are common (Eg. [3]), ensuring that ever higher-speed instrumentation will readily find applications. Signal processing applications in fields such as wide-band radar also continue to demand higher sample rates, and finally there is a constant demand for higher speed data conversion for military requirements [4].

Accurate, high speed analogue to digital converters (ADCs) are therefore fundamental components of modern, integrated signal processing systems and high-speed measurement and instrumentation systems. In particular, there is a demand for high-resolution (> 8-bits) ADCs with analogue bandwidths and sample rates in the gigahertz region. The achievement of these high sample rates using all-electronic means has proven to be very difficult.

One of the main problems facing designers of high speed sampling systems is that of accurately timing different parts of the system. Achieving appropriate clock phasing without timing jitter is often the single most difficult obstacle to attaining theoretical speed limitations. This problem arises primarily because of the extreme difficulty of impedance matching metallic interconnections at very high speeds as circuit complexity increases. Impedance mismatches at splits, bends and terminations result in high frequency reflections causing loss of pulse definition and therefore reduced timing accuracy. Also, transmission

line dispersion further reduces pulse definition and timing accuracy.

Optics, on the other hand, may offer new solutions to these very serious problems. By replacing the metallic interconnects with optical waveguides or free space optics, the problems of impedance mismatch and dispersion are eliminated [5]. Further advantages include the fact that modern mode-locked laser diodes produce ultra stable, ultra high-power pulses which can serve as an accurate clock source, and that optics has a much greater potential for connecting to the interior of a chip, simplifying pin-out problems. Hence one can see that optics potentially offers jitter-free interconnects with very large fanout and complex interconnectivity.

This project is a preliminary investigation of the practicalities of using optical clock distribution for high-speed sampled data applications, particularly high speed, high resolution A/D conversion.

#### 1.2 BACKGROUND TO ADCS AND SAMPLE AND HOLD CIRCUITS

The overall field of data conversion has sprung from two distinct sources. Starting in the late 1930s, interest developed in coding and decoding techniques for pulse code modulation (PCM) primarily for telephone communication. This exploits the noise immunity and lack of signal degradation inherent in digital transmission systems. Later, in the 1950s, the advent of digital computers provided a means for storing and manipulating data that was far superior to analogue techniques. By converting the analogue signals produced by natural phenomena into a digital format, signals can be processed using the powerful techniques of computing and digital electronics. This type of data conversion is employed extensively in military and instrumentation applications. Today, practically all communications, signal processing and increasing amounts of instrumentation are performed in the digital domain, with the analogue domain being used primarily as an interface to the outside world. The conversion from analogue to digital, and vice versa, is of crucial importance in a mixed signal system. Once in the digital domain a signal should suffer no further corruption, and therefore the accuracy of the data conversion will limit the overall system [6,7].

Analogue to digital and digital to analogue converters (DACs) translate

between the analogue signals of the real world and the artificial signal required or provided by digital control and computation circuits. They fulfil, therefore, a very important function in analogue control systems. In many analogue control systems using digital circuitry, the ADCs and DACs are the weakest link. Their accuracy and speed of operation limits the overall performance, and their complexity determines the overall size, weight and cost. Consequently, ADCs and DACs are often the bottleneck in applying digital control and computation to analogue control systems.

The performance of ADCs is steadily increasing with improvements in technology. Fig. 1.1 shows the performance of state of the art high-performance monolithic ADCs built in a range of technologies and using a variety of conversion techniques. It is clear from this figure that, for a given technology, there is a simple relationship between resolution and speed. Improvements in