# Oxidation of van-der-Waals Semiconductors for Neuromorphic Technology

Aferdita Xhameni\*, AbdulAziz AlMutairi\*, Antonio Lombardo, *Member, IEEE*

**Abstract**— Here, we report novel resistive memories based on oxides obtained by the chemical conversion of a two-dimensional van-der-Waals semiconductor: hafnium disulfide ( $\text{HfS}_2$ ). We apply a dry oxidation method, carefully controlling process parameters such as pressure, temperature, and oxygen flow. Hafnium oxides are integrated into crossbar structures, and resistive switching is studied by applying voltage ramps. We demonstrate unipolar switching achieving a  $\text{R}_{\text{ON}}/\text{R}_{\text{OFF}}$  ratio of  $\sim 10^4$  over 115 cycles, showing the potential of this approach for next-generation memristive technology.

## I. INTRODUCTION

Neuromorphic computing uses physical artificial neurons and synapses to directly process unstructured and noisy data. By co-locating memory and processing, it computes information with high power efficiency. It is particularly important for applications “at the edge”, requiring the processing of large amounts of noisy data with strict power and latency constraints [1]. Memristors are nonlinear, two-terminal devices characterised by a resistance that depends on the history of the electrical stress they have been subjected to and are among the most promising building blocks for neuromorphic computing [2]. The physical implementation of memristors typically consists of an electrode/switching layer/electrode stack, usually arranged in crossbar structures. Upon application of electrical stresses such as voltage ramps or pulses, the device's resistance can be reversibly switched between two or more resistance states due to redox, metal ion diffusion or phase change processes. The switching layer typically consists of oxides such as  $\text{HfO}_2$ ,  $\text{SiO}_2$  and  $\text{TiO}_2$ . Chemical conversion of two-dimensional van der Waals materials is a novel approach enabling the synthesis of ultrathin materials and interfaces by changing the composition or phase of an initial crystal while preserving its shape [3]. Here, we report on the oxidation of few-layer hafnium disulfide ( $\text{HfS}_2$ ) crystals by a controlled thermal process and using such an oxide in resistive memories.

Memristive devices can be characterised using a variety of different methods. In particular, the characteristic behaviour of a memristor is the appearance of a pinched hysteresis loop in its I-V curve [4]. The hysteresis usually arises due to a transition in the resistance of the device as a result of sufficiently high electrical stress. In some devices, an electroforming step is required, where the initially insulating switching layer is first switched from a high

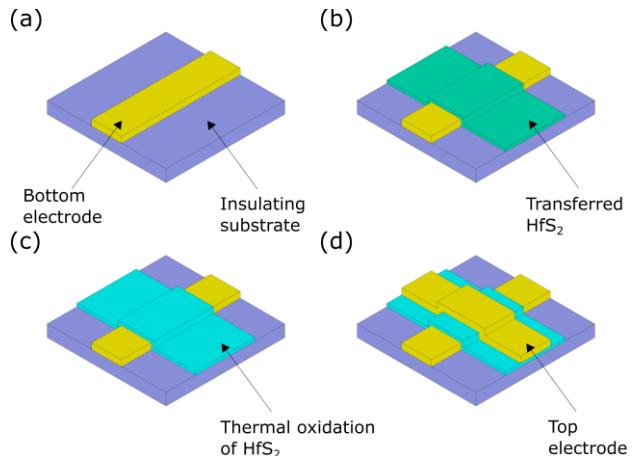

**Figure 1.** Hafnium oxide memristor fabrication process. (a) Bottom electrodes were fabricated using photolithography and metal deposition. (b) the  $\text{HfS}_2$  flake is transferred on top of the bottom electrode using a dry transfer method in an  $\text{N}_2$  environment. (c) The  $\text{HfS}_2$  flake is thermally oxidized under a controlled oxygen environment. (d) The top electrode is then fabricated in a similar manner to the bottom electrode.

resistive state (HRS) to a low resistive state (LRS) at the onset of a sufficiently high voltage called the forming voltage ( $V_{\text{FORM}}$ ). A current compliance ( $I_{\text{CC}}$ ) is often applied to prevent a complete dielectric breakdown in the switching layer. If the device has been electroformed, then on the return path of the DC I-V sweep, the I-V characteristics display a lower resistance than the device started with, forming a pinched hysteresis loop. While bipolar, unipolar and mixed unipolar/bipolar switching has been demonstrated in hafnium oxides grown by atomic layer deposition (ALD) [5] [6], in this work, we demonstrate unipolar switching with DC I-V sweeps in hafnium oxide thermally grown by oxidation of few-layer  $\text{HfS}_2$  crystals. Unipolar switching is a biasing method where the device is switched OFF or back to its HRS by applying electrical stress of the same polarity as the electroforming and SET operations. Crucially, the current compliance  $I_{\text{CC}}$  is also raised during RESET to facilitate the transition back to HRS. This occurs at the RESET voltage  $V_{\text{RESET}}$ . Once the device has been formed and RESET, it can be programmed back into the ON state by a SET operation: applying a voltage  $V_{\text{SET}}$ , which is typically greater than  $V_{\text{RESET}}$  but lower than  $V_{\text{FORM}}$  in magnitude, with  $I_{\text{CC}}$  lower than for RESET. The

\*These Authors contributed equally to this work.

Aferdita Xhameni and Antonio Lombardo (corresponding author, email: a.lombardo@ucl.ac.uk) are with the London Centre for Nanotechnology and the Electronic and Electrical Engineering

Department, University College London. AbdulAziz AlMutairi is with the Electrical Engineering Division, Engineering Department, University of Cambridge.

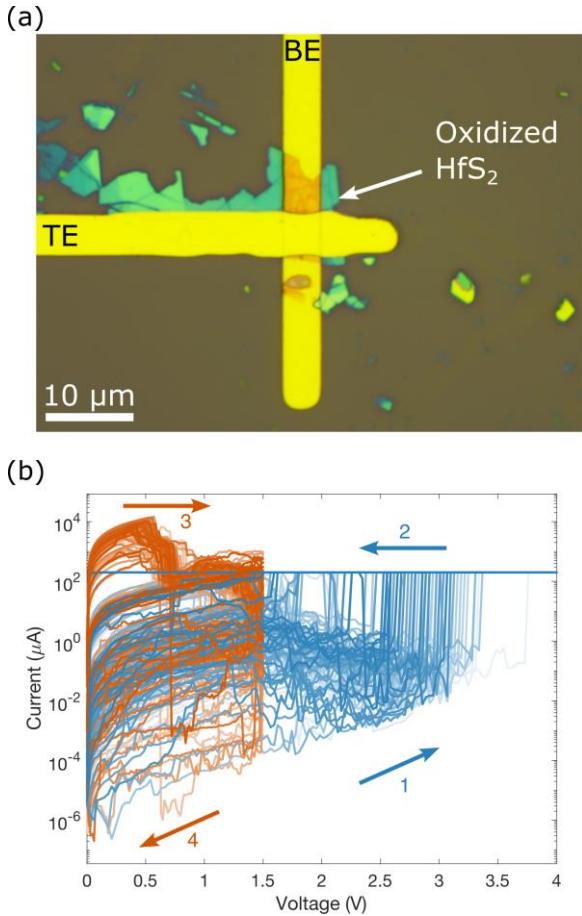

**Figure 2.** Memristor device architecture and DC I-V sweeps. (a) Optical image of the device showing the top electrode (TE), oxidized  $\text{HfS}_2$  and bottom electrode (BE); (b) DC I-V sweeps showing unipolar memristive behaviour. The blue curves are for the SET sweeps, whereas the orange curves are for the RESET sweeps. The colour gradient reflects the sweep cycle number where the colour becomes darker with each progressive sweep. The arrows indicate the scan direction of each sweep.

device can then be reversibly cycled between HRS and LRS by ramping the voltage from 0V to  $V_{\text{RESET}}$  and back for RESET, and from 0V to  $V_{\text{SET}}$  and back for SET, modulating  $I_{\text{CC}}$  accordingly.

## II. DEVICE FABRICATION

Fig. 1 schematically shows the structure of the device fabrication steps. Cr (5nm)/Au (50nm) bottom electrodes were first fabricated onto oxidised silicon wafers (285nm thermal oxide) by laser lithography followed by metal evaporation and lift-off (Fig 1a).  $\text{HfS}_2$  flakes were produced on a different substrate by mechanical exfoliating bulk  $\text{HfS}_2$  crystals (HQ graphene) under an inert ( $\text{N}_2$ ) atmosphere in a glove-box setup. Flakes were visually inspected with an optical microscope, and selected flakes were transferred onto the prefabricated bottom electrodes using a conventional dry transfer method using a polycarbonate (PC)/Polydimethylsiloxane (PDMS) stamp [7] under the same controlled atmosphere environment (Fig 1b).

Thermal oxidation was performed using a Moorfield MiniLab 026 annealing system at 275°C, 0.1 mbar and 38.5 SCCM  $\text{O}_2$  for 45 minutes (Fig 1c). Finally, a Ti (5nm)/Au (50nm) top electrode was fabricated via laser lithography followed by metal evaporation (Fig 1d). An optical micrograph of a representative device is shown in Fig. 2a.

## III. RESULTS

### A. IV Sweep Characteristics

A Keysight B1500A parameter analyser was used to test the switching performance of the hafnium oxide memristor by applying DC sweeps. The sweeps shown in Fig. 2b evidence that the device exhibits unipolar memristive switching. Initially, the device is in an HRS and after reaching a forming voltage of magnitude 4.8V ( $I_{\text{CC}}$  of 200 $\mu\text{A}$ ), the device switched from HRS to LRS. Given the unipolar behaviour of the device, a positive voltage was used for the RESET sweep, increasing  $I_{\text{CC}}$  to 15mA to facilitate the RESET operation. As shown in Fig 2b, the device maintained a LRS until a RESET voltage ( $V_{\text{RESET}}$ ) of 1.5V is reached, at which it switched back to a HRS. A SET voltage ( $V_{\text{SET}}$ ) of about 3V and  $I_{\text{CC}}$  of 200 $\mu\text{A}$  were used to

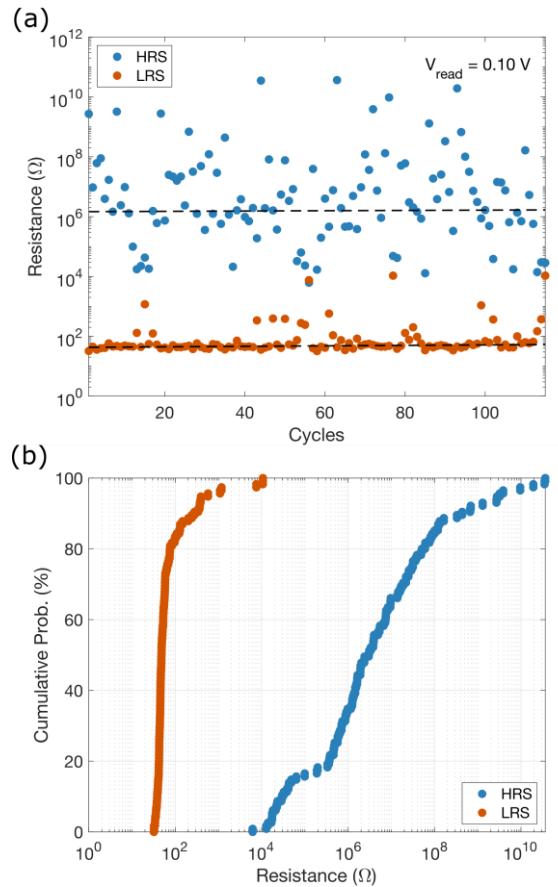

**Figure 3.** Cycle endurance analysis of the memristor over 115 cycles. (a) high-resistive state (HRS) and low-resistive state (LRS) endurance over cycles; (b) HRS and LRS cumulative distribution function (CDF) in percentage.

switch the device from HRS to LRS. This device demonstrated moderate endurance, achieving 115 cycles before becoming more conductive than the  $I_{CC}$  for RESET would allow, thereby remaining in the LRS. By adjusting  $V_{SET}$ ,  $V_{RESET}$ , and  $I_{CC}$ , further switching cycles were possible.

### B. State Evolution

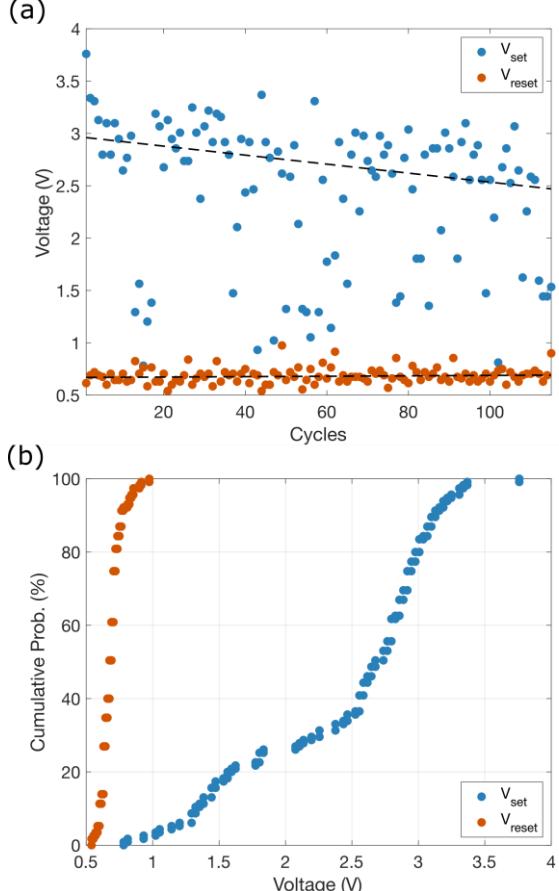

Further analysis of the I-V sweep cycles revealed that the device exhibits a  $R_{ON}/R_{OFF}$  ratio of  $\sim 10^4$  measured at 0.1V (Fig 3a). Nevertheless, HRS has a notable cycle-to-cycle variation compared to the LRS, as shown in Fig. 3a and 3b. Additionally,  $V_{SET}$  exhibits a trend towards lower voltages and a greater cycle-to-cycle variation than its  $V_{RESET}$  counterpart over the switching cycles tested (Fig 4a and 4b). This large variation is predicted to subside with further optimisation of the biasing scheme and the oxidation process of  $HfS_2$ . The failure mechanism for such a device could be attributed to the irreversible and successive gettering of oxygen ions in the titanium electrode, leaving behind a permanent  $TiO_x$  layer in proximity to the switching layer/electrode interface [8]. The displaced titanium ions can form a filament within the switching layer [9] [10]. This could be resolved by inserting a capping layer between the switching material and the top electrode, providing a chemical

**Figure 4.** SET and RESET voltage evolution over 115 cycles. (a) is the SET voltage ( $V_{set}$ ) and RESET voltage ( $V_{reset}$ ) cycle to cycle variation and (b) is the corresponding CDF plot of SET and RESET voltages.

boundary between them [11]. Furthermore, the abrupt rises of current during SET at high voltages may lead to an overcurrent experienced by the device caused by the delay in activating  $I_{CC}$  in the parameter analyzer. This could be damaging the device during switching and can be addressed by passing the current through a transistor channel instead, providing an instantaneous limitation to the current [12].

### IV. CONCLUSION

Memristors based on dry oxidation of few-layer  $HfS_2$  crystals have been reported, and unipolar resistive switching has been demonstrated. Using programming voltages of 3V and 1.5V for  $V_{SET}$  and  $V_{RESET}$ , respectively, the devices showed an endurance of 115 DC voltage ramp cycles and a  $R_{ON}/R_{OFF}$  of  $10^4$ . Such results pave the way for the application of ultra-thin oxides obtained by controlled oxidation of two-dimensional semiconductors such as  $HfS_2$  in neuromorphic technology, either in an active role such as in spiking networks or as a supportive selector layer.

### V. ACKNOWLEDGEMENTS

A.Xh. acknowledges financial support from EPSRC Grant EP/T517793/1. A.A. acknowledges financial support from the Saudi Arabian Ministry of Education.

### REFERENCES

1. Mehonic, A. and A.J. Kenyon, Brain-inspired computing needs a master plan. *Nature*, 2022. 604(7905): p. 255-260.

2. Mehonic, A., et al., Memristors—From In-Memory Computing, Deep Learning Acceleration, and Spiking Neural Networks to the Future of Neuromorphic and Bio-Inspired Computing. *Advanced Intelligent Systems*, 2020. 2(11).

3. Lam, D., D. Lebedev, and M.C. Hersam, Morphotaxy of Layered van der Waals Materials. *ACS Nano*, 2022. 16(5): p. 7144-7167.

4. Chua, L., 1971. Memristor—the missing circuit element. *IEEE Transactions on circuit theory*, 18(5), pp.507-519.

5. Chen YY, et al., Insights into Ni-filament formation in unipolar-switching Ni/ HfO<sub>2</sub>/TiN resistive random access memory device. *Appl. Phys. Lett.* 2012, 100, 113513.

6. Govoreanu B, et al., 10×10 nm<sup>2</sup> Hf/HfO<sub>x</sub> crossbar resistive RAM with excellent performance, reliability and low-energy operation. In *Electron Devices Meeting (IEDM), 2011 IEEE International*. IEEE, 2011.

7. Purdie, D.G., et al., Cleaning interfaces in layered materials heterostructures. *Nature Communications*, 2018. 9.

8. Roy, S., Chakrabarti, B. and Bhattacharya, E., 2023. Co-existence of interfacial and filamentary resistance switching in Ti/SiO<sub>x</sub>/Au resistive memory devices. *TechRxiv*. Preprint available at: <https://doi.org/10.36227/techrxiv.23521953.v1>

9. Privitera, S., et al., 2013. Microscopy study of the conductive filament in HfO<sub>2</sub> resistive switching memory devices. *Microelectronic Engineering*, 109, pp.75-78.

10. Valov, I., et al., 2016. Mobile ions, transport and redox processes in memristive devices. *ECS Transactions*, 75(5), p.27.

11. Hui, F., Grustan-Gutierrez, E., Long, S., Liu, Q., Ott, A.K., Ferrari, A.C. and Lanza, M., 2017. Graphene and related materials for resistive random-access memories. *Advanced Electronic Materials*, 3(8), p.1600195.

12. Zhu, K., et al., 2023. Hybrid 2D-CMOS microchips for memristive applications. *Nature*, 618(7963), pp.57-62.