# Low-latency Optically-switched Data Centre Interconnects enabled by Hollow Core Anti-resonant Fiber

Zichuan Zhou<sup>1</sup>, Hubert Dzieciol<sup>1</sup>, Kari Clark<sup>1</sup>, Radan Slavik<sup>2</sup>, Hesham Sakr<sup>2</sup>, Kerrianne Harrington<sup>2</sup>, David Richardson<sup>2</sup>, Francesco Poletti<sup>2</sup>, and Zhixin Liu<sup>1</sup>

<sup>1</sup>Optical Networks Group, University College London, Torrington Place, London, WC1E 7JE. UK

<sup>2</sup>Optoelectronics Research Centre, University of Southampton, Southampton, SO17 1BJ, UK

Author e-mail address: zczlzz0@ucl.ac.uk

**Abstract:** We leverage the low thermal sensitivity and low dispersion features of hollow antiresonant fiber to demonstrate a real-time low-latency optically-switched intra-data center interconnect at 51.2 GBd by co-designing fast wavelength switching and optical clock synchronization. © 2022 The Author(s)

#### 1. Introduction

The booming of machine-to-machine traffic in cloud data centers (DC) has stimulated research into fast optical switching to enable scalable DC networking with a reduced power consumption [1, 2]. Simultaneously, low-latency interconnection is becoming increasingly important to support time-sensitive cloud applications such as high frequency trading and augmented reality. Indeed, fast optical switching systems with low end-to-end latency will be desired in future data center interconnection (DCI). In optically switched DCIs, the physical layer end-to-end latency is the sum of the light propagation time in optical fiber, transceiver (TRx) latency (e.g. signal processing, data sampling and detection time, forward-error correction (FEC) computation time), and the inter-packet gap. Generally, the end-to-end latency of an optically switched system is higher than in point-to-point transmission as it requires additional time for clock and data recovery (CDR) as well as an inter-packet gap for optical switching [3]. Thus, low latency optically switched systems should minimize the signal processing latency, inter-packet gap and fibre time of flight.

Hollow core fiber (HCF) exhibits 34% lower light propagation latency than standard single mode fibers (SSMFs), providing the ultimate minimum time-of-flight close to that of light in vacuum [4]. In addition, we previously demonstrated that optical clock synchronization using HCF can help eliminate CDR locking time due to HCF's low thermal sensitivity [5, 6]. However, we previously emulated optical switching using a 2×2 fast Mach-Zehnder modulator (MZM), which cannot scale to support cloud DC networks. Recent research has shown that fast wavelength tunable lasers can achieve tuning times of less than 5 ns across the telecom C-band, promising fast optical switching with a large port count [7]. However, the wavelength tuning was not demonstrated with a data payload and consequently, the system performance and the required inter-packet gap have not been studied.

In this paper, we demonstrate a 50 GBd real-time wavelength-switched system with minimum transceiver latency and inter-packet gap, achieving 28 ns transceiver latency and 18 ns inter-packet gap for sub-10<sup>-9</sup> bit error ratio (BER) packet transmission. To achieve this, the low thermal sensitivity of HCF enabled phase stable optical clock synchronization through control plane links and eliminated any latency overhead for CDR. The HCF low and flat dispersion (<2ps/(nm·km) across telecom C-band) eliminated any signal processing overhead required to compensate for the clock phase shift due to the variation of group velocity delay (GVD). To the best of the authors' knowledge, this is the first study of the achievable latency of wavelength switched DCI.

### 2. Experimental Set-up

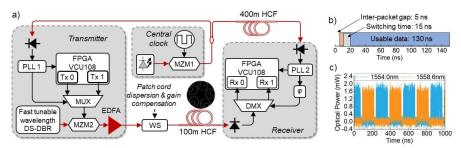

Fig. 1a shows the experimental set-up. The optical clock signal was generated by modulating a continuous wave (CW) signal with a 400 MHz reference clock using a quadrature-baised MZM, outputting -5 dBm optical clock signal that was split into two branches. The left branch was connected to the Tx through a 2 m SSMF patchcord and the right branch was transmitted the Rx through a 400 m HCF (with 5.5 dB total loss) after amplified by an erbium-doped fiber amplifier (EDFA1). At both Tx and Rx, the optically clock signals are detected by a photodetector and was fed into field programmable gate arrays (FPGAs, Xilinx VCU108) and phase lock loops (PLL2&3) as reference clocks. The Tx FPGA generated two streams of 25.6 GBd OOK packets that were multiplexed to 51.2 GBd using an external RF multiplexer driven with a 25.6 GHz clock signal generated by PLL2. The optical packets (Fig. 1b) consisted of a 5 ns inter-packet gap followed by a 145 ns payload (928 bytes) using a PRBS of 29 length. At the Rx, the 51.2 GBd OOK packets are demultiplexed by an RF demultiplexer, which outputs two streams of 25.6 GBd OOK data to two GTX receivers (Rx1 and Rx2) on the receiver FPGA for packet detection and BER calculation. A digital supermode distributed Bragg reflector (DS-DBR) laser was driven with pre-equalized electronic control signals to achieve fast wavelength switching [6]. The DS-DBR laser was configured to switch between 1554 nm and 1558.6 nm every 150 ns

(Fig. 1c) and was time synchronized to the multiplexed electronic packets to generate 51.2 GBd optical packets using a 40-GHz MZM. The optical packets were amplified and transmitted through a 100-m HCF. The waveshaper is used to compensate the residual dispersion of the SSMF patchcords to study the performance of all-HCF based systems (where integrated transceivers directly interface to HCF). No active CDR clock phase tracking was used due to the low thermal sensitivity of the HCFs. By reducing the electronic processing to sampling and detection only, we achieved a minimal transceiver latency of 28 ns [8].

Fig. 1: a) Experimental set-up; b) Packet structure; c) Received optical waveforms (orange: 1558.6 nm packet, blue: 1554 nm packet). PLL: Phase lock loop; MUX/DMX: RF multiplexer/de-multiplexer; WS: waveshaper; PD: Photodetector;  $\varphi$ : Phase shifter.

#### 3. Results

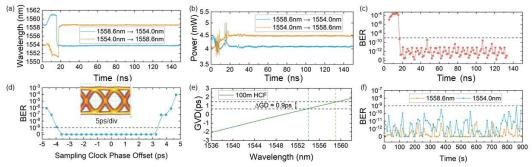

Figs. 2a and 2b show the measured wavelength and power change of the DS-DBR laser over the duration of an optical packet (150 ns) where the switching occurs at the beginning. The wavelength switching is accompanied by power fluctuations, which resulted in BER degradation at the beginning of each optical packet (Fig. 2c). This limited the minimum required inter-packet gap to 18 ns. Fig. 2d shows the measured BER at different sampling phase. The system achieves a BER of sub- $10^{-9}$  when the clock phase offset is under  $\pm 3.7$ ps from the optimum sampling phase. Fig. 2e shows the measured GVD of the 100 m HCF used, showing a GVD slope of about 0.19 ps/nm. Thus, switching between 1554 nm and 1558.6 nm only resulted in a change of time-of-flight by about 0.9 ps, which is within the clock phase offset tolerance window of the 50 GBd packets. Note that a 100-m SSMF at the same wavelength would result in 7.8 ps GVD change, exceeding the error free window and therefore requiring additional processing time such as clock phase recovery to correct the clock phase, adding signal processing latency. Finally, we tested the system in a laboratory environment with  $\pm 1^{\circ}$ C temperature variation and recorded the BER over 15 minutes, recording sub- $10^{-9}$  BER for both wavelengths, which validates the stability of the HCF-based system.

Fig 2: (a) Wavelength switching dynamics; (b) Switching dynamics of optical power; (c) BER across packet; (d) BER tolerable sampling clock phase offsets; (e) measured GVD of the 100-m HCF; f) long-term BER stability test.

## 4. Conclusion

We demonstrate an ultra-low latency optically switched system with minimal (28 ns) transceiver latency and an 18 ns inter-packet gap using a fast wavelength switched laser and signal transmission through HCF. HCF's low dispersion minimizes the GVD change when switching wavelength and its low thermal sensitivity enables stable clock distribution without active CDR, together enabling 51.2 GBd packet transmission with minimal transceiver latency.

#### Reference

- [1] H. Ballani, et al., Proc. SIGCOMM, pp 782-797, 2020

- [2] H. Dorren, et al., J. Lightw. Technol, 33, pp 1117–1125, 2015

- [3] K. Clark, et al., Nat. Electronics, 3, pp 426-422, 2020

- [4] F. Poletti et al., Nat. Photon. 7, pp 279–284, 2013

- [5] K. Clark, et al., J. Lightw. Technol, 38, pp 2703–2709, 2020

- [6] R. Slavík, et al., Sci. Reports, 5, 2015

- [7] T. Gerard, et al., IEEE. Photonics. Technol. Letter, 32, pp 477-480, 2020

- [8] Xilinx GTY TRx latency:

- https://support.xilinx.com/s/article/66341