# **Modelling, Analysis and Design of Optimised Electronic Circuits for Visible Light Communication Systems**

Amany Kassem

A thesis submitted for the degree of Doctor of Philosophy

of

**University College London**

Information & Communication Systems Research Group

Department of Electronic and Electrical Engineering

University College London

November, 2021

# **Declaration**

I, Amany Kassem, confirm that the work presented in this thesis is my own. Where information has been derived from other sources, I confirm that this has been indicated in the work.

Amany Kassem

# Abstract

This thesis explores new circuit design techniques and topologies to extend the bandwidth of visible light communication (VLC) transmitters and receivers, by ameliorating the bandwidth-limiting effects of commonly used optoelectronic devices. The thesis contains detailed literature review of transmitter and receiver designs, which inspired two directions of work. The first proposes new designs of optically lossless light emitting diode (LED) bandwidth extension technique that utilises a negative capacitance circuit to offset the diode's bandwidth-limiting capacitance. The negative capacitance circuit was studied and verified through newly developed mathematical analysis, modelling and experimental demonstration. The bandwidth advantage of the proposed technique was demonstrated through measurements in conjunction with several colour LEDs, demonstrating up to 500% bandwidth extension with no loss of optical power. The second direction of work enhances the bandwidth of VLC receivers through new designs of ultra-low input impedance transimpedance amplifiers (TIAs), designed to be insensitive to the high photodiode capacitances ( $C_{pd}$ ) of large area detectors. Moreover, the thesis proposes a new circuit, which modifies the traditional regulated cascode (RGC) circuit to enhance its bandwidth and gain. The modified RGC amplifier efficiently treats significant RGC inherent bandwidth limitations and is shown, through mathematical analysis, modelling and experimental measurements to extend the bandwidth further by up to 200%. The bandwidth advantage of such receivers was demonstrated in measurements, using several large area photodiodes of area up to  $600 \text{ mm}^2$ , resulting in a substantial bandwidth improvement of up to 1000%, relative to a standard  $50 \Omega$  termination. An inherent limitation of large area photodiodes, associated with internal resistive elements, was identified and ameliorated, through the design of negative resistance circuits. Altogether, this research resulted in a set of design methods and practical circuits, which will hopefully contribute to wider adoption of VLC systems and may be applied in areas beyond VLC.

# Impact Statement

This thesis contributes to the study, design, and practical implementations of new electronic circuit design techniques to enhance the bandwidth of optoelectronic devices in visible light communication systems (VLC). This theme is particularly relevant given the unprecedented demand on the limited radio frequency (RF) spectrum, which has motivated researchers to explore alternative technologies to support data communication. VLC established itself as one of the most promising candidate technologies to alleviate the looming RF spectral crisis. As an indoor access network, one of the main driving forces for VLC is the significant advances in solid-state lighting, which enabled power-efficient and extended life-span lighting infrastructure using light-emitting diodes (LEDs). Moreover, the ubiquity of LEDs offers an attractive economic advantage since VLC technology leverages on the existing lighting infrastructure to serve the dual functionality of illumination and data communication. In addition to offering other advantages such as the huge unregulated  $\sim$ 400 THz bandwidth free of licensing costs.

The analysis, techniques and topologies introduced in this thesis are shown to improve the utility of the VLC technology significantly through performance optimisation of the highly bandwidth-limited optoelectronic devices, including high power LEDs and large area photodiodes, which are typically employed in VLC systems. The bandwidth optimisation techniques proposed in this thesis tackle the bandwidth limitation associated with the optoelectronic devices in a rather atypical approach by adopting new and existing electronic circuits that boosts performance. Such techniques are envisaged to impact the innovation in VLC systems and motivate new research to construct simple and cost-effective systems using optimised circuits for indoor communications in office and home environments. Furthermore,

the reported circuit techniques dealt with the bandwidth challenges encountered at both the transmitter and the receiver side, which paved the way for the efficient utilisation of commercially available high power LED lighting to provide room illumination alongside data communication. This is in addition to the use of commercially available exceptionally large area photodiodes with significantly better light-harvesting capabilities, therefore, allowing for communication at practical data rates and transmission distances.

Most of the research and experimental work presented in the thesis have been peer-reviewed and reported in four top conference papers and one journal paper in the field of circuits and systems design. The successful implementation of the proposed circuit techniques would hopefully contribute to the wide adoption of VLC systems and may be applied in areas beyond VLC, especially in high-speed optical fibre communications, where the adoption of the proposed circuit techniques could potentially allow for higher achievable data rates. Furthermore, the techniques developed in this thesis may impact other areas of electronic sensing applications and sensor networks, from pollution monitoring and ultrasound sensing to tomography for industrial and medical applications and other systems where performance is limited by high and undesirable capacitances of sensors and sources.

# Acknowledgements

First and foremost, I would like to express my deep heartfelt appreciation to my principal supervisor Professor Izzat Darwazeh who has patiently guided me throughout my PhD and my MSc before that. Izzat has been incredibly generous with his time and efforts. He motivated my sense of curiosity and wonder, which deepened my enthusiasm and passion for circuit design and influenced how I view and approach my work. Thank you for believing in me and for continuously challenging my knowledge of the subject, which have significantly improved the quality of the work in this thesis. Your contribution to my personal and professional growth has been immeasurable. You have been a mentor and, above all, a friend, and for that, I am eternally grateful.

The research presented in this thesis was carried out in the Laboratories of the Electronic and Electrical Engineering department at University College London, where I was lucky to have been surrounded and supported by a bunch of fantastic people to whom I am deeply indebted and so appreciative. I first offer my gratitude to Dr Paul Anthony Haigh, who was a postdoctoral fellow at UCL for part of my PhD. I really appreciate the guidance he has given me, especially with setting up my first VLC experiments. Thank you, sincerely. I am also so grateful for Dr Temitope Odedeyi for all the technical discussions and the good lab company he provided during lockdown times. Dr Waseem Ozan, for providing the best company during lunch and for all the coffees throughout the years. Thank you both for your valuable friendships. To my dearest friend, Xinyue Liu, who joined UCL halfway through my PhD and my life has not been the same ever since. She brought so much fun to my life and has provided a much needed refuge that has sustained me during

the past years. Thank you for your friendship. Last but not least, I must thank Scott Martin for fabricating all the PCBs used in this research, often at a very short notice. Thank you for your patience. I would also like to thank Gerald McBrearty and Andrew Moss for maintaining a well-organised lab environment and for their help providing much of the equipment used in the experiments in this work.

I would like to express my immense gratitude to my parents, who not only generously funded my PhD but relentlessly pushed me to be my best self. As always, this PhD would not have been possible without their support. To my mother, thank you for going above and beyond what is possible to support me and for setting a wonderful example of what it means to be a strong loving woman. I look up to you in so many ways. To my father, my greatest supporter, no words can ever do you justice or express the love and admiration I have for you. I hope I always make you both proud. To my twin brother Hossam, who was in London for a good part of my PhD, I am beyond blessed to have you by my side. Thank you very much for always believing in me. I hope we both continue to shine together.

Last but not least, to my partner, Mostafa, your support means the world to me. Thank you for loving me and being by my side. I would also like to thank my best friends; Menna and Zeina, whom I consider to be my chosen family. Thank you very much for being such good listeners and reliable friends. I am forever grateful to have you both. I would also like to thank my dear friends, Sarah and Nour, with whom I have shared a lot of happy memories and whose friendships made London feel like home.

Finally, I would like to acknowledge funding, for 18 months of this PhD work, by UCL and by the Engineering and Physical Sciences Research Council (EPSRC) Multifunctional Polymer Light-Emitting Diodes with Visible Light Communications (MARVEL) grant.

# Contents

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| <b>List of Figures</b>                                            | <b>20</b> |

| <b>List of Tables</b>                                             | <b>22</b> |

| <b>List of Abbreviations &amp; Symbols</b>                        | <b>23</b> |

| <b>1 Introduction</b>                                             | <b>27</b> |

| 1.1 VLC Preliminaries & Challenges . . . . .                      | 31        |

| 1.2 Thesis Structure . . . . .                                    | 39        |

| 1.3 Key Contributions & Publications . . . . .                    | 42        |

| <b>2 Negative Impedance: Concept &amp; Techniques</b>             | <b>46</b> |

| 2.1 Introduction . . . . .                                        | 46        |

| 2.2 Negative Impedance Preliminaries . . . . .                    | 47        |

| 2.3 Negative Impedance Circuit Techniques . . . . .               | 50        |

| 2.3.1 NIC Fundamentals & Configurations . . . . .                 | 50        |

| 2.3.2 Negative Capacitance Circuits using Miller Effect . . . . . | 59        |

| 2.4 Summary & Discussion . . . . .                                | 69        |

| <b>3 Negative Capacitance Circuit for VLC Applications</b>        | <b>72</b> |

| 3.1 Introduction . . . . .                                        | 72        |

| 3.2 Design Concept . . . . .                                      | 73        |

| 3.3 Negative Capacitance Circuit Design . . . . .                 | 73        |

| 3.3.1 Negative Capacitance Circuit Design & Modelling . . . . .   | 73        |

| 3.3.2 Semi-Empirical Negative Capacitance Circuit Model . . . . . | 79        |

|          |                                                                            |            |

|----------|----------------------------------------------------------------------------|------------|

| 3.4      | Performance Assessment based on Modelling and Simulations . . . . .        | 83         |

| 3.4.1    | Effect of $-R_c$ on the Quality of $-C_c$ . . . . .                        | 83         |

| 3.4.2    | Effect of $R_b$ on the Frequency Range of $-C_c$ . . . . .                 | 88         |

| 3.4.3    | Effect of Non-Ideal Transistors on the Range of $-C_c$ . . . . .           | 93         |

| 3.5      | Experimental Verification & Testing . . . . .                              | 97         |

| 3.5.1    | Verification of the Effect of $-R_c$ on the Quality of $-C_c$ . . . . .    | 100        |

| 3.5.2    | Verification of the Effect of $R_{com}$ on the Quality of $-C_c$ . . . . . | 102        |

| 3.5.3    | Verification of the Range of $-C_c$ . . . . .                              | 106        |

| 3.6      | Conclusions . . . . .                                                      | 109        |

| <b>4</b> | <b>Negative Capacitance for LED Bandwidth Extension</b>                    | <b>111</b> |

| 4.1      | Introduction . . . . .                                                     | 111        |

| 4.2      | A Brief Review of LED Modelling . . . . .                                  | 112        |

| 4.3      | LED Bandwidth Extension Techniques . . . . .                               | 116        |

| 4.4      | Proposed LED Bandwidth Extension Technique . . . . .                       | 122        |

| 4.4.1    | Design Methodology . . . . .                                               | 122        |

| 4.4.2    | Derivation of Compensated LED Equivalent Model . . . . .                   | 123        |

| 4.4.3    | Negative Capacitance Circuit Measurements . . . . .                        | 128        |

| 4.5      | Optical Measurements based on LEDs . . . . .                               | 133        |

| 4.5.1    | LED Model Extraction . . . . .                                             | 133        |

| 4.5.2    | Negative Capacitance for LED Bandwidth Extension . . . . .                 | 141        |

| 4.6      | Discussion & Conclusions . . . . .                                         | 150        |

| <b>5</b> | <b>Low Input Impedance Configurations of TIAs</b>                          | <b>152</b> |

| 5.1      | Introduction . . . . .                                                     | 152        |

| 5.2      | Design Techniques of Optical Pre-amplifiers . . . . .                      | 153        |

| 5.3      | Shunt Feedback TIAs . . . . .                                              | 160        |

| 5.4      | Low Input Impedance TIAs . . . . .                                         | 164        |

| 5.4.1    | Common Base/Gate TIA Configuration . . . . .                               | 164        |

| 5.4.2    | Regulated Cascode TIA Configuration . . . . .                              | 176        |

| 5.5      | Discussion & Conclusions . . . . .                                         | 185        |

---

|                                                                               |            |

|-------------------------------------------------------------------------------|------------|

| <b>6 A New High Bandwidth Modified Regulated Cascode Amplifier</b>            | <b>187</b> |

| 6.1 Introduction . . . . .                                                    | 187        |

| 6.2 Design of the RGC TIA . . . . .                                           | 190        |

| 6.2.1 RGC Equivalent Circuit Model Derivation . . . . .                       | 190        |

| 6.3 Performance Assessment of the RGC TIA . . . . .                           | 196        |

| 6.3.1 Effect of RGC $R_{in}$ on the Bandwidth Performance . . . . .           | 196        |

| 6.3.2 Miller Effect of $C_{\mu 1}$ . . . . .                                  | 200        |

| 6.4 Design of a Modified RGC TIA . . . . .                                    | 208        |

| 6.4.1 Modified RGC Equivalent Model Derivation . . . . .                      | 209        |

| 6.5 Comparative Assessment of the RGC & the Modified RGC TIAs . .             | 214        |

| 6.5.1 Comparison of $R_{in}$ of the RGC & Modified RGC . . . . .              | 214        |

| 6.5.2 Effects of Neutralising the Miller Capacitance of $C_{\mu 1}$ . . . . . | 217        |

| 6.6 TIAs Verification & Measurements . . . . .                                | 226        |

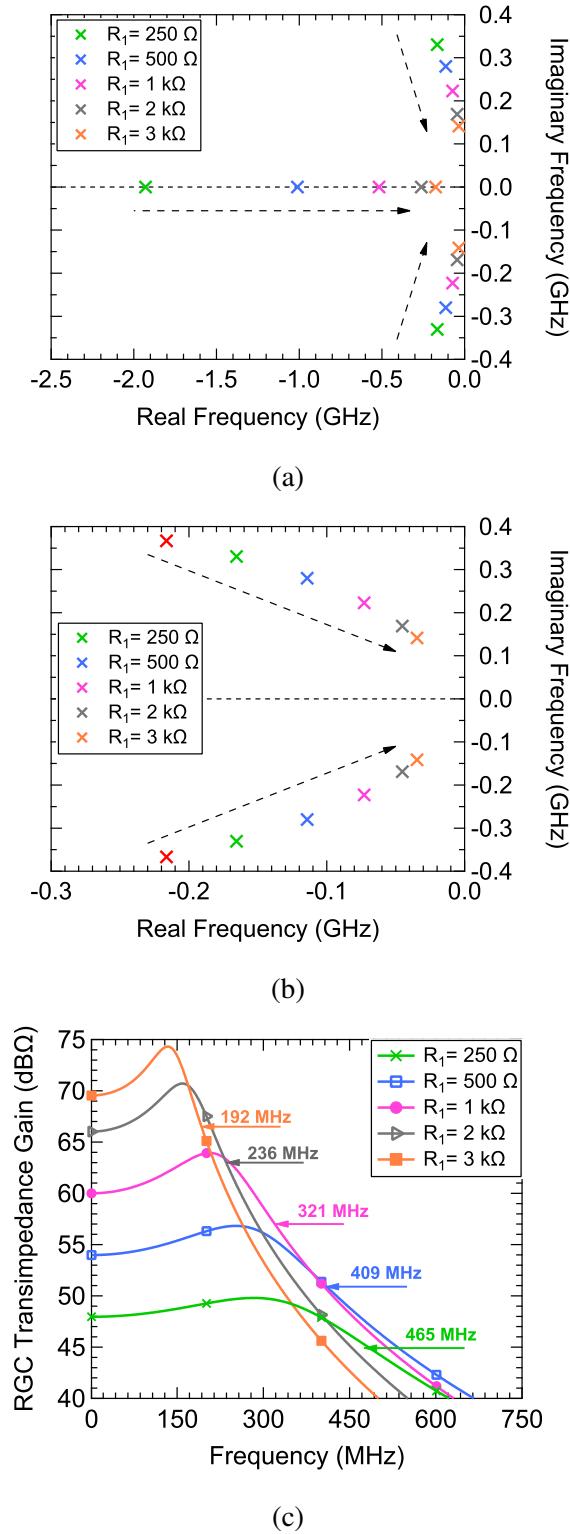

| 6.6.1 Verification of the Effect of $R_{in}$ on Bandwidth . . . . .           | 227        |

| 6.6.2 Bandwidth versus gain of the RGC & Modified RGC . . . . .               | 229        |

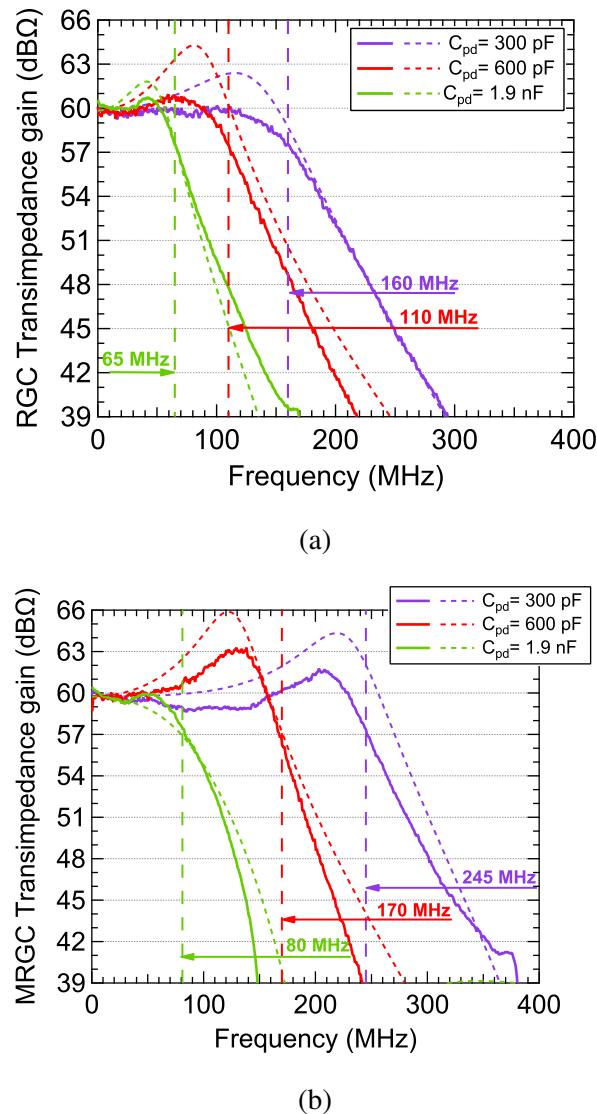

| 6.6.3 Bandwidth versus $C_{pd}$ of the RGC & Modified RGC . . . . .           | 232        |

| 6.7 Discussion & Conclusions . . . . .                                        | 234        |

| <b>7 Low Impedance Amplifiers for Large-Area Photodiode Receivers</b>         | <b>235</b> |

| 7.1 Introduction . . . . .                                                    | 235        |

| 7.2 Optical Link Measurements with the Large-Area Photodiodes . .             | 237        |

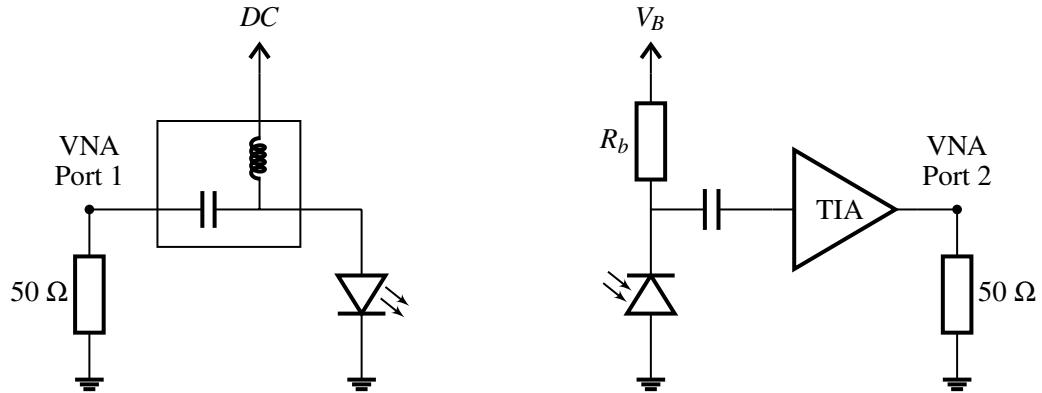

| 7.2.1 Experimental Set-up . . . . .                                           | 237        |

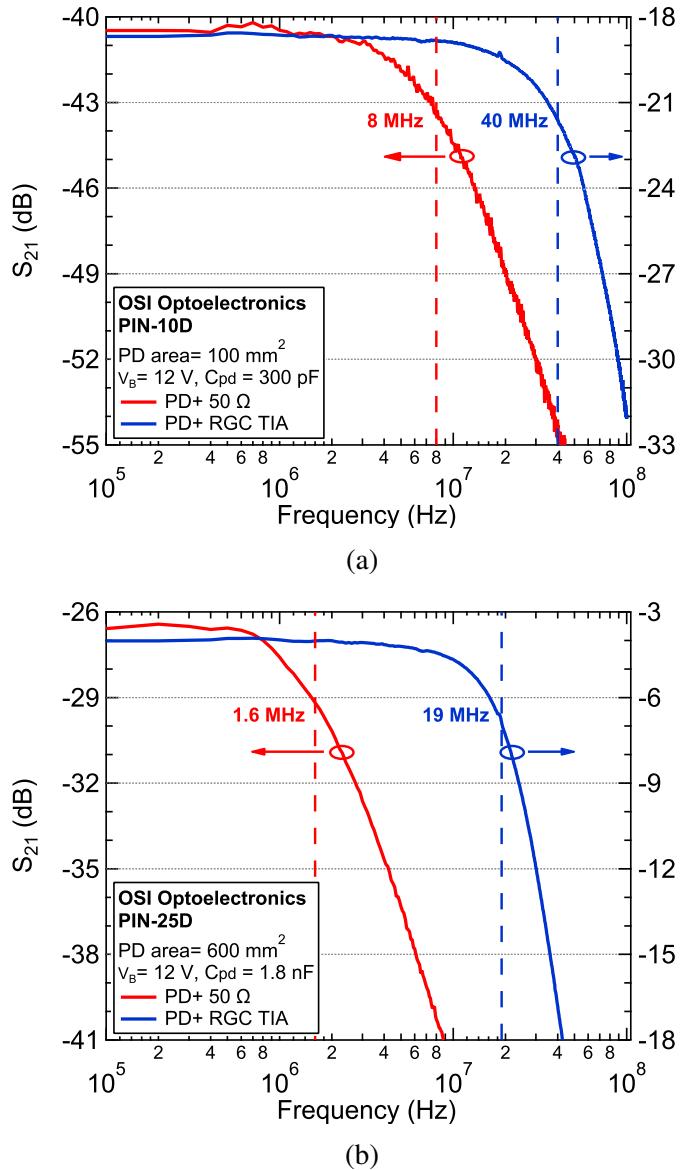

| 7.2.2 Measurements of the RGC TIA . . . . .                                   | 239        |

| 7.3 Photodiode Modelling & Parameter Extraction . . . . .                     | 246        |

| 7.3.1 Photodiode Equivalent Model . . . . .                                   | 246        |

| 7.3.2 Parameter Extraction . . . . .                                          | 251        |

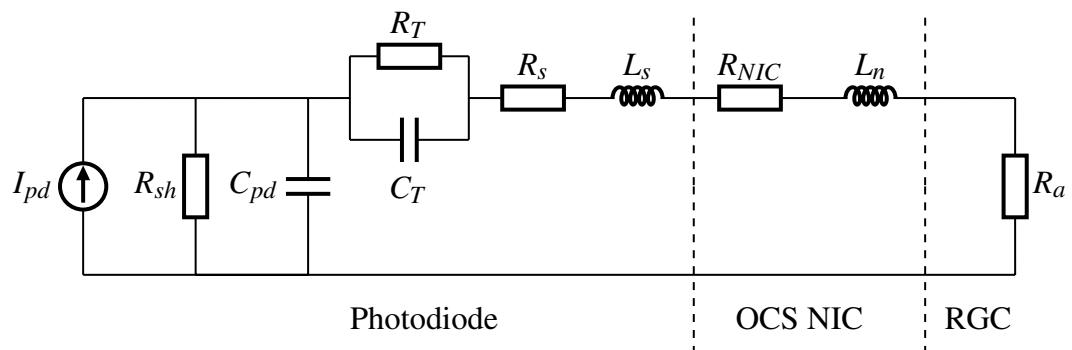

| 7.4 RGC/Modified RGC with the Photodiode Model . . . . .                      | 265        |

| 7.5 Neutralising the Series Resistance of Photodiodes . . . . .               | 268        |

| 7.5.1 Negative Resistance Generation . . . . .                                | 268        |

| 7.5.2 Negative Resistance-RGC TIA for Large Photodiodes . . . . .             | 275        |

| 7.6 Discussion & Conclusions . . . . .                                        | 282        |

|                                                            |            |

|------------------------------------------------------------|------------|

| <b>8 Conclusions</b>                                       | <b>284</b> |

| 8.1 Summary & Discussion . . . . .                         | 284        |

| 8.2 Further Investigations & Research Directions . . . . . | 294        |

| 8.2.1 Further Investigations . . . . .                     | 294        |

| 8.2.2 Future Research Directions . . . . .                 | 295        |

| <b>Appendices</b>                                          | <b>297</b> |

| <b>A Linvill NIC Verification and Measurements</b>         | <b>297</b> |

| A.1 Negative Resistance Generation . . . . .               | 298        |

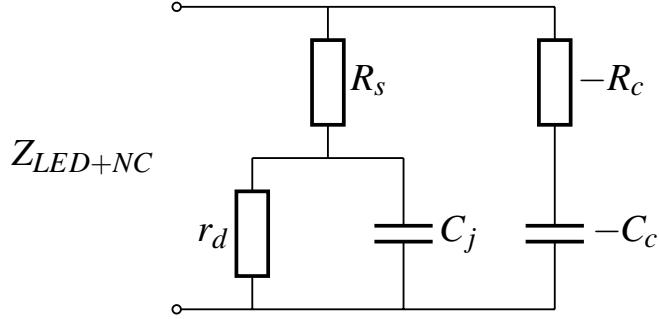

| A.2 Linvill NIC-Photodiode-TIA Equivalent Model . . . . .  | 300        |

| <b>List of References</b>                                  | <b>301</b> |

# List of Figures

|      |                                                                                                                              |    |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | EM spectrum                                                                                                                  | 31 |

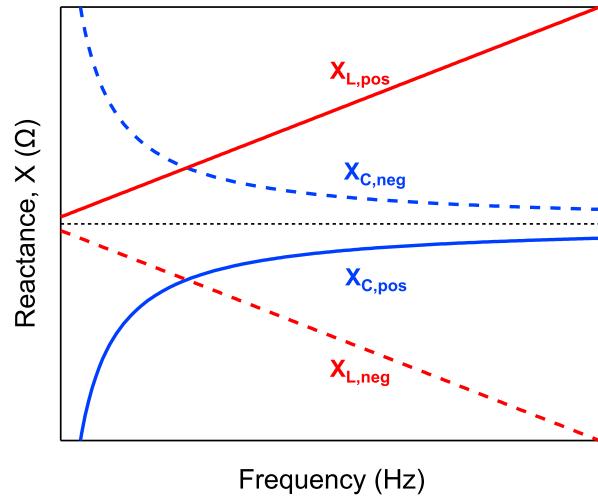

| 2.1  | Solid: reactance of positive (Foster) reactive elements, dashed: reactance of negative (non-Foster) reactive elements        | 48 |

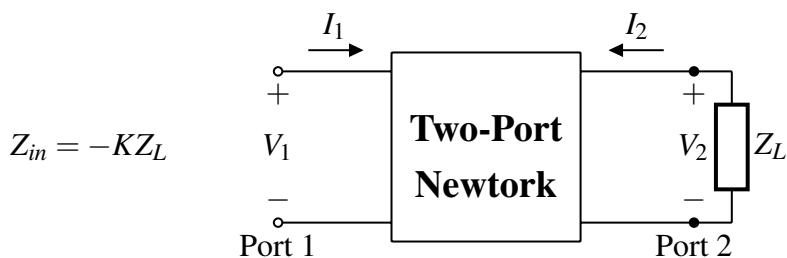

| 2.2  | Ideal two-port network representation of NICs                                                                                | 50 |

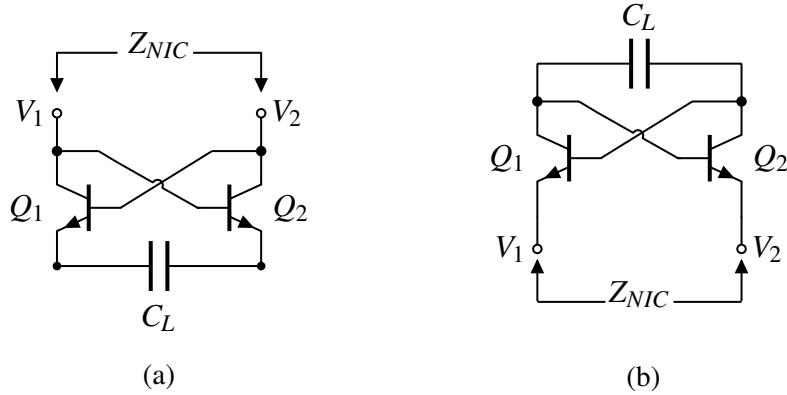

| 2.3  | Linvill's balanced NIC implementation generating negative capacitance (a) SCS NIC (b) OCS NIC                                | 52 |

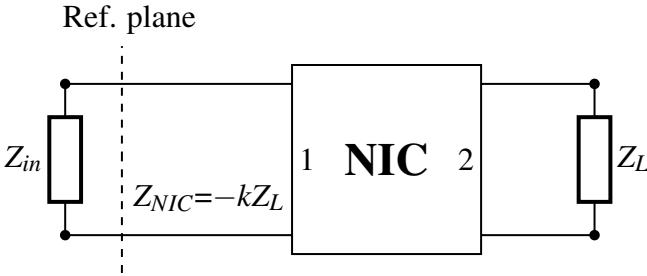

| 2.4  | NIC stability using reference plane method as in [79]                                                                        | 53 |

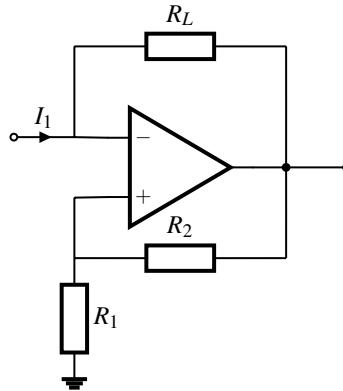

| 2.5  | Op-amp current inversion NIC circuit                                                                                         | 57 |

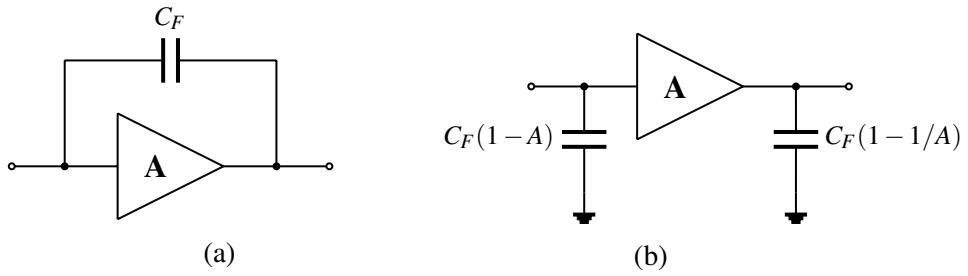

| 2.6  | Negative capacitance circuit and its Miller equivalent circuit                                                               | 60 |

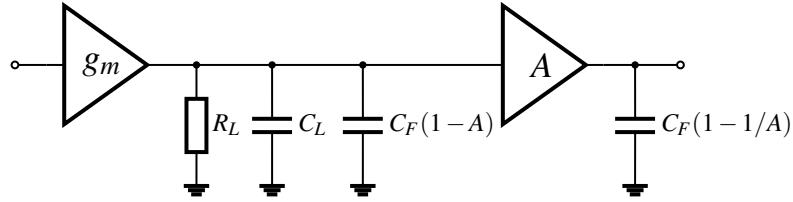

| 2.7  | Negative capacitance circuit ( $A > 1$ ) attached to an amplifier output to compensate for its output load capacitance $C_L$ | 61 |

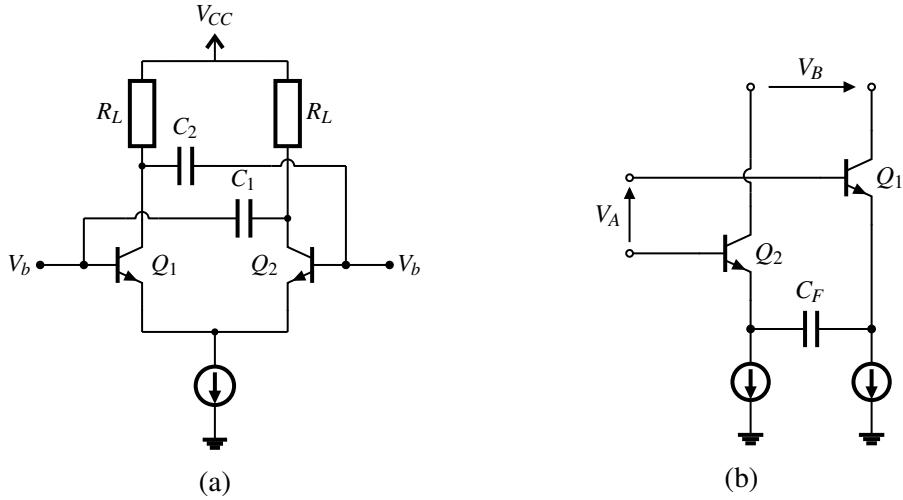

| 2.8  | (a) $C_c$ neutralisation in differential stages (b) Parasitic capacitance compensation circuit proposed by Wakamito in [61]  | 62 |

| 2.9  | Parasitic capacitance compensation circuit proposed by Vadipour in [62]                                                      | 63 |

| 2.10 | Parasitic capacitance compensation circuit proposed by Centurelli in [63]                                                    | 64 |

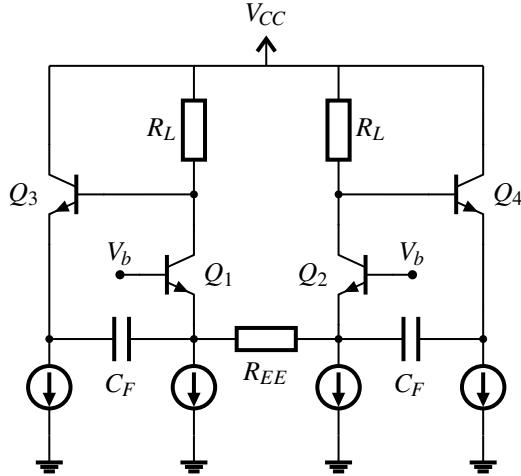

| 2.11 | Negative capacitance circuit proposed by Golden in [46]                                                                      | 67 |

| 3.1  | Proposed negative capacitance circuit                                                                                        | 74 |

| 3.2  | Simplified equivalent circuit model of the negative capacitance circuit                                                      | 74 |

|      |                                                                                                                                                                                                                                                                                |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

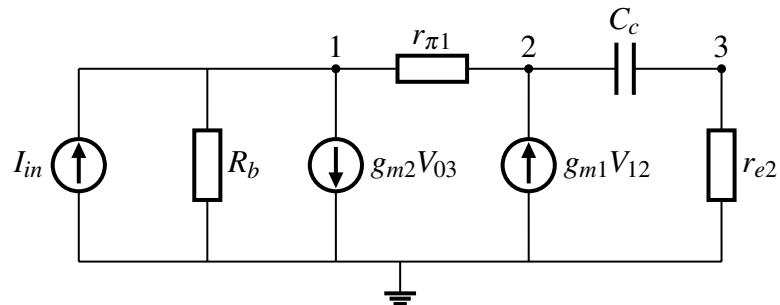

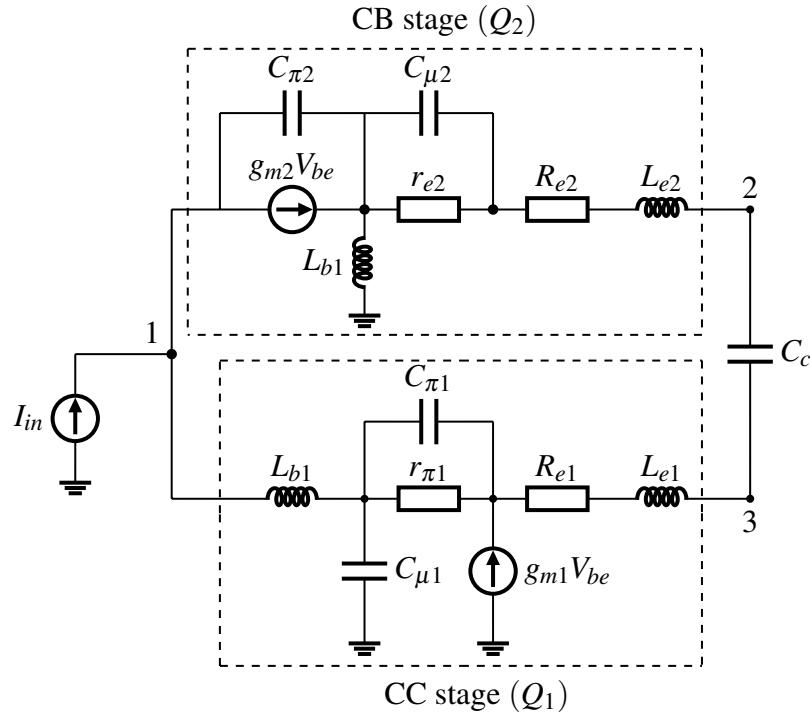

| 3.3  | Simulations of negative capacitance simplified equivalent circuit model vs. full transistor circuit (a) $R_c$ (b) $X_c$ (c) derived $-C_c$ . Figures on the left $R_b = \infty$ , Figures on the right $R_b = 800 \Omega$ . . . . .                                            | 77 |

| 3.4  | Semi-empirical equivalent circuit model of the negative capacitance circuit with reference to nodes in Figure 3.1 . . . . .                                                                                                                                                    | 80 |

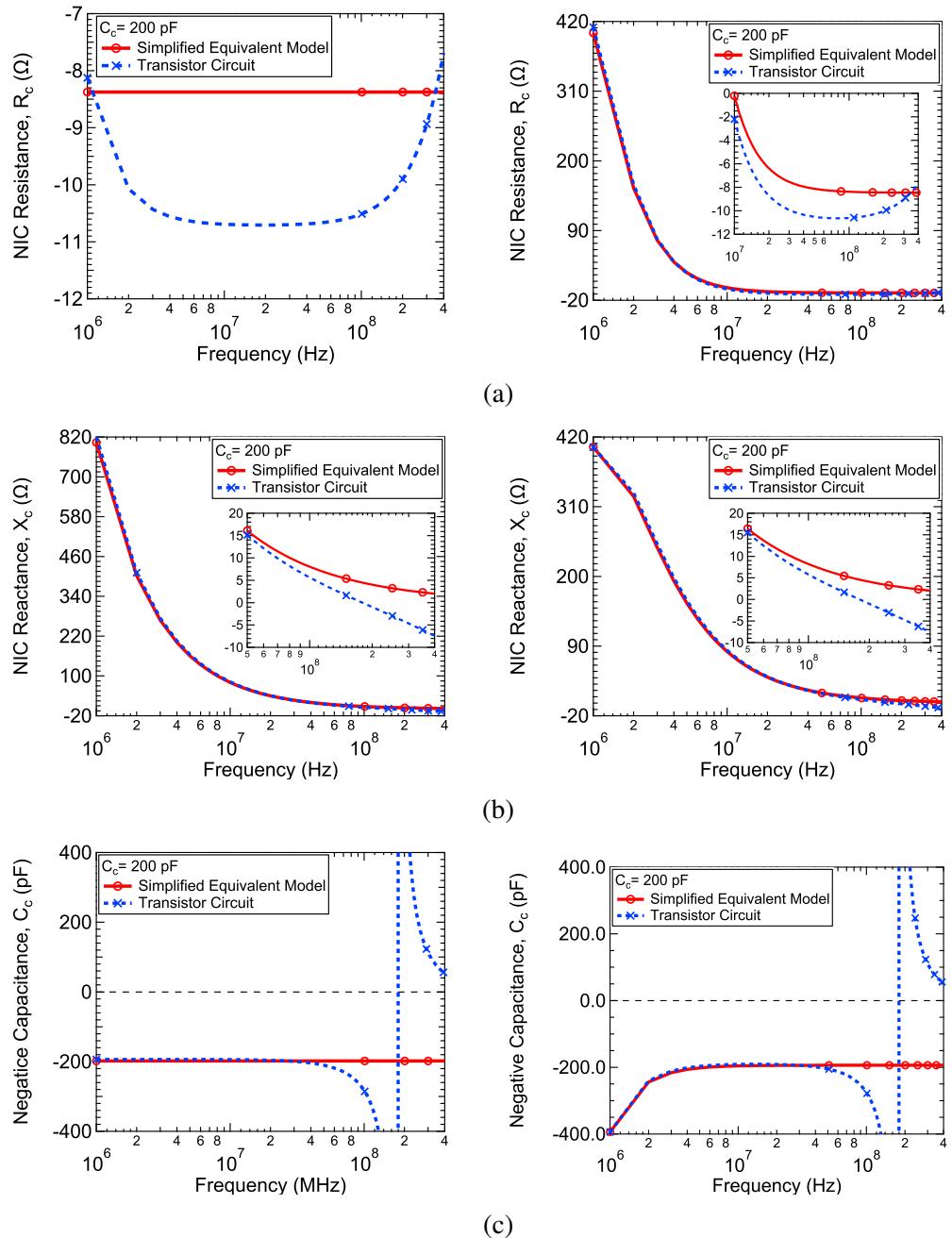

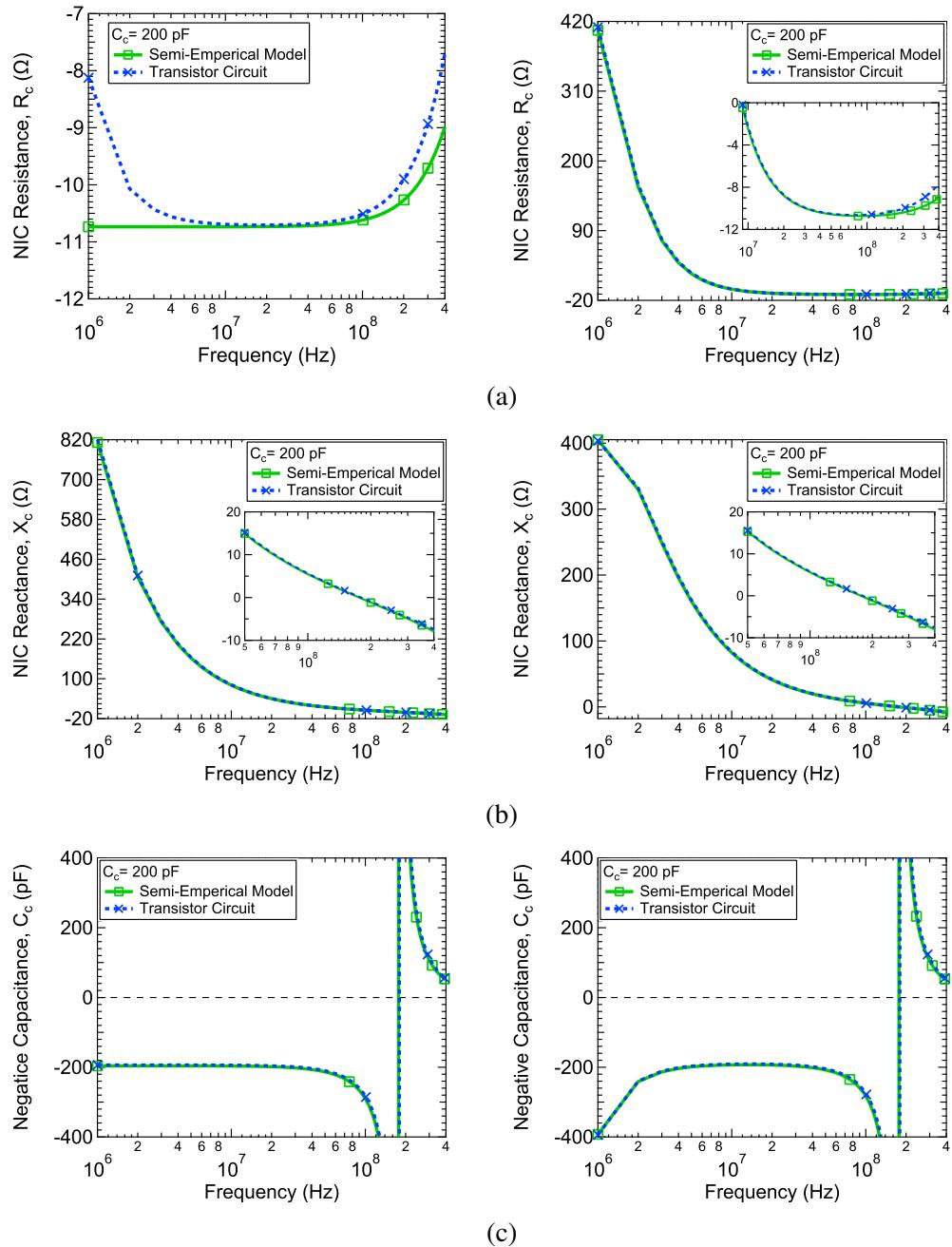

| 3.5  | Simulations of the negative capacitance circuit semi-empirical vs. full transistor circuit (a) $R_c$ (b) $X_c$ (c) derived $-C_c$ . Figures on the left $R_b = \infty$ , Figures on the right $R_b = 800 \Omega$ . . . . .                                                     | 81 |

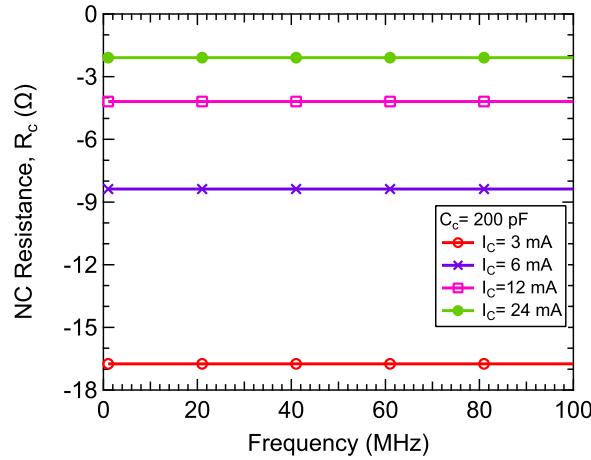

| 3.6  | Simulations of $-R_c$ of the simplified equivalent circuit model of the negative capacitance circuit with increasing $g_m$ . . . . .                                                                                                                                           | 84 |

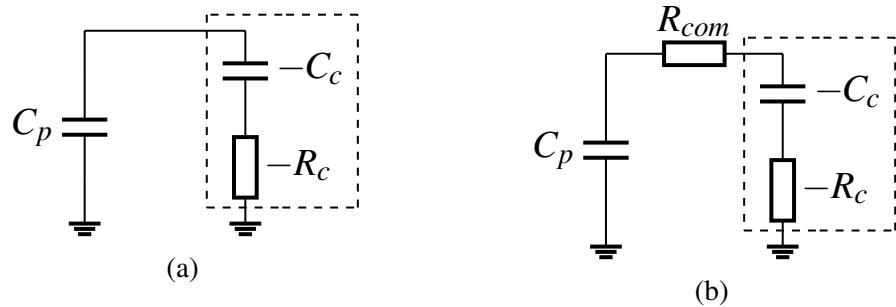

| 3.7  | Passive equivalent circuit model of the simulation set-up used to assess the effect of $-R_c$ on the negative capacitance circuit efficacy in neutralising $C_p$ . . . . .                                                                                                     | 84 |

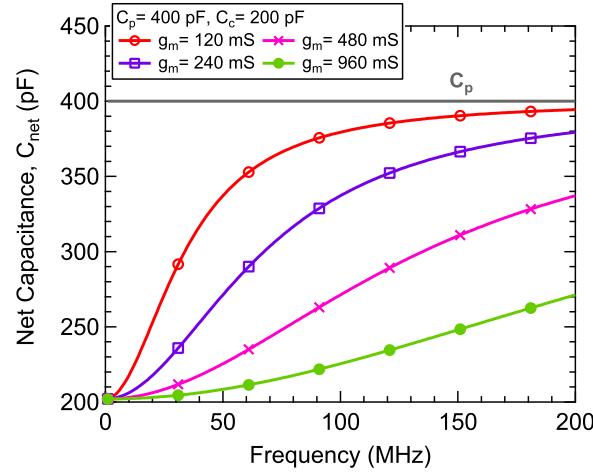

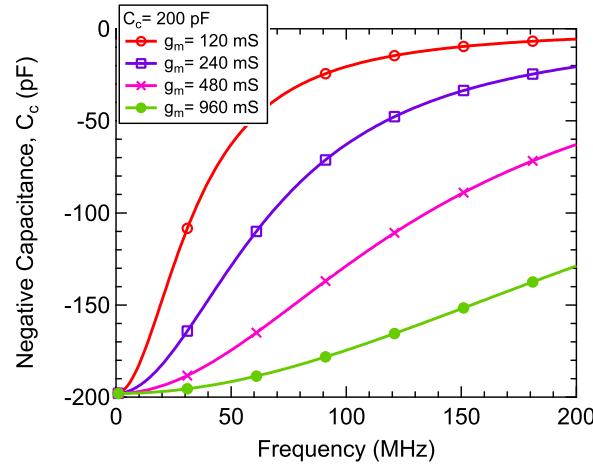

| 3.8  | Simulations of the net capacitance $C_{net}$ at varying $g_m$ . . . . .                                                                                                                                                                                                        | 85 |

| 3.9  | De-embedded effective negative capacitance at varying $g_m$ . . . . .                                                                                                                                                                                                          | 85 |

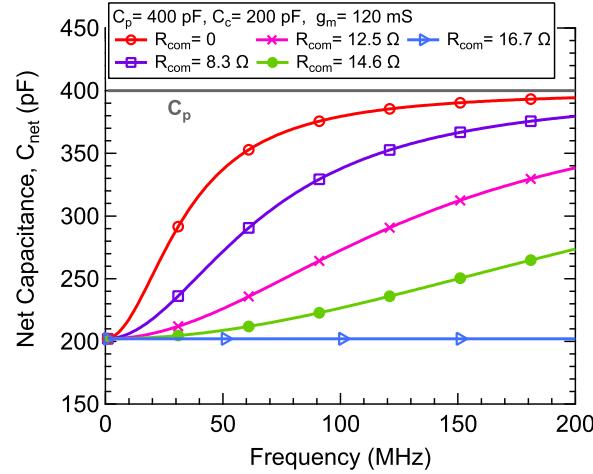

| 3.10 | Net Capacitance at $g_m = 120 \text{ mS}$ with the addition of compensating resistor compensating resistor ( $R_{com}$ ) . . . . .                                                                                                                                             | 87 |

| 3.11 | Passive equivalent model of the simulation set-up used to assess the effect of $-R_c$ on the negative capacitance efficacy to neutralise $C_p$ . .                                                                                                                             | 88 |

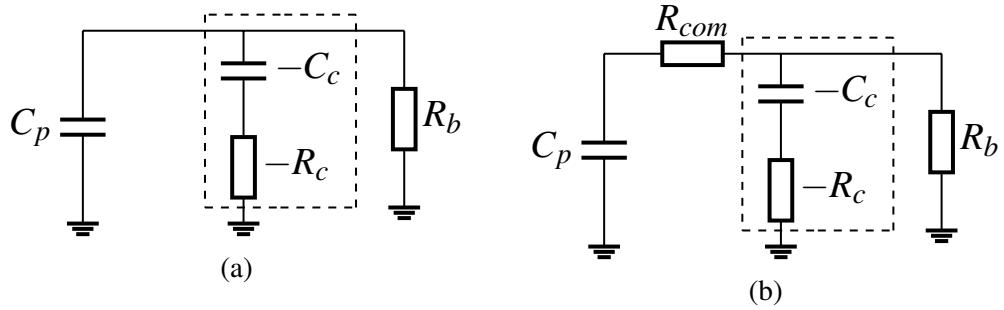

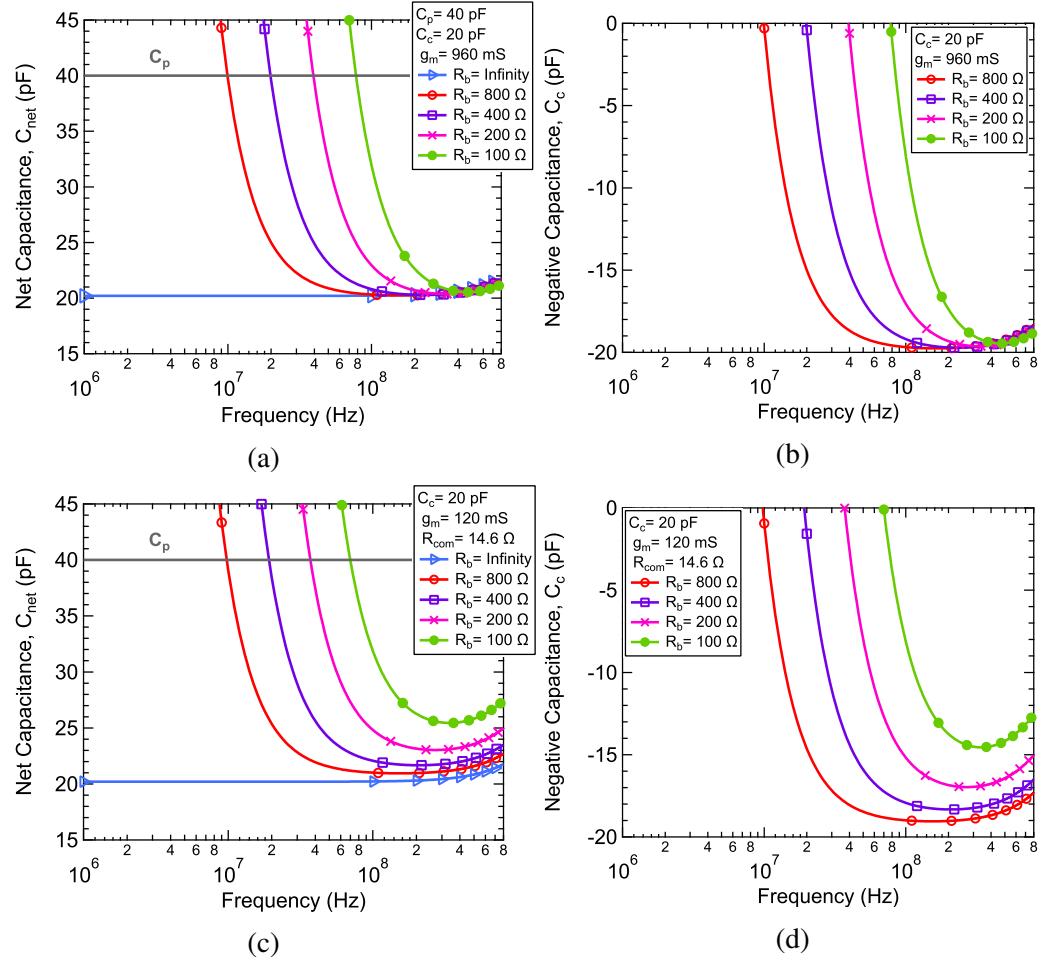

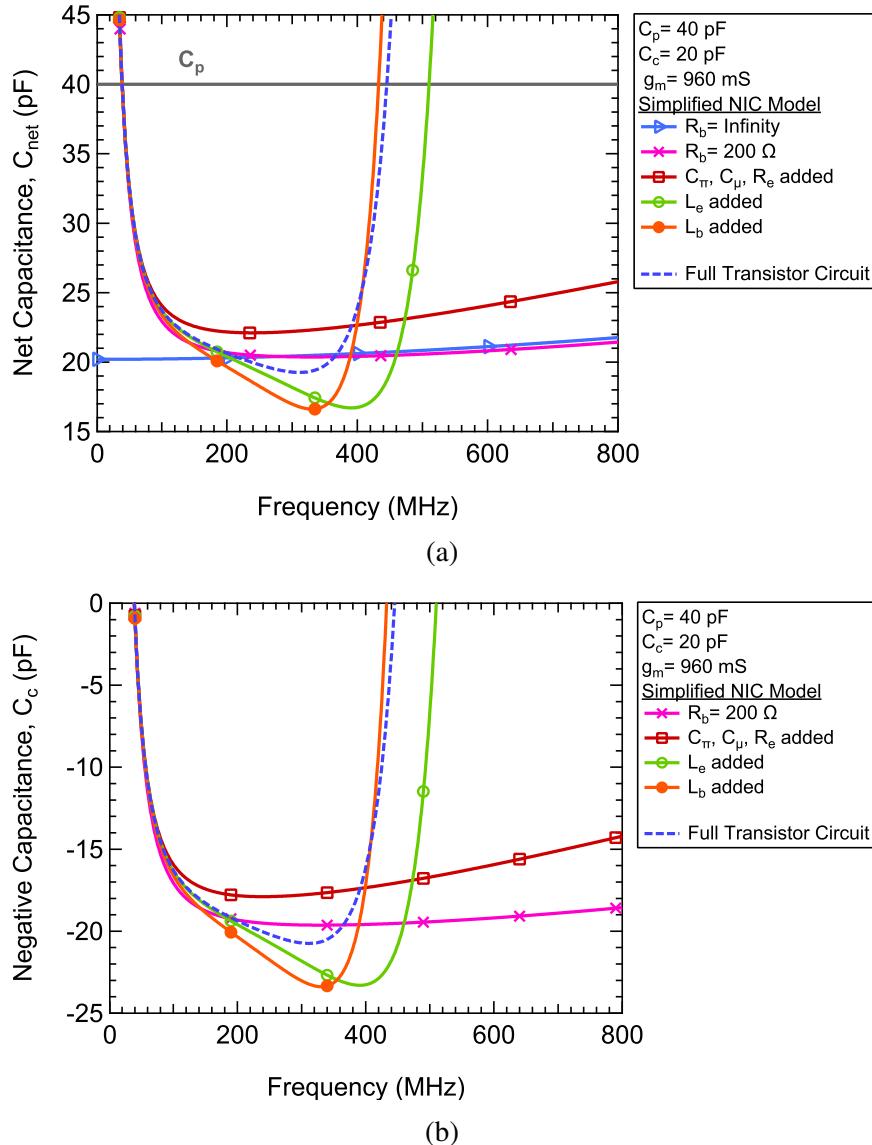

| 3.12 | Simulations of $C_{net}$ and de-embedded $-C_c$ of the negative capacitance circuit simplified equivalent model including $R_b$ at $C_c = 200 \text{ pF}$ at different $I_C$ (a)-(b) $g_m = 960 \text{ mS}$ (c)-(d) $g_m = 120 \text{ mS}$ , $R_{com} = 14.6 \Omega$ . . . . . | 89 |

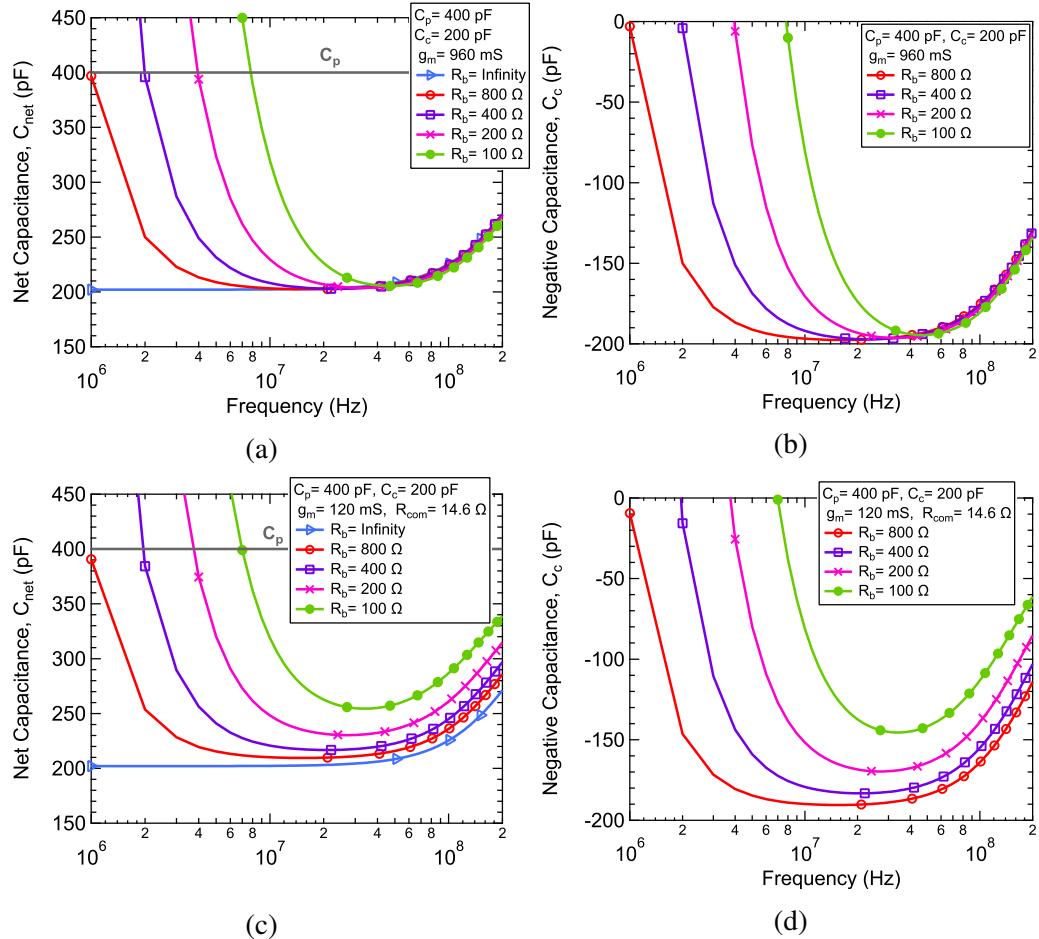

| 3.13 | Simulations of $C_{net}$ and de-embedded $-C_c$ of the negative capacitance circuit simplified equivalent model including $R_b$ at $C_c = 20 \text{ pF}$ at different $I_C$ (a)-(b) $g_m = 960 \text{ mS}$ (c)-(d) $g_m = 120 \text{ mS}$ , $R_{com} = 14.6 \Omega$ . . . . .  | 91 |

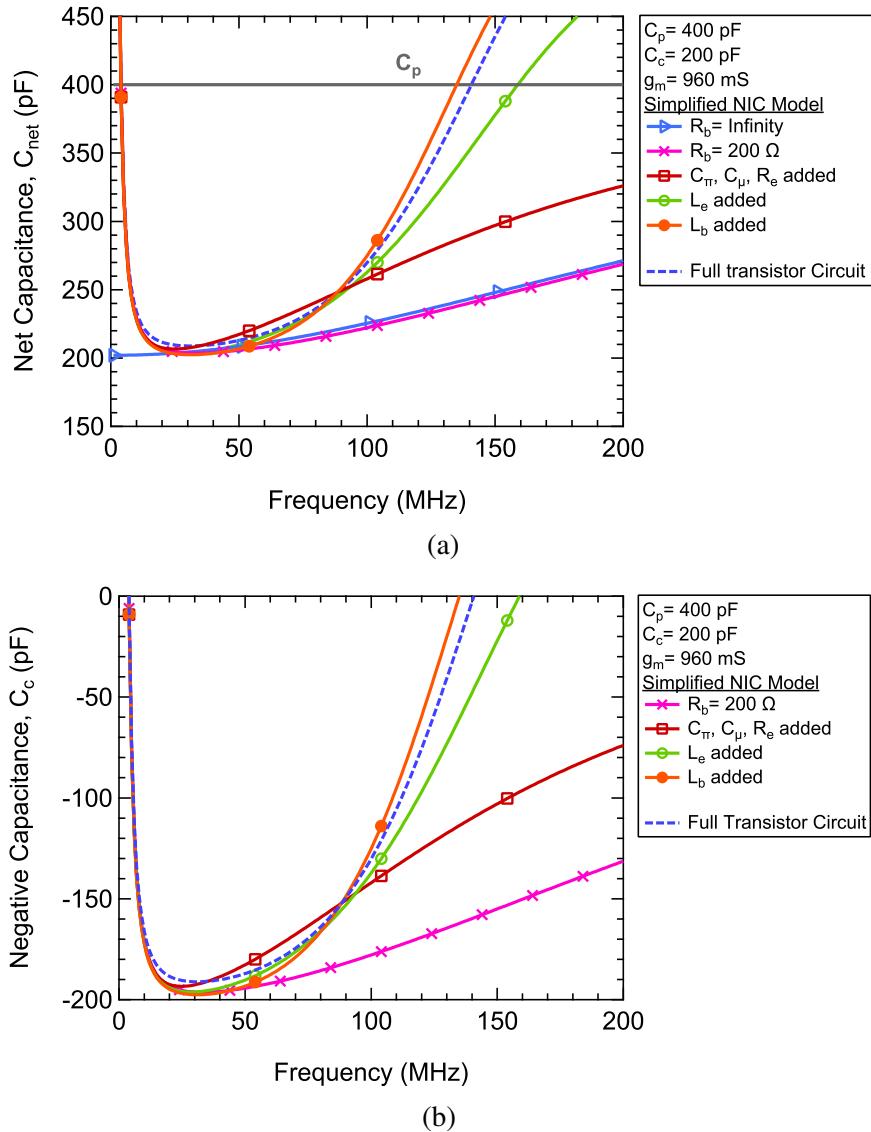

| 3.14 | Simulations illustrating the effects of the non-ideal transistors vs. full transistor circuit at $C_c = 200 \text{ pF}$ (a) $C_{net}$ (b) $-C_c$ . . . . .                                                                                                                     | 94 |

|      |                                                                                                                                                                   |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.15 | Simulations illustrating the effects of the non-ideal transistors vs. full transistor circuit at $C_c = 20$ pF (a) $C_{net}$ (b) $-C_c$ . . . . .                 | 96  |

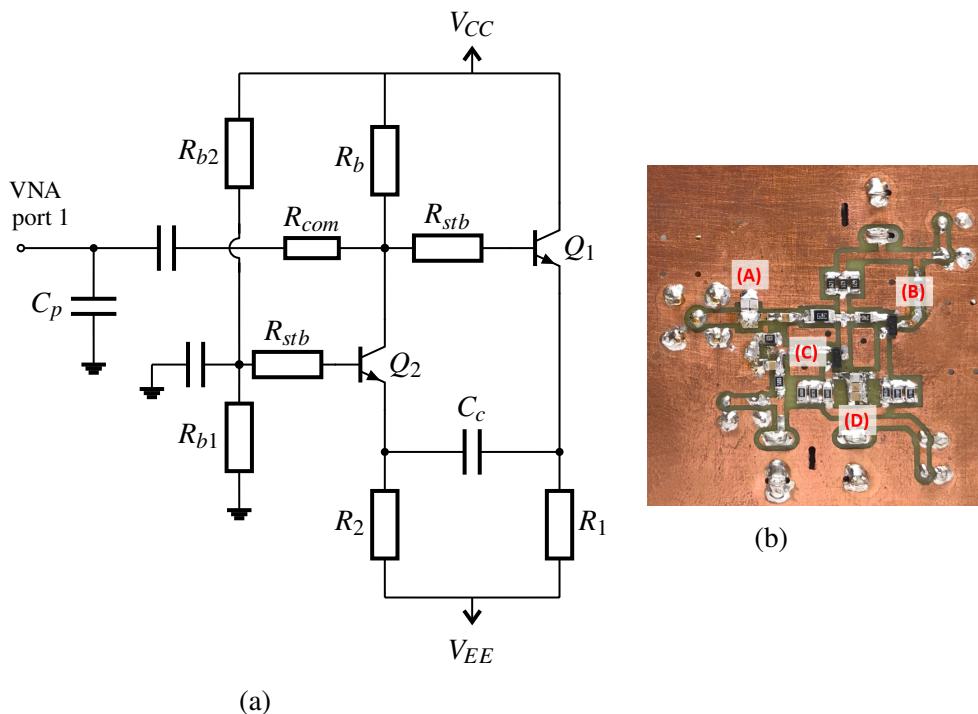

| 3.16 | (a) Full negative capacitance circuit (b) Fabricated negative capacitance circuit PCB (A) $C_p$ (B) CC stage ( $Q_1$ ) (C) CB stage ( $Q_2$ ) (D) $C_c$ . . . . . | 97  |

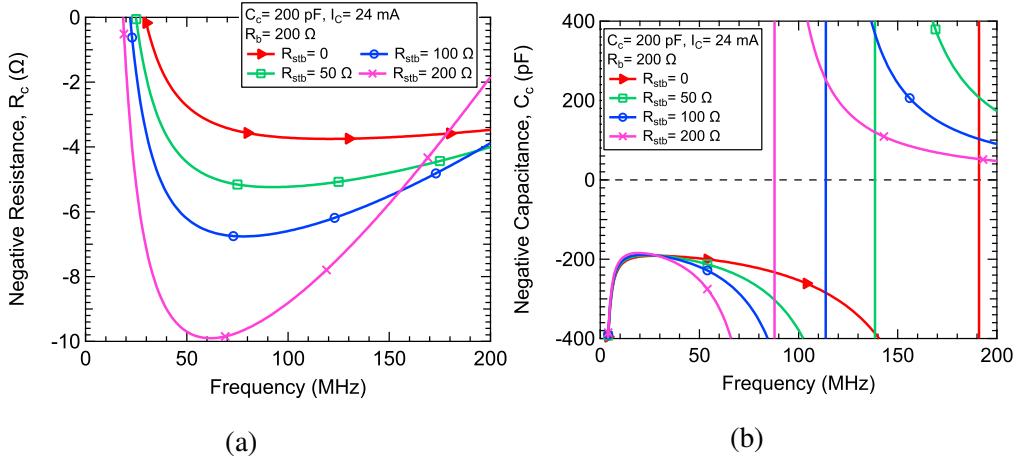

| 3.17 | Simulations of the negative capacitance transistor circuit showing the effect of stabilising resistor ( $R_{stb}$ ) on (a) $-R_c$ (b) $-C_c$ . . . . .            | 99  |

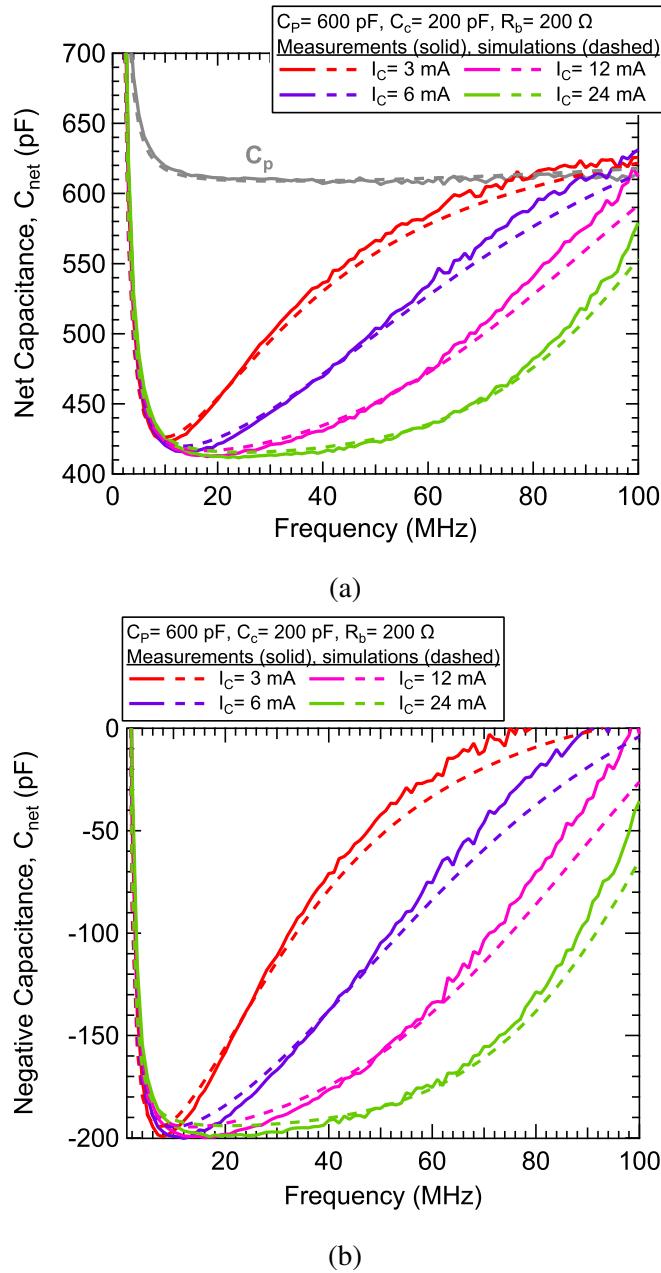

| 3.18 | Measured and simulated $C_{net}$ and $-C_c$ for $C_p = 600$ pF and $C_c = 200$ pF at varying $I_C$ . . . . .                                                      | 101 |

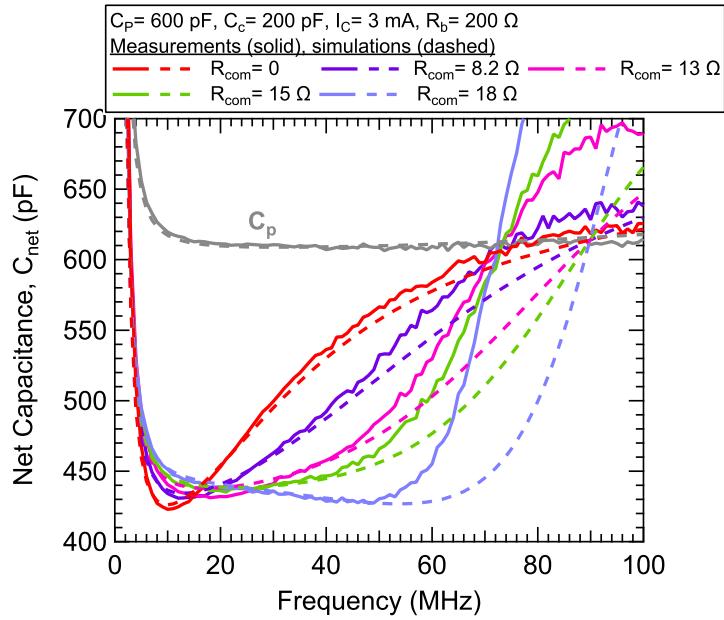

| 3.19 | Measured and simulated $C_{net}$ and $-C_c$ for $C_p = 600$ pF and $C_c = 200$ pF at $I_C = 3$ mA and varying $R_{com}$ . . . . .                                 | 103 |

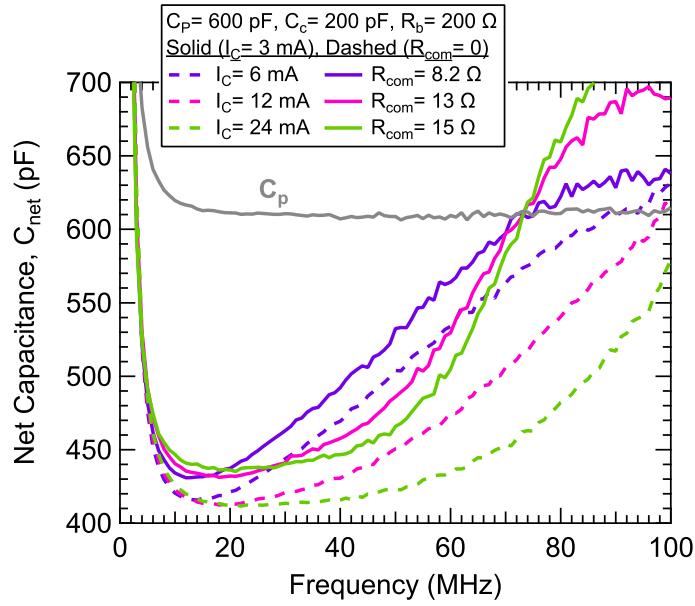

| 3.20 | Comparison of measured $C_{net}$ at varying $I_C$ versus at fixed $I_C = 3$ mA and varying $R_{com}$ . . . . .                                                    | 105 |

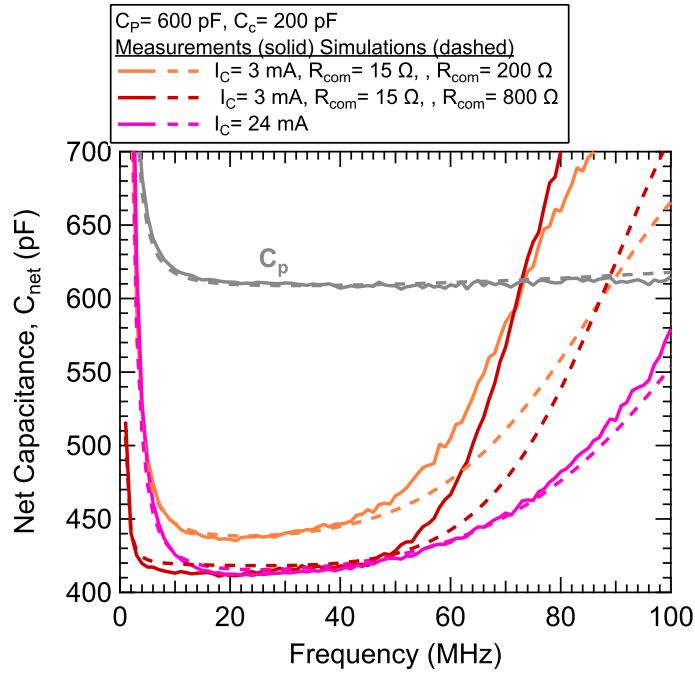

| 3.21 | Comparison of measured and simulated $C_{net}$ at $I_C = 3$ mA, $R_{com} = 15 \Omega$ at $R_b = 200$ and $800 \Omega$ versus for varying $I_C = 24$ mA . . . . .  | 105 |

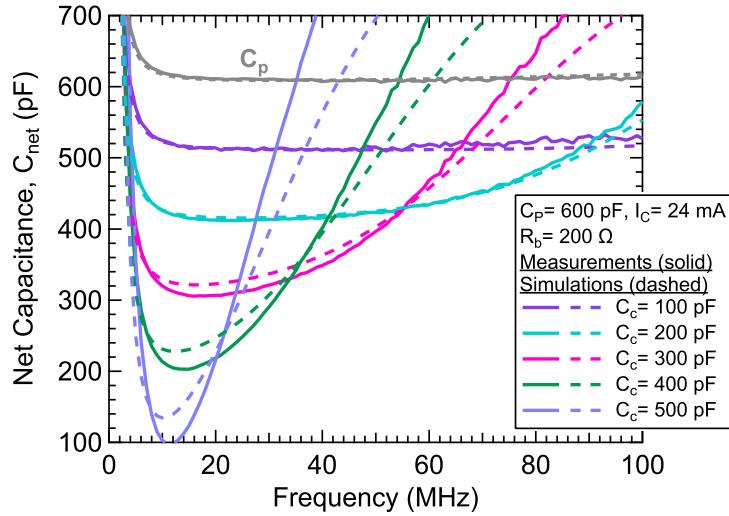

| 3.22 | Measured and simulated $C_{net}$ at $I_C = 24$ mA for varying $C_c$ . . . . .                                                                                     | 108 |

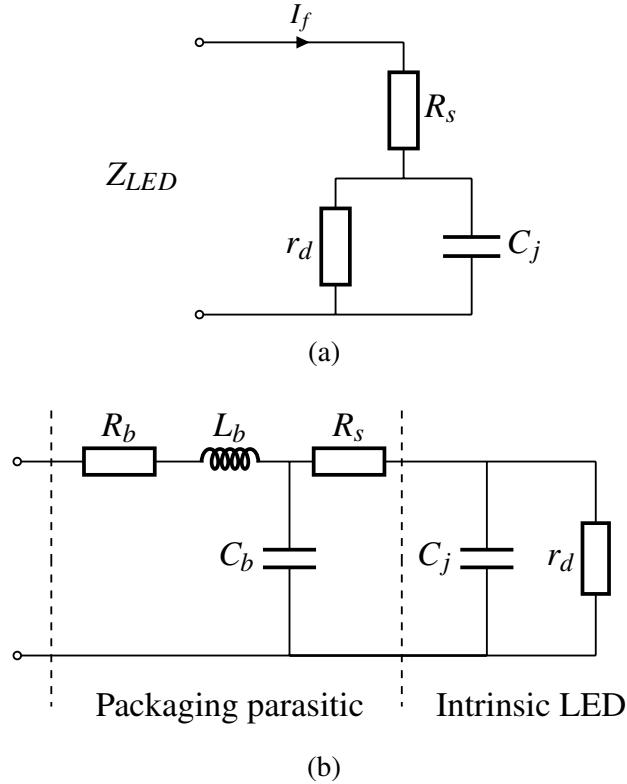

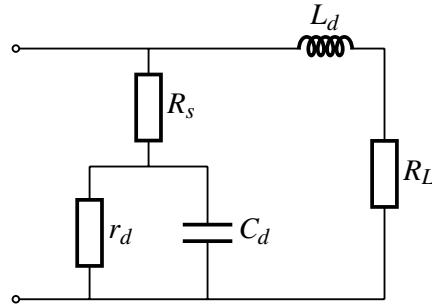

| 4.1  | (a) Low frequency LED passive equivalent model reported in [99, 100] (b) High frequency LED equivalent model reported in [101] . .                                | 114 |

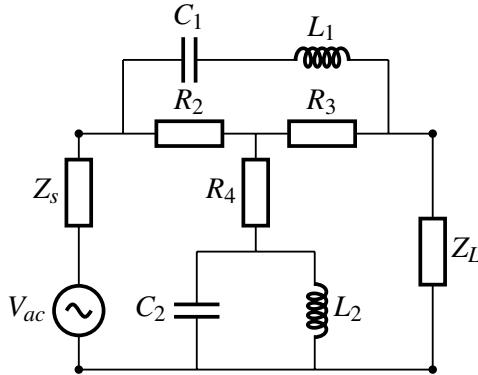

| 4.2  | Multi-resonance circuit diagram, including bias-T and LED proposed in [15] . . . . .                                                                              | 117 |

| 4.3  | Symmetrical bridged-T amplitude equaliser reported in [19] . . . . .                                                                                              | 118 |

| 4.4  | LED equivalent circuit with $C_d$ incorporated into ATL reported in [20] . . . . .                                                                                | 119 |

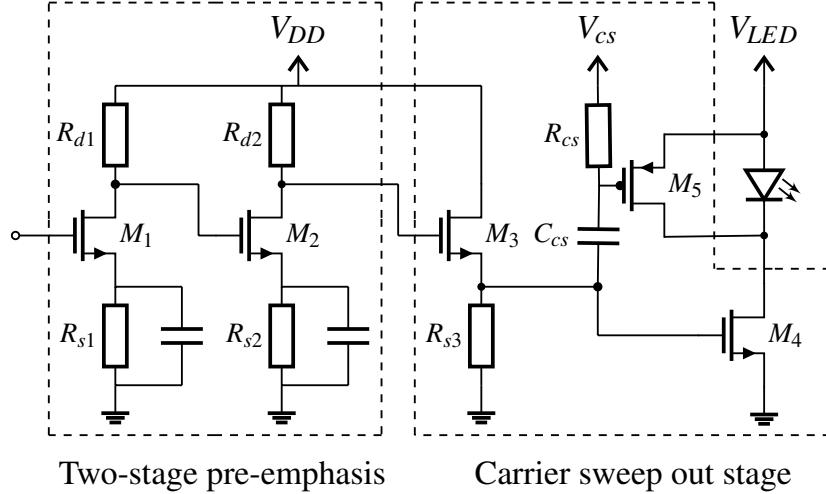

| 4.5  | LED driver employing both pre-emphasis and carrier sweep out circuit                                                                                              | 120 |

| 4.6  | LED and NC simplified equivalent model . . . . .                                                                                                                  | 123 |

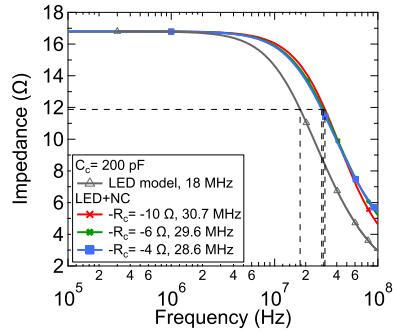

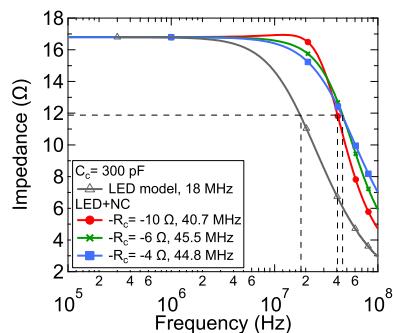

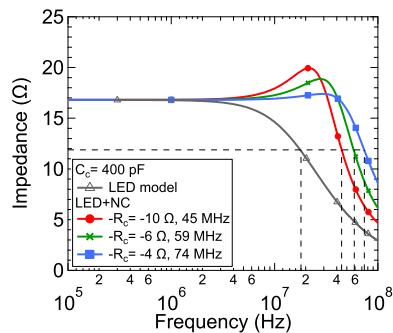

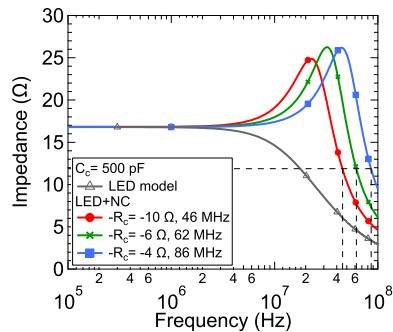

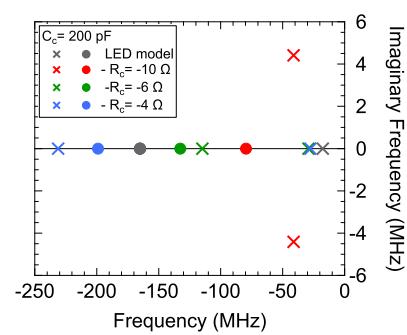

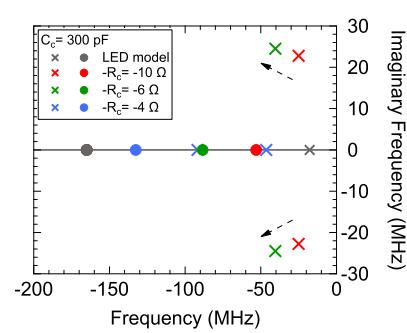

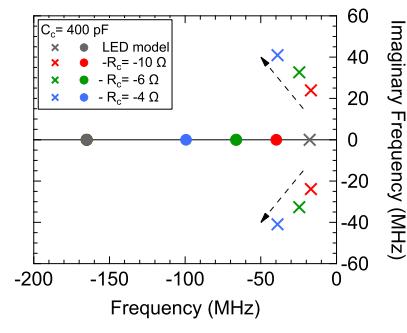

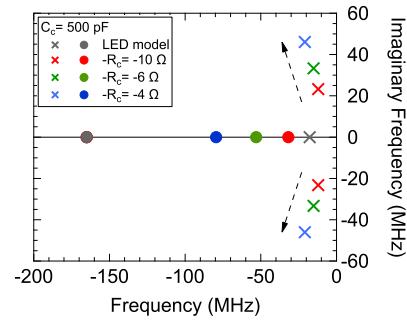

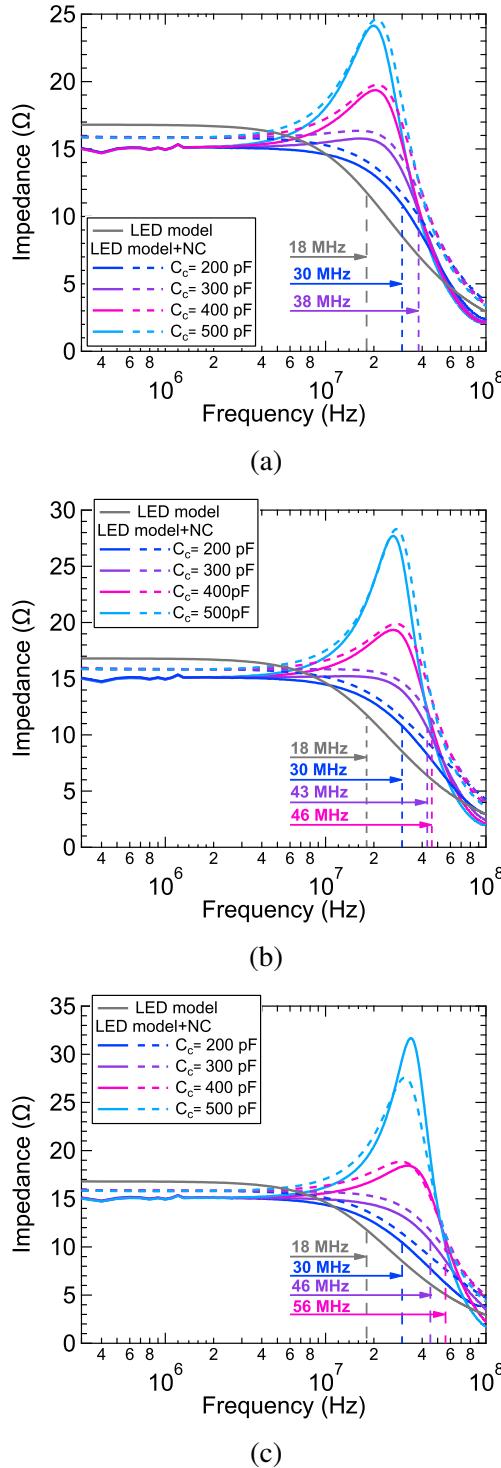

| 4.7  | Impedance of the LED+NC model at variable $-R_c$ for $C_c$ (a) 200 pF (b) 300 pF (c) 400 pF (d) 500 pF . . . . .                                                  | 127 |

| 4.8  | pole-zero action of LED+NC model at variable $-R_c$ for $C_c$ (a) 200 pF (b) 300 pF (c) 400 pF (d) 500 pF . . . . .                                               | 127 |

|      |                                                                                                                                                                                                                                             |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

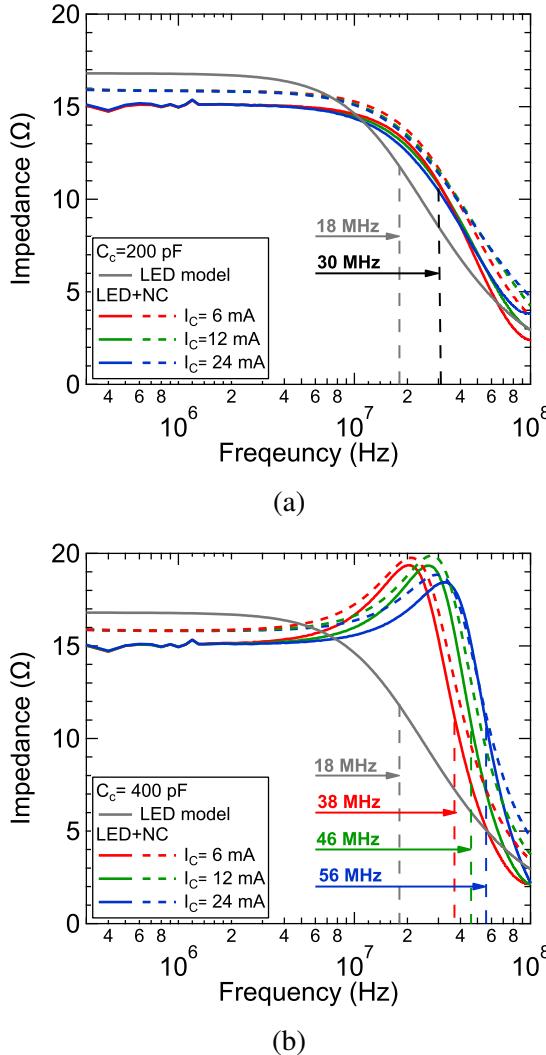

| 4.9  | Measured (solid) and simulated (dashed) impedance of the LED equivalent circuit model when connected to the negative capacitance circuit for different values of $C_c$ under (a) $I_C = 6$ mA (b) $I_C = 12$ mA (c) $I_C = 24$ mA . . . . . | 129 |

| 4.10 | Measured (solid) and simulated (dashed) impedance of the LED equivalent model when connected to the negative capacitance circuit for different $I_C$ at (a) $C_c = 200$ pF (b) $C_c = 400$ pF . . . . .                                     | 131 |

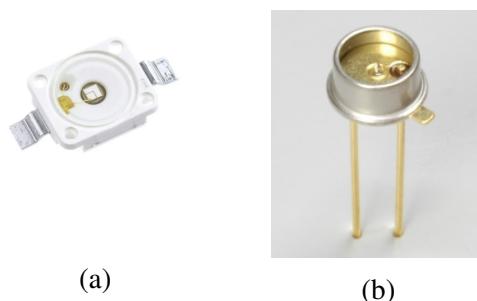

| 4.11 | LEDs under test (a) Blue (b) Red . . . . .                                                                                                                                                                                                  | 133 |

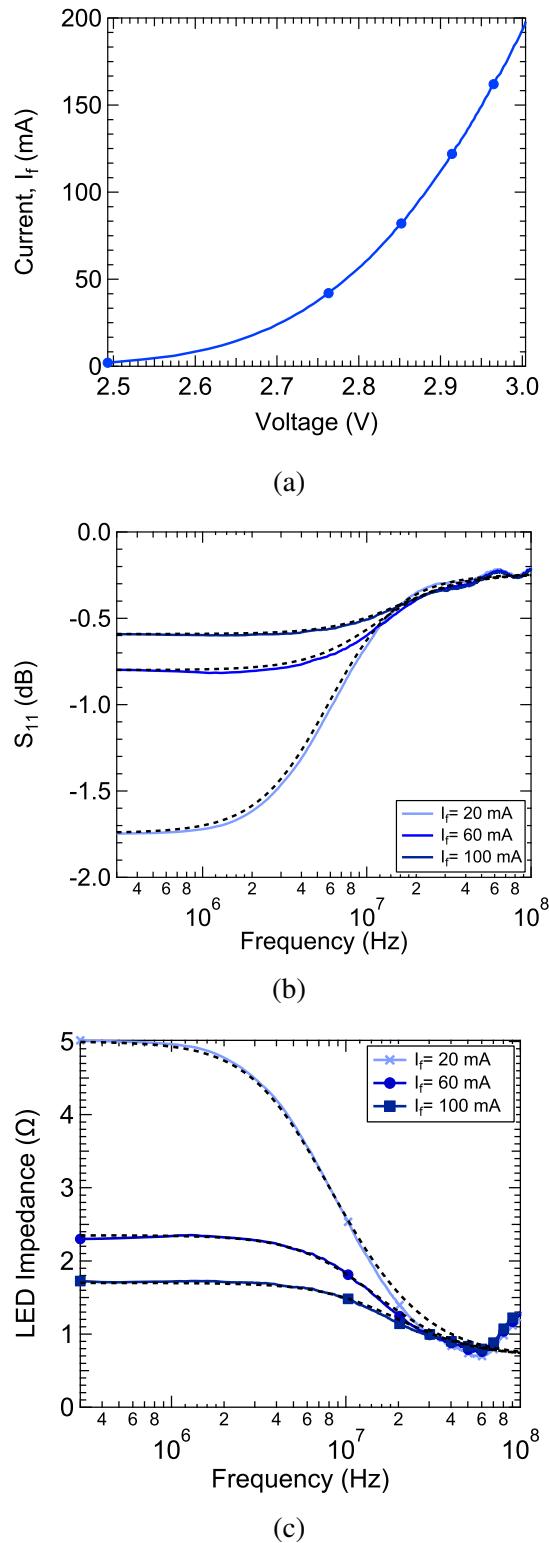

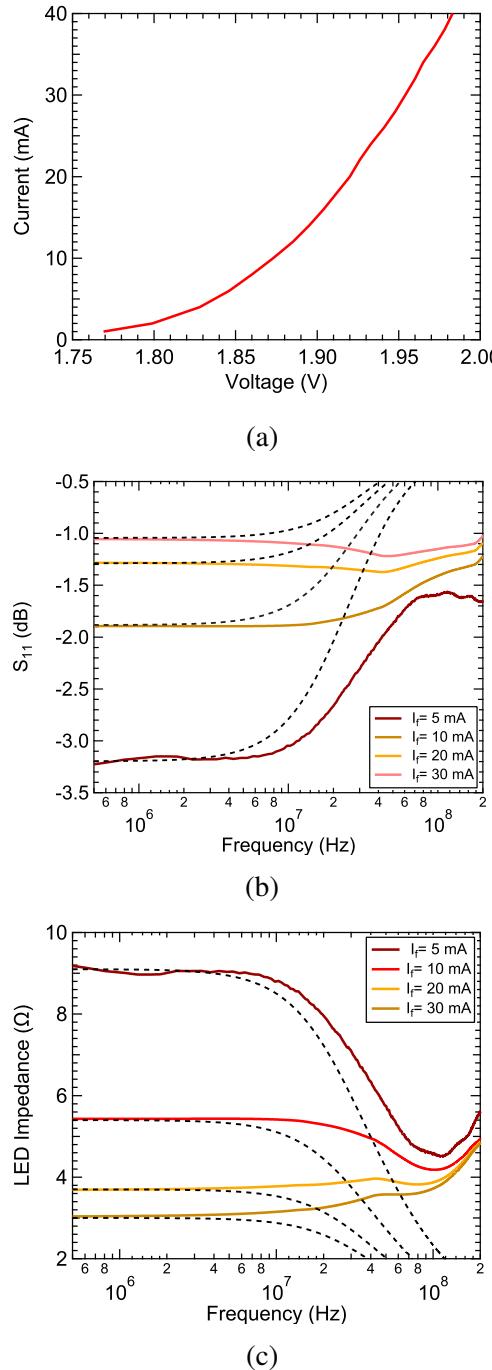

| 4.12 | Measured (solid) and fitted model (dashed) blue LED responses (a) IV characteristics (b) $S_{11}$ (c) $Z_{11}$ . . . . .                                                                                                                    | 136 |

| 4.13 | Measured $S_{21}$ of the blue LED at different $I_f$ . . . . .                                                                                                                                                                              | 137 |

| 4.14 | Measured (solid) and fitted model (dashed) red LED responses (a) IV characteristics (b) $S_{11}$ (c) $Z_{11}$ . . . . .                                                                                                                     | 139 |

| 4.15 | Measured $S_{21}$ of the red LED at different $I_f$ . . . . .                                                                                                                                                                               | 140 |

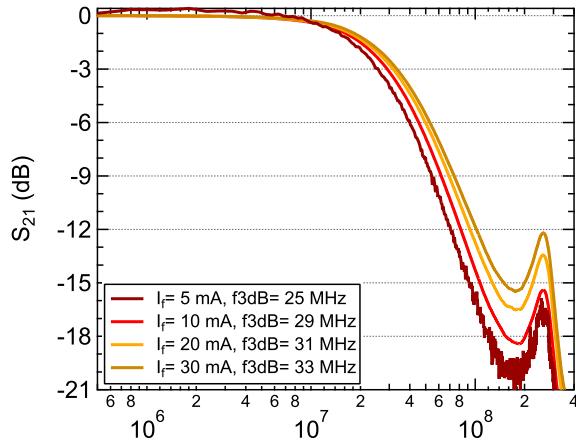

| 4.16 | Test set-up to measure LED+NC impedance and $S_{21}$ . . . . .                                                                                                                                                                              | 141 |

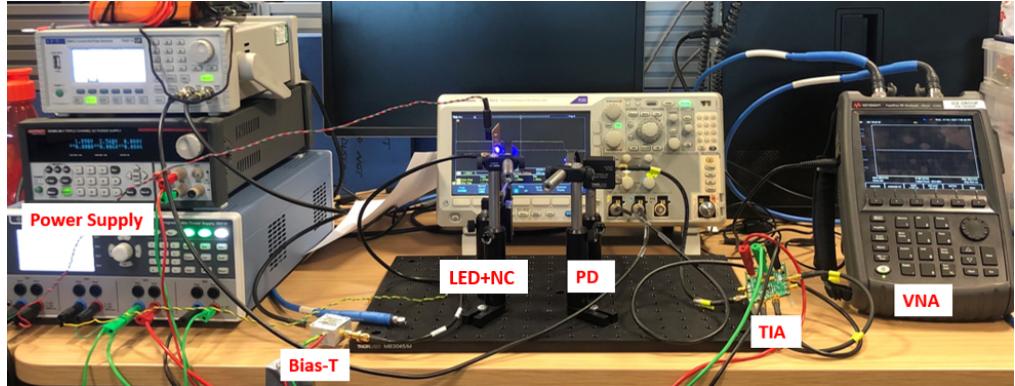

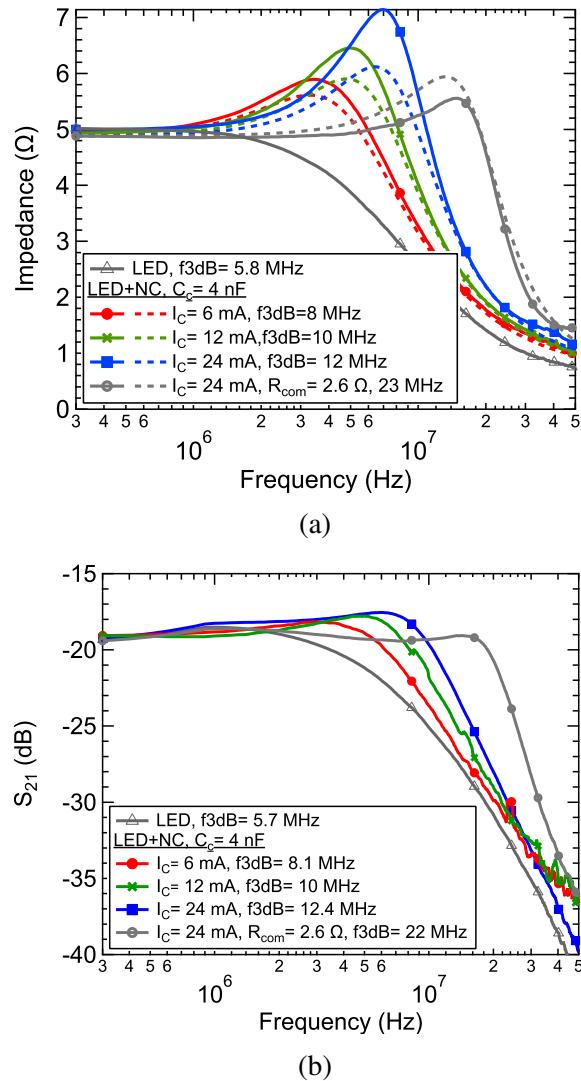

| 4.17 | Measured blue LED responses at $I_f = 20$ mA and $C_c = 4$ nF for different negative capacitance circuit bias currents $I_C$ (a) $Z_{11}$ (b) $S_{21}$ . . . . .                                                                            | 143 |

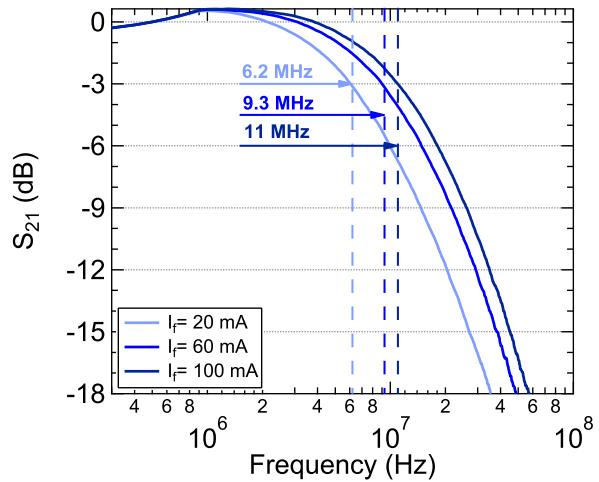

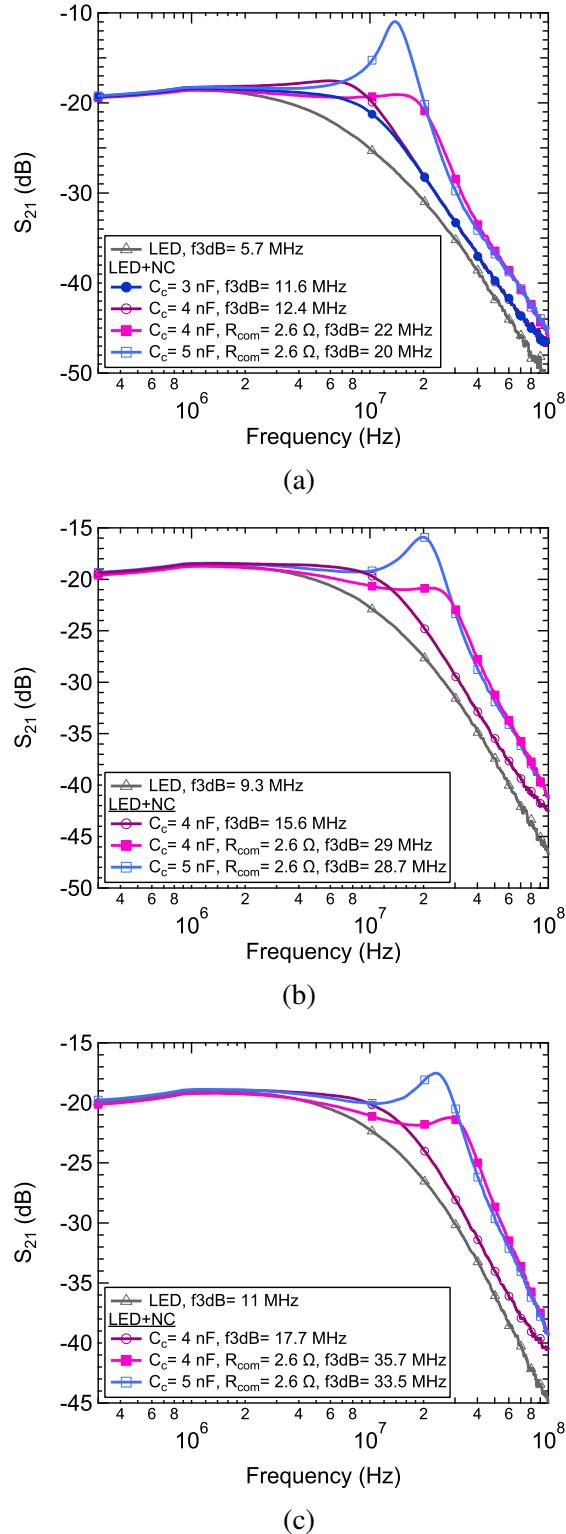

| 4.18 | Blue LED $S_{21}$ magnitude measurements at $I_C = 24$ mA for different LED forward current $I_f$ (a) 20 mA (b) 60 mA (c) 100 mA . . . . .                                                                                                  | 145 |

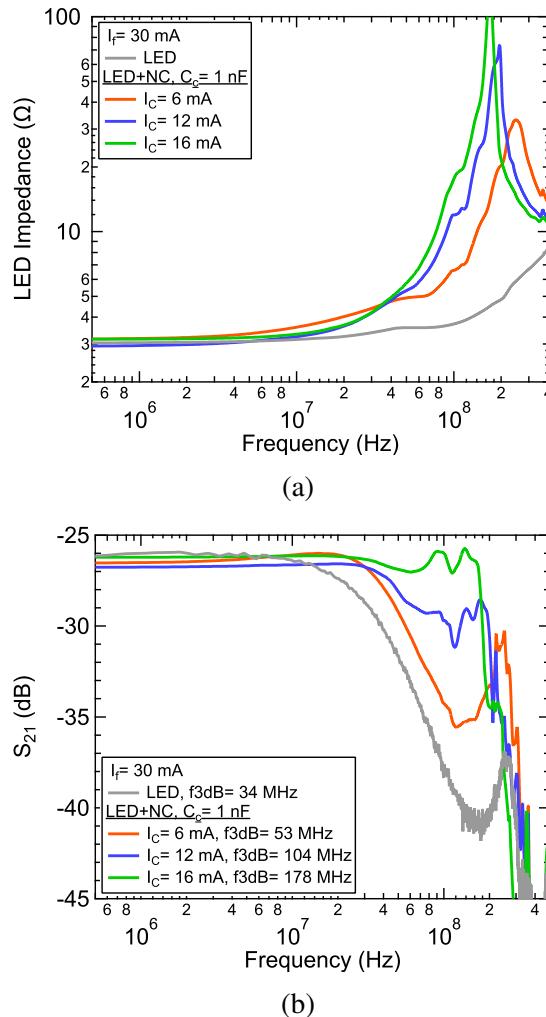

| 4.19 | Measured red LED responses at $I_f = 30$ mA and $C_c = 1$ nF for different $I_C$ (a) $Z_{11}$ (b) $S_{21}$ . . . . .                                                                                                                        | 147 |

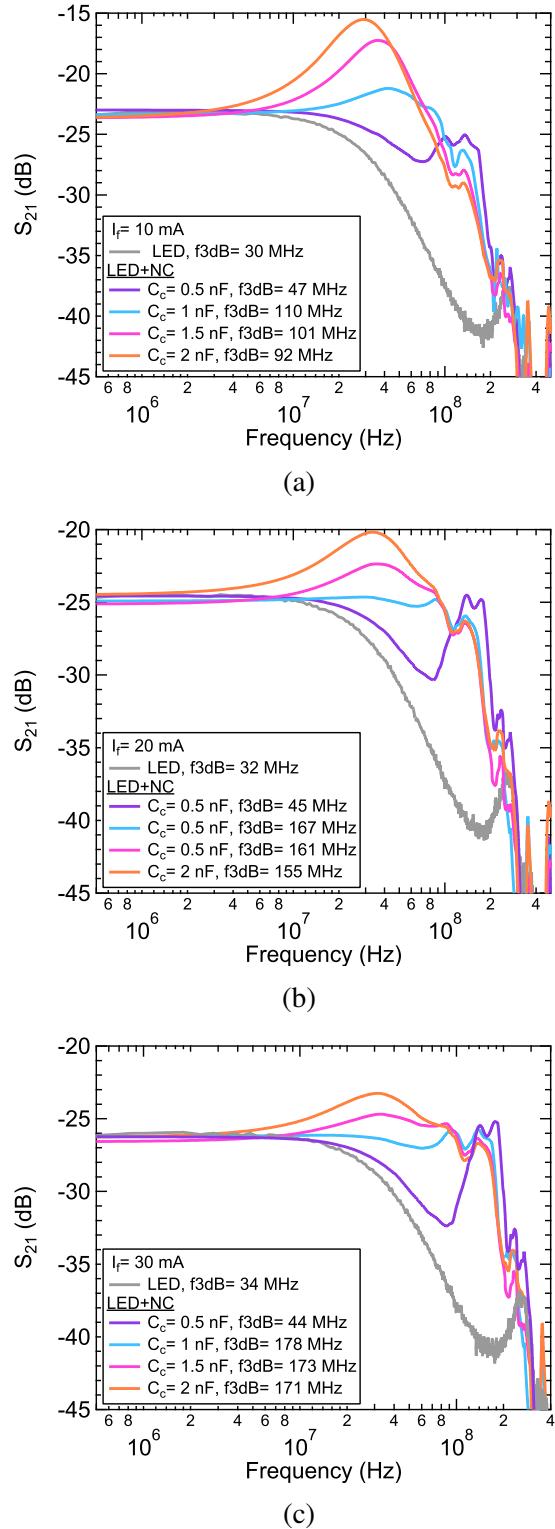

| 4.20 | Measured $S_{21}$ responses of the red LED for different $C_c$ for (a) $I_f = 10$ mA (b) $I_f = 10$ mA (c) $I_f = 30$ mA . . . . .                                                                                                          | 149 |

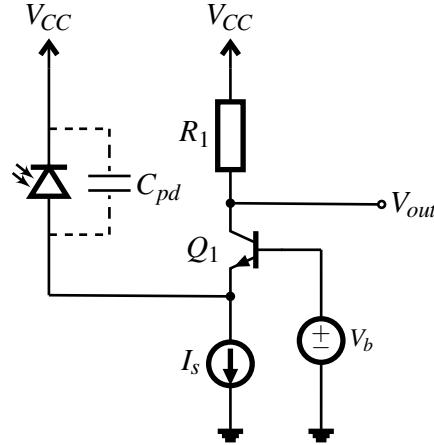

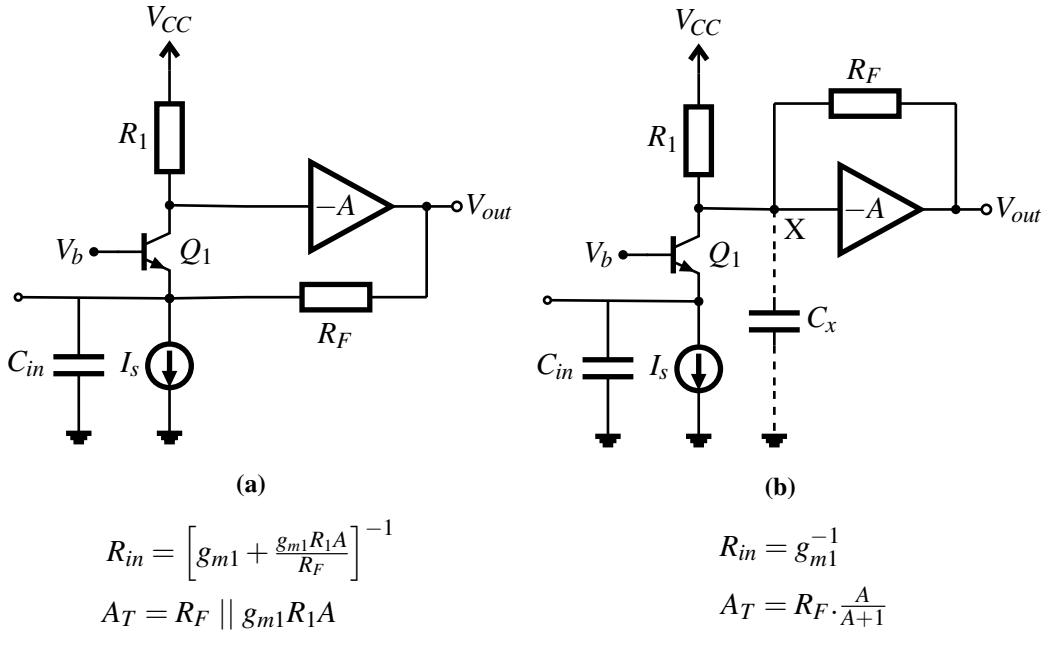

| 5.1  | Basic shunt-feedback amplifier configuration . . . . .                                                                                                                                                                                      | 161 |

| 5.2  | The feedforward CB transimpedance amplifier . . . . .                                                                                                                                                                                       | 165 |

| 5.3  | (a) Shunt feedback TIA with CB input stage (b) CB TIA with current feedback . . . . .                                                                                                                                                       | 167 |

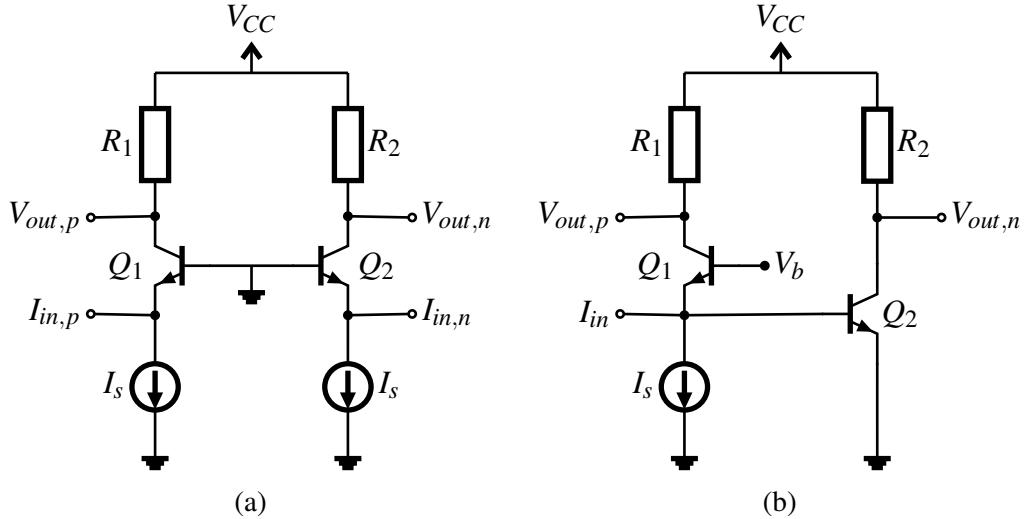

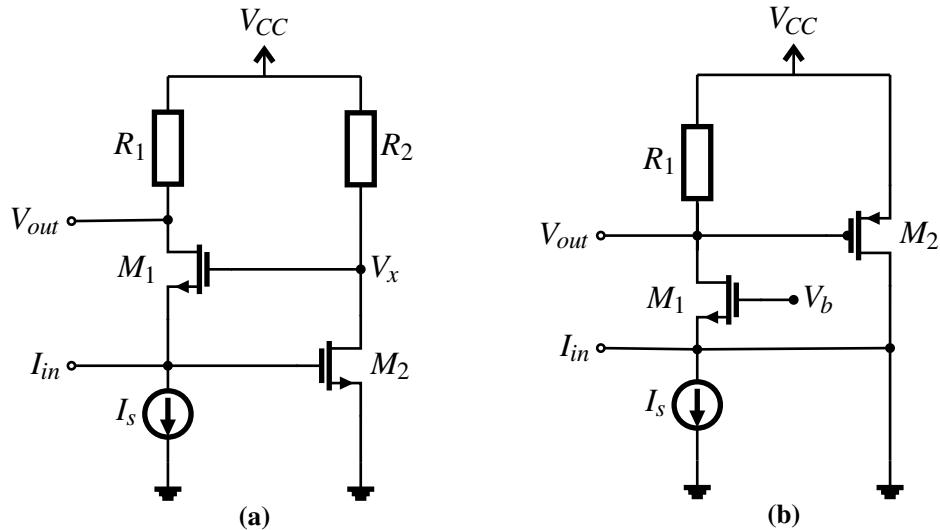

| 5.4  | (a) Feedforward CB TIA with differential input and differential output (b) Feedforward CB TIA with single-ended input and differential output . . . . .                                                                                     | 170 |

|      |                                                                                                                                                                                                                                                                          |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

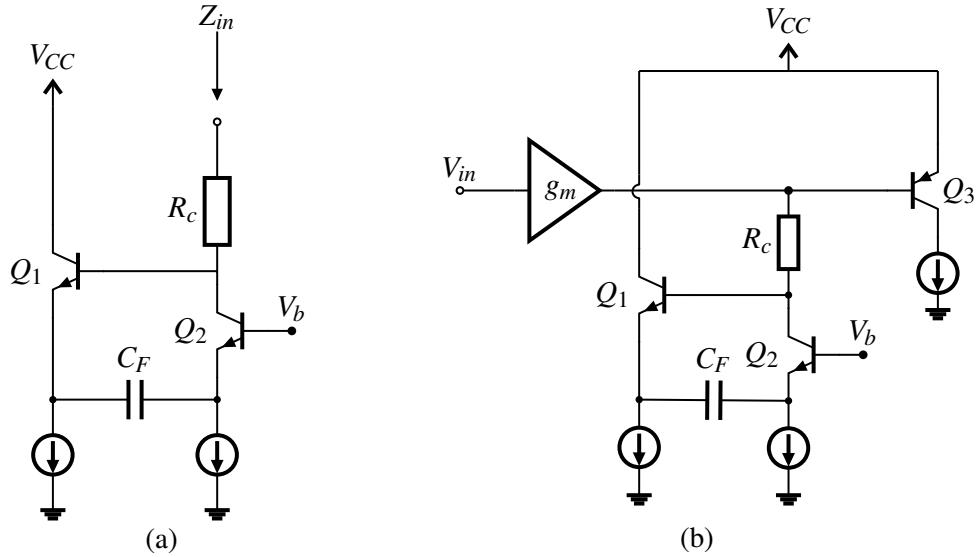

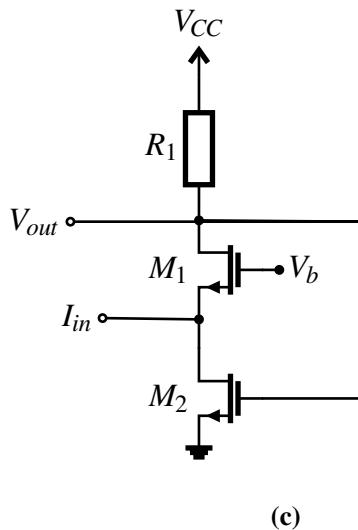

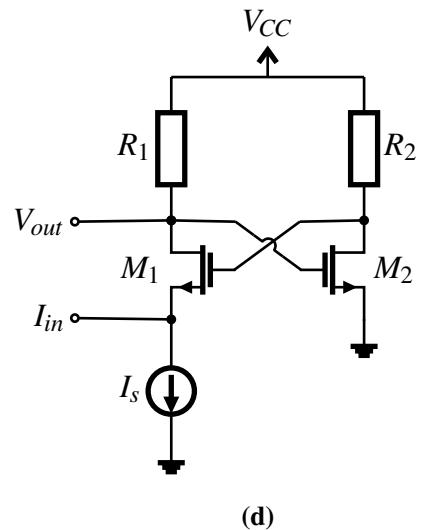

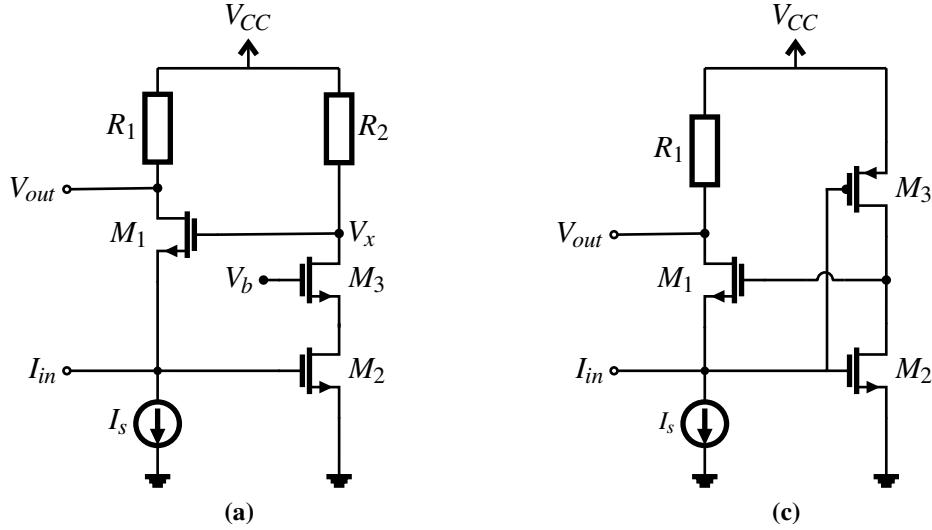

| 5.5  | a) RGC TIA (b) CG TIA with active feedback (c) CG TIA with direct feedback (d) cross-coupled CG TIA . . . . .                                                                                                                                                            | 172 |

| 5.6  | Block diagram of the RGC TIA . . . . .                                                                                                                                                                                                                                   | 177 |

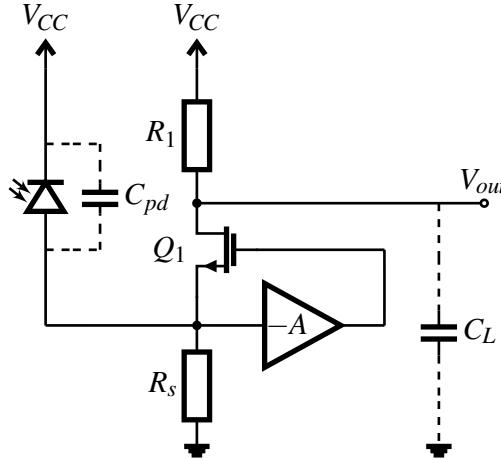

| 5.7  | (a) RGC TIA with auxiliary cascode feedback stage (b) RGC with inverter auxiliary amplifier stage (c) RGC with cross coupled pair feedback stage . . . . .                                                                                                               | 181 |

| 6.1  | The conventional RGC TIA with photodiode input . . . . .                                                                                                                                                                                                                 | 188 |

| 6.2  | Simplified equivalent model of the RGC TIA with photodiode input                                                                                                                                                                                                         | 191 |

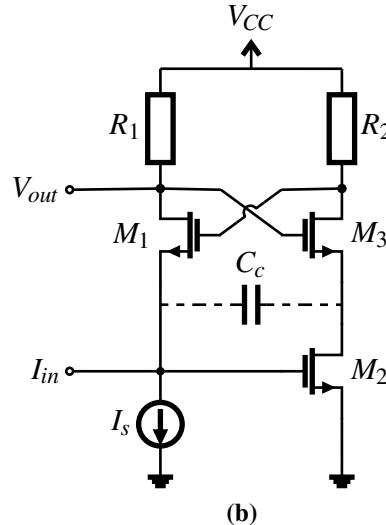

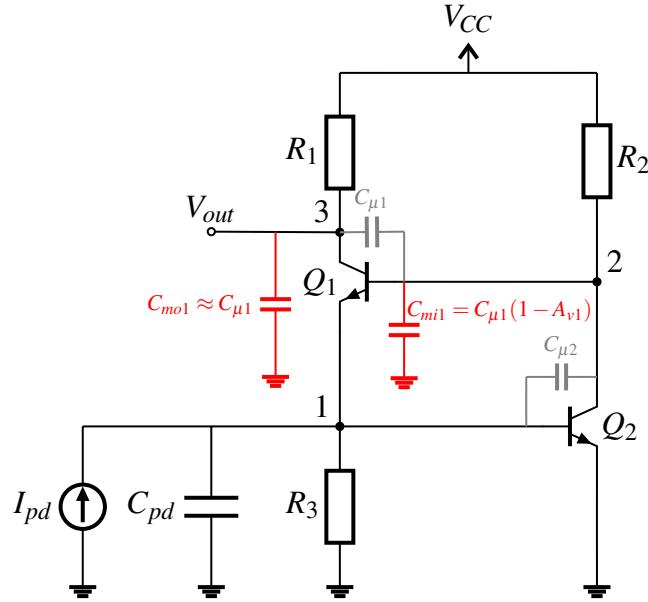

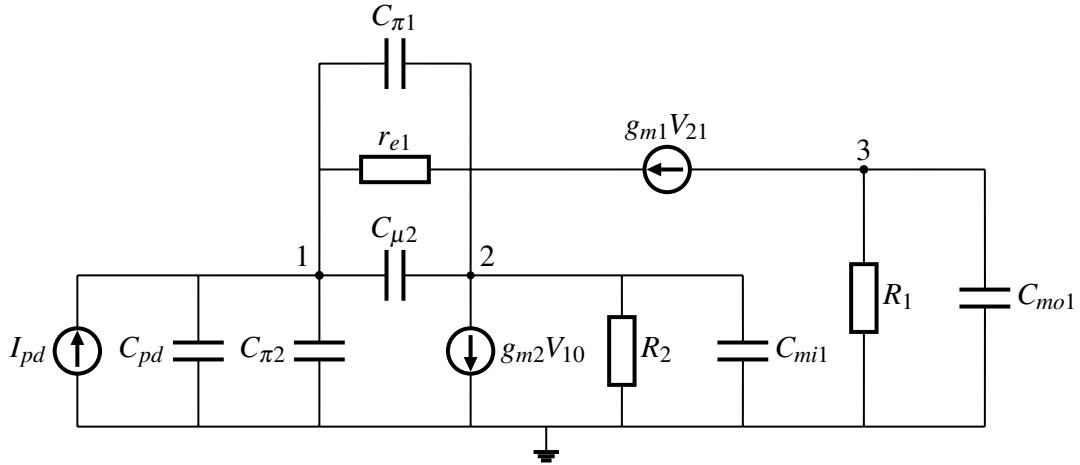

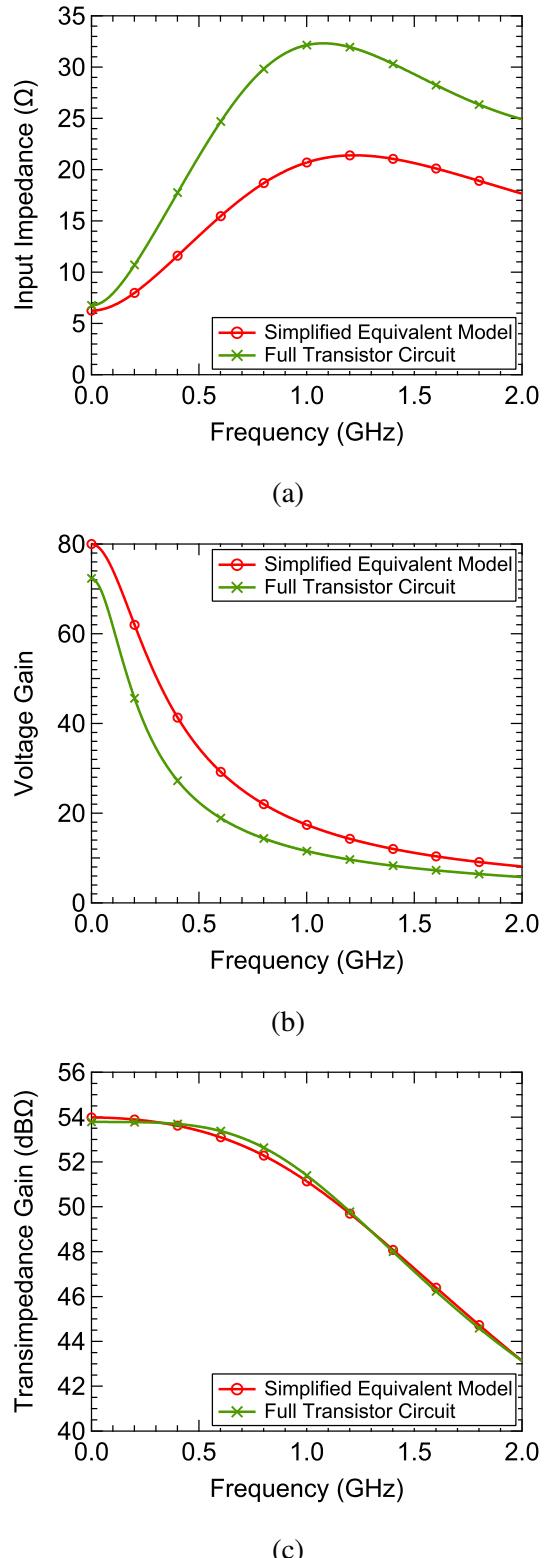

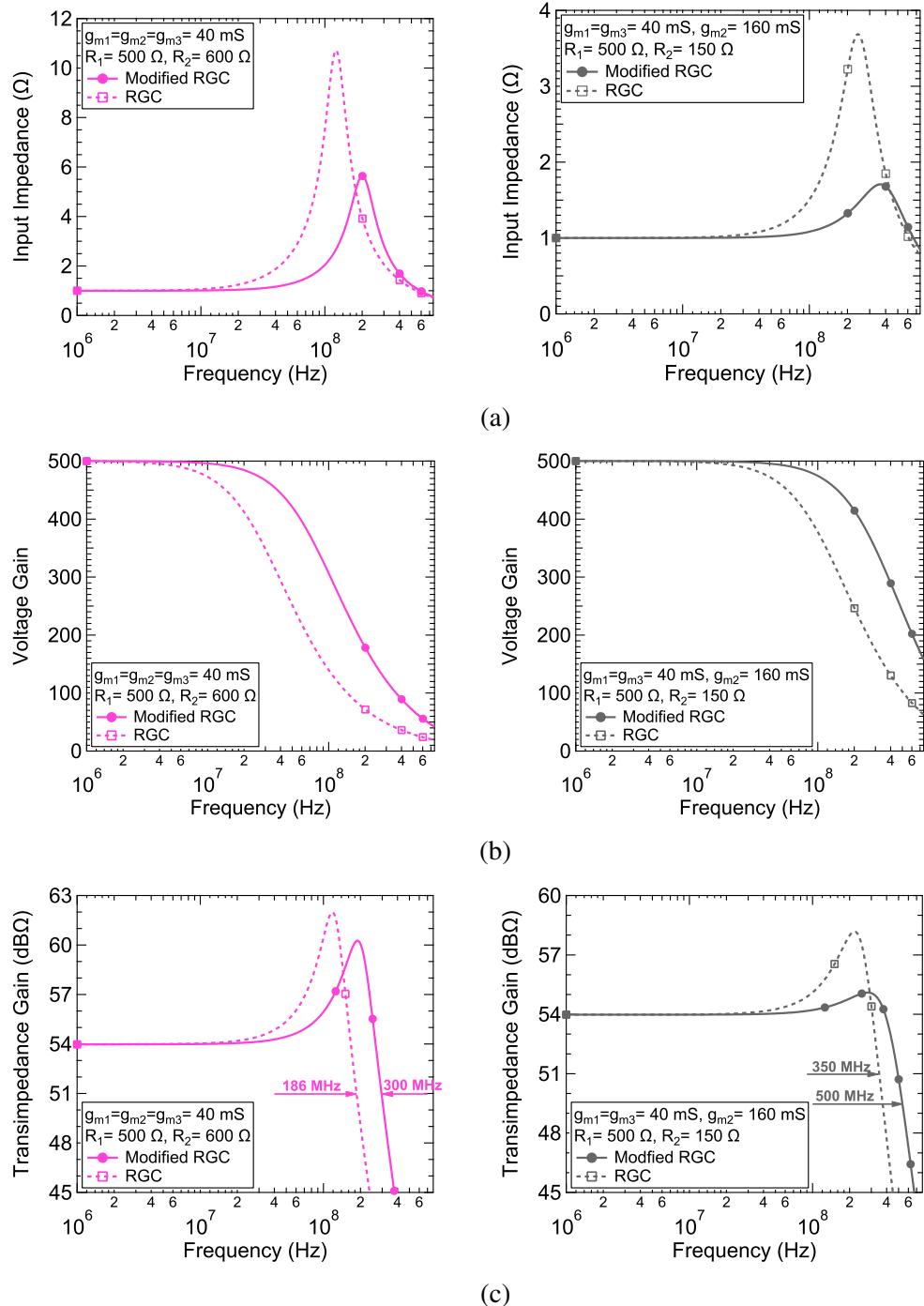

| 6.3  | Simulations of the RGC simplified equivalent model vs. full transistor model simulation (a) Input impedance (b) Voltage gain (c) Transimpedance gain . . . . .                                                                                                           | 194 |

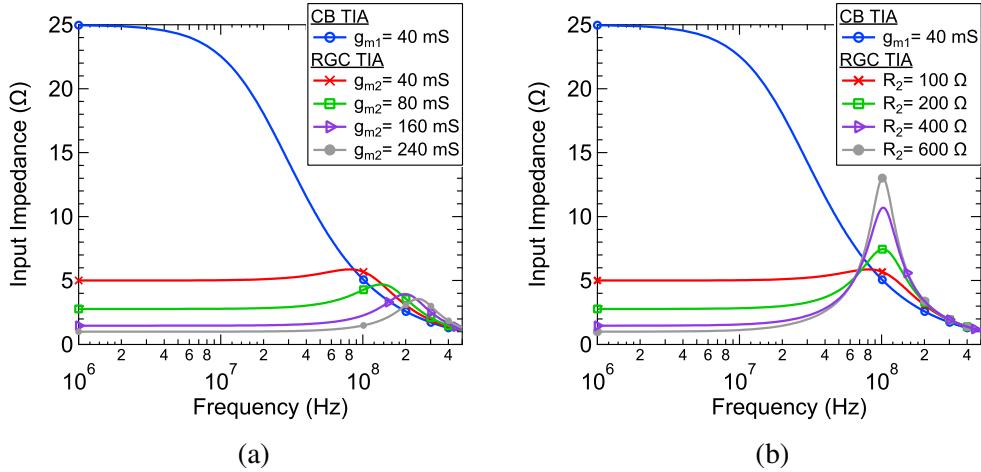

| 6.4  | Simulations of the RGC input impedance versus the CB at $g_{m1} = 40 \text{ mS}$ (a) variable $g_{m2}$ at constant $R_2 = 100 \Omega$ (b) variable $R_2$ at constant $g_{m2} = 40 \text{ mS}$ . . . . .                                                                  | 197 |

| 6.5  | Simulations of the effect of varying $g_{m2}$ and $R_2$ on the RGC at $R_1 = 500 \Omega$ and $g_{m1} = 40 \text{ mS}$ (a) Input impedance (b) Voltage gain (c) Transimpedance gain . . . . .                                                                             | 199 |

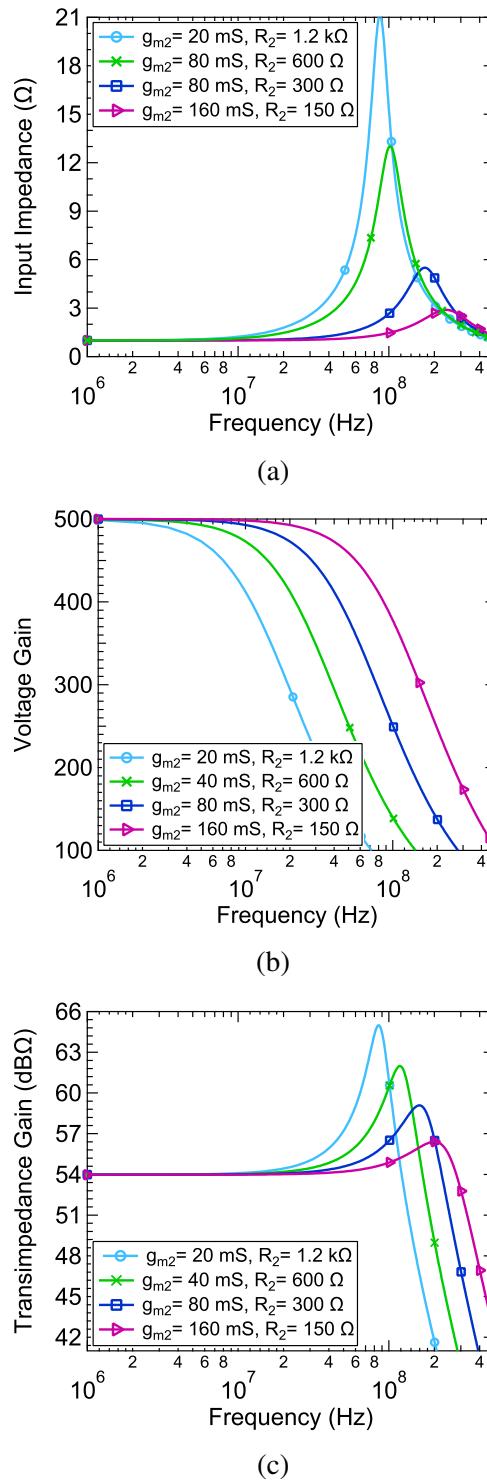

| 6.6  | The effect of varying $R_1$ for different $C_{\mu 1}$ on the RGC at $g_{m1} = 40 \text{ mS}$ , $g_{m2} = 240 \text{ mS}$ and $R_2 = 100 \Omega$ (a) Bandwidth (b) $Q$ -factor (c) Phase margin (d) Transimpedance gain . . . . .                                         | 201 |

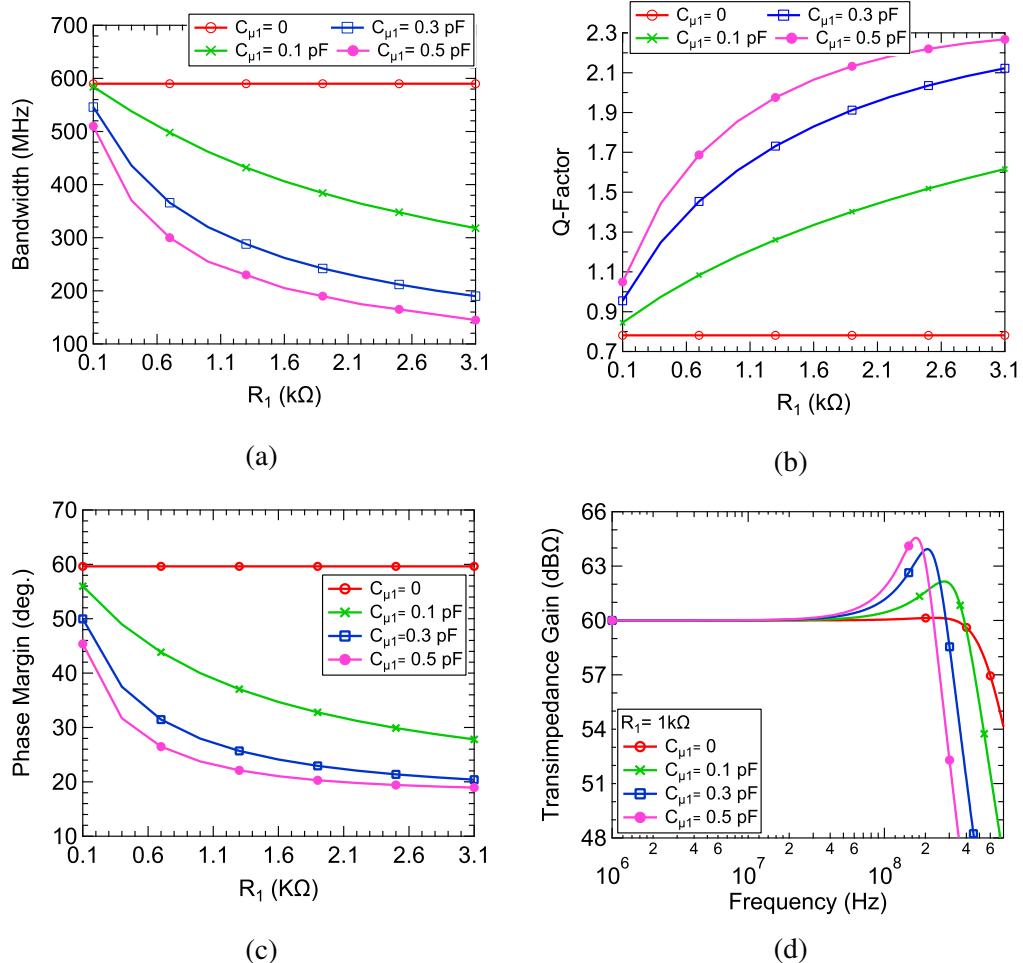

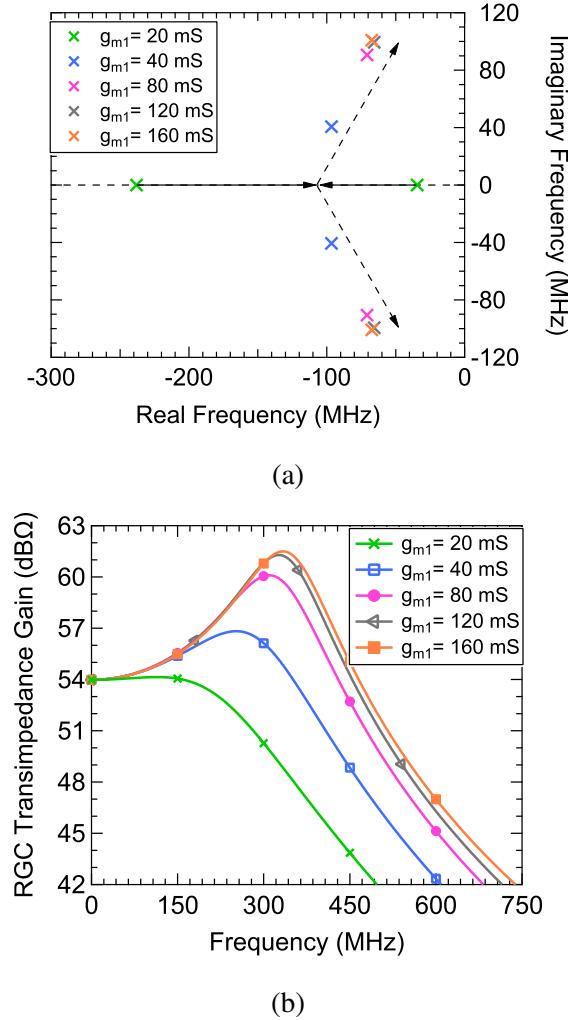

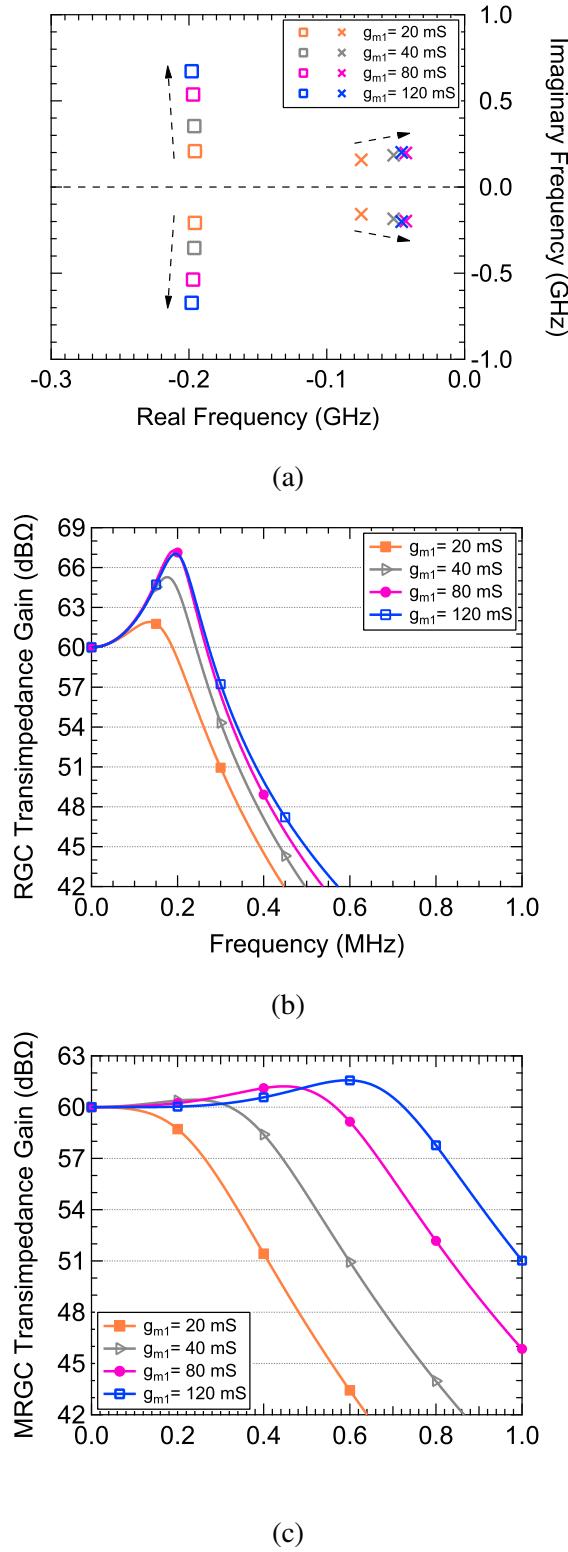

| 6.7  | Simulations of the effect of increasing $R_1$ on the RGC TIA at $g_{m1} = 40 \text{ mS}$ , $g_{m2} = 240 \text{ mS}$ and $R_2 = 100 \Omega$ (a) Pole action including $p_{(1,2)}$ and $p_3$ (b) Pole action including only $p_{(1,2)}$ (c) Transimpedance gain . . . . . | 204 |

| 6.8  | Simulations of the effect of increasing $g_{m1}$ on the RGC TIA at $R_1 = 500 \Omega$ , $g_{m2} = 240 \text{ mS}$ and $R_2 = 100 \Omega$ for $C_{\mu 1} = 0.3 \text{ pF}$ (a) Pole action including $p_{(1,2)}$ only (b) Transimpedance gain . . . . .                   | 205 |

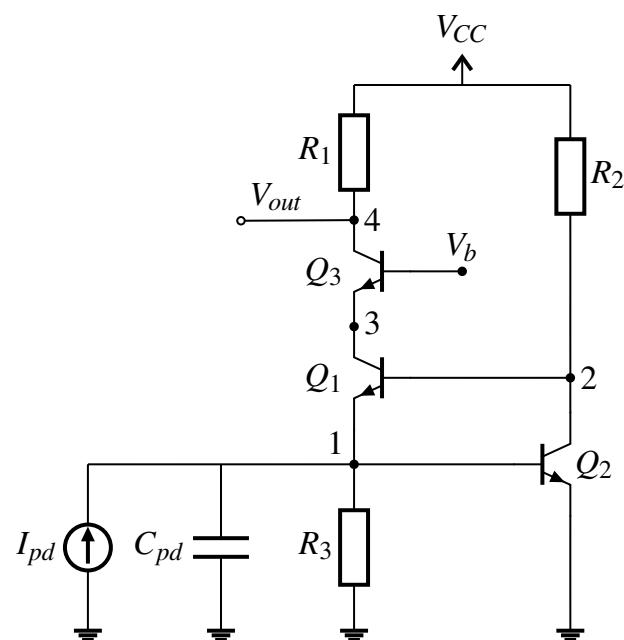

| 6.9  | The modified RGC TIA circuit with photodiode input . . . . .                                                                                                                                                                                                             | 208 |

| 6.10 | Simplified equivalent model of the modified RGC with photodiode input . . . . .                                                                                                                                                                                          | 209 |

|                                                                                                                                                                                                                                                                               |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

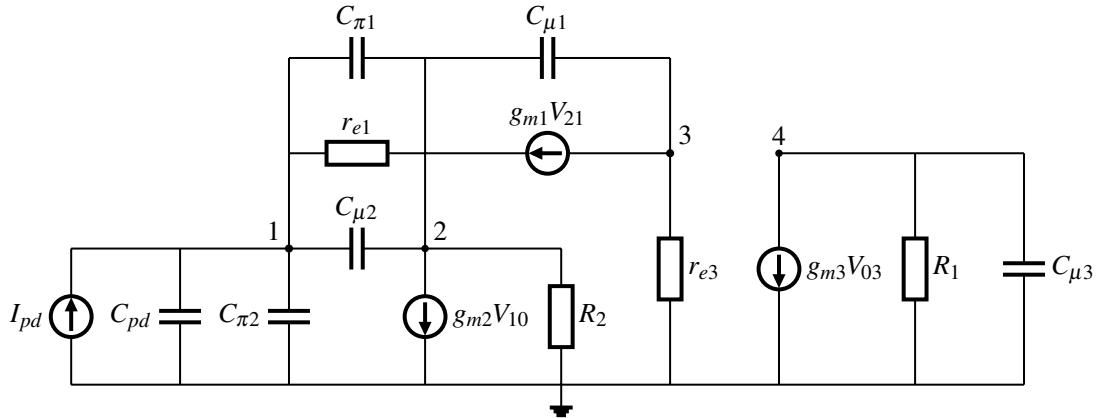

| 6.11 Simulations of the modified RGC simplified equivalent circuit model vs. full transistor circuit (a) Input impedance (b) Voltage gain (c) Transimpedance gain . . . . .                                                                                                   | 212 |

| 6.12 The effect of different values of $g_{m2}$ and $R_2$ on the RGC and modified RGC TIAs for Case 1 (left side) and Case 2 (right side) at $g_{m1} = 40$ mS and $R_1 = 500 \Omega$ (a) Input impedance (b) Voltage gain (c) Transimpedance gain . . . . .                   | 215 |

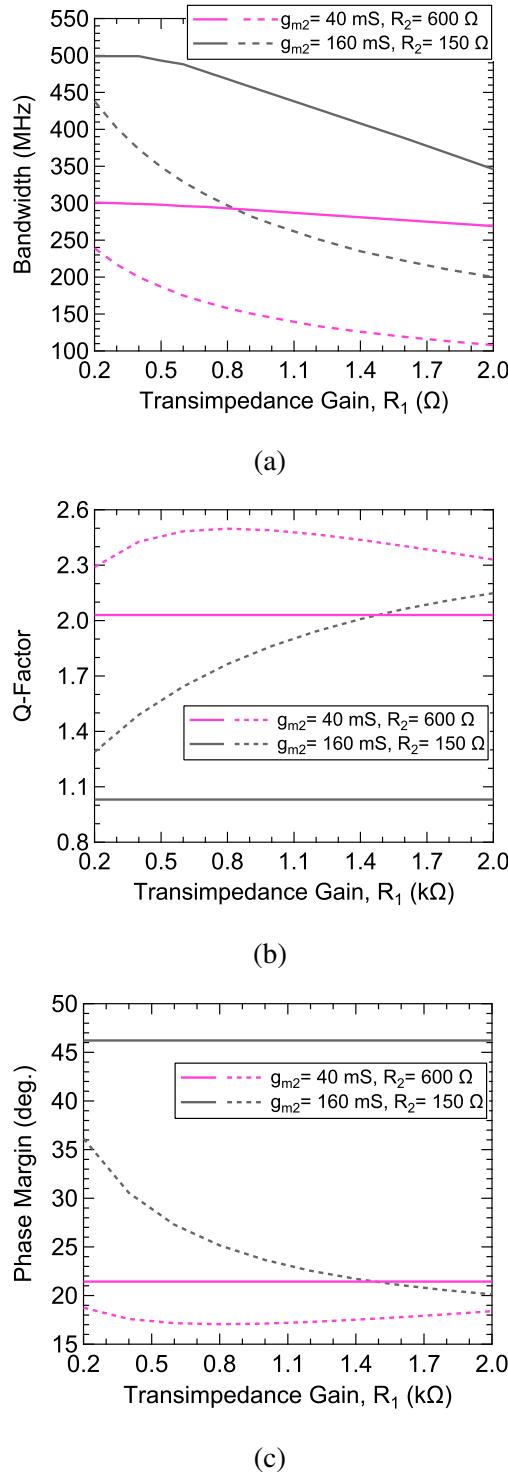

| 6.13 Performance comparison of RGC (dashed) versus the modified RGC (solid) as the transimpedance gain ( $R_1$ ) increases at $A_{v2} = 24$ for different $g_{m2}R_2$ combinations (a) Bandwidth (b) $Q$ -factor (c) Phase margin . . . . .                                   | 218 |

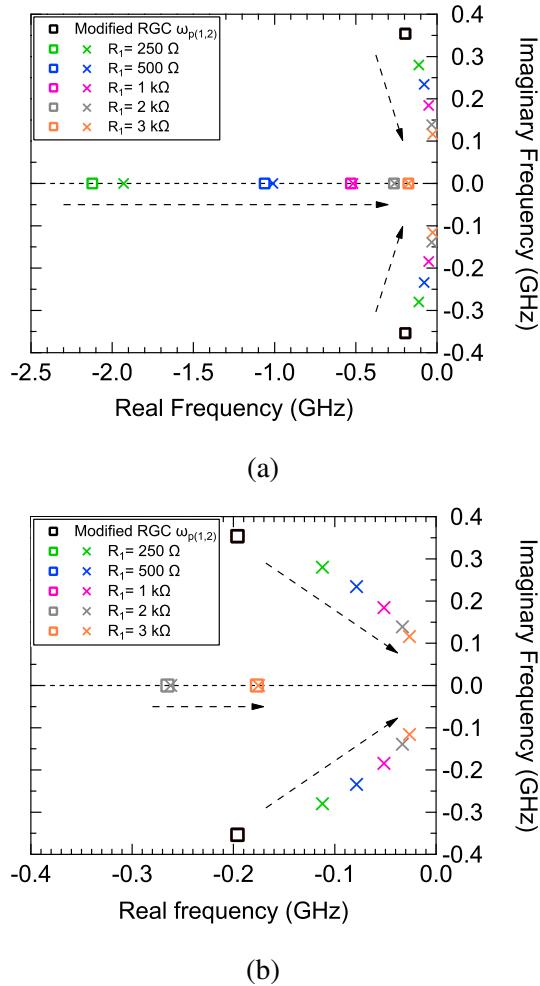

| 6.14 Simulations of the RGC (cross symbol) and modified RGC (square symbol) pole action for increasing $R_1$ at $g_{m1} = 40$ mS, $g_{m2} = 160$ mS and $R_2 = 150 \Omega$ (a) Including $p_{(1,2)}$ and $p_3$ (b) Including $p_{(1,2)}$ and significant $p_3$ . . . . .      | 221 |

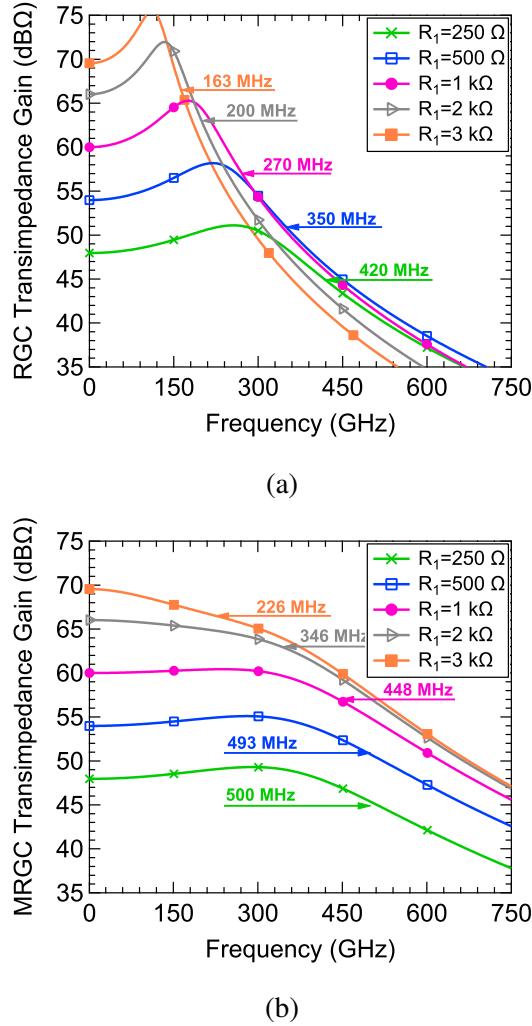

| 6.15 Simulations the transimpedance gain frequency responses for increasing $R_1$ at $g_{m1} = 40$ mS, $g_{m2} = 160$ mS and $R_2 = 150 \Omega$ (a) RGC (b) Modified RGC . . . . .                                                                                            | 223 |

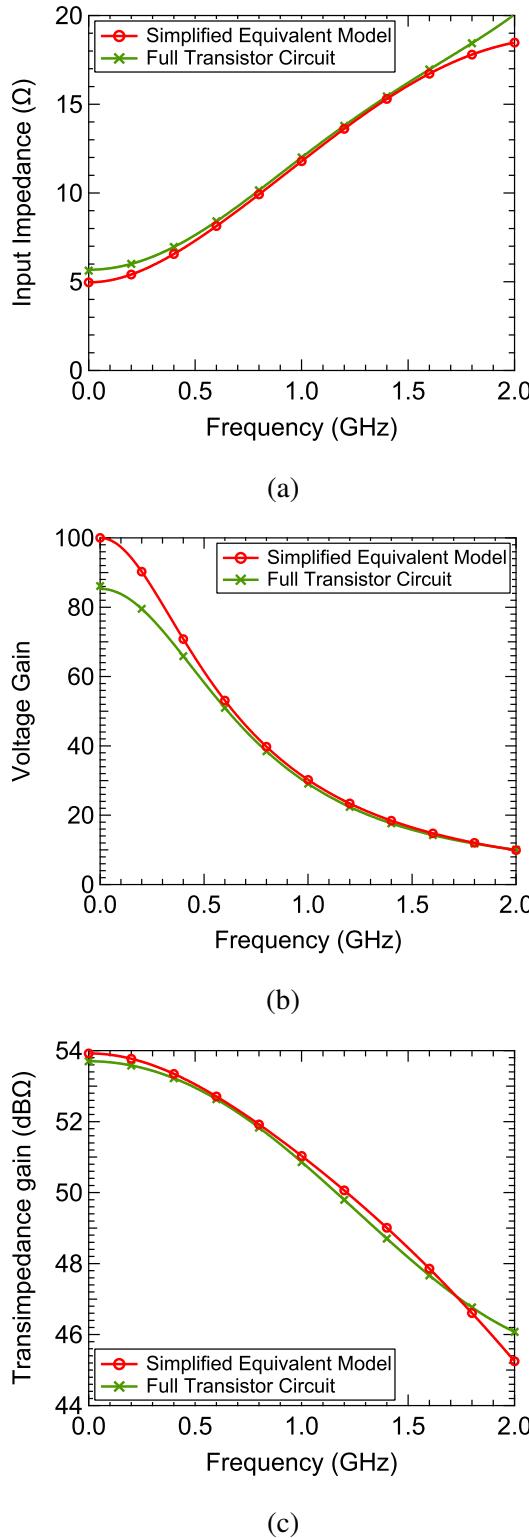

| 6.16 The effect of increasing $g_{m1}$ on the modified RGC versus the conventional RGC TIA at $R_1 = 1 \text{ k}\Omega$ , $g_{m2} = 160$ mS and $R_2 = 150 \Omega$ (a) pole action of the two TIAs (b) RGC Transimpedance gain (b) Modified RGC Transimpedance gain . . . . . | 225 |

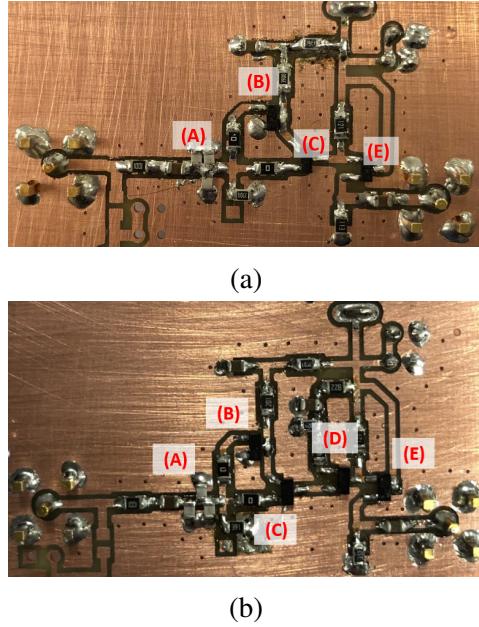

| 6.17 Fabricated PCBs (a) RGC TIA (b) Modified RGC TIA, where (A) Photodiode capacitance (B) CE ( $Q_2$ ) stage (C) CB ( $Q_1$ ) stage (D) CB ( $Q_3$ ) stage (E) Additional CC stage . . . . .                                                                                | 226 |

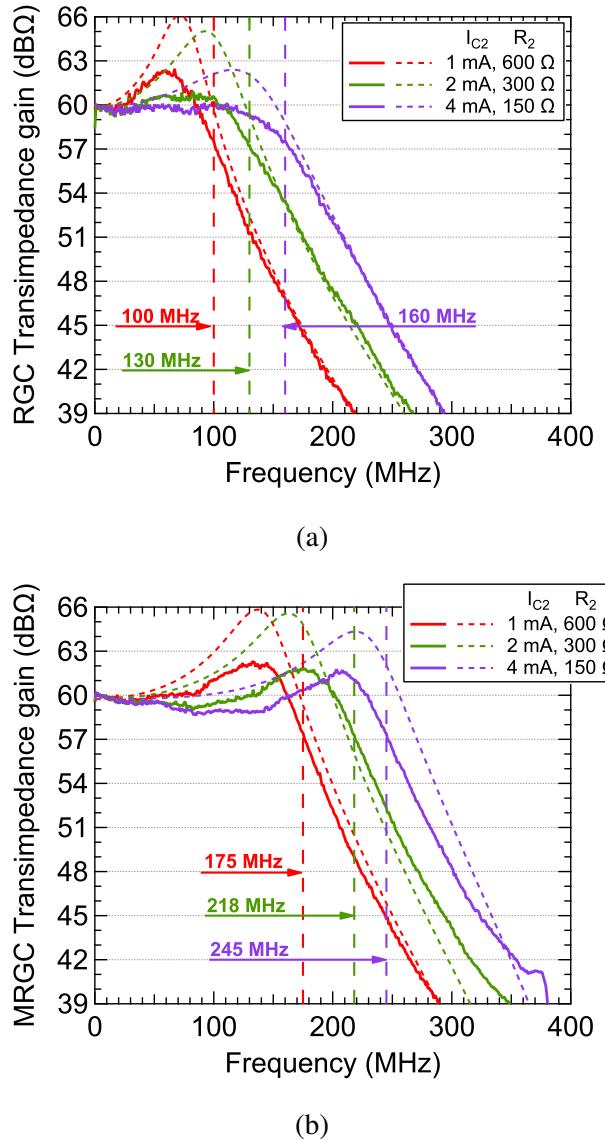

| 6.18 Measured (solid) and simulated (dashed) frequency responses for varying $I_{C2}$ and $R_2$ at $C_{pd} = 300 \text{ pF}$ , $R_1 = 1 \text{ k}\Omega$ and $I_{C1} = 1 \text{ mA}$ (a) RGC TIA (b) Modified RGC TIA . . . . .                                               | 228 |

|      |                                                                                                                                                                                                                                                                                               |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

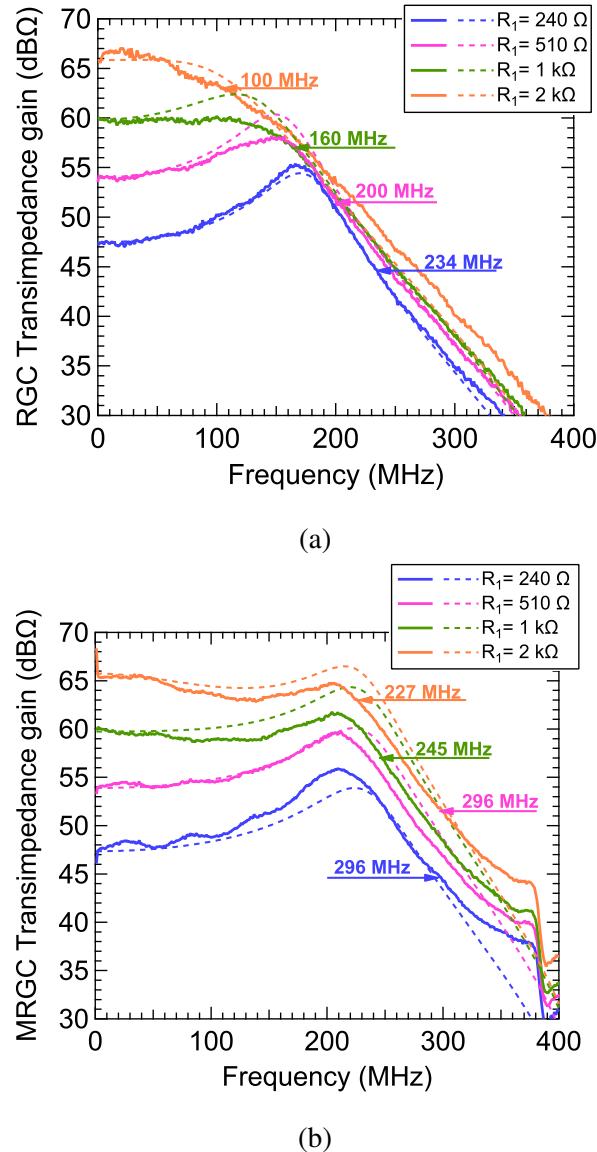

| 6.19 | Measured (solid) and simulated (dashed) frequency responses for varying transimpedance gain at $C_{pd} = 300 \text{ pF}$ , $I_{C1} = 1 \text{ mA}$ , $I_{C2} = 4 \text{ mA}$ and $R_2 = 150 \Omega$ (a) RGC TIA (b) Modified RGC TIA . . . . .                                                | 230 |

| 6.20 | Measured (solid) and simulated (dashed) frequency responses for varying $C_{pd}$ at $R_1 = 1 \text{ k}\Omega$ , $R_2 = 150 \Omega$ , $I_{C1} = 1 \text{ mA}$ and $I_{C2} = 4 \text{ mA}$ (a) RGC TIA (b) Modified RGC TIA . . . . .                                                           | 232 |

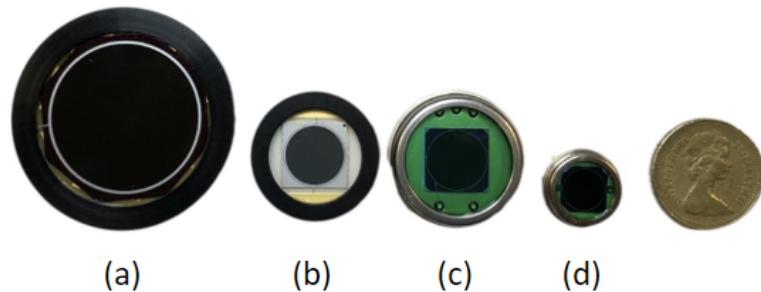

| 7.1  | Photodiodes under-test (a) OSI Optoelectronics PIN25-D (600 $\text{mm}^2$ ) (b) OSI Optoelectronics PIN10-D (100 $\text{mm}^2$ ) (c) Centronic OSD100-E (100 $\text{mm}^2$ ) (d) Centronic OSD50-E (50 $\text{mm}^2$ ) . . . . .                                                              | 237 |

| 7.2  | Experimental set-up used to test the large-area photodiode with the RGC TIA . . . . .                                                                                                                                                                                                         | 238 |

| 7.3  | Measured $S_{21}$ responses of the OSI optoelectronics photodiode when connected to a $50 \Omega$ impedance versus the RGC TIA (a) 100 $\text{mm}^2$ (b) 600 $\text{mm}^2$ . . . . .                                                                                                          | 240 |

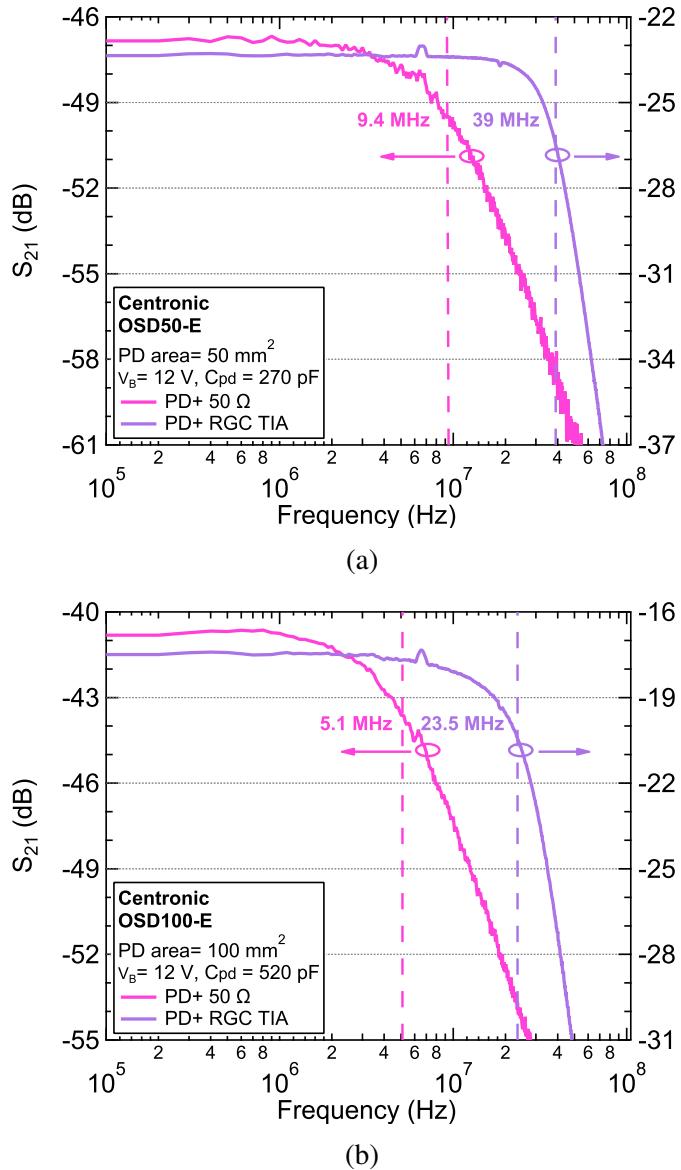

| 7.4  | Measured $S_{21}$ responses of the Centronic photodiode when connected to a $50 \Omega$ impedance versus the RGC TIA (a) 50 $\text{mm}^2$ (b) 100 $\text{mm}^2$ . . . . .                                                                                                                     | 242 |

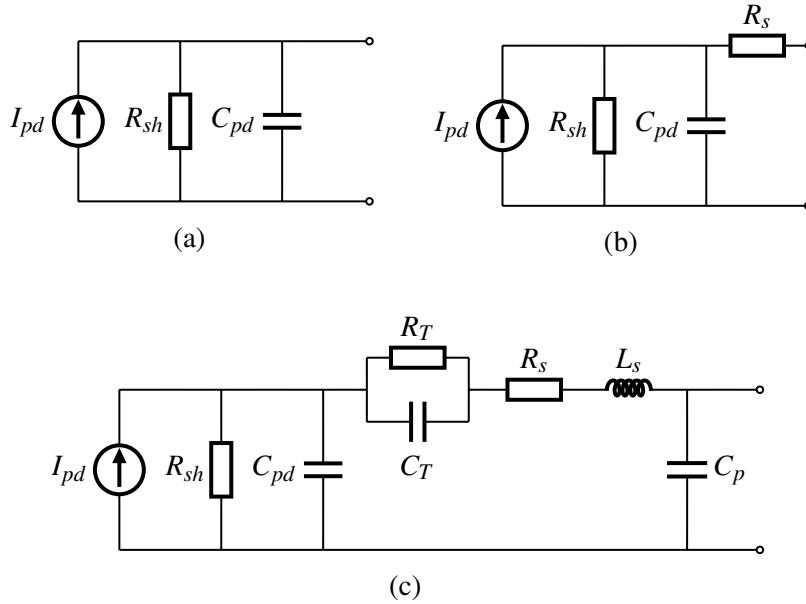

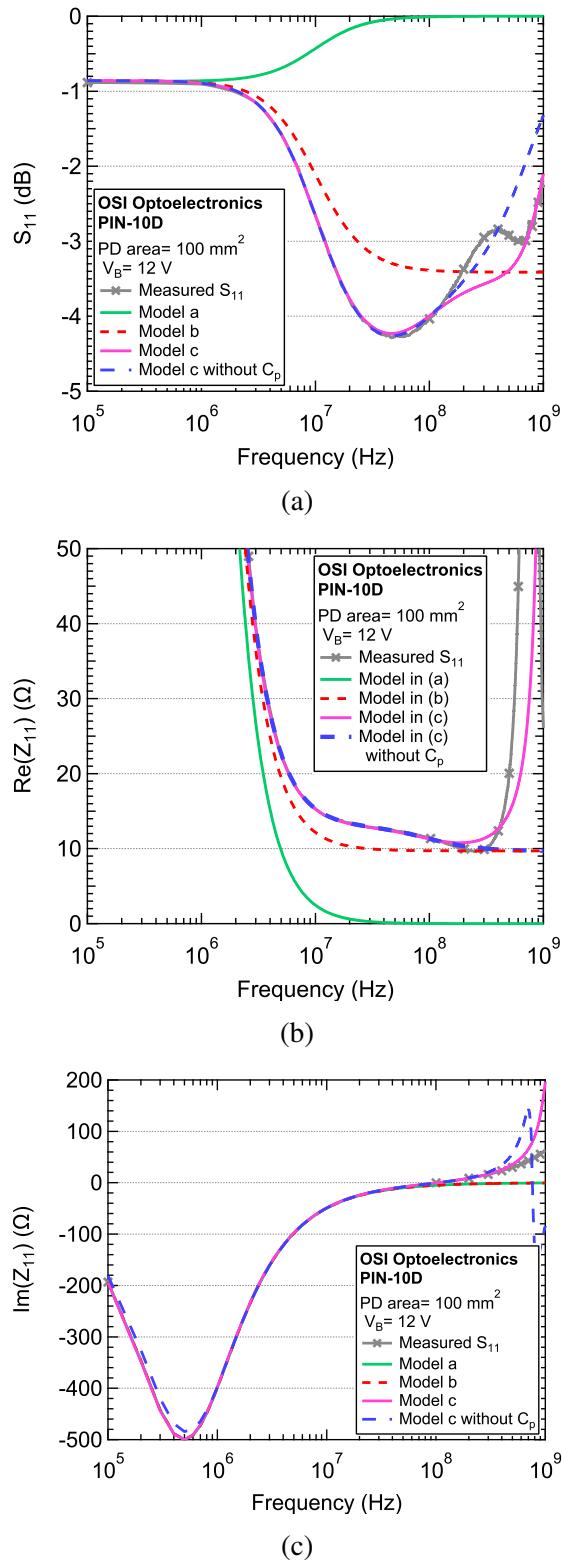

| 7.5  | Photodiode small signal equivalent circuit model (a) Simple RC circuit model as used in [21] (b) Photodiode equivalent circuit model in [114] (c) Extended photodiode equivalent circuit model in [175] .                                                                                     | 247 |

| 7.6  | Simulations of the photodiode equivalent models in Figure 7.5 versus photodiode measurements (a) $S_{11}$ (b) $\text{Re}(Z_{11})$ (c) $\text{Im}(Z_{11})$ . . . . .                                                                                                                           | 249 |

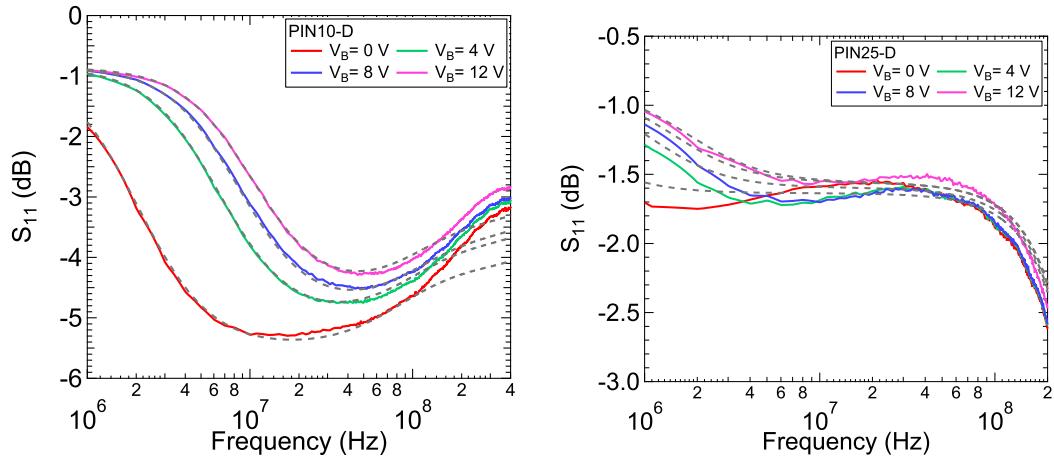

| 7.7  | Measured $S_{11}$ (solid) of the OSI Optoelectronics PIN10-D (left-side) and PIN25-D (right-side) versus the equivalent photodiode circuit model (dashed) at different $V_B$ . . . . .                                                                                                        | 253 |

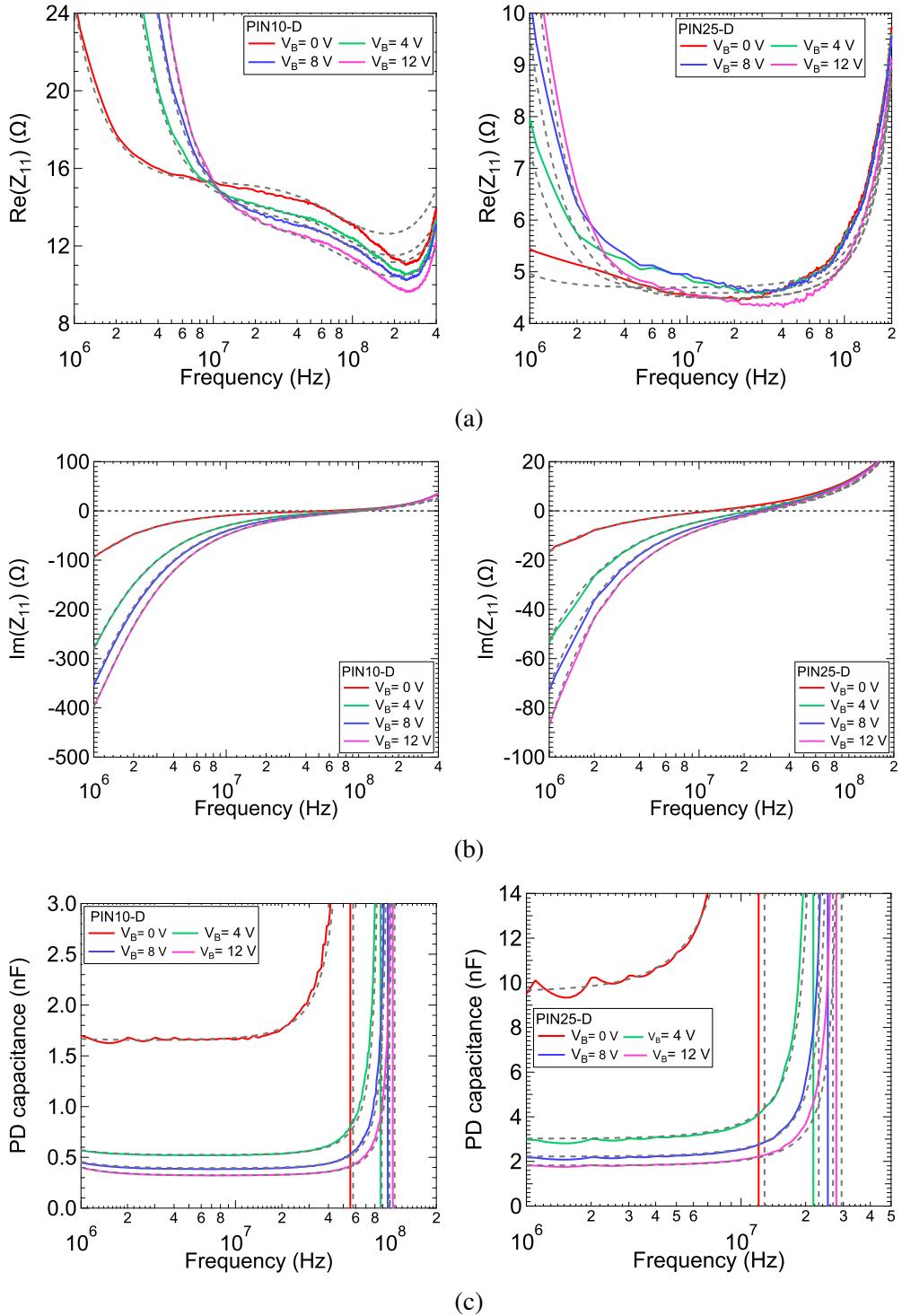

| 7.8  | Measurements (solid lines) and fitted photodiode equivalent circuit model (dashed line) of the PIN10-D (100 $\text{mm}^2$ ) on the left-side and the PIN25-D (600 $\text{mm}^2$ ) on the right-side at different $V_B$ (a) $\text{Re}(Z_{11})$ (b) $\text{Im}(Z_{11})$ (c) $C_{pd}$ . . . . . | 255 |

|      |                                                                                                                                                                                                                                                           |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

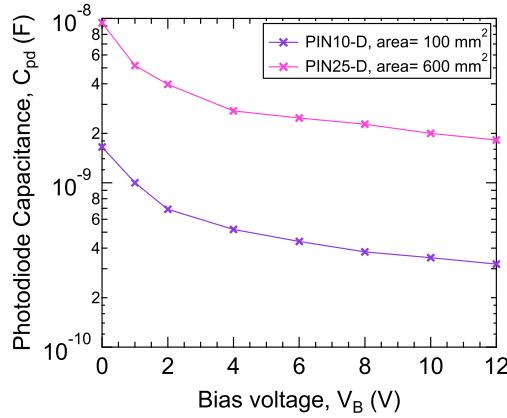

| 7.9  | Measured $C_{pd}$ versus $V_B$ for the PIN10-D (100 mm <sup>2</sup> ) and PIN25-D (600 mm <sup>2</sup> ) . . . . .                                                                                                                                        | 256 |

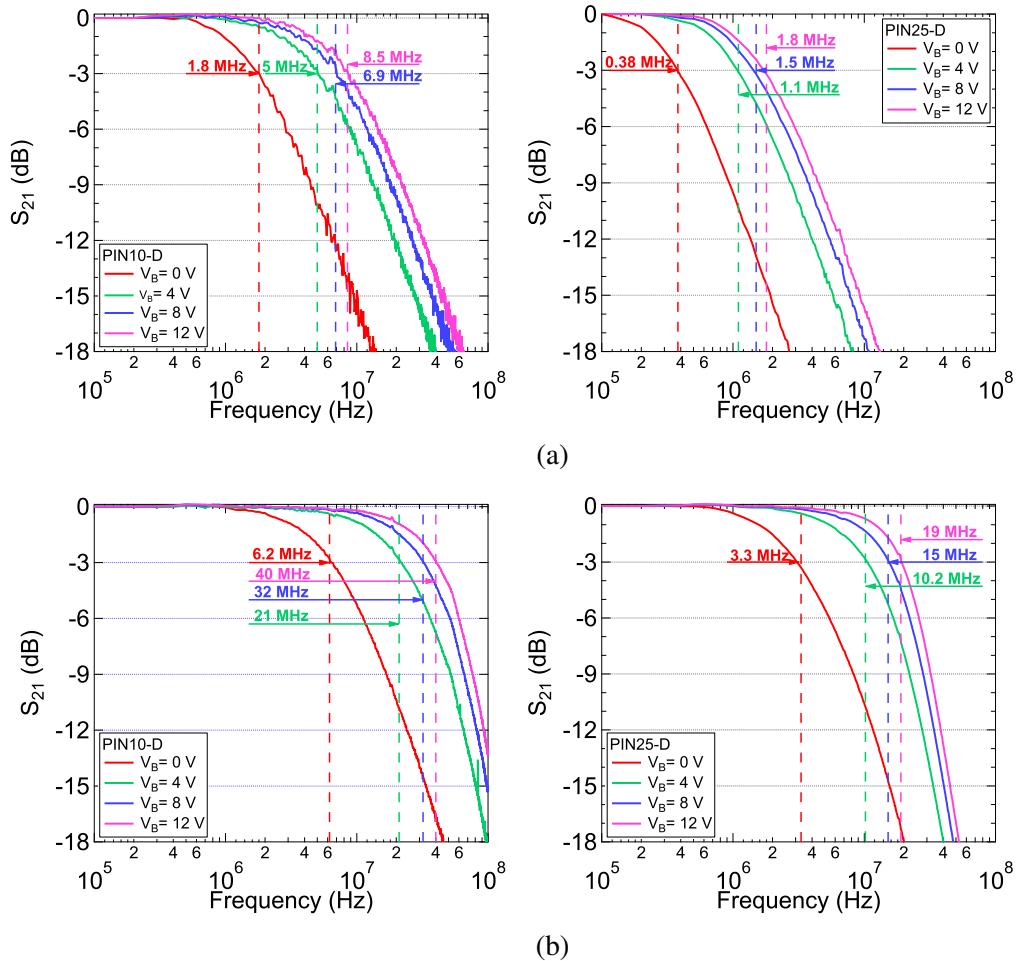

| 7.10 | Measured $S_{21}$ of the PIN10-D (100 mm <sup>2</sup> ) on the left-side and PIN25-D (600 mm <sup>2</sup> ) on the right-side at different $V_B$ (a) 50 Ω (b) RGC TIA . . . . .                                                                           | 257 |

| 7.11 | Measured $S_{11}$ (solid) of the OSD50-E (50 mm <sup>2</sup> ) on the left-side and OSD10-E (100 mm <sup>2</sup> ) on the right-side versus the equivalent model (dashed) at different $V_B$ . . . . .                                                    | 260 |

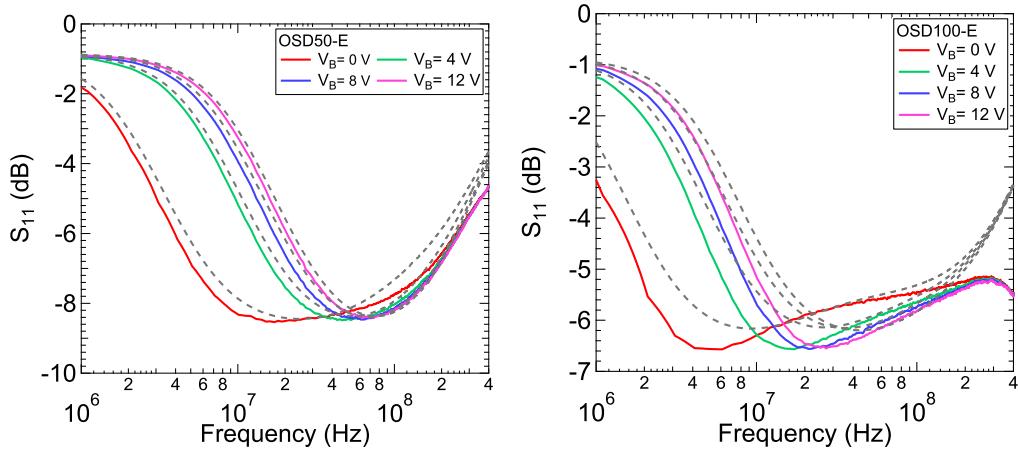

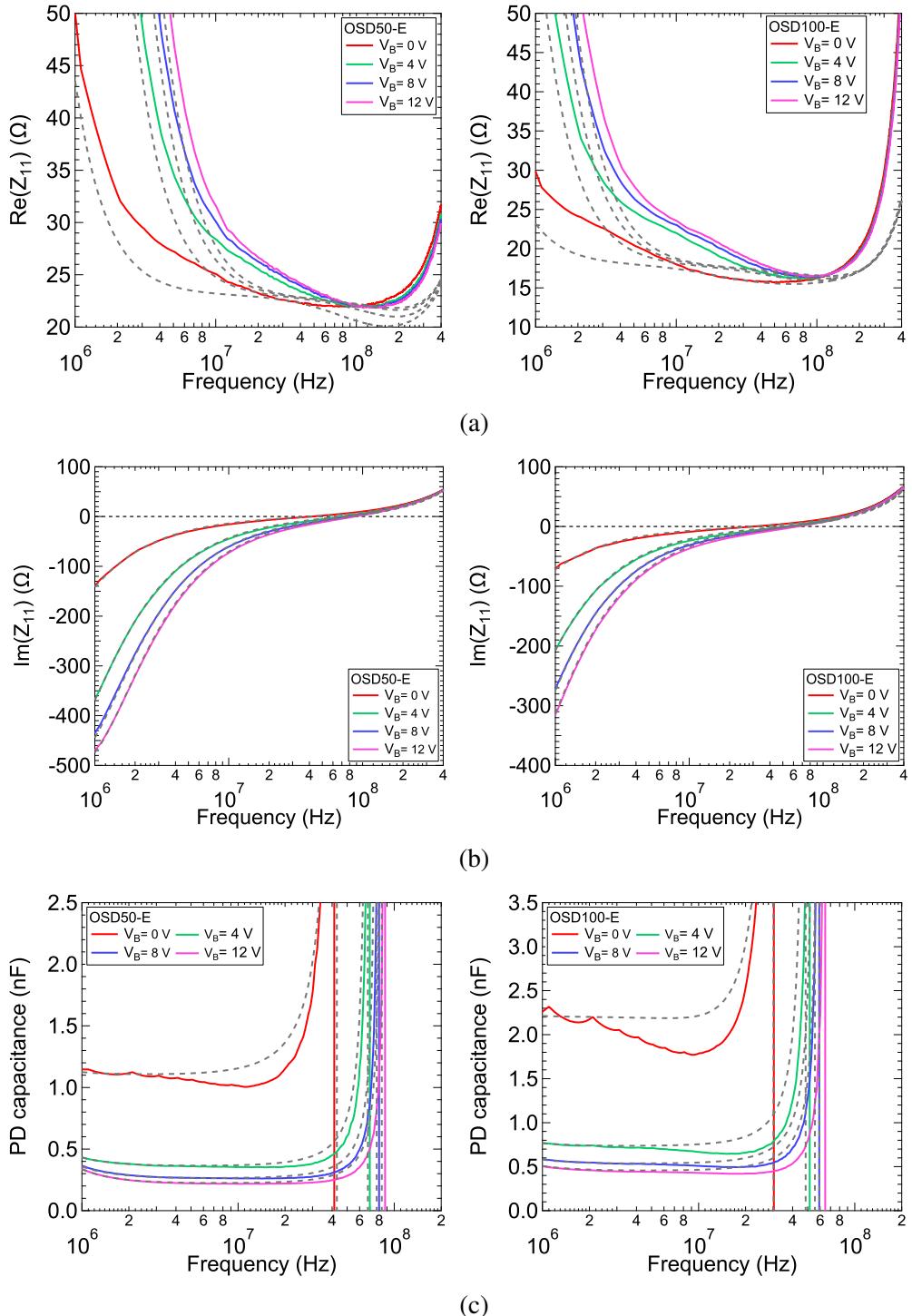

| 7.12 | Measurements (solid lines) and fitted model (dashed line) of the OSD50-E and OSD100-E at different $V_B$ (a) $\text{Re}(Z_{11})$ (b) $\text{Im}(Z_{11})$ (c) $C_{pd}$ . . . . .                                                                           | 261 |

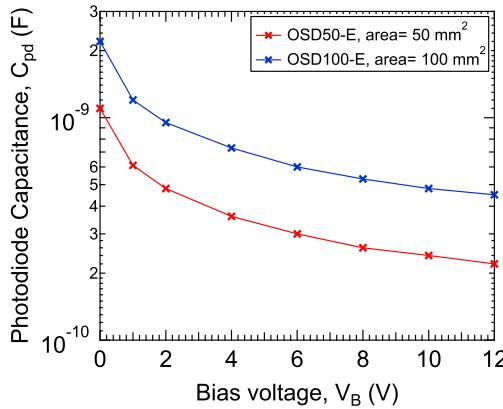

| 7.13 | Measured $C_{pd}$ versus $V_B$ for the OSD50-E (50 mm <sup>2</sup> ) and OSD100-E (100 mm <sup>2</sup> ) . . . . .                                                                                                                                        | 262 |

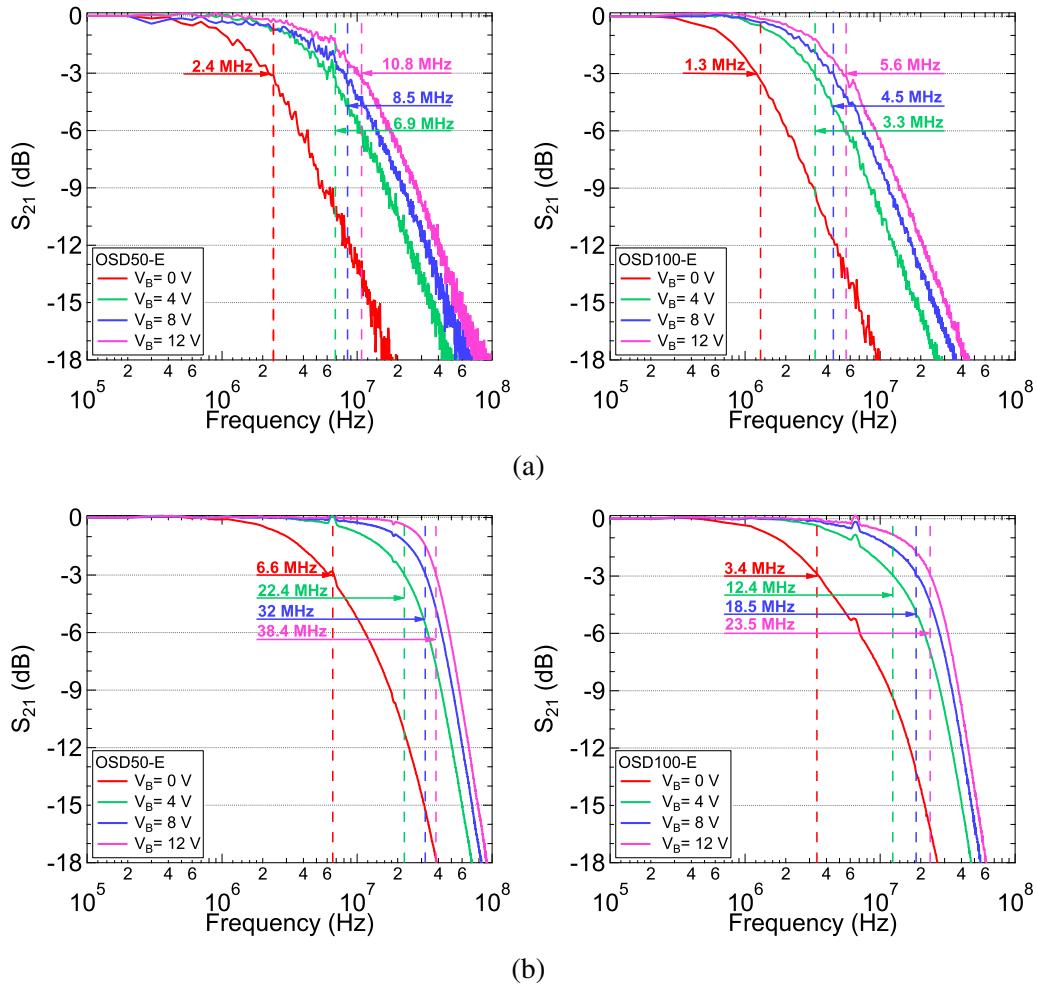

| 7.14 | Measured $S_{21}$ of the OSD50-E (50 mm <sup>2</sup> ) on the left-side and OSD100-E (100 mm <sup>2</sup> ) on the right-side at different $V_B$ (a) 50 Ω (b) RGC TIA . . . . .                                                                           | 263 |

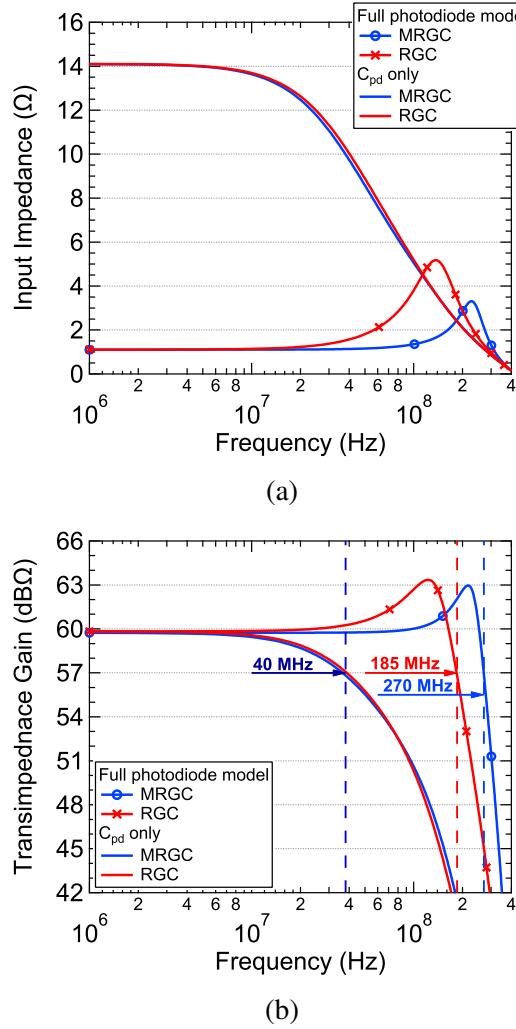

| 7.15 | Simulations of the RGC and modified RGC TIAs with the full and simplified photodiode equivalent circuit model in Figures 7.5a and 7.5c based on parameter extraction of the PIN10-D at $V_B = 12$ V (a) Input impedance (b) Transimpedance gain . . . . . | 266 |

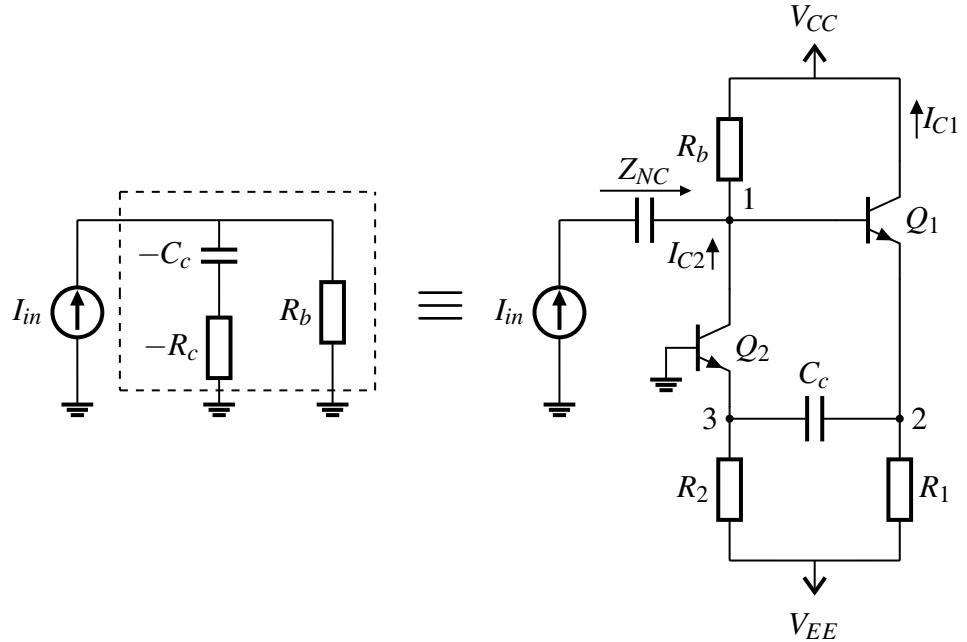

| 7.16 | Linvill OCS NIC circuit generating negative floating resistance and its passive equivalent circuit model . . . . .                                                                                                                                        | 269 |

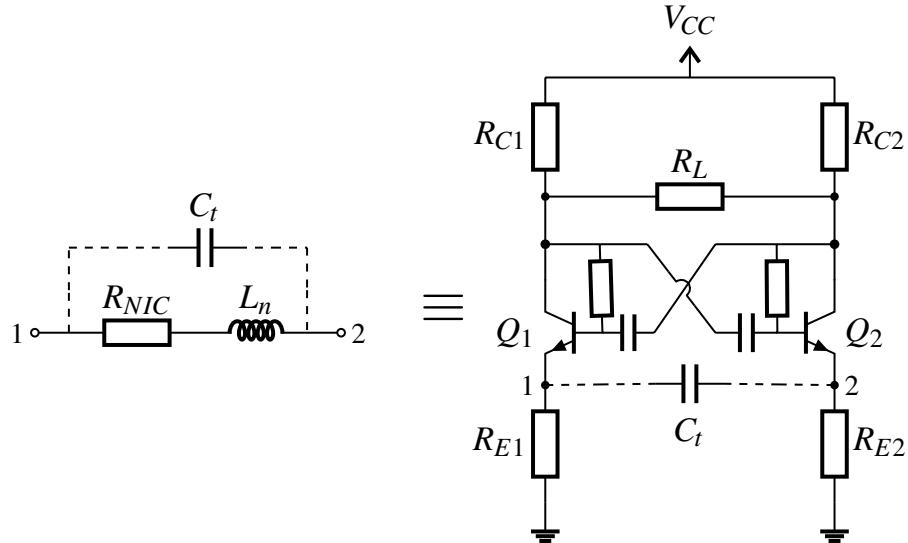

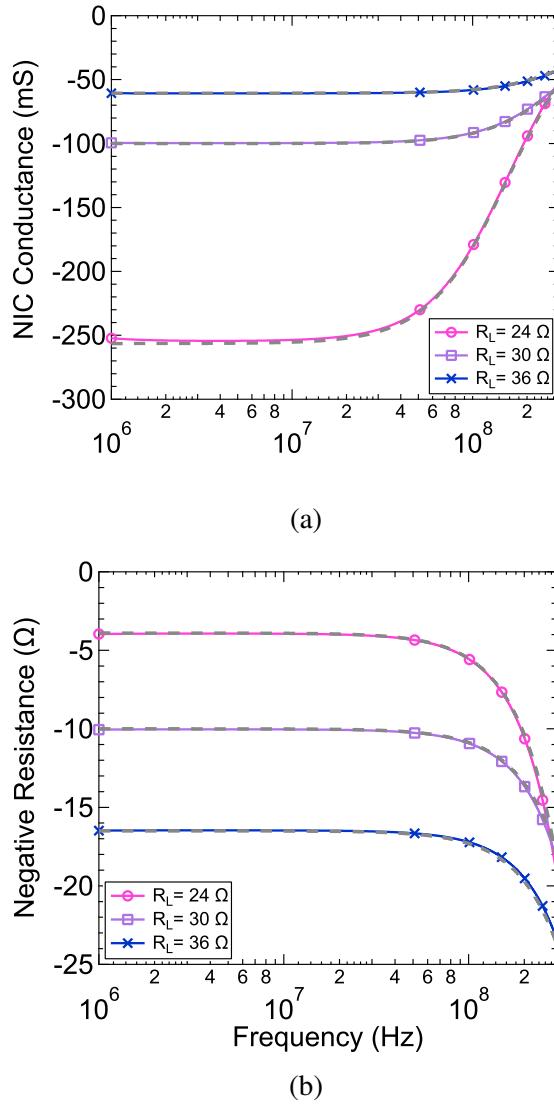

| 7.17 | Simulations of the Linvill OCS NIC circuit (solid) and passive equivalent circuit model (dashed) for different $R_L$ (a) Input conductance (b) Negative resistance . . . . .                                                                              | 272 |

| 7.18 | Additional capacitance to compensate for NIC inductance of Linvill OCS NIC circuit (a) Without and (b) With tuning capacitance $C_t$ . .                                                                                                                  | 273 |

| 7.19 | Photodiode and NIC passive equivalent circuit model . . . . .                                                                                                                                                                                             | 275 |

| 7.20 | Linvill OCS NIC circuit generating negative floating resistance to compensate for the photodiode series resistances $R_s + R_T$ . . . . .                                                                                                                 | 277 |

|                                                                                                                                                                                                                                                                                                        |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

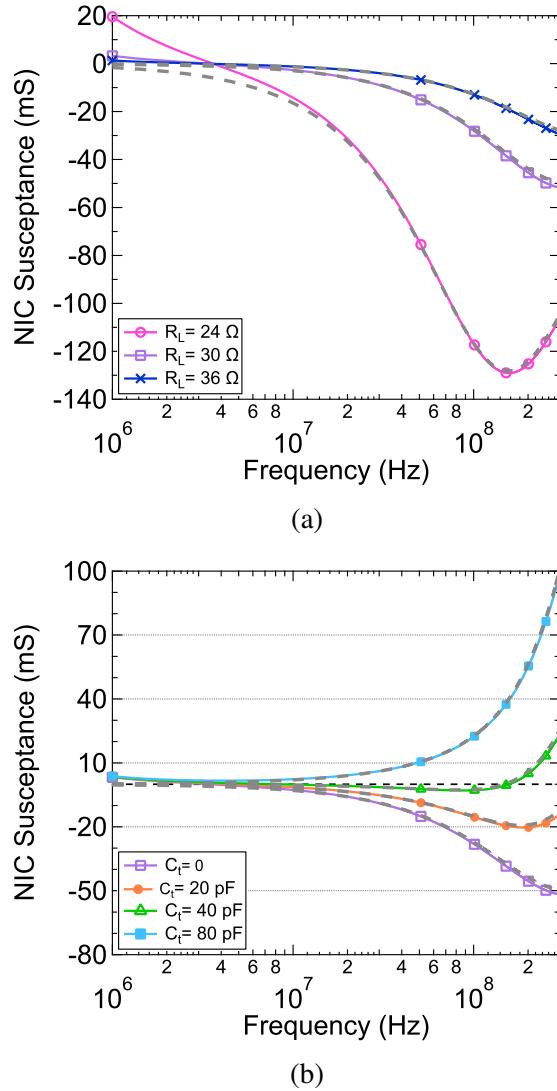

| 7.21 Simulations of the application of the negative resistance circuit (OCS NIC circuit) to the full photodiode equivalent model and the RGC TIA as shown in Figure 7.20, for different $R_L$ values (a) Input impedance (b) Transimpedance gain . . . . .                                             | 278 |

| 7.22 Simulations of the application of the negative resistance circuit (OCS NIC circuit) to the full photodiode equivalent model and the RGC TIA as shown in Figure 7.20 at $R_L = 30 \Omega$ for different values of the tuning capacitor $C_t$ (a) Input impedance (b) Transimpedance gain . . . . . | 280 |

| 7.23 Simulations of the application of the negative resistance circuit (OCS NIC circuit) to the full photodiode equivalent model and the RGC TIA versus the modified RGC TIA at $R_L = 30 \Omega$ and $C_t = 80 \text{ pF}$                                                                            | 281 |

| <br>                                                                                                                                                                                                                                                                                                   |     |

| A.1 Fabricated OCS NIC PCB . . . . .                                                                                                                                                                                                                                                                   | 297 |

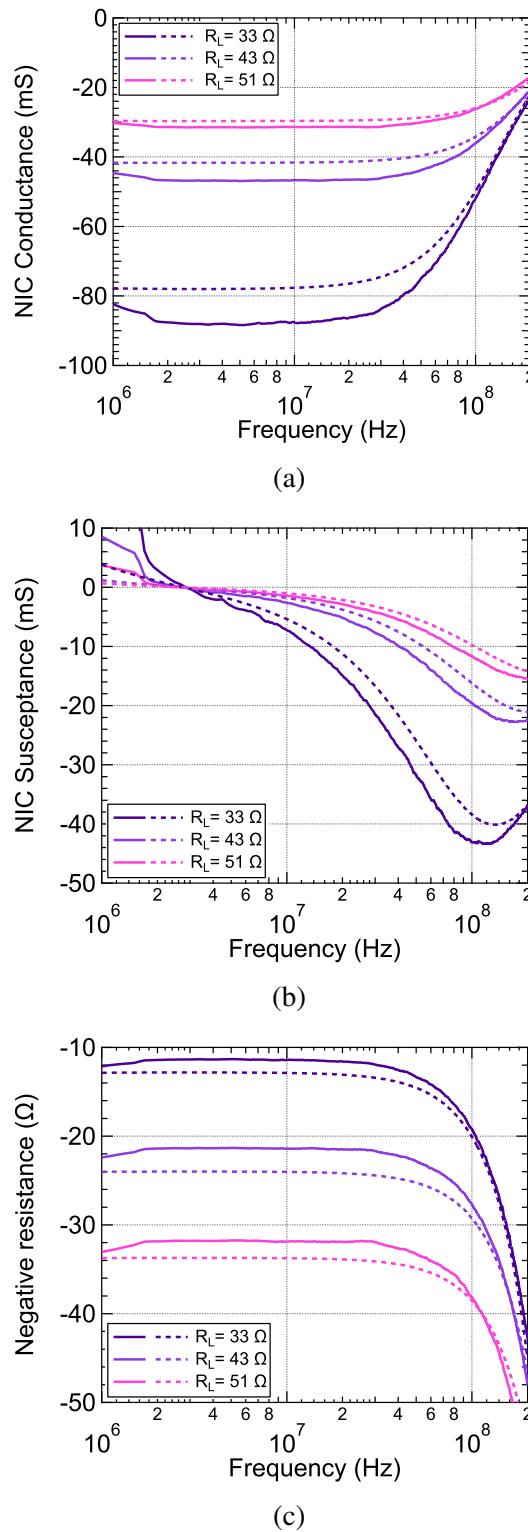

| A.2 Measured (solid) and simulated (dashed) OCS Linvill NIC at $I_C = 3$ for different $R_L$ (a) Conductance (b) Susceptance (c) Negative resistance . . . . .                                                                                                                                         | 299 |

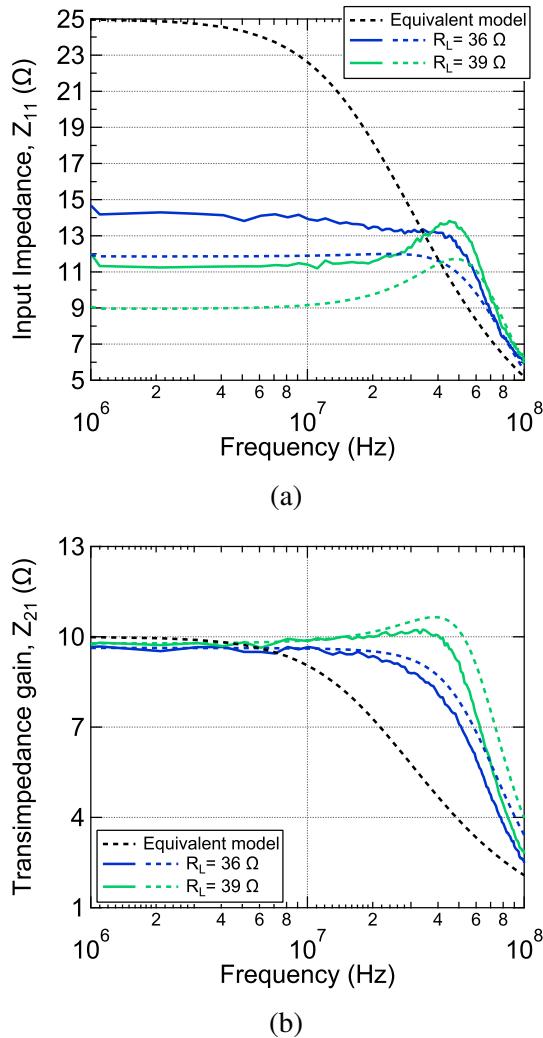

| A.3 Measured (solid) and simulated (dashed) responses of overall network including OCS Linvill NIC, photodiode and TIA equivalent circuit model (a) Impedance response (b) Transimpedance gain . . .                                                                                                   | 301 |

# List of Tables

|     |                                                                                                                                                                    |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Summary of the key negative impedance circuits . . . . .                                                                                                           | 70  |

| 3.1 | The negative capacitance circuit semi-empirical equivalent circuit model parameters . . . . .                                                                      | 82  |

| 4.1 | Blue LED extracted model parameters at various currents . . . . .                                                                                                  | 134 |

| 4.2 | Red LED extracted model parameters at various currents . . . . .                                                                                                   | 140 |

| 4.3 | Key System Parameters . . . . .                                                                                                                                    | 141 |

| 5.1 | Performance summary of TIAs for OWC applications . . . . .                                                                                                         | 159 |

| 5.2 | Performance comparison for various low input impedance TIA configurations . . . . .                                                                                | 184 |

| 6.1 | RGC equivalent model circuit parameter . . . . .                                                                                                                   | 193 |

| 7.1 | Extracted model parameters for the PIN10-D (100 mm <sup>2</sup> ) at different $V_B$ . . . . .                                                                     | 253 |

| 7.2 | Extracted model parameters for the PIN25-D (600 mm <sup>2</sup> ) at different $V_B$ . . . . .                                                                     | 253 |

| 7.3 | Measured and predicted bandwidths of the PIN10-D (100 mm <sup>2</sup> ) and PIN25-D (600 mm <sup>2</sup> ) at different $V_B$ into a 50 $\Omega$ and the RGC TIA . | 258 |

| 7.4 | Extracted model parameters for the OSD50-E (50 mm <sup>2</sup> ) at different $V_B$ . . . . .                                                                      | 260 |

| 7.5 | Extracted model parameters for the OSD100-E (100 mm <sup>2</sup> ) at different $V_B$ . . . . .                                                                    | 260 |

|     |                                                                                                                                                                     |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.6 | Measured and predicted bandwidths of the OSD50-E (50 mm <sup>2</sup> ) and<br>OSD100-E (100 mm <sup>2</sup> ) at different $V_B$ into a 50 $\Omega$ and the RGC TIA | 264 |

| 7.7 | Extracted passive equivalent model parameters for the NIC circuit<br>in Figure 7.16 at different $R_L$                                                              | 271 |

# List of Abbreviations & Symbols

$\beta$  Transistor current gain

$\zeta$  Damping factor

$\omega_n$  Natural frequency

$\epsilon_o$  Relative permittivity of vacuum

$\epsilon_r$  Dielectric constant of a material

$A_T$  Transimpedance gain

$A_v$  Amplifier voltage gain

$C_\mu$  Base collector capacitance

$C_\pi$  Base emitter capacitance

$C_c$  Compensating capacitor

$C_{gd}$  Gate drain capacitance

$C_{gs}$  Gate source capacitance

$C_j$  Junction capacitance of the LED

$C_{pd}$  Photodiode junction capacitance

$L_b$  Base contact inductance

$L_c$  Collector contact inductance

$L_e$  Emitter contact inductance

$Q$  Quality factor of the complex pole

$R_F$  Feedback resistor

$R_{com}$  Compensating resistor

$R_e$  Emitter contact resistance

$R_{in}$  Input resistance

$R_{stb}$  Stabilising resistor

$f_T$  Transit frequency

$g_m$  Transconductance

$r_\pi$  Base emitter junction dynamic resistance

$r_{bb}$  Intrinsic base spreading resistance

$r_d$  Dynamic resistance of the LED

$r_e$  Transistor dynamic resistance

**AGC** Automatic Gain Control

**ANN** Artificial Neural Network

**BJT** Bipolar Junction Transistor

**BLW** Baseline Wander

**CAP** Carrier-less Amplitude and Phase

**CB** Common Base

**CC** Common Collector

**CD** Common Drain

**CE** Common Emitter

**CG** Common Gate

**CML** Current Mode Logic

**CMOS** Complementary Metal Oxide Semiconductor

**CS** Common Source

**DMT** Discrete Multitone

**EM** Electromagnetic

**ESD** Electrostatic Discharge Circuit

**FET** Field Effect Transistor

**HBT** Heterojunction Bipolar Transistor

**IEEE** Institute of Electrical and Electronic Engineering

**INIC** Current Inversion Negative Impedance Converter

**IoT** Internet of Things

**LED** Light Emitting Diode

**NIC** Negative Impedance Converter

**NII** Negative Impedance Inverter

**NMOS** N-channel Metal Oxide Semiconductor

**OCS** Open Circuit Stable

**OFDM** Orthogonal Frequency Division Multiplexing

**OOK** On Off Keying

**Op-amp** Operational amplifier

**OWC** Optical Wireless Communication

**PCB** Printed Circuit Board

**PMOS** P-channel Metal Oxide Semiconductor

**RF** Radio Frequency

**RGC** Regulated Cascode

**SCS** Short Circuit Stable

**SFB** Shunt Feedback

**SiGe** Silicon Germanium

**SMD** Surface Mount Devices

**SNR** Signal to Noise Ratio

**TIA** Transimpedance Amplifier

**VLC** Visible Light Communication

**VLCC** Visible Light Communication Consortium

**VLSI** Very Large Scale Integration

**VNA** Vector Network Analyser

**VNIC** Voltage Inversion Negative Impedance Converter

**WDM** Wavelength Division Multiplexing

**XCP** Cross Coupled transistor Pair

## Chapter 1

# Introduction

Communication specialist companies such as Cisco forecast the number of connected devices to be more than three times the global population by 2023 [1]. The proliferation of mobile devices, all of which demand faster connection speeds, is fuelled by various data-hungry applications such as virtual reality, multimedia streaming and gaming services, resulting in severe spectral congestion, causing a capacity crunch; the main cause is the inability of radio frequency (RF) to meet demand due to spectrum shortage. Therefore, complementary wireless communication systems are being continuously proposed, and one of the most promising candidates is visible light communication (VLC). VLC uses light in the spectral range 380-740 nm ( $\sim$ 800-400 THz) to transmit and receive data, mainly via light emitting diodes (LEDs) and photodiodes, respectively.

The first demonstration of VLC using a single white LED was in Japan in 2000 [2]; since then interest in VLC rapidly grew with abundance of practical demonstrations adopting different technologies to enable multi-Gbps VLC systems. Alas, practical VLC is still in its infancy, due to the bandwidth limitation imposed by the optoelectronic devices, namely, LEDs and photodiodes, hence, restricting the achievable transmission speeds. Moreover, severe limitations are imposed by the highly attenuating free-space channel, which limits the received optical signal power. To combat such limitations, researchers focused on the efficient utilisation of the limited bandwidth offered by the optoelectronic devices by (i) Adopting advanced modulation formats, such as orthogonal frequency division

multiplexing (OFDM) and carrier-less amplitude and phase (CAP), to maximise the number of transmitted bits per symbol [3–8], (ii) Using efficient equalisation techniques at the transmitter and receiver [9, 10] (iii) Exploiting the colour dimension to enable wavelength division multiplexing (WDM), as such provide additional spectrum [11, 12]. Others resorted to improving the available bandwidth by employing higher bandwidth devices such  $\mu$ LEDs and lasers. Only a few researchers have exploited bandwidth enhancement circuits techniques to circumvent the bandwidth limitation imposed by LEDs or photodiodes.

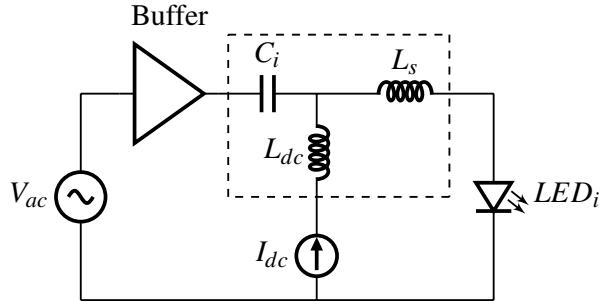

This work is motivated by the importance of dealing with the bottleneck imposed by the optoelectronic devices, which has been identified as a perpetual challenge in achieving high data rates in VLC in [13], and most recently elegantly summarised in [14], where the importance of optimised device selection was highlighted. As such this thesis focuses on exploring existing and new electronic circuit techniques that improve the utility of the highly bandwidth-limited optoelectronic devices in VLC systems, extending the bandwidth of VLC transmitters and receivers. At the transmitter, the main challenge is improving data transmission speeds, considering the low modulation bandwidth of commercially available LEDs, typically limited to a few MHz. The LED bandwidth is determined by the carrier lifetime and the RC time constant associated with its dynamic resistance ( $r_d$ ) and junction capacitance ( $C_j$ ). A commonly used circuit technique to overcome the bandwidth limitations of LEDs is analogue passive RC-based equalisers, as reported in [15–20]. This type of equaliser applies a passive high pass filter with the inverse response of the LED frequency response, hence, extending its bandwidth. Nevertheless, such bandwidth extension is often at the expense of substantial loss in the LED optical signal power. While such equalisers have effectively demonstrated high data rates in VLC links by extending the transmitter bandwidth, their benefits will always be limited as they incur a significant loss in optical power. Hence, limiting the LED output light intensity and possibly the overall system capacity due to the reduction in signal to noise ratio (SNR) at the receiver.

In contrast, the work in this thesis proposes an optically lossless LED circuit-

based bandwidth extension technique. The technique is based on the use of active circuits to generate negative capacitance in parallel to the LED junction capacitance to neutralise its bandwidth-limiting effect on the determination of the VLC transmitter bandwidth. The elegance of such a technique is that it does not result in any resistive loading to the LED; hence, the resultant bandwidth enhancement does not compromise its optical power. Moreover, it allows for bespoke, yet easily adjustable, LED driver circuit design based on the distinct characteristics of each LED, while also combining with other existing techniques to further the bandwidth enhancement. The generation of negative capacitance via active circuits can be achieved either by using networks known as negative impedance converters (NICs) or by using amplifiers that utilise the Miller effect. The operation, advantages and disadvantages of each of the negative capacitance circuits are to be discussed in Chapter 2.

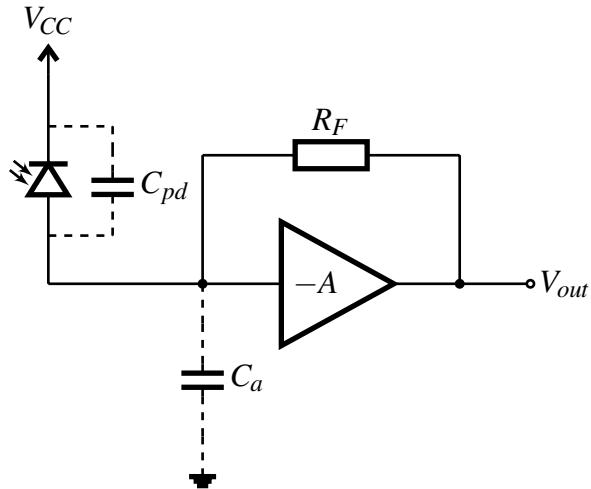

At the receiver, the challenge is to capture sufficient light to ensure correct detection of the transmitted information. This is a difficult challenge due to two reasons; firstly, the highly attenuating nature of the free-space channel, whose loss is proportional to the square of the transmission distance. Second, most photodiodes operating in the visible range are made of doped silicon, which has poor responsivity in the visible light frequency range, especially at blue wavelength, commonly used in VLC. To boost the received optical power and maximise the associated photocurrent, especially for applications that demand large transmission distances, ideally, the receiver should have a large-area photodiode to maximise light capture. Alternatively, systems may employ high gain transimpedance amplifiers (TIAs)<sup>1</sup> to convert the low amplitude photocurrent from the photodiode into an amplified voltage. Ideally, systems would combine large photoactive area detectors and high gain TIAs. Unfortunately, large-area photodiodes have highly limited bandwidth, particularly when followed by either  $50\ \Omega$  or high input impedance TIAs; such limitation arises from their substantially high junction capacitance ( $C_{pd}$ ), which is proportional to the active area. In the vast majority of VLC reports, such bandwidth limitation is avoided by employing small area photodiodes, which are simply

---

<sup>1</sup>Throughout this thesis, the term TIA, which is the most commonly used, is adopted for optical front-ends with current input and voltage output

incapable of collecting sufficient optical power to allow practical distances.

Using a low input impedance TIA configuration is advantageous in tolerating high photodiode capacitances [21]. This is because the dominant time constant, which determines the receiver bandwidth, is a product of photodiode capacitance and the TIA input resistance. Hence, a TIA with low input resistance reduces the time constant and significantly increases the bandwidth. Circuits with ultra-low input resistance, such as the regulated cascode (RGC) [22–24] were found to be highly attractive for use in VLC systems. The work in this thesis proposes the use of the low input impedance RGC TIA to improve the utility of unconventionally large-area photodiodes, in the range of  $100\text{ mm}^2$  to  $600\text{ mm}^2$ , which have associated junction capacitances in the range of 100's of picofarads to a few nanofarads. The use of such large-area photodiode is not common in VLC systems, which often employ photodiodes of few  $\text{mm}^2$ . This is often done to avoid the bandwidth limitation associated with such large-area photodiodes, yet it removes the increased signal power advantages achieved with such photodiodes and, in turn, often limit the transmission distances.

Employing such a large-area photodiode can be highly beneficial in boosting the received signal power. Such an increase in the received signal power may allow for transmission at longer distances, making the application of VLC more practicable. Nevertheless, it imposes a complex design challenge on the successive transimpedance amplifier. This work endorses the use of low input impedance TIAs for their advantages in tolerating such high photodiode capacitance and, therefore, provides a remarkable improvement in bandwidth compared to a traditional  $50\text{ }\Omega$  TIAs. The work explores existing and new low input impedance TIA configurations based on critical analysis of their performance with high photodiode capacitances to achieve high gain and wide-band performance.

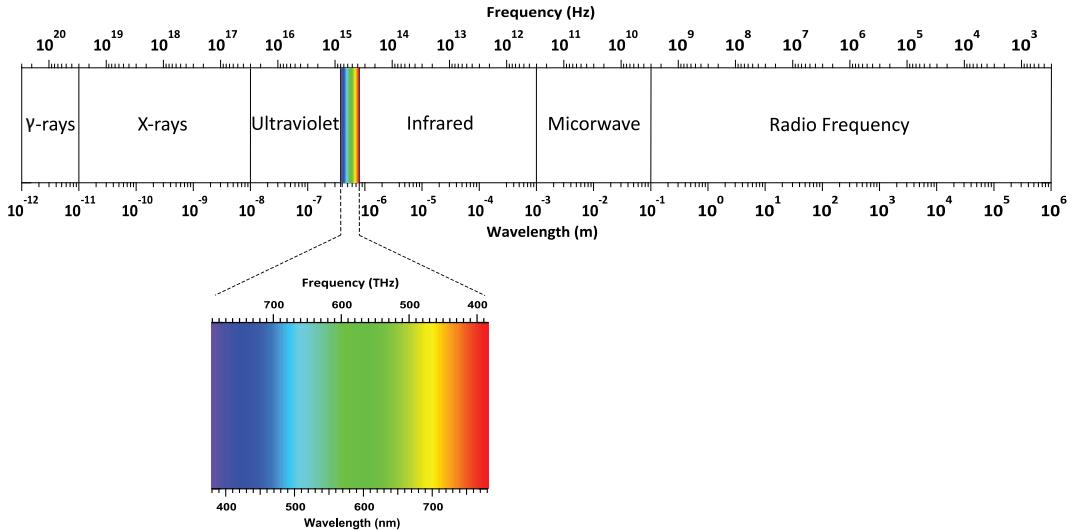

Figure 1.1: EM spectrum

## 1.1 VLC Preliminaries & Challenges

Figure 1.1 shows the electromagnetic (EM) spectrum specifying the wavelength band of different waves, where it extends from low RF to highest frequency gamma rays with the shortest wavelength. The RF is predominately the most used portion of the EM spectrum to facilitate communication. On the other hand, advancements in user electronics and mobile communication have led to an unprecedented proliferation of mobile devices, demanding higher data rates and better signal quality. The result is a severely congested RF spectrum. Therefore, systems that complement wireless links have been proposed, and one of the most promising is VLC, which is gaining high research momentum. VLC offers  $\sim 400$  THz of new, unlicensed bandwidth, as opposed to the 300 GHz of heavily regulated RF spectrum. This spectrum directly translates into a new capacity for access networks, alleviating the looming capacity crunch.

Moreover, the ubiquity of LEDs renders an economic advantage, as existing lighting infrastructure is utilised, and installation of LEDs is cheap: LEDs serve the dual functionality of illumination and communication, through intensity modulation of an LED using a data source. The modulated light from the LED propagates over free-space and is recovered using direct detection via a photodetector. The first VLC report using white LEDs emerged in Japan [2]. Following this, the concept of VLC

started to grow rapidly, and the visible light communication consortium (VLCC) was established in Japan in 2003. This was followed by the standardisation of VLC by the institute of electrical and electronic engineering (IEEE) in 2012, and ever since, the interest in VLC has rapidly grown with an abundance of practical demonstrations adopting different technologies to enable high data rate transmission. The following sections briefly discuss some of the transmitters and receivers employed in VLC, highlighting their advantages and drawback and some of the technologies that allowed for improved utility of such devices in the application of high-speed data transmission. Noting that the following discussion of the bandwidth limitation of the optoelectronic devices and techniques to tackle such limitation is only relevant within applications requiring high-speed data transmission, yet such theme may not concern other visible light applications such as indoor positioning.

## **VLC Transmitter Light Source**

The majority of light sources utilised in VLC systems are white light LEDs, which are classified into two types: Phosphors-coated LEDs (PC-LEDs) and tri-chromatic red, green and blue LEDs (RGB-LED). The first type achieves white light using a single blue LED coated with a complementary colour converting material such as a yellow phosphor. The second method is by combining the emission of multiple colour LEDs to form white light. However, the former approach limits the bandwidth of the LED to a few MHz due to the slow response of the phosphorous colour converting material [13, 25]. It is possible to enhance the modulation bandwidth of PC-LEDs by employing blue filtering at the receiver to undo the effect of the slow yellow component and extract the fast blue response. Hence, extending the LED bandwidth up to 30 MHz, but at the expense of considerable loss in the received signal power [25–27].

To overcome the LED bandwidth limitation, advanced modulation techniques have been extensively adopted. The most popular advanced modulation formats used in VLC are OFDM and CAP. A comparative study highlighting the merits and drawbacks of the two modulation schemes is available [28]. In addition, a review in [7], surveys the milestone of the application of CAP modulation in VLC

has undergone, including multi-band CAP and its transition to non-orthogonal sub-bands and to the most recent developments. The adoption of advanced modulation formats such as CAP, has substantially improved the utility of highly bandwidth-limited devices. For example, work in [8] utilises a large off-the-shelf LED panel with dimensions of  $60 \times 60 \text{ cm}^2$  at distances up to 2 metres, achieving a data rate of 40 Mbps due to the use of multi-band CAP modulation.

While the generation of white light using PC-LEDs offers advantages in terms of reduced cost and complexity compared to RGB-LEDs. RGB-LEDs, however, offer the distinct possibility of modulating each colour independently and hence supporting parallel transmission using WDM. Moreover, the bandwidth of individual components is not limited by the colour converting material as in PC-LEDs. However, one of the main challenges with WDM is the cross-talk between the different colour components, where the energy from each wavelength overlaps, causing difficulties in separating individual wavelengths at the receiver. Such limitation often requires the implementation of independent dichroic filters, photodiodes and receiver circuits for each wavelength used, which leads to increased system complexity as reported in [11]. Other reports propose to reduce the complexity of WDM systems by utilising different colour LEDs, yet only one photodiode receiver [12]. The technique capitalises on the natural diversity offered by photodiodes based on the wavelength-dependent responsivities, which allows for the separation of the different LED wavelengths based on their different SNR ratios.

The bandwidth of a single-colour LED is fundamentally limited by its carrier lifetime and the RC time constant associated with the product of its dynamic resistance and junction capacitance. One popular variety of LEDs that treats the bandwidth limitations encountered in conventional single-colour LEDs is  $\mu$ LEDs. Compared to conventional broad area single-colour LEDs,  $\mu$ LEDs can be driven at significantly higher current densities, reducing their carrier lifetime, allowing for higher bandwidth. Moreover, since capacitances scale with the device area, the modulation bandwidth of  $\mu$ LEDs is not limited by its RC time constant. However, despite their significantly high modulation bandwidth, implementing  $\mu$ LEDs of-

ten requires aggregating a large number of  $\mu$ LEDs into an array. This is because the optical power given by a single  $\mu$ LED is quite low, due to its ultra-small area emitting area. For example, work in [3], utilises a single 50- $\mu$ m diameter LED of 60 MHz 3dB- bandwidth and a commercial high-speed silicon photodiode (ultra-small area 0.12 mm<sup>2</sup>), in addition to employing OFDM, bit and power loading to achieve a communication speed of 3 Gbps at a 5 cm link distance. Whereas, work in [29] aggregates a 3x3 40- $\mu$ m LED array of 245 MHz 6dB- bandwidth and, also employing OFDM, to achieve communication speed of 4.81 Gbps at a 30 cm link distance. One reason for the increase in the communication distance is the increase in the transmitter optical power from 4.5 mW to 18 mW, from the single to the 3x3 40- $\mu$ LED case, respectively.

Organic LEDs (OLEDs) are another light source used in VLC, which has garnered a lot of research interest, mainly due to their widespread use in display technologies and their simple and cost-effective manufacturing ability [30]. Nevertheless, such devices have significantly low charge mobility, typically three orders of magnitude lower than inorganic LEDs, limiting their modulation bandwidths in the range of 10's to 100's of kHz only. Despite their severe bandwidth limitation, such devices are still suitable for a wide range of prospective applications, such as the implementation of the internet of things (IoT), which only require data rates of a few Mbps. In [31], a new class of OLEDs are integrated into a real-time VLC setup employing a commercially available silicon photodiode of area 13 mm<sup>2</sup>, achieving an error-free above 1 Mbps, without the use of any computationally complex equalisers, yet at a distance of only 5 cm.

Laser diodes light sources are often employed in VLC systems, with demonstrated Gbps transmission rates. However, despite having significantly higher modulation bandwidth than LEDs, their quality for indoor illumination remains debatable, due to the highly directional nature of their emission. Nevertheless, studies in [32] showed that the use of diffused laser light sources could provide a homogeneous illumination as with conventional LED light luminaries.

All of the sources used require drive circuits, which match the characteristics

of the device, a challenge often overlooked by designers, which will be addressed in this thesis.

## **VLC Receiver Light Detectors**

The receiver detectors used in VLC systems are predominately either silicon-based positive-intrinsic-negative (PIN) photodiodes or avalanche photodiodes (APD). Other photodetector varieties, such as the single-photon avalanche (SPAD) photodiode, have also established themselves as one of the promising receiver technologies because of their potential for improved sensitivity. However, the dead time, finite output pulse width, and photon detection efficiency of existing SPAD still limit their bandwidth [33]. Other viable photodetectors like solar cells [34], and imaging sensors (camera sensors) [10] have also been reported. Moreover, advances in photodetectors using polymer-based materials have given rise to organic photodiode (OPD), which can be cheaply and easily fabricated and has the advantage of responsivity higher than silicon in the visible range [35]. Yet, such devices are limited by their significantly low bandwidth (<1 MHz) [36].

The available SNR at the receiver determines the quality of the received signal, and for a given bandwidth, the SNR is determined by the transmitted power, channel loss and the receiver responsivity and noise, which are sometimes expressed as figures of sensitivity. As in all communication systems, a compromise is required between power, bandwidth and signal quality. For example, a VLC transmitter employing traditional large-area LED can maximise the transmitted optical power, yet would have limited bandwidth. On the other hand, employing  $\mu$ LEDs would result in higher bandwidth, yet with reduced transmitted optical power. VLC receivers power-bandwidth compromise is no different from that of transmitters, since employing larger area photodiodes has the advantage of increasing the light collection; as such, improving the SNR, yet again limits the available bandwidth because of associated high capacitances. Another way of improving the SNR when using small area photodiodes is to use concentrators, which typically consists of a set of lenses at the transmitter and the receiver, but other implementations are also possible such as the use of luminescent concentrators [37]. The advantage of using optical con-

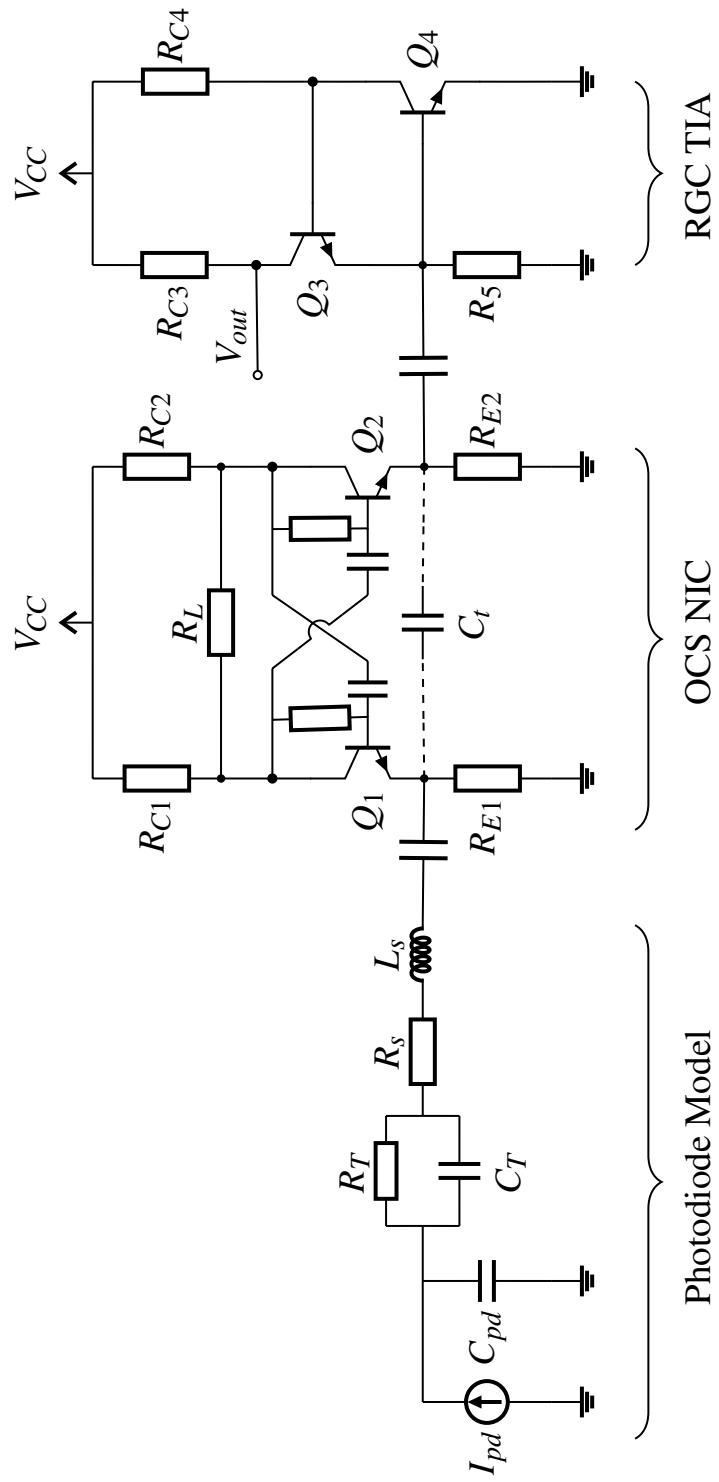

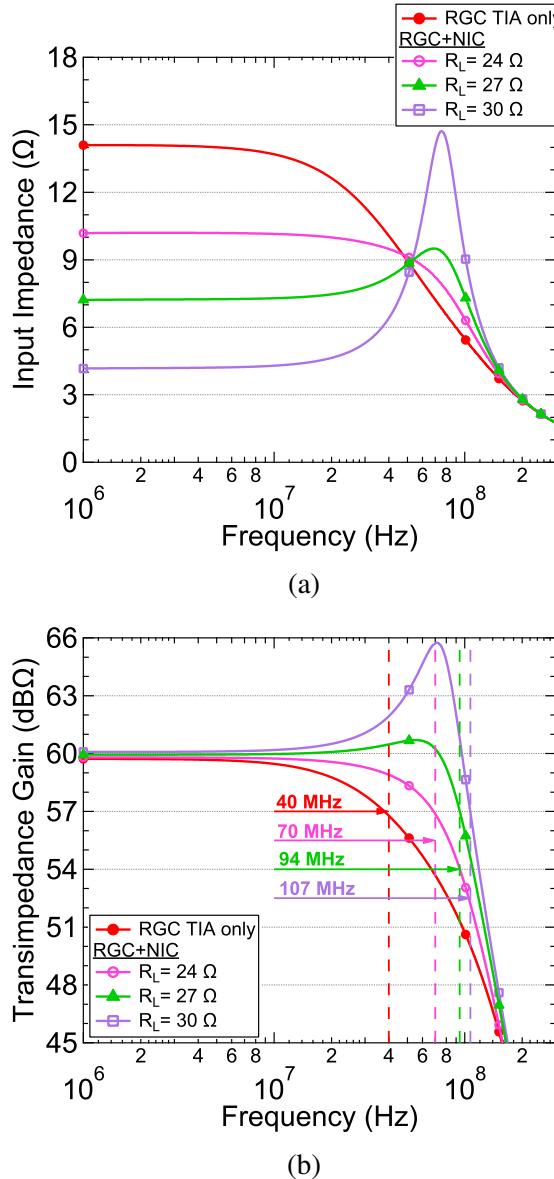

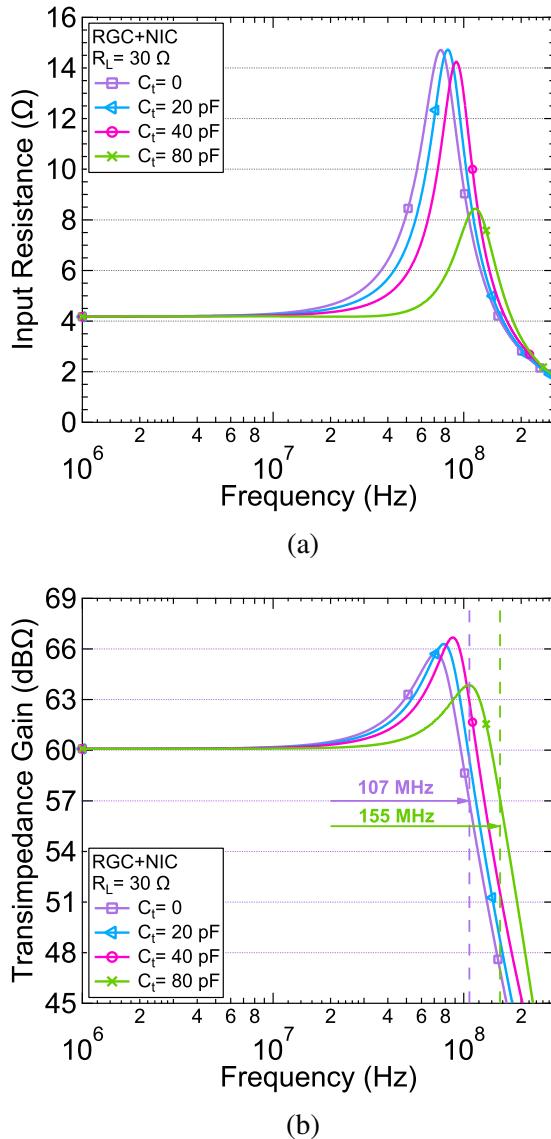

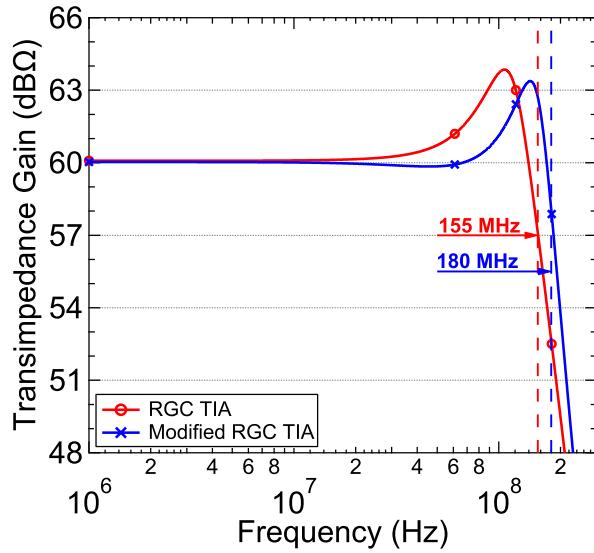

centrators is increasing the effective receiver area and hence, increasing the signal power without compromising bandwidth. However, such an advantage is typically at the expense of reducing the receiver field of view [13].