UNIVERSITY OF LONDON

University College London

**DESIGN OF LINEAR AND

NONLINEAR CIRCUITS USING

DERIVATIVE SUPERPOSITION**

By

Gholamreza Ataei

A THESIS

Submitted to the University of London

in fulfillment of the requirements for

the degree of Doctor of Philosophy

February 2000

ProQuest Number: 10797841

All rights reserved

INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10797841

Published by ProQuest LLC (2018). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code

Microform Edition © ProQuest LLC.

ProQuest LLC.

789 East Eisenhower Parkway

P.O. Box 1346

Ann Arbor, MI 48106 – 1346

# DESIGN OF LINEAR AND NONLINEAR CIRCUITS USING DERIVATIVE SUPERPOSITION

by

Gholamreza Ataei

## ABSTRACT

Modern communication systems require a wide variety of linear and nonlinear circuits such as power amplifiers and frequency multipliers. The derivative superposition (DS) technique has been proposed for the design of linear and nonlinear circuits. A DS circuit uses a number of field effect transistors (FETs) in parallel with each other and having different gate widths and operating points. This allows the designer to control the shape of the transfer characteristic to meet a particular linear or nonlinear specification. This technique has been chosen to be the subject of the work in this thesis.

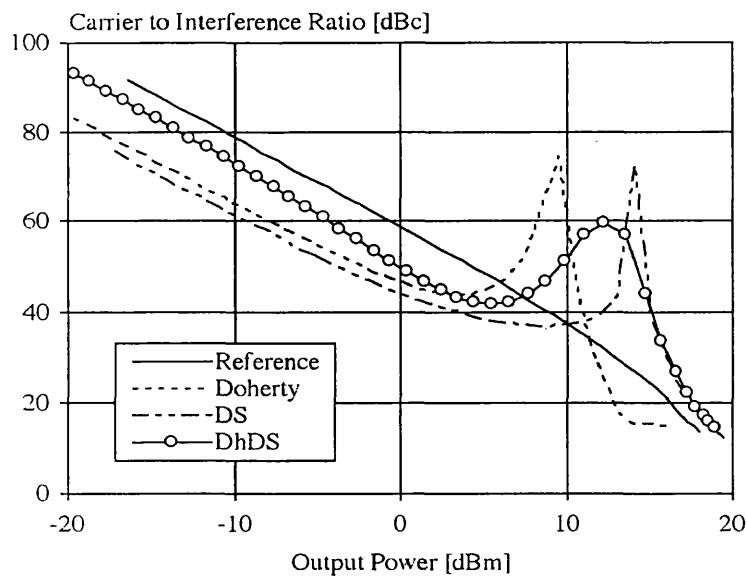

It is shown that a MMIC DS power amplifier using a novel phase reversal form of DS achieves a two tone carrier to interference ratio (c/i) of 45 dBc with an efficiency of 22.5 % close to 1 dB compression around 0.5 GHz providing a better compromise between linearity and efficiency than conventional single amplifier classes. A novel composite Doherty-DS structure is proposed which is capable of providing a wider dynamic range for better c/i performance close to 1 dB compression and a good compromise in terms of efficiency compared to those of either the Doherty or the DS amplifiers alone.

The DS approach is used to design a nonlinear function circuit for a quasi-optical tracking system and a MMIC frequency tripler design which achieves a considerable suppression of unwanted frequency products. A refined version of the DS frequency tripler is proposed which employs a rat race coupler for operation well into the microwave region.

During this work some improvements were made to the set-up for the intermodulation distortion measurements of FETs, a study of factors affecting distortion of various FETs was carried out and a visualisation technique was developed for mapping the distortion of a FET allowing identification of an optimum bias and loading condition.

# Acknowledgements

I wish gratefully to thank my supervisors Dr. David Haigh and Dr. Danny Webster who made this work possible. Dr. Haigh, for his endless support, enthusiasm, encouragement and proof reading and always being willing and available for discussion despite his hectic schedule during the period of this thesis. Dr. Webster, for his continuous technical support, inspiration, encouragement and never ending enthusiasm and always being eager and available for discussion despite his busy schedule throughout the period of this thesis.

I would like to thank Dr. Paul Brennan for his very helpful comments on the M.Phil. to Ph.D. transfer thesis.

I would like to thank my fellow Ph.D. student and friend Mervin Hutabarat for useful discussions during this work.

I wish to extend my thanks to all my friends who have given me their support and provided me with much needed comfort away from the academic life.

Lastly, but by rights first, I would like to thank my parents and sisters for their patience, support and love throughout the period of this thesis.

به پدر و مادرم

از برای عشق بیکران

"هل يسْتَوِي الَّذِينَ يَعْلَمُونَ وَ الَّذِينَ لَا يَعْلَمُونَ إِنَّمَا يَتَذَكَّرُ أُولُوا الْأَلْبَابِ"

(سوره الزمر، آیه ۹)

چون بباید مشتری بر فروخت

دایما بازار او با رونق است.

علم تقليدي برد بهر فروخت

مشتری علم تحقیقی حق است

(مثنوی معنوی، دفتر دوم، ایيات ۳۲۶۵ و ۳۲۶۶)

# Contents

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| <b>Title Page</b>                                                 | <b>1</b>  |

| <b>Abstract</b>                                                   | <b>2</b>  |

| <b>Acknowledgement</b>                                            | <b>3</b>  |

| <b>Dedication</b>                                                 | <b>4</b>  |

| <b>Contents</b>                                                   | <b>5</b>  |

| <b>List of Figures</b>                                            | <b>11</b> |

| <b>List of Tables</b>                                             | <b>22</b> |

| <b>1 Introduction</b>                                             | <b>24</b> |

| 1.1 Linear and Nonlinear Circuits in Modern Communication Systems | 24        |

| 1.2 Derivative Superposition Approach . . . . .                   | 25        |

| 1.3 Aim of Project . . . . .                                      | 25        |

| 1.4 Statement of Collaboration . . . . .                          | 25        |

| 1.5 Review of Chapter Contents . . . . .                          | 26        |

| 1.6 List of Publications . . . . .                                | 28        |

| <b>2 Background</b>                                               | <b>32</b> |

| 2.1 General . . . . .                                             | 32        |

| 2.2 GaAs Devices and Technology . . . . .                         | 32        |

| 2.2.1 Advantages of GaAs . . . . .                                | 33        |

| 2.2.2 Passive Devices . . . . .                                   | 34        |

| 2.2.3 Active Devices . . . . .                                    | 35        |

| 2.3 Nonlinear Analysis . . . . .                                  | 37        |

| 2.3.1 Terminology . . . . .                                       | 37        |

| 2.3.1.1 Concepts of Linearity and Nonlinearity . . . . .          | 37        |

|          |                                                      |           |

|----------|------------------------------------------------------|-----------|

| 2.3.1.2  | Fundamental Definitions                              | 39        |

| 2.3.2    | Nonlinear Analysis Techniques                        | 43        |

| 2.4      | Nonlinearity Characterisation Techniques             | 46        |

| 2.4.1    | Load Pull Method                                     | 46        |

| 2.4.2    | Measuring S-parameters                               | 47        |

| 2.4.3    | Pulsed I-V Measurement                               | 47        |

| 2.4.4    | Maas RF Harmonic Distortion Measurement Method       | 48        |

| 2.4.5    | Pedro and Perez Distortion Measurement Method        | 49        |

| 2.4.6    | FET Resistance Measurement                           | 49        |

| 2.4.7    | TDFD Measurement                                     | 51        |

| 2.5      | MESFET and HEMT Models                               | 52        |

| 2.5.1    | The Schichmann-Hodges Model                          | 52        |

| 2.5.2    | The Curtice Quadratic Function MESFET Model          | 53        |

| 2.5.3    | Materka Model                                        | 53        |

| 2.5.4    | Statz Model                                          | 53        |

| 2.5.5    | Curtice Cubic Model                                  | 54        |

| 2.5.6    | TOM Model                                            | 54        |

| 2.5.7    | Parker Skellern MESFET Model                         | 55        |

| 2.5.8    | Frequency Dispersion in MESFETs and HEMTs            | 57        |

| 2.6      | Summary                                              | 60        |

| <b>3</b> | <b>Review of Linear and Nonlinear Circuit Design</b> | <b>66</b> |

| 3.1      | General                                              | 66        |

| 3.2      | Survey of Requirements                               | 66        |

| 3.2.1    | Linear Amplifiers                                    | 66        |

| 3.2.1.1  | Small Signal Amplifiers                              | 67        |

| 3.2.1.2  | Power Amplifiers                                     | 67        |

| 3.2.2    | Amplifiers with Prescribed Nonlinearity              | 68        |

| 3.2.3    | Nonlinear Circuit Requirements                       | 68        |

| 3.3      | The Common-Source Amplifier                          | 70        |

| 3.3.1    | Basic Circuit Configuration                          | 70        |

| 3.3.2    | Distortion Generation Mechanism                      | 70        |

| 3.3.3    | Matching Networks                                    | 72        |

| 3.3.4    | Effect of Bias and Load on Distortion                | 72        |

| 3.3.5    | Effect of Filtering for Nonlinear Applications       | 73        |

| 3.4      | Extensions to the Common-Source Amplifier            | 73        |

| 3.4.1    | The Distributed Amplifier                            | 73        |

| 3.4.2    | The Derivative Superposition Approach                | 74        |

|          |                                                                                                          |            |

|----------|----------------------------------------------------------------------------------------------------------|------------|

| 3.4.2.1  | Derivatives of a FET . . . . .                                                                           | 75         |

| 3.4.2.2  | Derivative Superposition Topology . . . . .                                                              | 76         |

| 3.4.2.3  | Derivative Superposition Amplifier Based on High-pass Transmission Lines . . . . .                       | 78         |

| 3.4.2.4  | Super Deriv Software . . . . .                                                                           | 80         |

| 3.5      | Comparison of Circuit Linearisation Design Techniques for Small and Medium Signal Applications . . . . . | 82         |

| 3.5.1    | Balanced Amplifier with Passive Splitter/Combiner . . . . .                                              | 82         |

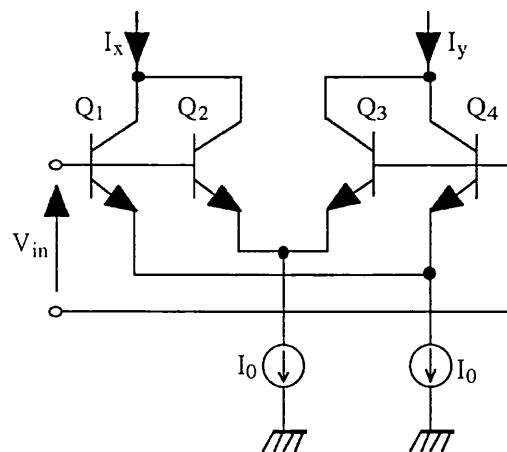

| 3.5.2    | Multi-tanh Technique . . . . .                                                                           | 83         |

| 3.5.3    | Translinear Technique . . . . .                                                                          | 85         |

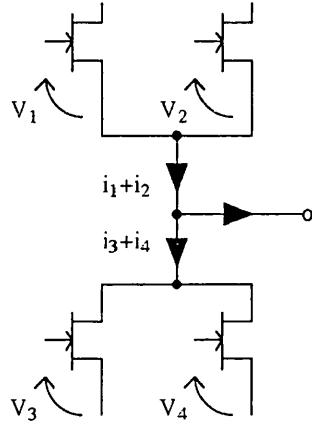

| 3.5.4    | Balanced Amplifier with Active Splitter/Combiner . . . . .                                               | 86         |

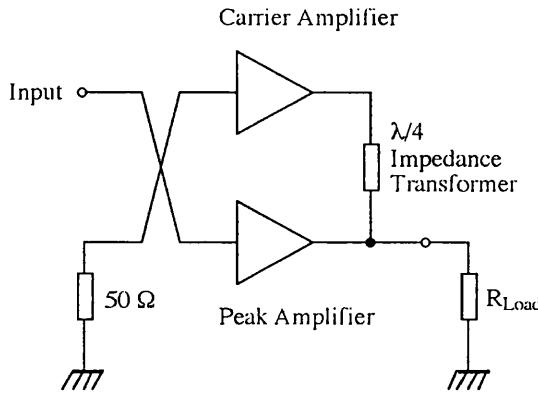

| 3.5.5    | Doherty Amplifier . . . . .                                                                              | 87         |

| 3.5.6    | Derivative Superposition . . . . .                                                                       | 88         |

| 3.6      | Comparison of Design Techniques for Nonlinear Applications . . . . .                                     | 92         |

| 3.6.1    | Balanced Amplifier with Passive Splitter/Combiner . . . . .                                              | 92         |

| 3.6.2    | Multi-tanh Technique . . . . .                                                                           | 93         |

| 3.6.3    | Translinear Technique . . . . .                                                                          | 93         |

| 3.6.4    | Balanced Amplifier with Active Splitter/Combiner . . . . .                                               | 94         |

| 3.6.5    | Derivative Superposition . . . . .                                                                       | 95         |

| 3.7      | Techniques for Power Amplifier Design . . . . .                                                          | 98         |

| 3.7.1    | Discussion of Some of the Amplifier Configurations . . . . .                                             | 98         |

| 3.7.2    | System Level Linearisation Techniques . . . . .                                                          | 100        |

| 3.7.3    | Application of Derivative Superposition to Power Amplifiers                                              | 103        |

| 3.8      | Discussion and Conclusions . . . . .                                                                     | 103        |

| <b>4</b> | <b>Measurement of Intermodulation Distortion of FETs</b>                                                 | <b>108</b> |

| 4.1      | General . . . . .                                                                                        | 108        |

| 4.2      | Problems in IMD Measurement . . . . .                                                                    | 108        |

| 4.2.1    | Residual Distortion . . . . .                                                                            | 108        |

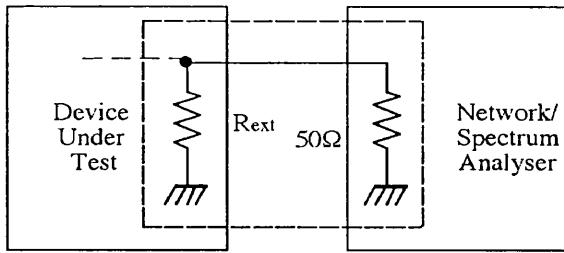

| 4.2.2    | High Impedance Probe . . . . .                                                                           | 110        |

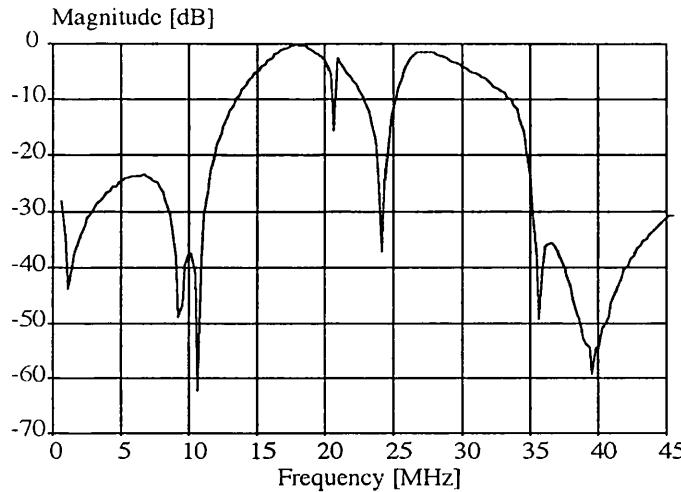

| 4.2.3    | RBW Setting Effects of Network/Spectrum Analyser . . . . .                                               | 111        |

| 4.3      | Ways of Improving IMD Measurement . . . . .                                                              | 111        |

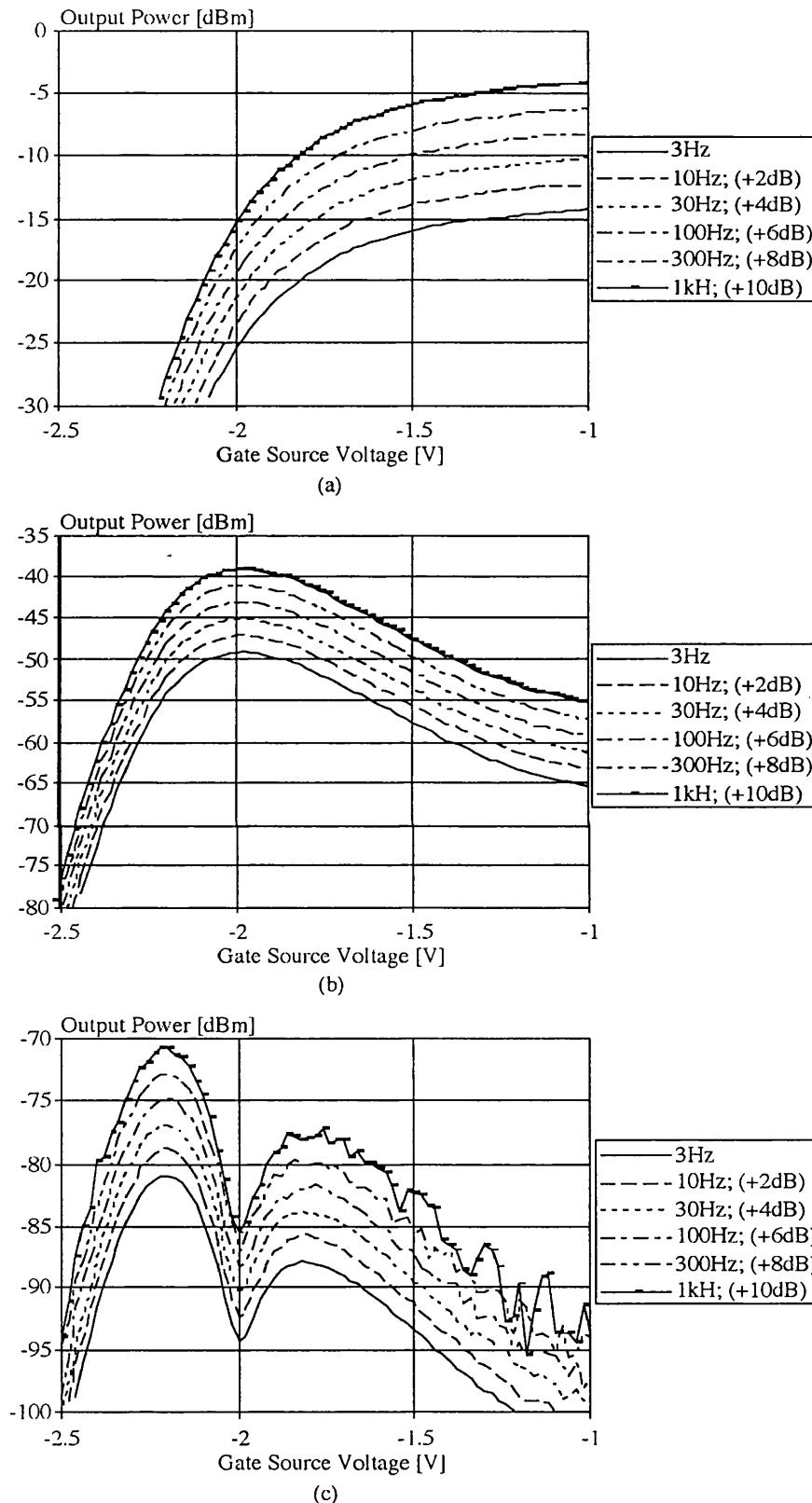

| 4.3.1    | New Load Resistance Configuration . . . . .                                                              | 111        |

| 4.3.2    | Comparison of Various Types of Load Resistance . . . . .                                                 | 114        |

| 4.3.3    | Improved On-wafer Distortion Measurement Set-up . . . . .                                                | 114        |

| 4.4      | High Frequency Measurement Set-up . . . . .                                                              | 116        |

| 4.4.1    | Schematic Diagram of the Measurement Set-up . . . . .                                                    | 116        |

|          |                                                                                                                  |            |

|----------|------------------------------------------------------------------------------------------------------------------|------------|

| 4.4.2    | Choice of Signal Generators Frequency and Residual Distortion . . . . .                                          | 116        |

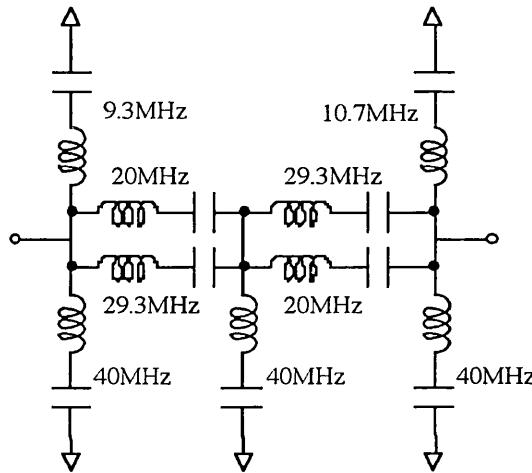

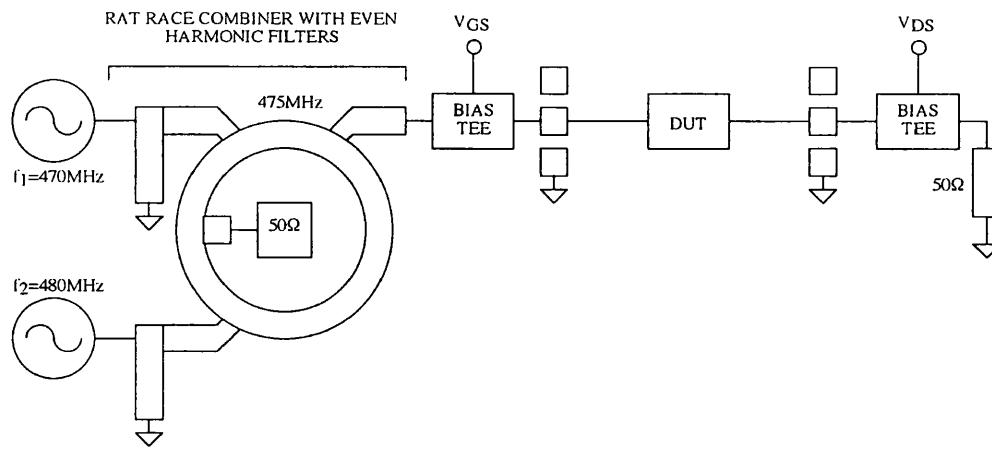

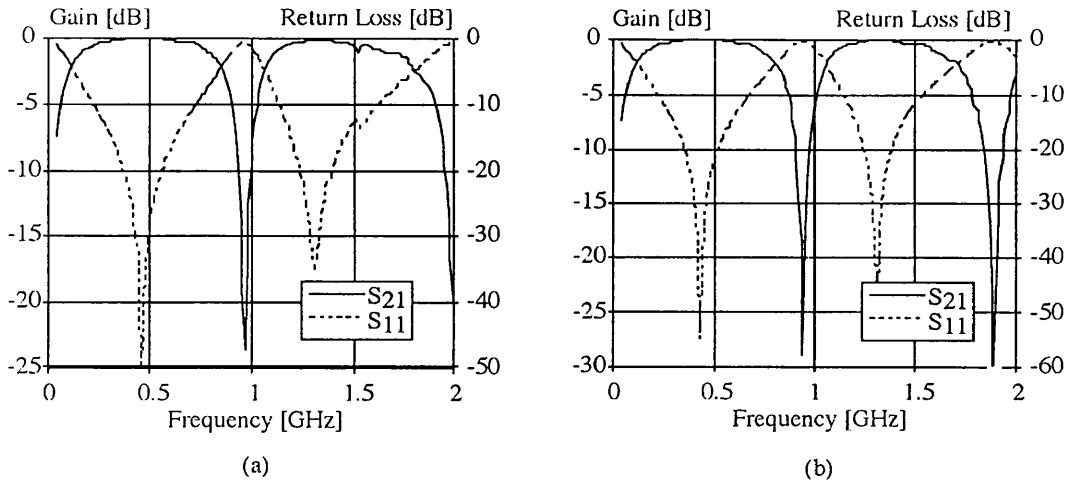

| 4.4.3    | Rat Race Design and Response . . . . .                                                                           | 117        |

| 4.4.4    | Stub Filters Design and Response . . . . .                                                                       | 118        |

| 4.5      | Summary . . . . .                                                                                                | 118        |

| <b>5</b> | <b>Study of the Nonlinear Behaviour of Typical FETs</b>                                                          | <b>121</b> |

| 5.1      | General . . . . .                                                                                                | 121        |

| 5.2      | Observations Using SPICE . . . . .                                                                               | 121        |

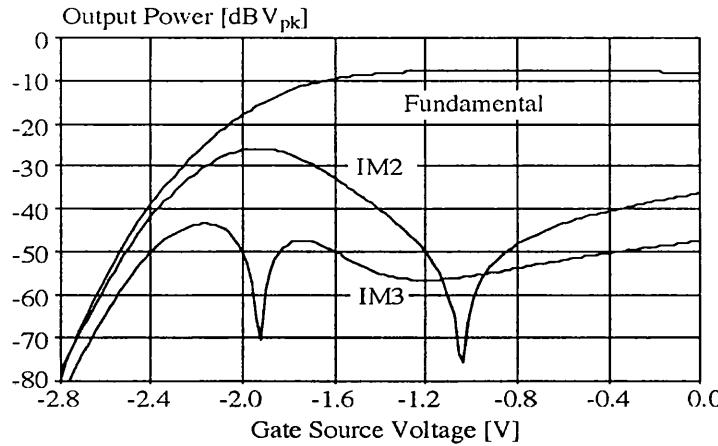

| 5.2.1    | Effect of Gate Bias on Distortion . . . . .                                                                      | 122        |

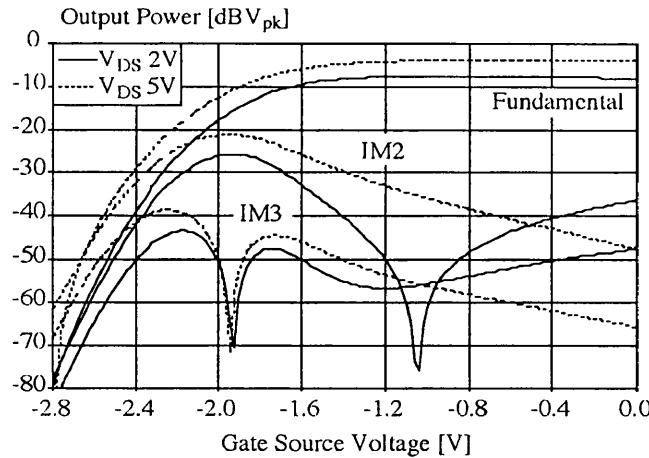

| 5.2.2    | Effect of Drain Bias on Distortion . . . . .                                                                     | 122        |

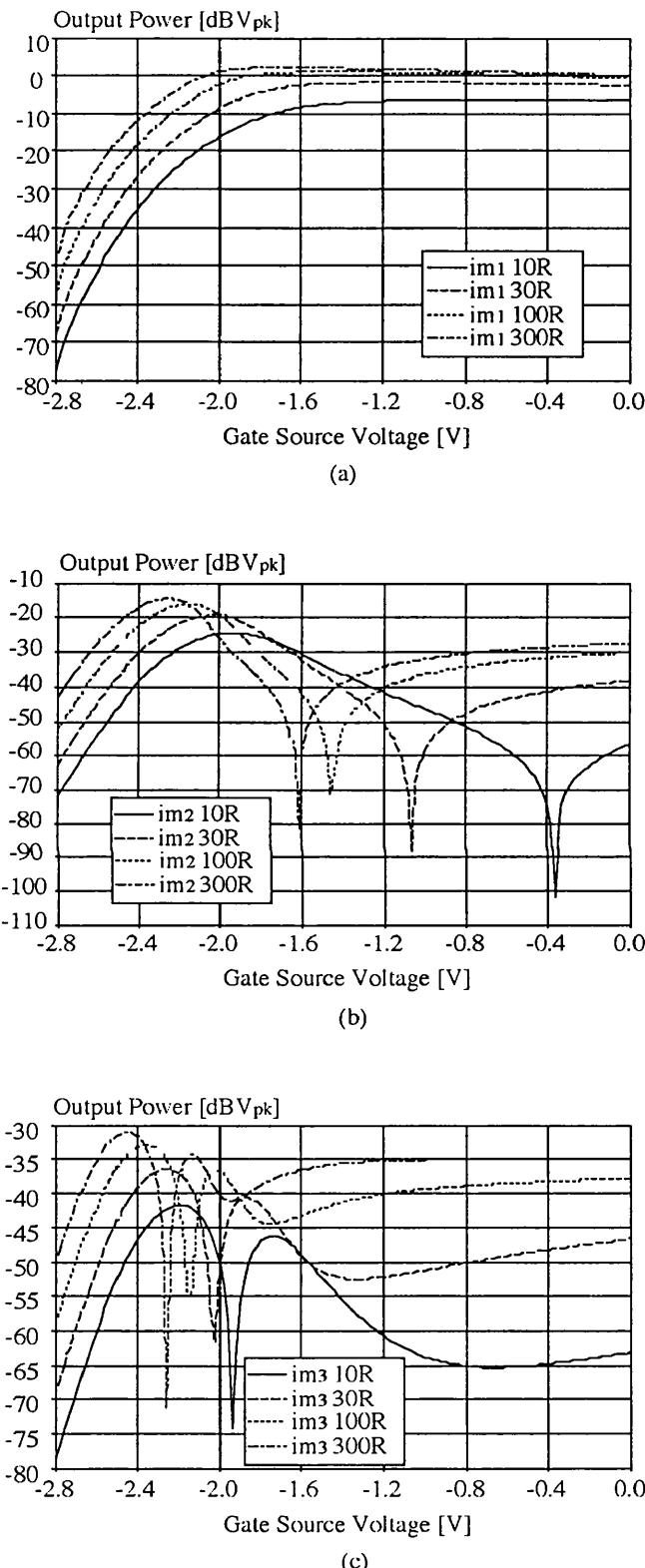

| 5.2.3    | Effect of Load Resistance on Distortion . . . . .                                                                | 123        |

| 5.2.4    | Effect of Input Signal Amplitude on Distortion . . . . .                                                         | 123        |

| 5.3      | CLY5 GaAs MESFET Measurements . . . . .                                                                          | 126        |

| 5.3.1    | Characterisation and Measurement . . . . .                                                                       | 126        |

| 5.3.2    | DC Measurements and Modelling . . . . .                                                                          | 131        |

| 5.4      | Measured Comparison of Some Devices . . . . .                                                                    | 131        |

| 5.5      | Visualisation Technique for Optimum Design . . . . .                                                             | 140        |

| 5.6      | Summary . . . . .                                                                                                | 143        |

| <b>6</b> | <b>An Example of Derivative Superposition : A Nonlinear Function Circuit for a Quasi-Optical Tracking System</b> | <b>145</b> |

| 6.1      | General . . . . .                                                                                                | 145        |

| 6.2      | Preliminary Considerations for the Design . . . . .                                                              | 146        |

| 6.2.1    | Gain Budget . . . . .                                                                                            | 146        |

| 6.2.2    | Power Amplifier Considerations . . . . .                                                                         | 148        |

| 6.2.3    | Proposed Electrical Specification of the Transceiver Cell . . . . .                                              | 149        |

| 6.3      | UoG MESFET Characterisation . . . . .                                                                            | 149        |

| 6.4      | Design of a 100 MHz Circuit . . . . .                                                                            | 150        |

| 6.4.1    | Design Strategy . . . . .                                                                                        | 151        |

| 6.4.2    | A Derivative Superposition Solution . . . . .                                                                    | 151        |

| 6.4.3    | Circuit Implementation . . . . .                                                                                 | 152        |

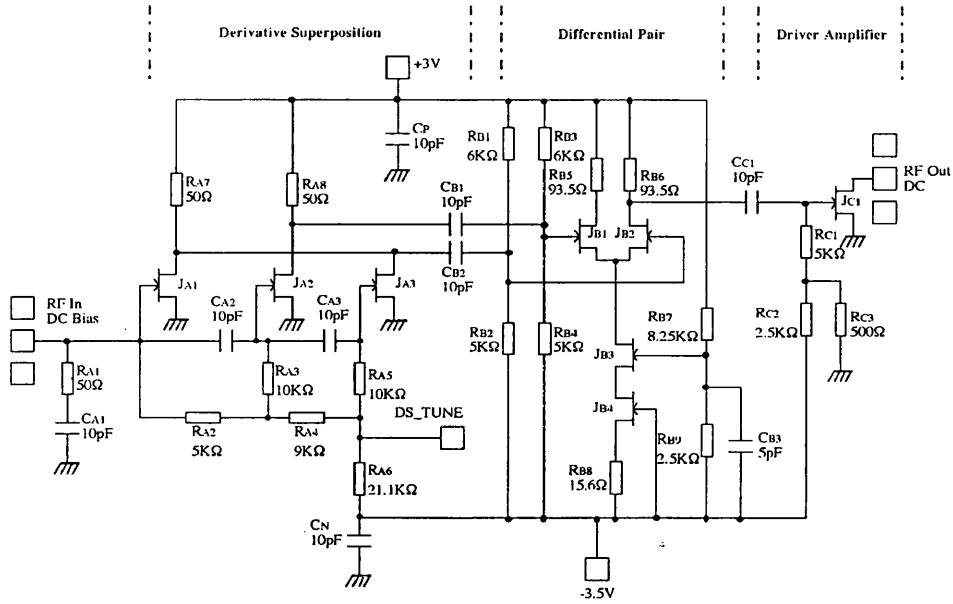

| 6.4.3.1  | Derivative Superposition Block . . . . .                                                                         | 153        |

| 6.4.3.2  | Differential Pair Block . . . . .                                                                                | 155        |

| 6.4.3.3  | Driver Amplifier Block . . . . .                                                                                 | 165        |

| 6.4.4    | MMIC Layout . . . . .                                                                                            | 166        |

| 6.5      | Summary . . . . .                                                                                                | 168        |

|                                                                                          |            |

|------------------------------------------------------------------------------------------|------------|

| <b>7 Low Distortion MMIC Power Amplifier Using Derivative Superposition</b>              | <b>170</b> |

| 7.1 General . . . . .                                                                    | 170        |

| 7.2 MMIC Design, Fabrication and Test . . . . .                                          | 171        |

| 7.2.1 MMT F20 Characterisation . . . . .                                                 | 171        |

| 7.2.1.1 DC TDFD Parker Skellern Model Extraction . . .                                   | 175        |

| 7.2.1.2 Parker Skellern Model Based on Pulsed I-V Measurements . . . . .                 | 175        |

| 7.2.2 Preliminary Amplifier Design . . . . .                                             | 176        |

| 7.2.3 Derivative Superposition Design Strategy . . . . .                                 | 177        |

| 7.2.4 MMIC Power Amplifier Design . . . . .                                              | 181        |

| 7.2.4.1 Detailed Design Using Super Deriv . . . . .                                      | 181        |

| 7.2.4.2 Spectral Regrowth Simulations . . . . .                                          | 183        |

| 7.2.5 MMIC Layout . . . . .                                                              | 187        |

| 7.2.6 Measured Performance . . . . .                                                     | 187        |

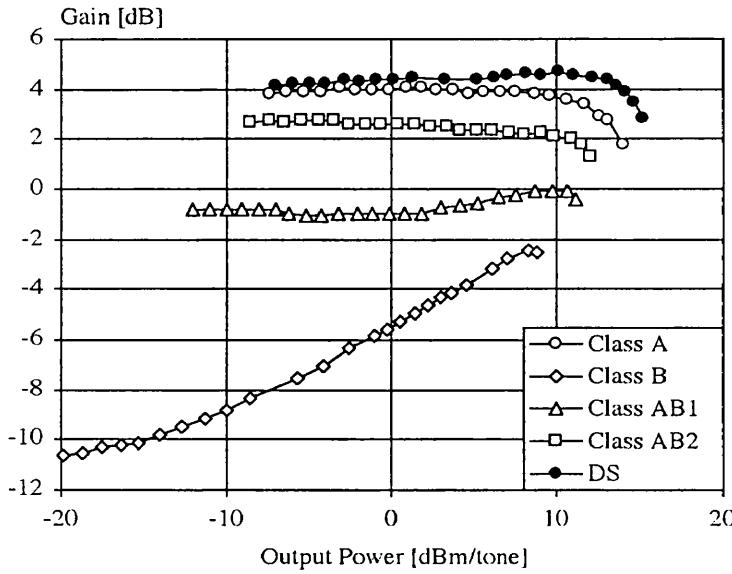

| 7.2.6.1 Gain . . . . .                                                                   | 188        |

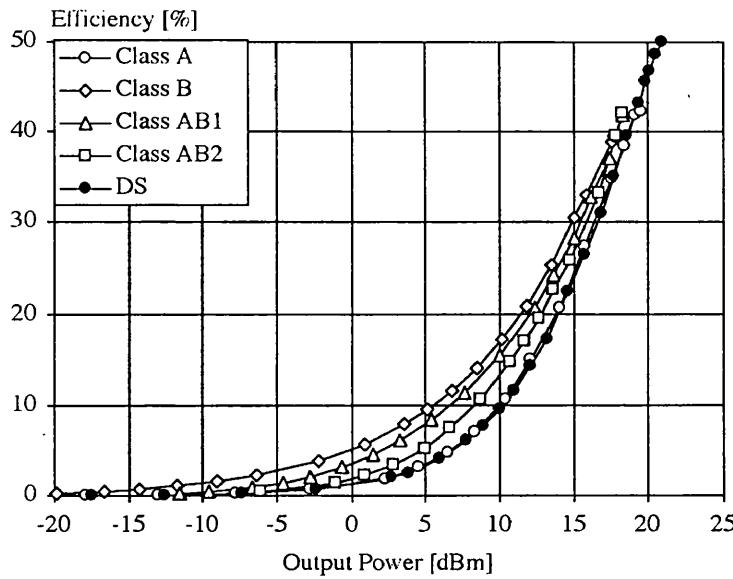

| 7.2.6.2 Single Tone Efficiency . . . . .                                                 | 188        |

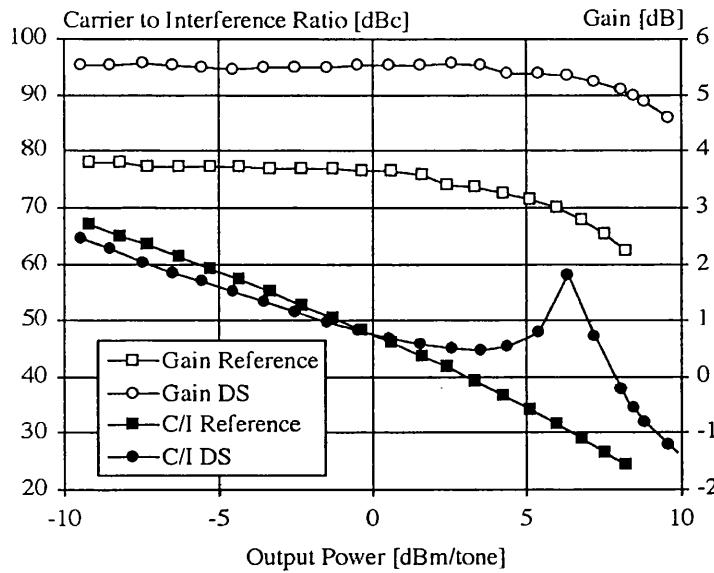

| 7.2.6.3 3rd Order Intermodulation Distortion . . . . .                                   | 188        |

| 7.2.6.4 Frequency Response . . . . .                                                     | 191        |

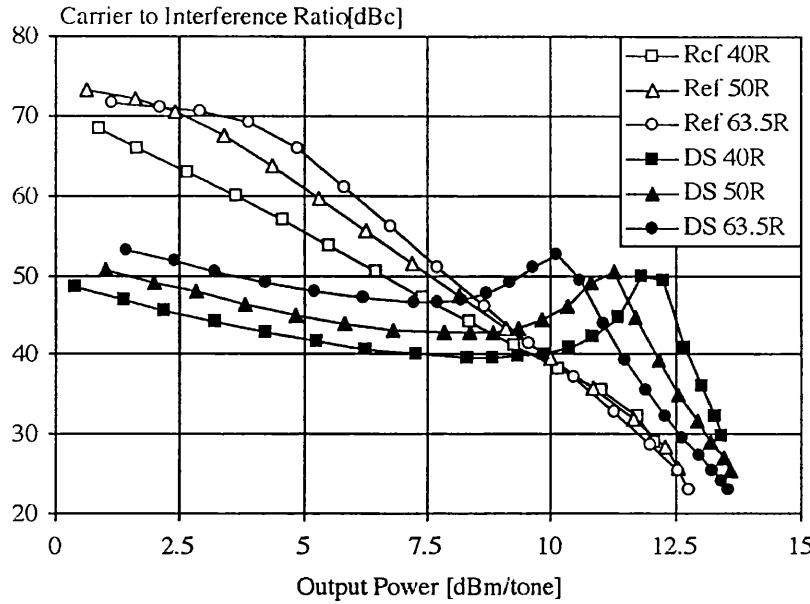

| 7.2.6.5 Effect of Load Resistance on Distortion . . . . .                                | 192        |

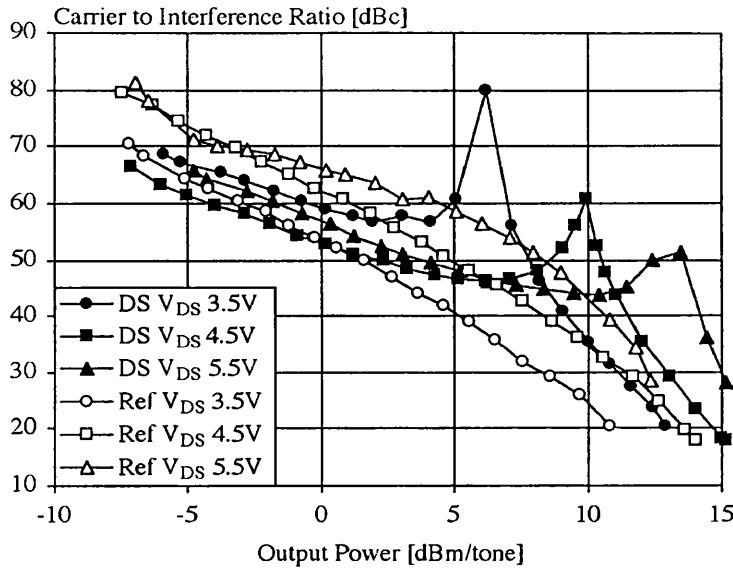

| 7.2.6.6 Effect of Drain Bias on Distortion . . . . .                                     | 193        |

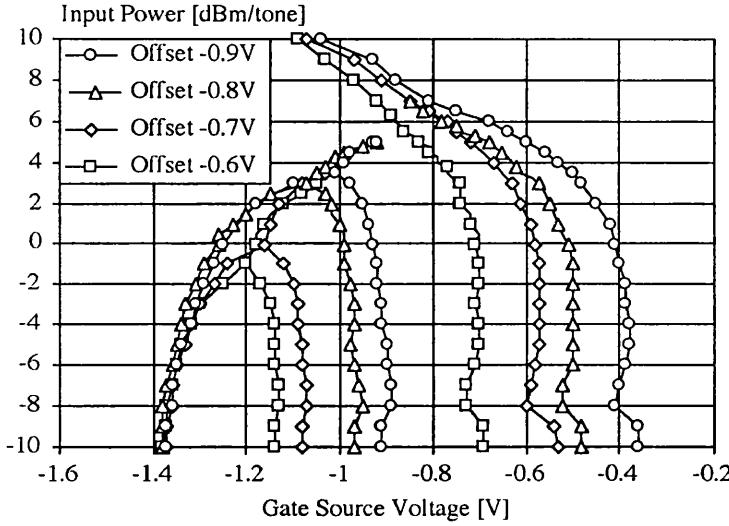

| 7.2.6.7 Effect of Offset Voltage on Distortion . . . . .                                 | 193        |

| 7.2.6.8 Comparison Indicating Potential Advantage . . .                                  | 195        |

| 7.2.6.9 Measured and Simulated C/I Comparison . . . .                                    | 202        |

| 7.2.6.10 Alternative Implementation Using UoG MONO-FAST MESFET Process . . . . .         | 203        |

| 7.2.6.11 Comparison of the Technologies Used . . . . .                                   | 204        |

| 7.3 Simulation of the Doherty Amplifier and the Composite Doherty-DS Structure . . . . . | 206        |

| 7.3.1 Design . . . . .                                                                   | 206        |

| 7.3.2 Simulated Performance . . . . .                                                    | 207        |

| 7.3.2.1 Carrier to Interference Ratio Response . . . . .                                 | 207        |

| 7.3.2.2 Efficiency . . . . .                                                             | 209        |

| 7.4 Summary . . . . .                                                                    | 210        |

| <b>8 MMIC Derivative Superposition Frequency Tripler</b>                                 | <b>214</b> |

| 8.1 MMIC Design, Fabrication and Test . . . . .                                          | 214        |

| 8.1.1 General . . . . .                                                                  | 214        |

|          |                                                                  |            |

|----------|------------------------------------------------------------------|------------|

| 8.1.2    | Design Strategy . . . . .                                        | 215        |

| 8.1.2.1  | Derivative Superposition Solution . . . . .                      | 215        |

| 8.1.2.2  | Differential Pair Section . . . . .                              | 218        |

| 8.1.2.3  | Amplifier Section . . . . .                                      | 219        |

| 8.1.3    | Simulated Performance of the Entire Design . . . . .             | 222        |

| 8.1.3.1  | Time Domain Response . . . . .                                   | 222        |

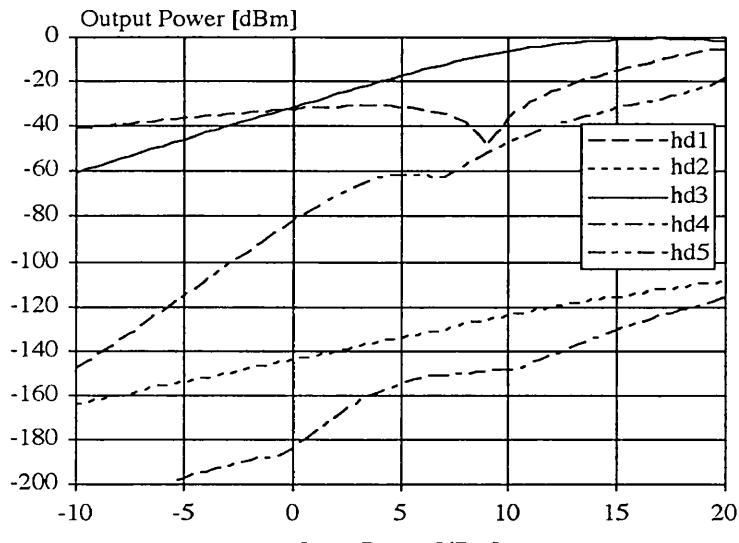

| 8.1.3.2  | Harmonic Distortion Variation with Input Signal .                | 222        |

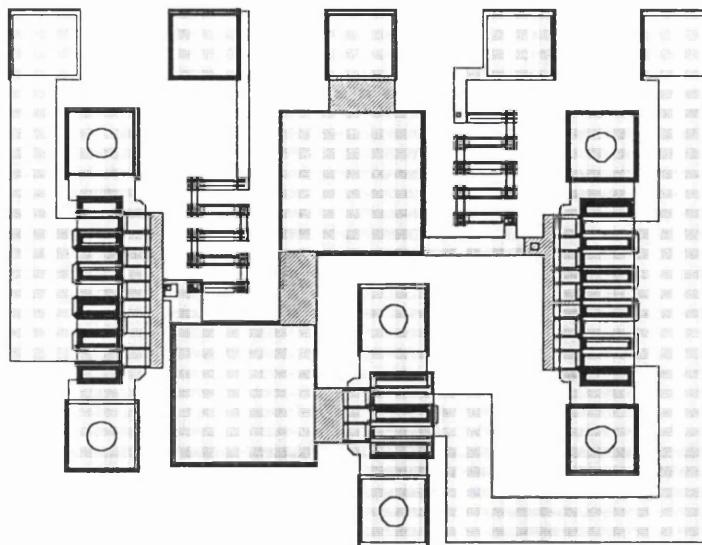

| 8.1.4    | MMIC Layout . . . . .                                            | 222        |

| 8.1.5    | Measured Performance . . . . .                                   | 225        |

| 8.2      | Incorporation of MMIC on a MIC for Microwave Frequency Operation | 228        |

| 8.2.1    | General . . . . .                                                | 228        |

| 8.2.2    | Design . . . . .                                                 | 228        |

| 8.2.3    | Simulated Performance . . . . .                                  | 229        |

| 8.2.3.1  | Time Domain Response . . . . .                                   | 229        |

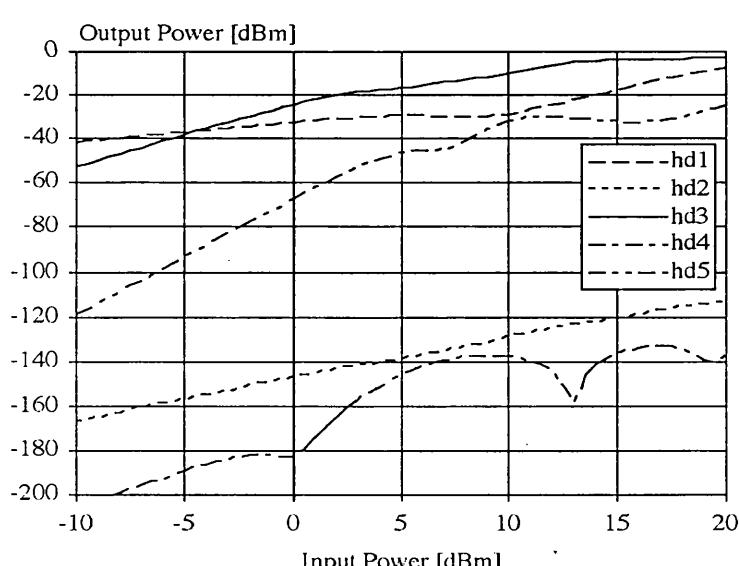

| 8.2.3.2  | Harmonic Distortion Variation with Input Signal .                | 229        |

| 8.2.4    | MMIC Layout Suitable for MIC Incorporation . . . . .             | 230        |

| 8.3      | Summary . . . . .                                                | 230        |

| <b>9</b> | <b>Conclusions and Further Work</b>                              | <b>234</b> |

| 9.1      | Conclusions . . . . .                                            | 234        |

| 9.2      | Future Work . . . . .                                            | 235        |

# List of Figures

|      |                                                                                                                                                                                                                 |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

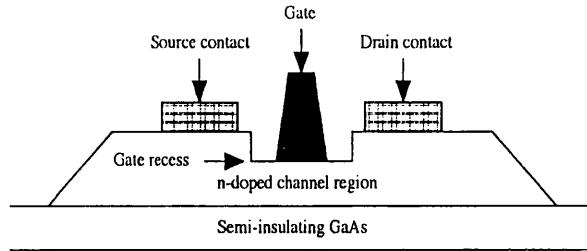

| 2.1  | The cross section of a typical GaAs MESFET. . . . .                                                                                                                                                             | 35 |

| 2.2  | Conventional HEMT structure. . . . .                                                                                                                                                                            | 37 |

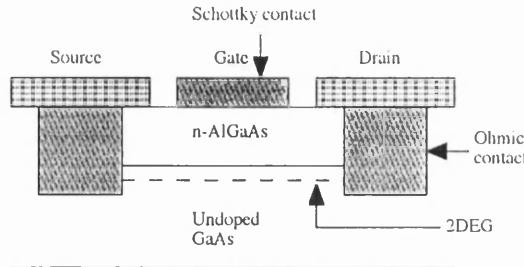

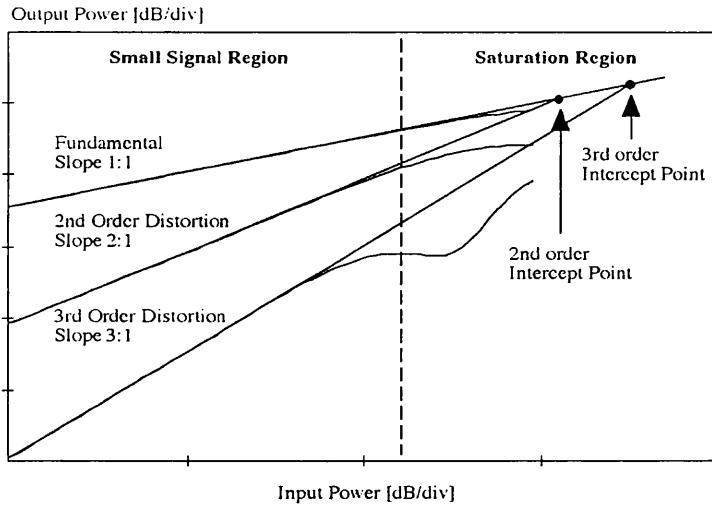

| 2.3  | Harmonic and intermodulation distortion products. (a) Two tone excitation signals at the input and (b) two tone excitation signals plus harmonic and intermodulation distortion products at the output. . . . . | 41 |

| 2.4  | Intercept points. . . . .                                                                                                                                                                                       | 42 |

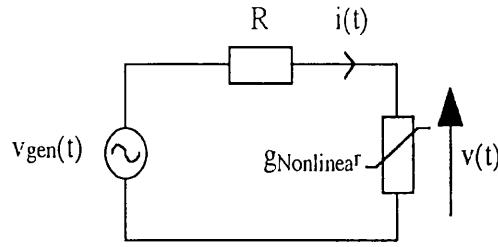

| 2.5  | Circuit with a nonlinear conductance. . . . .                                                                                                                                                                   | 44 |

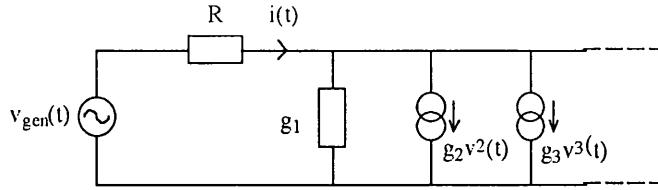

| 2.6  | The circuit of Figure 2.5 in which the nonlinear conductance has been replaced by a linear conductance and a set of current sources. . . . .                                                                    | 45 |

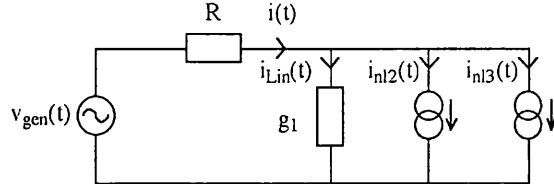

| 2.7  | The circuit of Figure 2.6 in which each current source represents a single order of mixing products. Note that the circuit represents the mixing products only up to the 3rd degree. . . . .                    | 45 |

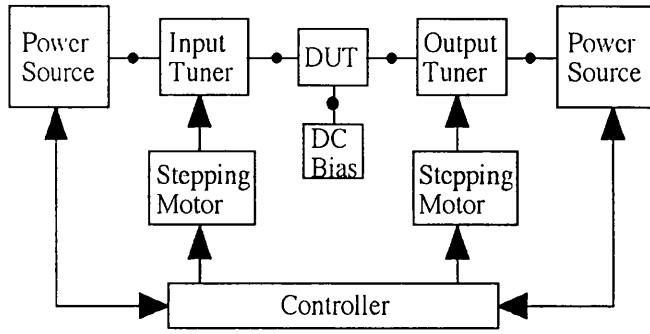

| 2.8  | The block diagram of a typical load pull measurement set-up. . . . .                                                                                                                                            | 46 |

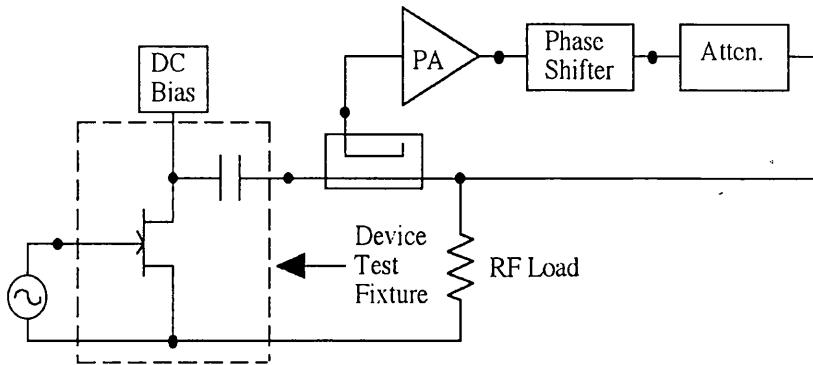

| 2.9  | Active load pull measurement set-up. . . . .                                                                                                                                                                    | 47 |

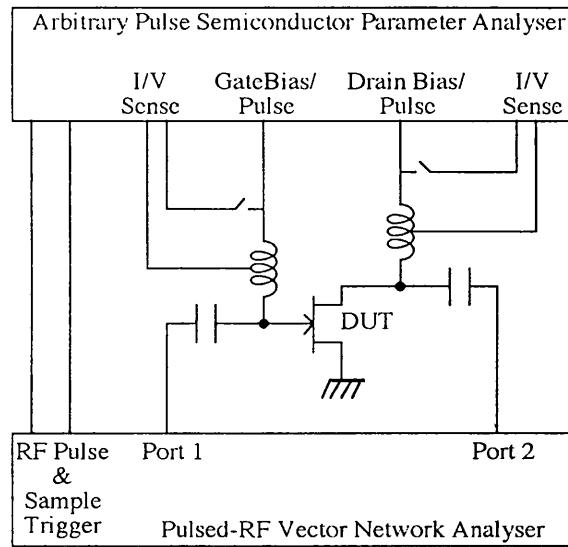

| 2.10 | Schematic diagram of a typical pulsed I-V measurement set-up. . . . .                                                                                                                                           | 48 |

| 2.11 | Maas RF harmonic distortion measurement set-up. . . . .                                                                                                                                                         | 49 |

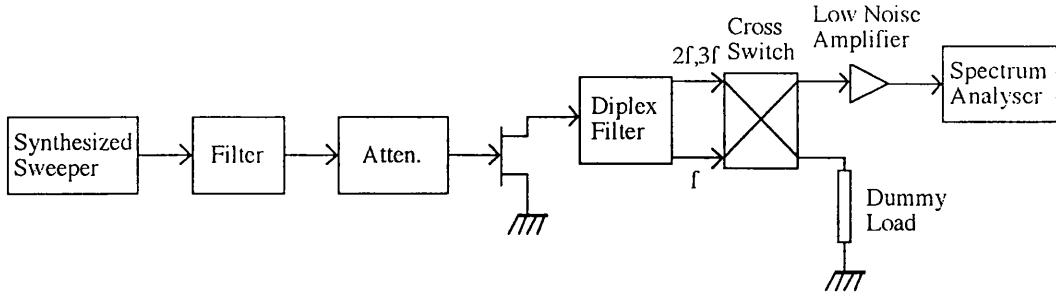

| 2.12 | Pedro and Perez distortion measurement set-up. . . . .                                                                                                                                                          | 49 |

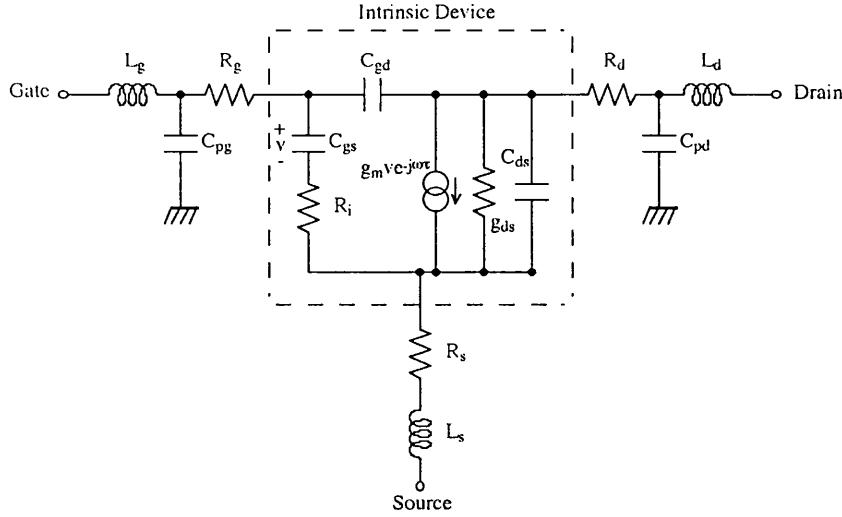

| 2.13 | Small signal equivalent circuit of a field effect transistor. . . . .                                                                                                                                           | 50 |

| 2.14 | Block diagram of the TDFD measurement set-up. . . . .                                                                                                                                                           | 51 |

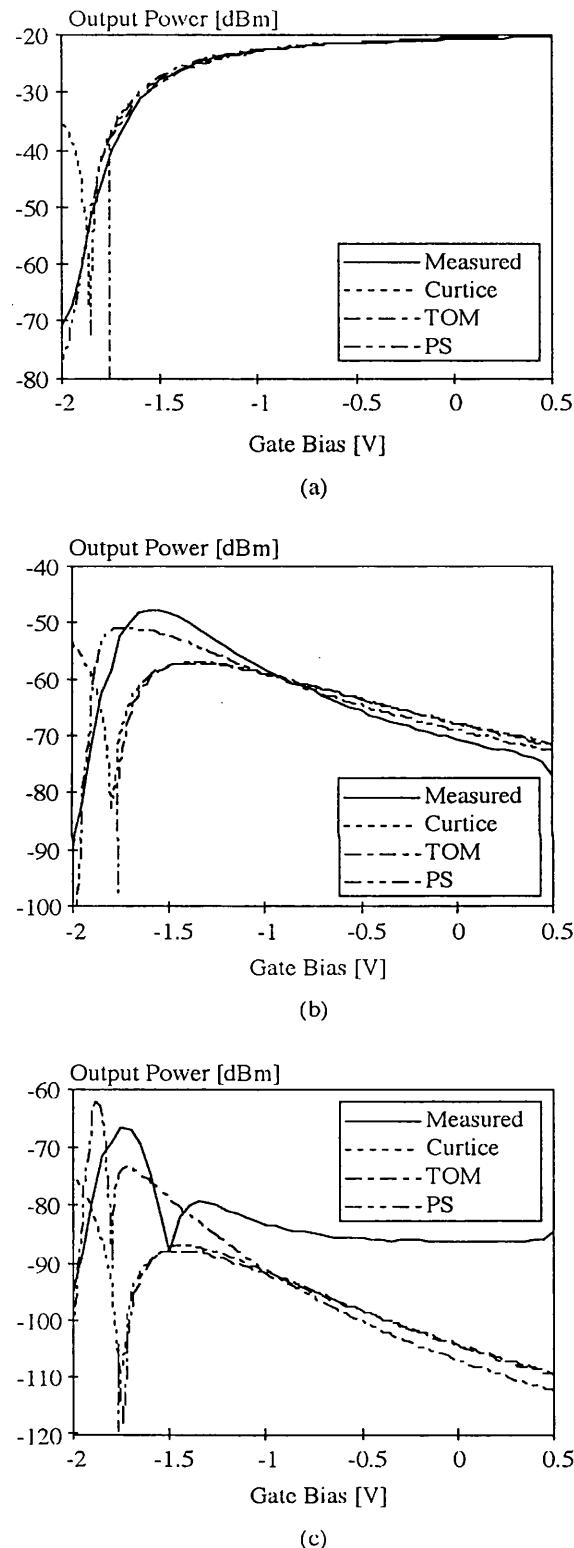

| 2.15 | Comparison of the prediction of distortion by various models; (a) Fundamental, (b) 2nd order distortion and (c) 3rd order distortion. . . . .                                                                   | 58 |

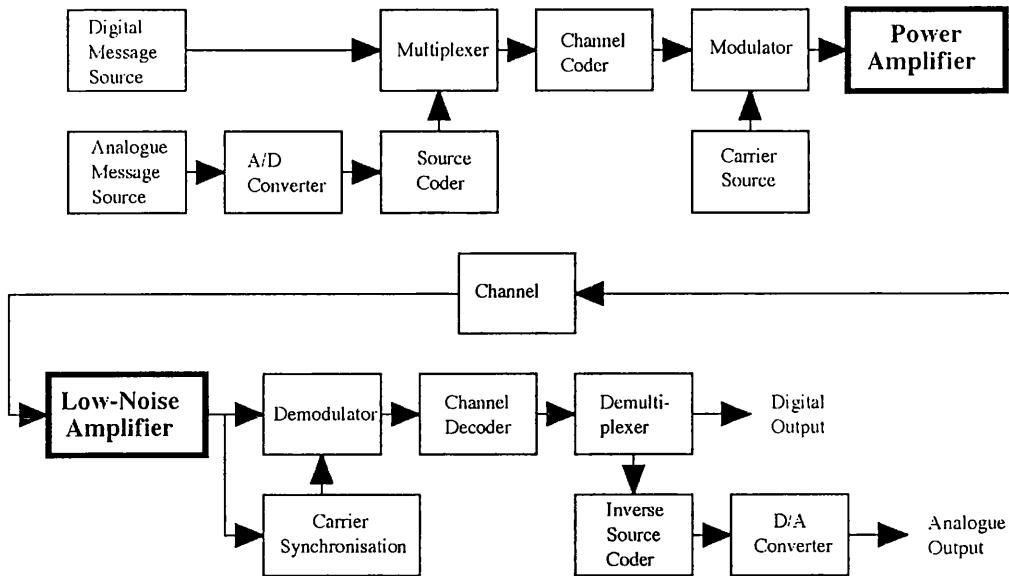

| 3.1  | Block diagram of a typical digital communication system. . . . .                                                                                                                                                | 67 |

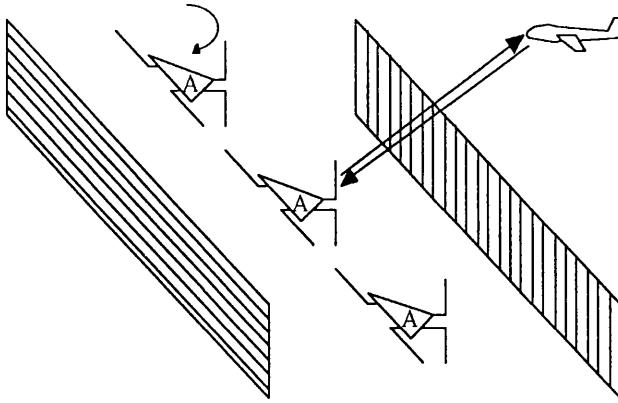

| 3.2  | Block diagram of the complete quasi-optical tracking system. . . . .                                                                                                                                            | 68 |

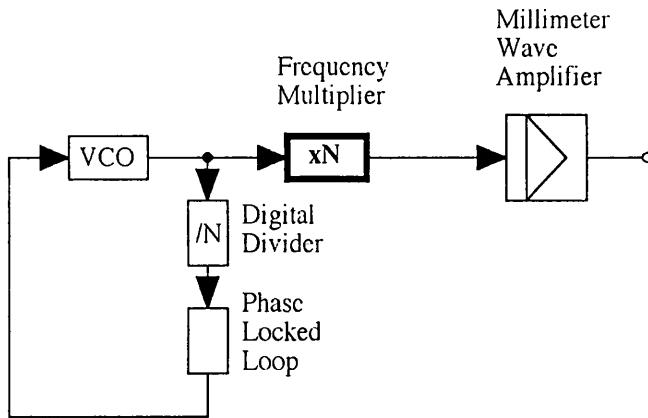

| 3.3  | Block diagram of a millimetre wave signal source indicating the usage of frequency multipliers. . . . .                                                                                                         | 69 |

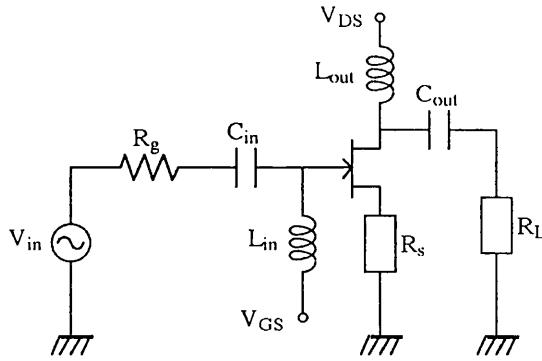

| 3.4  | Schematic diagram of a common source amplifier. . . . .                                                                                                                                                         | 70 |

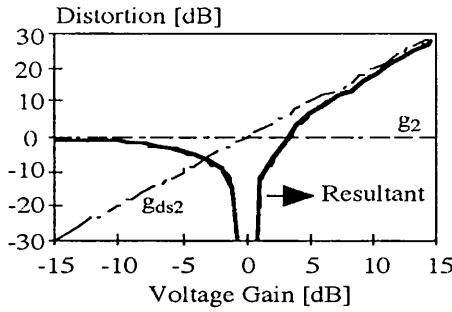

| 3.5  | Input referred distortion versus arbitrary voltage gain with two dominant terms. . . . .                                                                                                                        | 71 |

|      |                                                                                                                                                                                                                                                                     |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

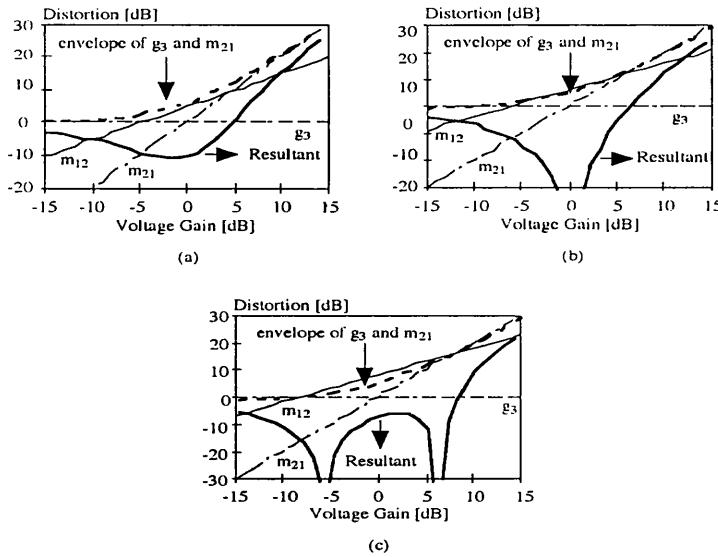

| 3.6  | Input referred distortion versus arbitrary voltage gain with three dominant terms, (a) $m_{12}$ close to the resultant, (b) $m_{12}$ touching the resultant and (c) $m_{12}$ crossing the resultant. . . . .                                                        | 72 |

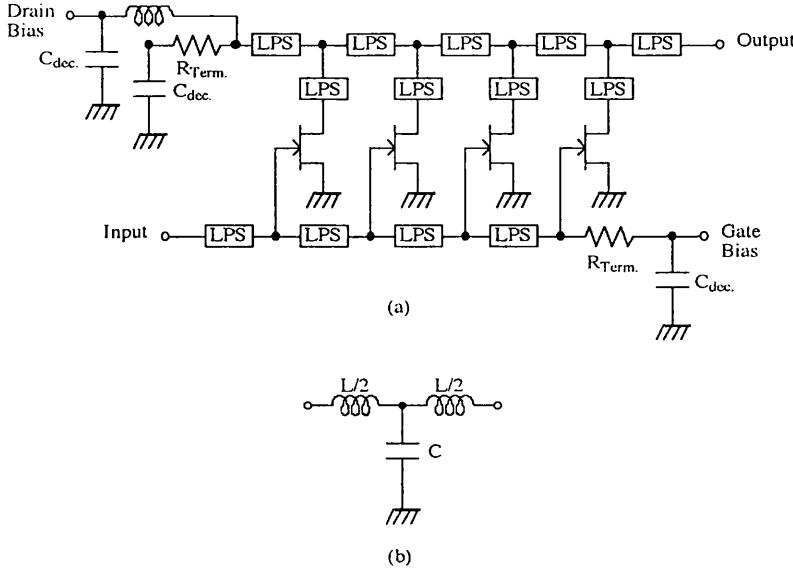

| 3.7  | The schematic diagrams of (a) a conventional distributed amplifier and (b) a single low pass T-section. . . . .                                                                                                                                                     | 74 |

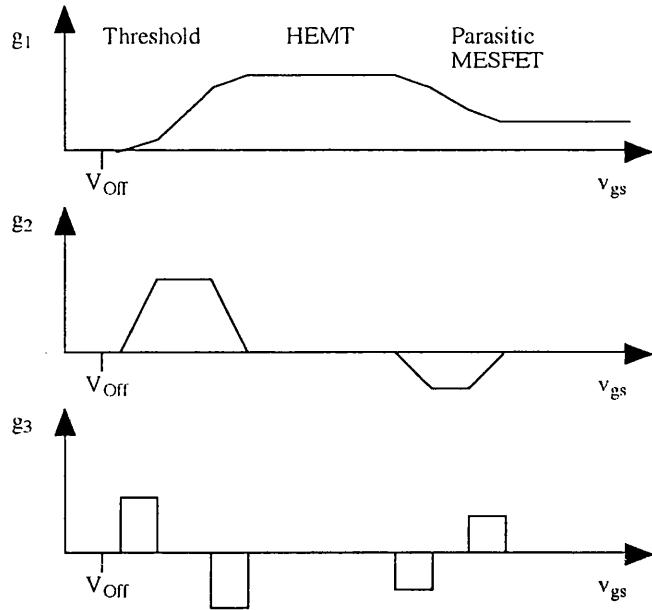

| 3.8  | Derivatives of an idealised HEMT. . . . .                                                                                                                                                                                                                           | 76 |

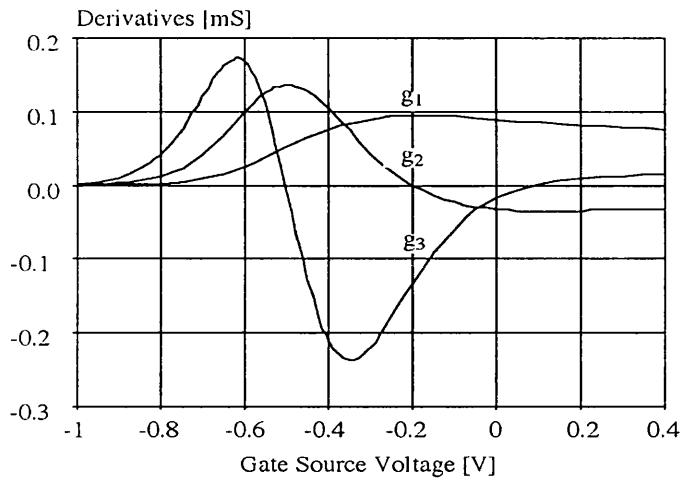

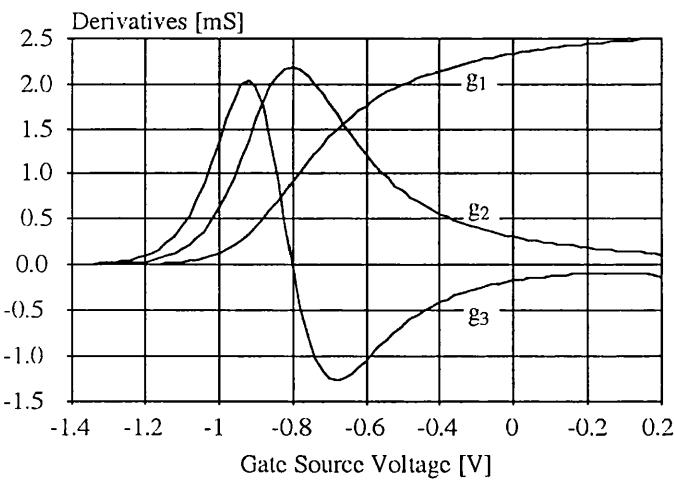

| 3.9  | The bias dependent derivatives for a real HEMT (NE32684). . . . .                                                                                                                                                                                                   | 77 |

| 3.10 | The bias dependent derivatives for a real MESFET (MGF1400). . . . .                                                                                                                                                                                                 | 77 |

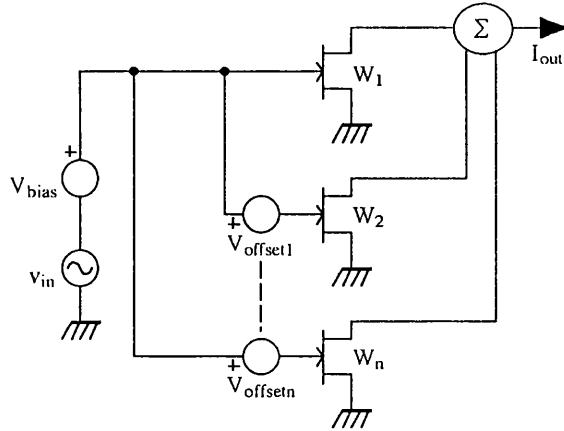

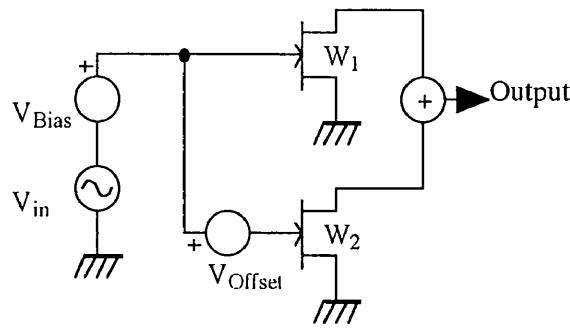

| 3.11 | The schematic diagram of the derivative superposition topology. . . . .                                                                                                                                                                                             | 78 |

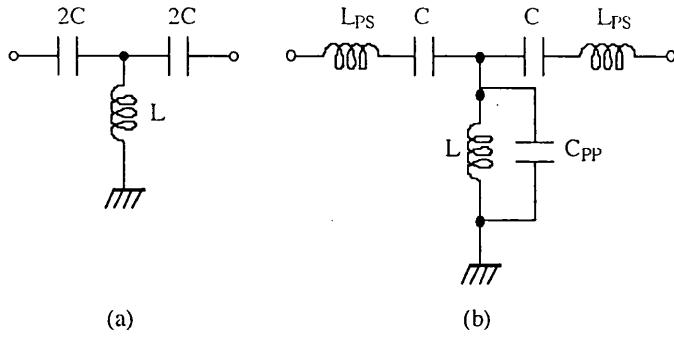

| 3.12 | Lumped-element high-pass transmission line sections. (a) Ideal model and (b) realistic model. . . . .                                                                                                                                                               | 79 |

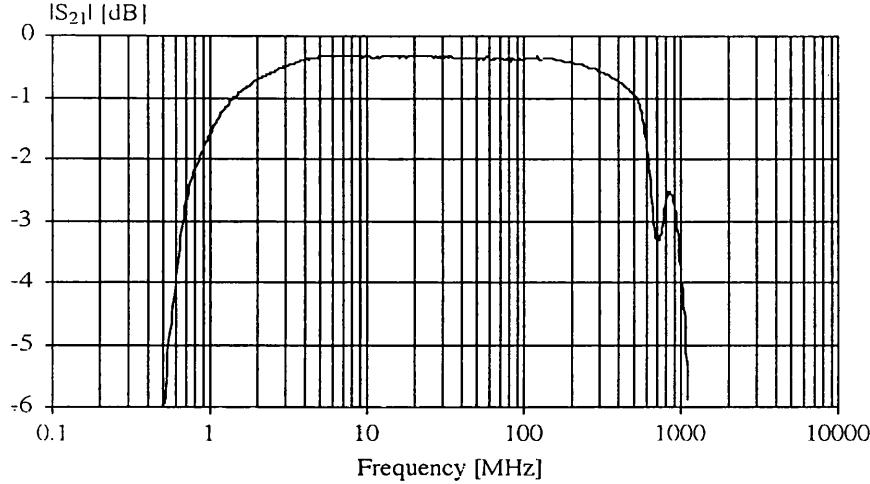

| 3.13 | Measured $ S_{21} $ of a five-section surface mount lumped-element high-pass transmission line. . . . .                                                                                                                                                             | 80 |

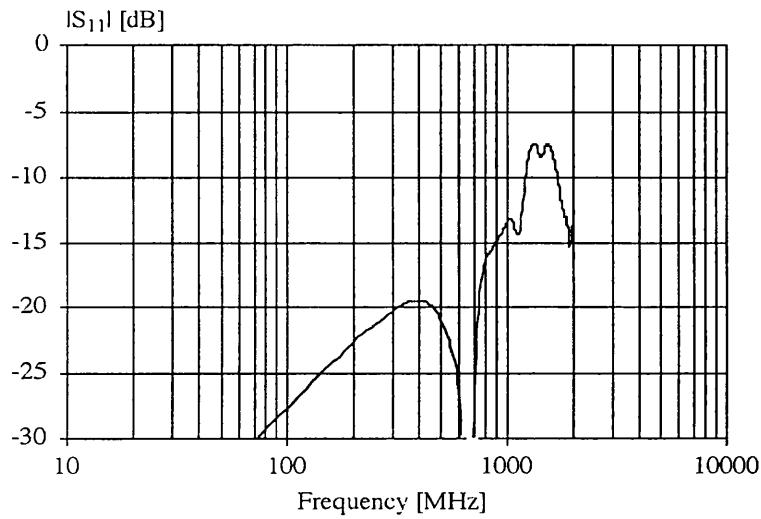

| 3.14 | Measured $ S_{11} $ of a five-section surface mount lumped-element high-pass transmission line. . . . .                                                                                                                                                             | 81 |

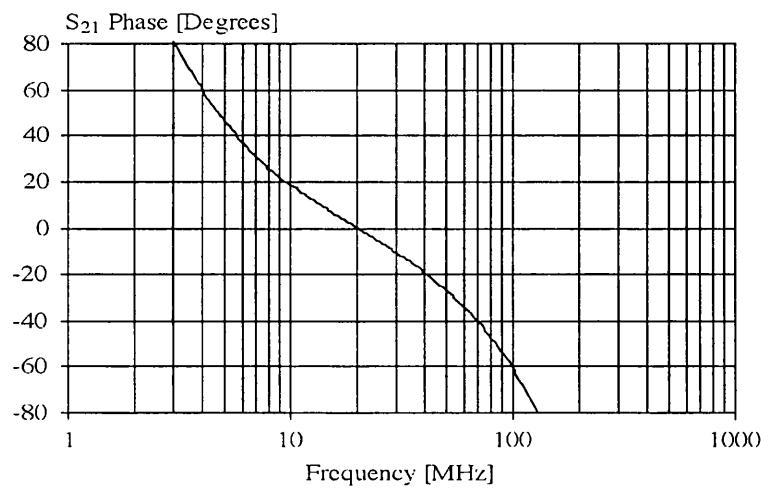

| 3.15 | Measured phase of $S_{21}$ of a five-section surface mount lumped-element high-pass transmission line. . . . .                                                                                                                                                      | 81 |

| 3.16 | Schematic diagram of a balanced structure suitable for linear applications. . . . .                                                                                                                                                                                 | 82 |

| 3.17 | Schematic diagram of a single BJT differential pair. . . . .                                                                                                                                                                                                        | 84 |

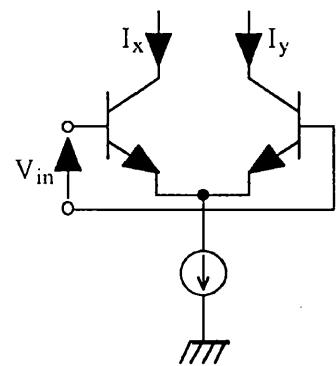

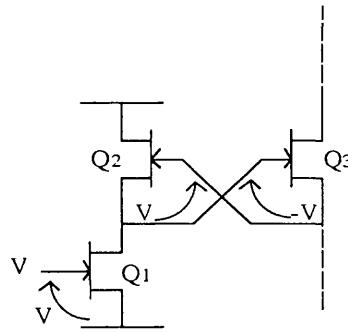

| 3.18 | The multi-tanh doublet. . . . .                                                                                                                                                                                                                                     | 84 |

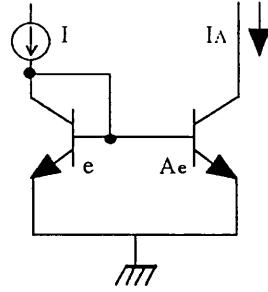

| 3.19 | Current mirror, an example of translinear circuit. . . . .                                                                                                                                                                                                          | 86 |

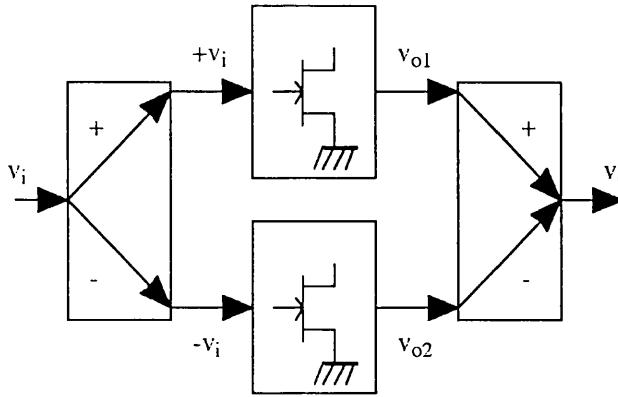

| 3.20 | The push-pull architecture suitable for combiner realisation. . . . .                                                                                                                                                                                               | 86 |

| 3.21 | An inverting voltage floatation building block. . . . .                                                                                                                                                                                                             | 87 |

| 3.22 | Doherty amplifier topology. . . . .                                                                                                                                                                                                                                 | 88 |

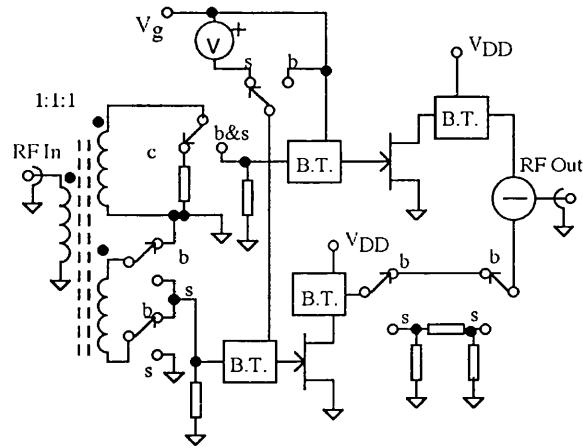

| 3.23 | Schematic of the Linear Law Demonstrator Board. The board allows the comparison of the Linear Law design, a single common source FET and a balanced FET amplifier. The switch positions are denoted by balanced (b), common source (c) and synthesised (s). . . . . | 89 |

| 3.24 | Schematic circuit diagram suitable for a gain stage with desired distortion characteristics fixed by the derivative superposition method. . . . .                                                                                                                   | 89 |

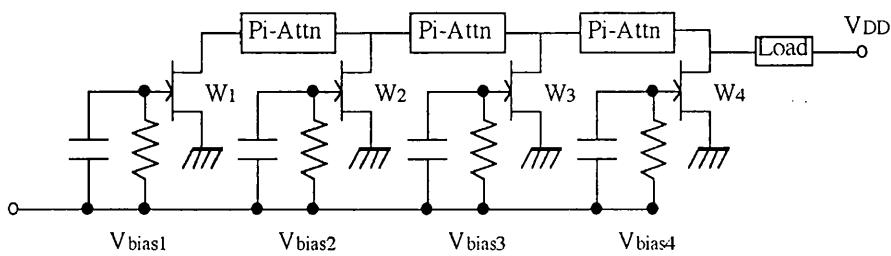

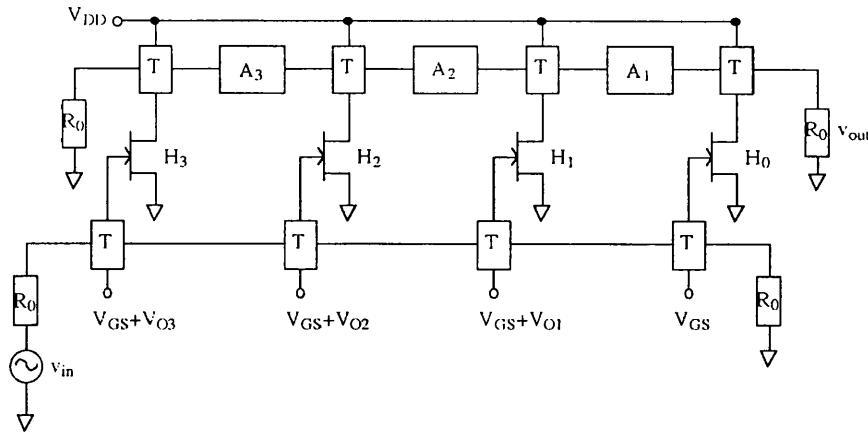

| 3.25 | Schematic diagram of a DS amplifier. T's are the high-pass transmission line sections and A's are the pi-section attenuators. Devices are NE42484C HEMTs. . . . .                                                                                                   | 90 |

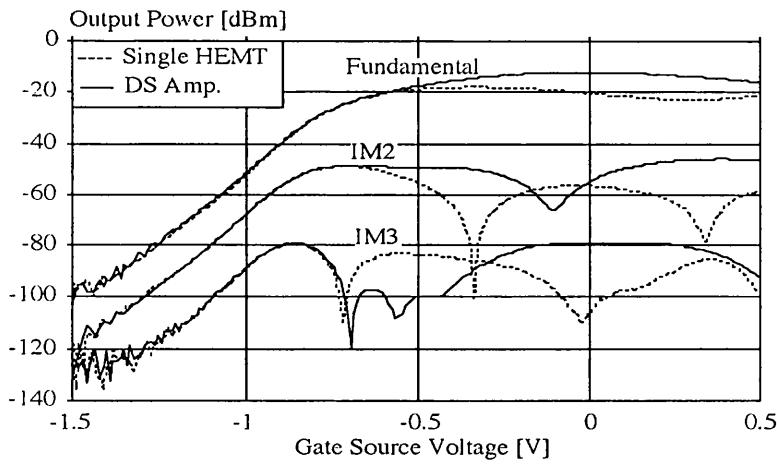

| 3.26 | Comparison of the intermodulation distortion versus gate bias for both a single HEMT and the derivative superposition amplifier. . . . .                                                                                                                            | 91 |

|                                                                                                                                                                                                                                                                 |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

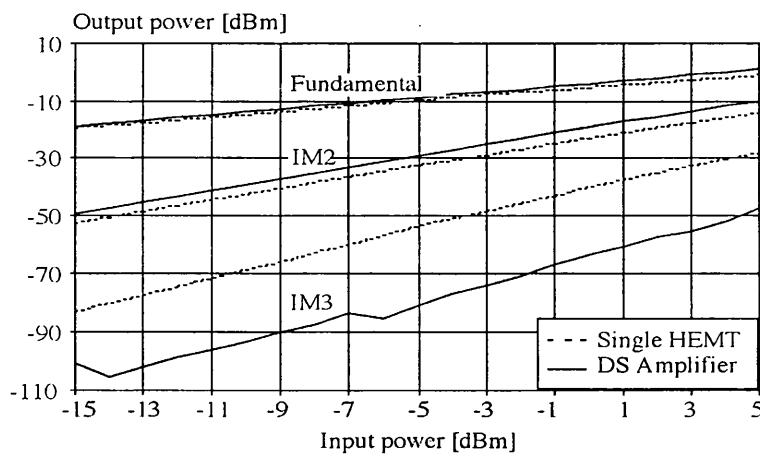

| 3.27 Comparison of the intermodulation distortion versus input power for both a single HEMT and the derivative superposition amplifier; $V_{GS} = -0.55V$ . . . . .                                                                                             | 91  |

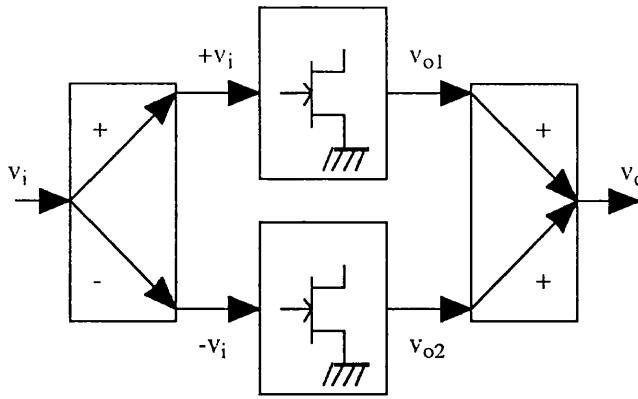

| 3.28 Schematic diagram of a balanced structure suitable for nonlinear applications. . . . .                                                                                                                                                                     | 92  |

| 3.29 The translinear principle; a diode bridge loop. . . . .                                                                                                                                                                                                    | 93  |

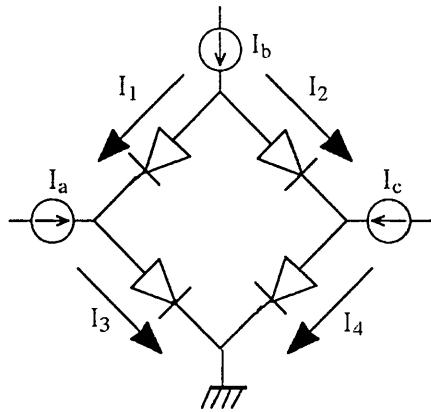

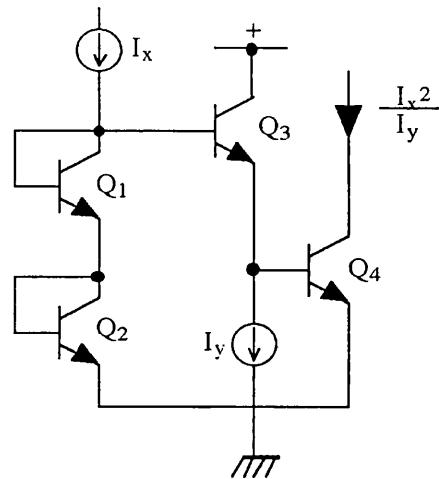

| 3.30 A simple one-quadrant translinear squarer. . . . .                                                                                                                                                                                                         | 94  |

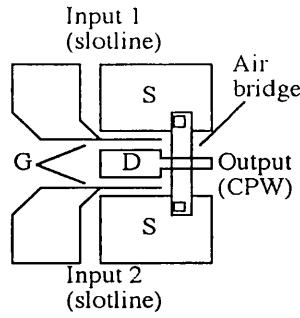

| 3.31 Realisation of an active in-phase power combiner (referred to as line unified or LU-FETs). . . . .                                                                                                                                                         | 95  |

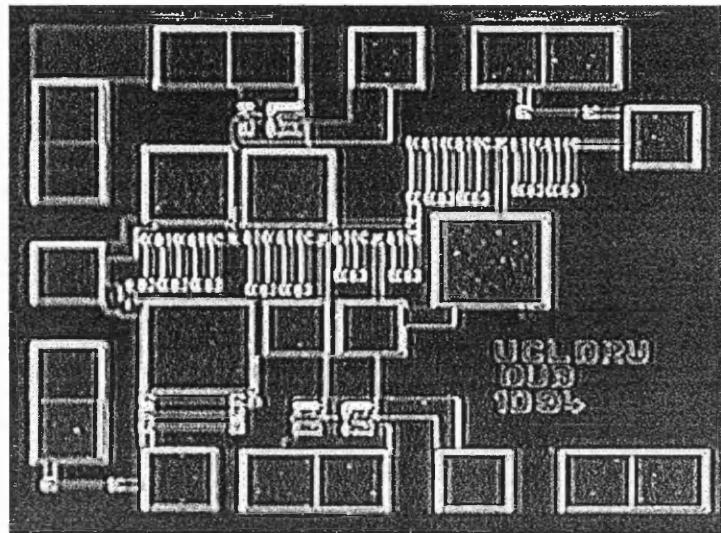

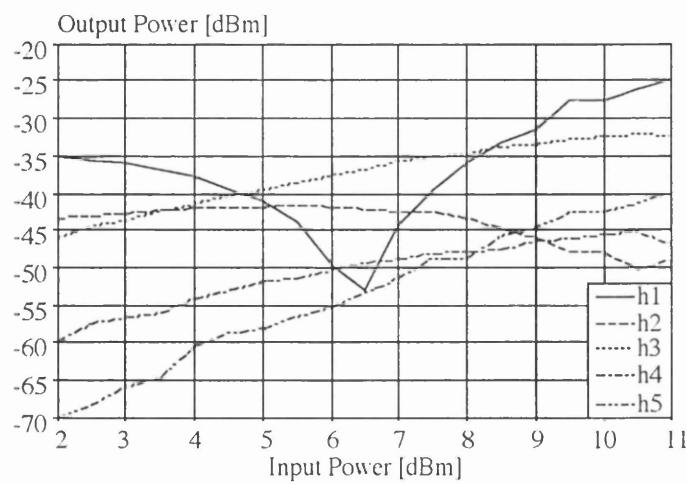

| 3.32 Photograph of the MMIC DS frequency doubler. . . . .                                                                                                                                                                                                       | 96  |

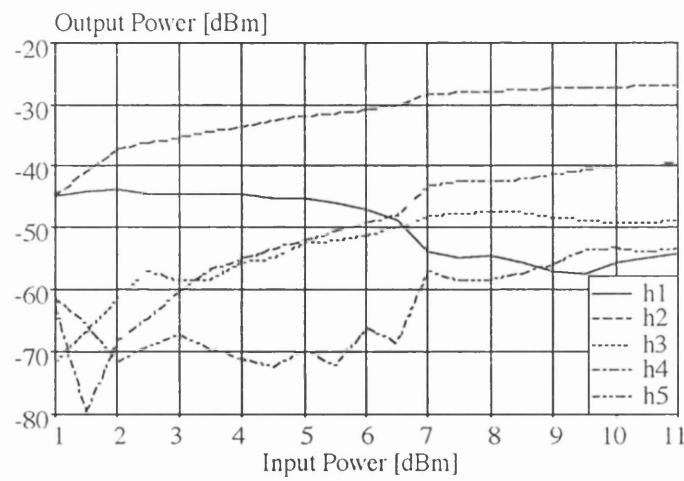

| 3.33 Measured performance of the derivative superposition frequency doubler. . . . .                                                                                                                                                                            | 96  |

| 3.34 Photograph of the MMIC DS frequency tripler. . . . .                                                                                                                                                                                                       | 97  |

| 3.35 Measured performance of the derivative superposition frequency tripler. . . . .                                                                                                                                                                            | 97  |

| 3.36 Possible bias points for class A, B and AB amplifiers. . . . .                                                                                                                                                                                             | 99  |

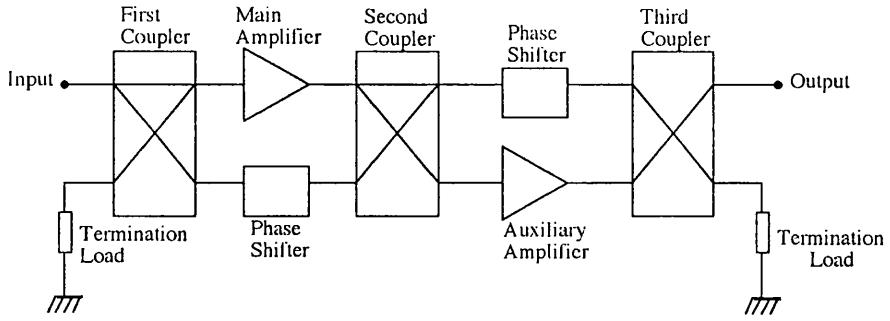

| 3.37 Schematic diagram of the feedforward linearisation technique. . . .                                                                                                                                                                                        | 101 |

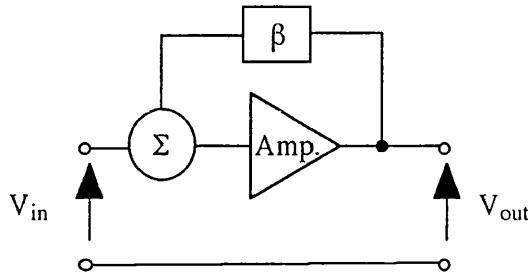

| 3.38 Schematic diagram of the feedback linearisation technique. . . .                                                                                                                                                                                           | 101 |

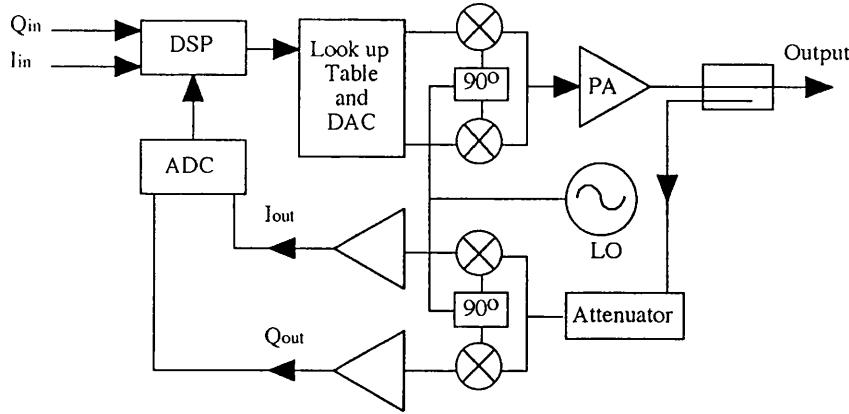

| 3.39 Adaptive digital predistortion system. . . . .                                                                                                                                                                                                             | 102 |

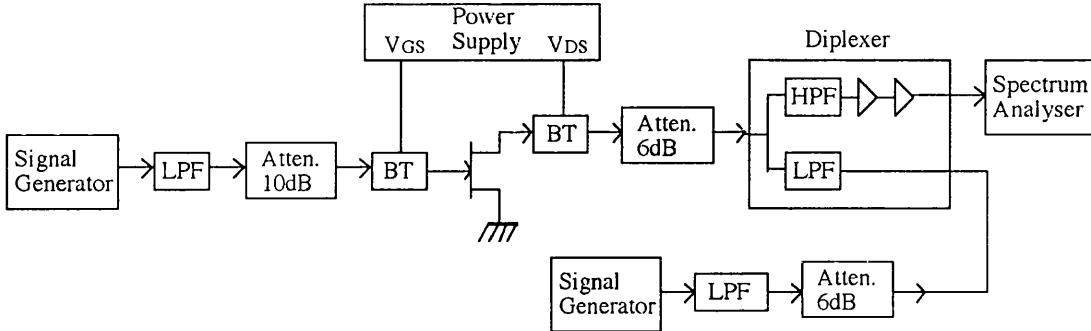

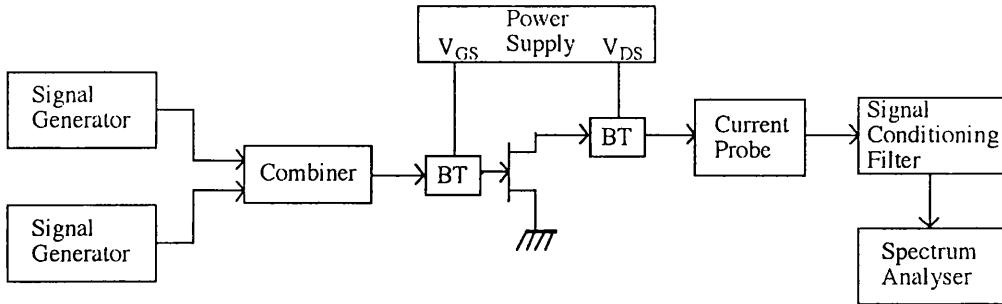

| 4.1 TDFD intermodulation distortion measurement set-up. . . . .                                                                                                                                                                                                 | 109 |

| 4.2 Schematic diagram of the scrubbing filter. . . . .                                                                                                                                                                                                          | 109 |

| 4.3 Measured response of the scrubbing filter. . . . .                                                                                                                                                                                                          | 110 |

| 4.4 The effect of the resolution bandwidth of the network/spectrum analyser on distortion for a GaAs MESFET; (a) Fundamental, (b) IMD2 and (c) IMD3. . . . .                                                                                                    | 112 |

| 4.5 Load resistance configuration for desired loads less than $50 \Omega$ . . . .                                                                                                                                                                               | 113 |

| 4.6 Load resistance configuration for desired loads more than $50 \Omega$ . .                                                                                                                                                                                   | 113 |

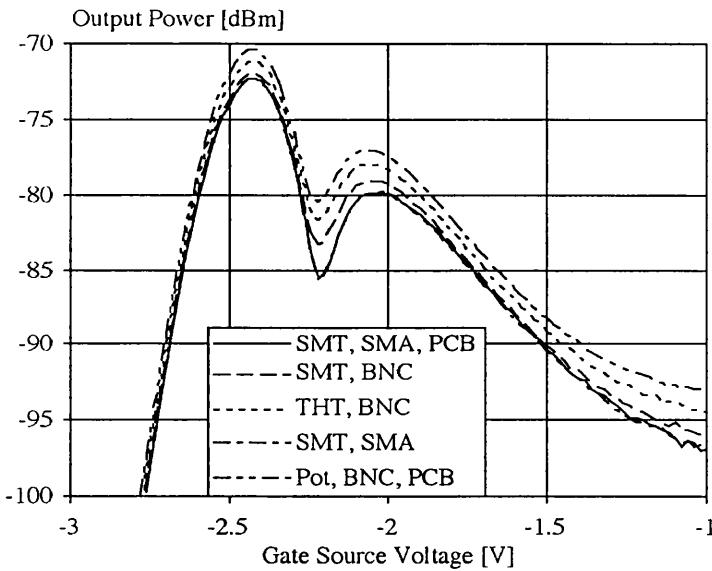

| 4.7 Comparison of the measured IMD3 for a CLY5 GaAs MESFET for various load resistance configurations. . . . .                                                                                                                                                  | 114 |

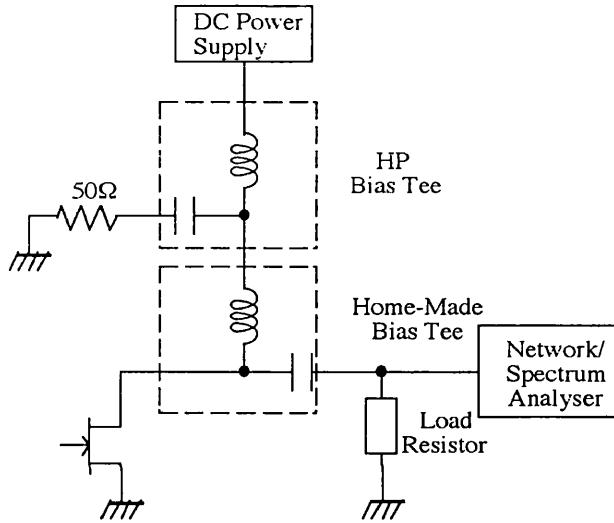

| 4.8 Schematic diagram of the improved bias tees arrangement. . . . .                                                                                                                                                                                            | 115 |

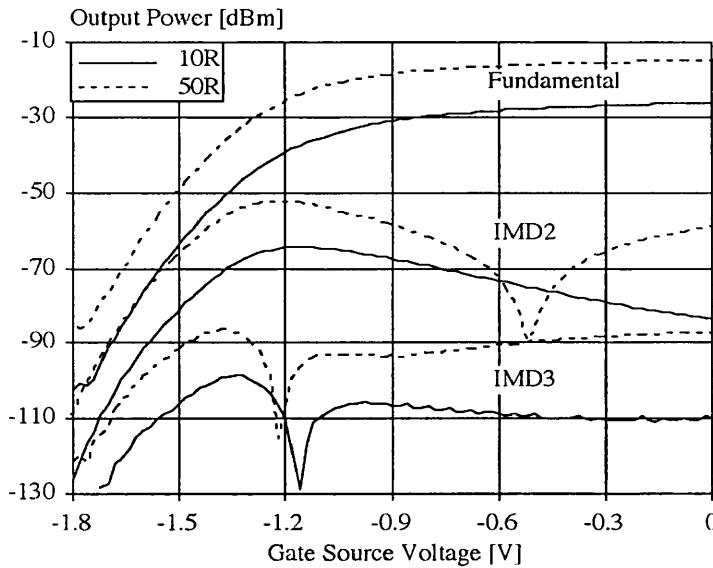

| 4.9 Measured on-wafer distortion results with the improved on-wafer measurement test set-up. Device measured is a $6 \times 100 \mu\text{m}$ F20 GaAs MESFET with a load resistance of $10 \Omega$ and $50 \Omega$ ; the input signal level is -15 dBm. . . . . | 116 |

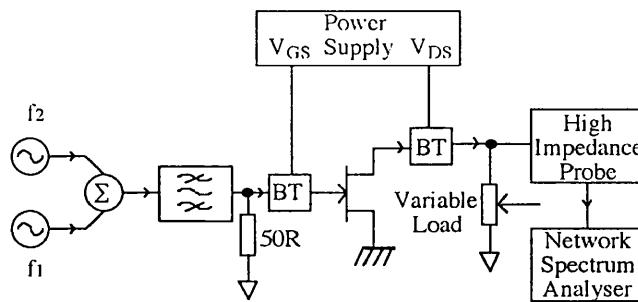

| 4.10 Schematic diagram of the high frequency measurement set-up. . . .                                                                                                                                                                                          | 117 |

| 4.11 Measured responses of the short circuited stubs; (a) at 470 MHz and (b) at 480 MHz. . . . .                                                                                                                                                                | 119 |

|      |                                                                                                                                                                                                              |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

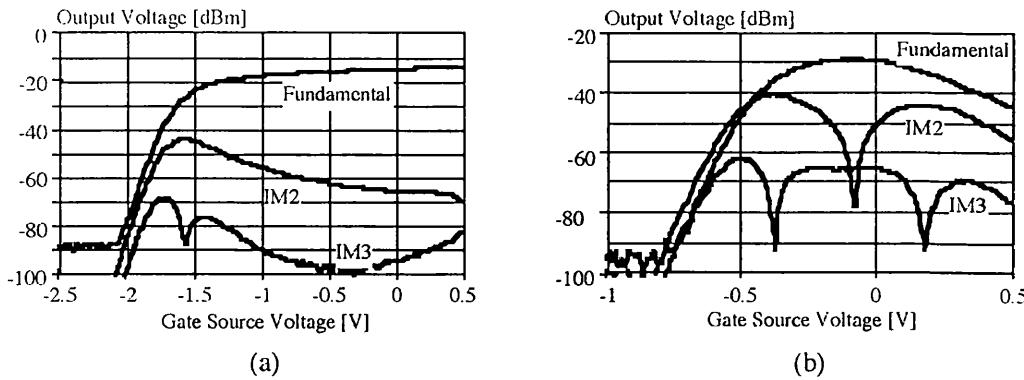

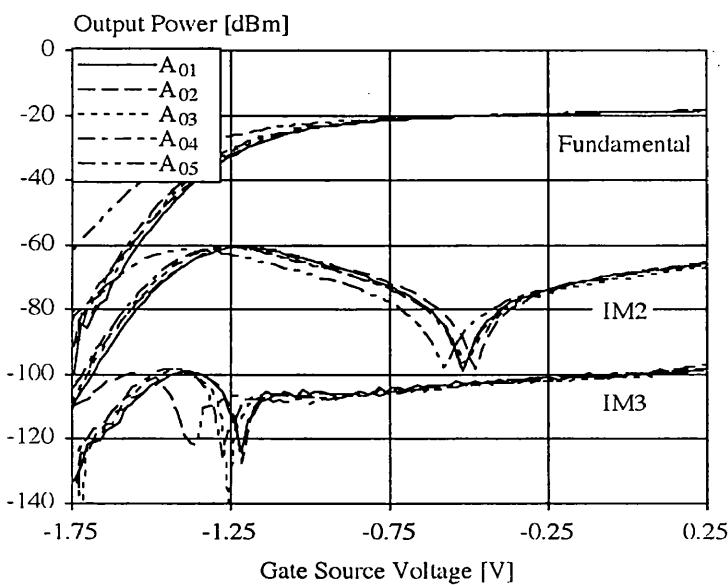

| 5.1  | Simulated bias dependent intermodulation distortion for a CLY5 GaAs MESFET; $V_{DS} = 2V$ and $R_{Load} = 10\Omega$ . . . . .                                                                                | 122 |

| 5.2  | Simulated observation of the effect of drain bias on distortion. The device is a CLY5 GaAs MESFET with a load resistance of $10\Omega$ . . . . .                                                             | 123 |

| 5.3  | Simulated observation of load resistance on distortion; $V_{DS} = 3V$ ; (a) Fundamental, (b) IMD2 and (c) IMD3. . . . .                                                                                      | 124 |

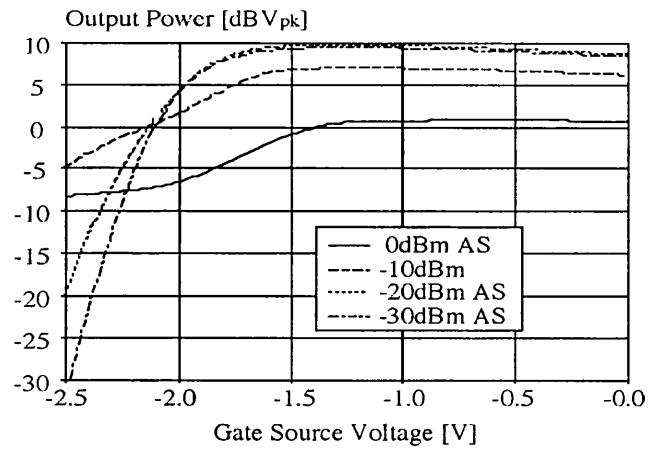

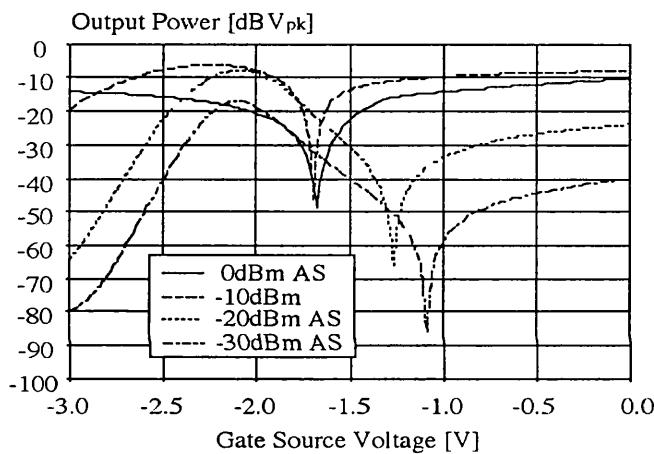

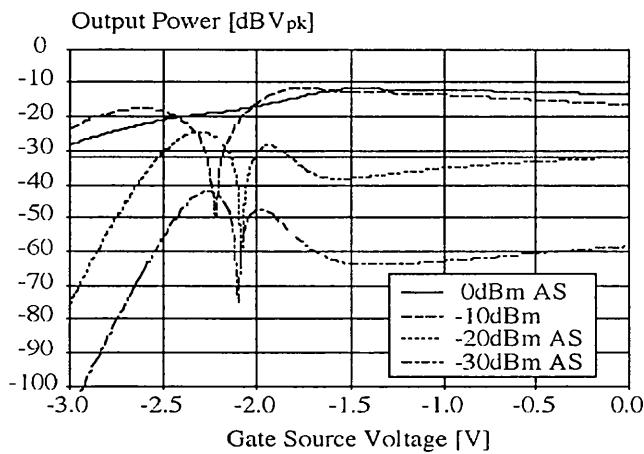

| 5.4  | Simulated observation of input power levels on distortion for a CLY5 GaAs MESFET; AS indicates amplitude shifting. $V_{DS} = 3V$ and $R_{Load} = 50\Omega$ ; (a) Fundamental, (b) IMD2 and (c) IMD3. . . . . | 125 |

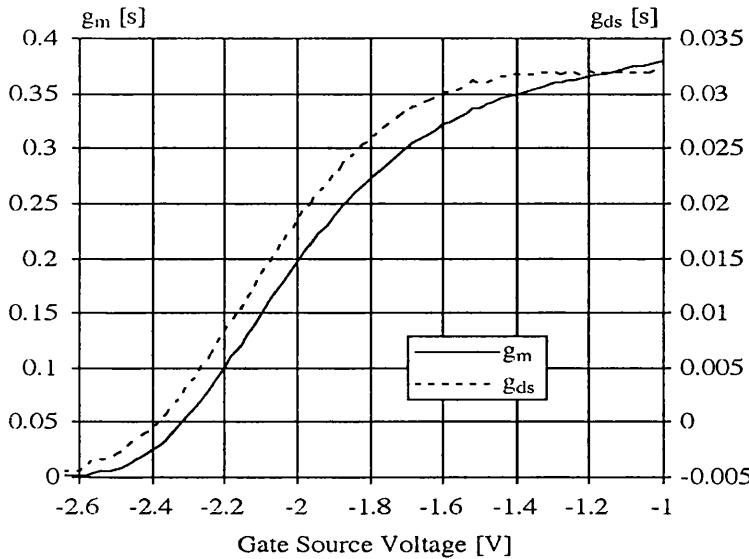

| 5.5  | The measured plot of $g_m$ and $g_{ds}$ against gate-source voltage for a CLY5 GaAs MESFET; $V_{DS} = 3V$ and input power level is -10 dBm. . . . .                                                          | 127 |

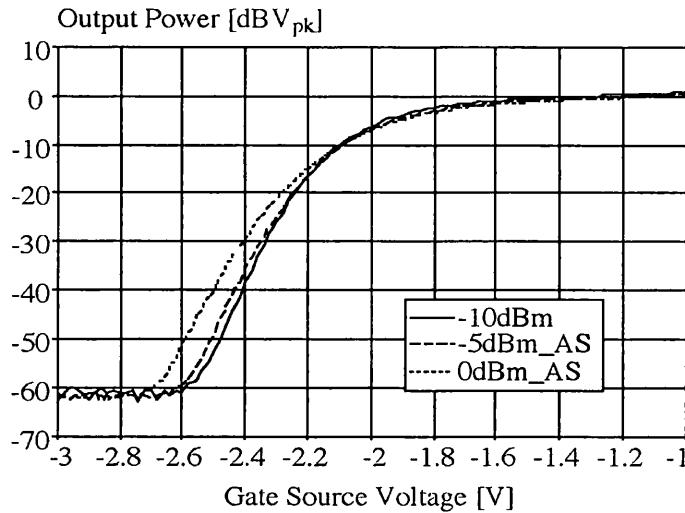

| 5.6  | Measured fundamental saturation effect for a CLY5 GaAs MESFET; $V_{DS} = 3V$ and $R_{Load} = 50\Omega$ . Note that amplitude shifting (AS) has been carried out. . . . .                                     | 128 |

| 5.7  | Measured 2nd and 3rd order intermodulation distortion saturation effect on a CLY5 GaAs MESFET; $V_{DS} = 3V$ and $R_{Load} = 50\Omega$ . Note that amplitude shifting (AS) has been carried out. . . . .     | 128 |

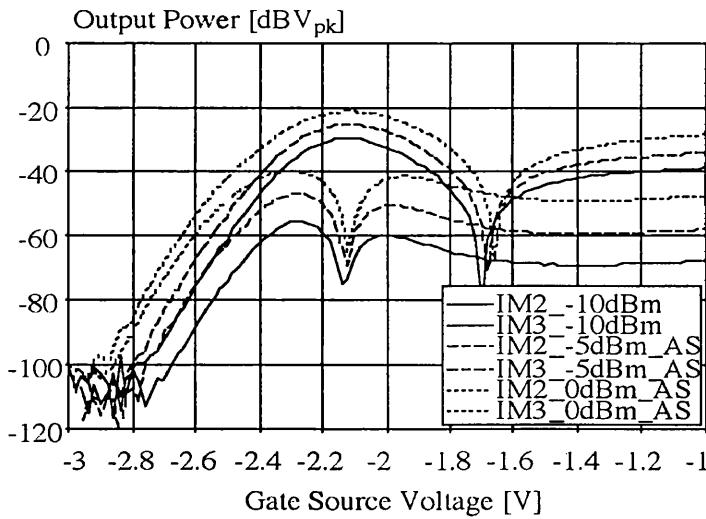

| 5.8  | Measured IMD3 as a function of gate source voltage for various input power levels for two load resistance values. AS indicates amplitude shifting. . . . .                                                   | 129 |

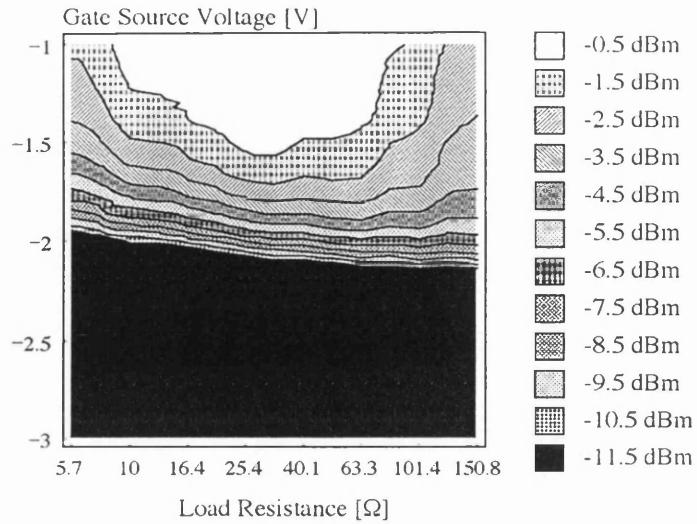

| 5.9  | Measured contour plot of power gain versus load resistance and gate source voltage; $V_{DS} = 3V$ and input power level is -10 dBm. The device is a CLY5 GaAs MESFET. . . . .                                | 130 |

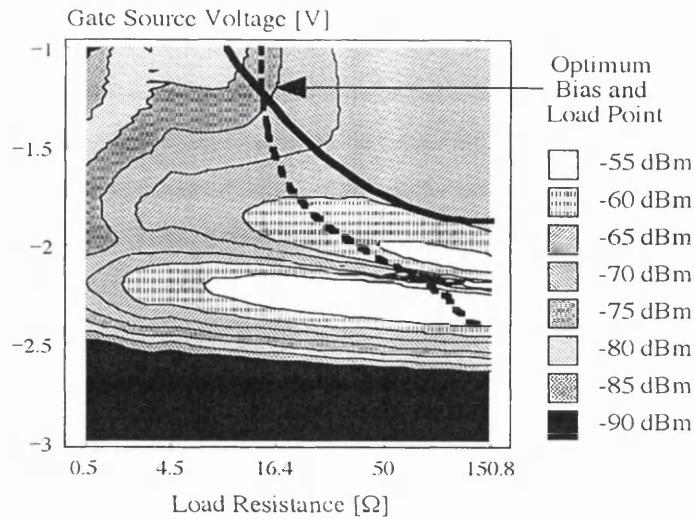

| 5.10 | Measured contour plot of 2nd order intermodulation distortion versus load resistance and gate-source voltage; $V_{DS} = 3V$ and input power level is -10 dBm. The device is a CLY5 GaAs MESFET. . . . .      | 130 |

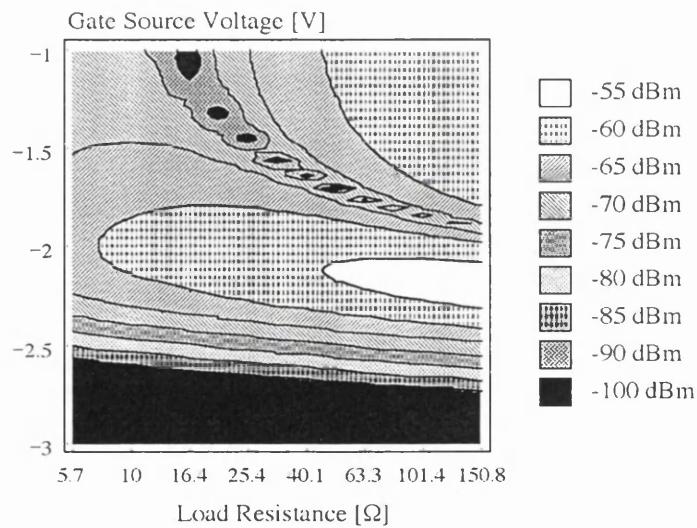

| 5.11 | Measured contour plots of 3rd order intermodulation distortion versus load resistance and gate-source voltage.; $V_{DS} = 3V$ and input power level is -10 dBm. The device is a CLY5 GaAs MESFET. . . . .    | 131 |

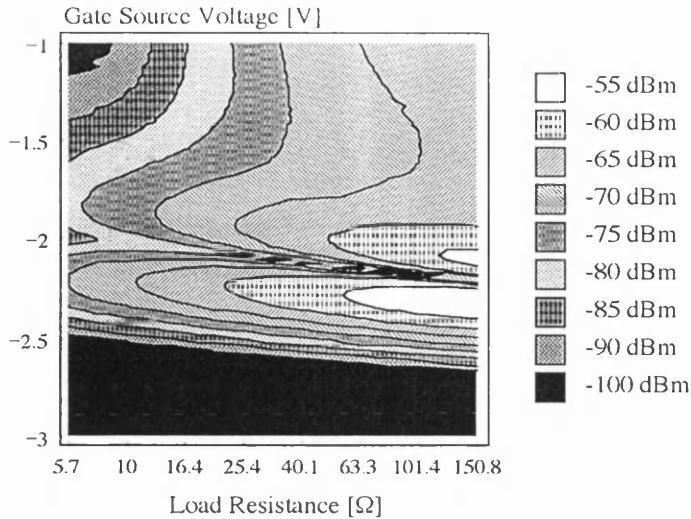

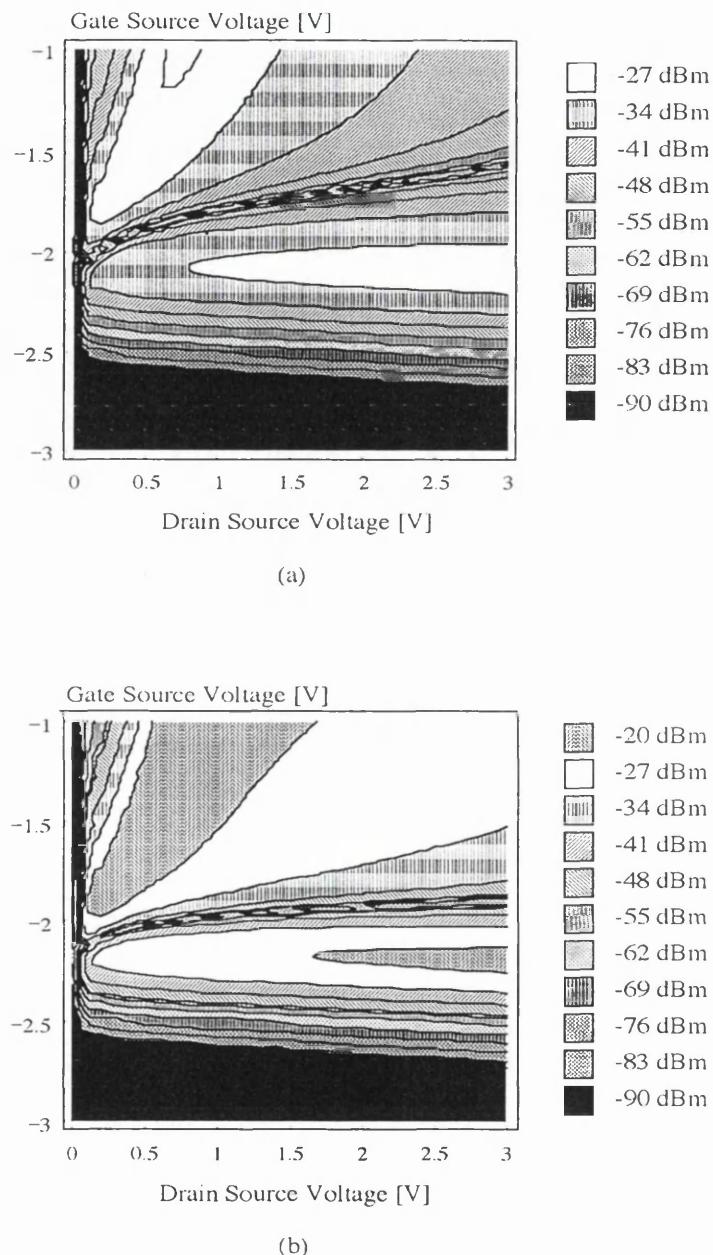

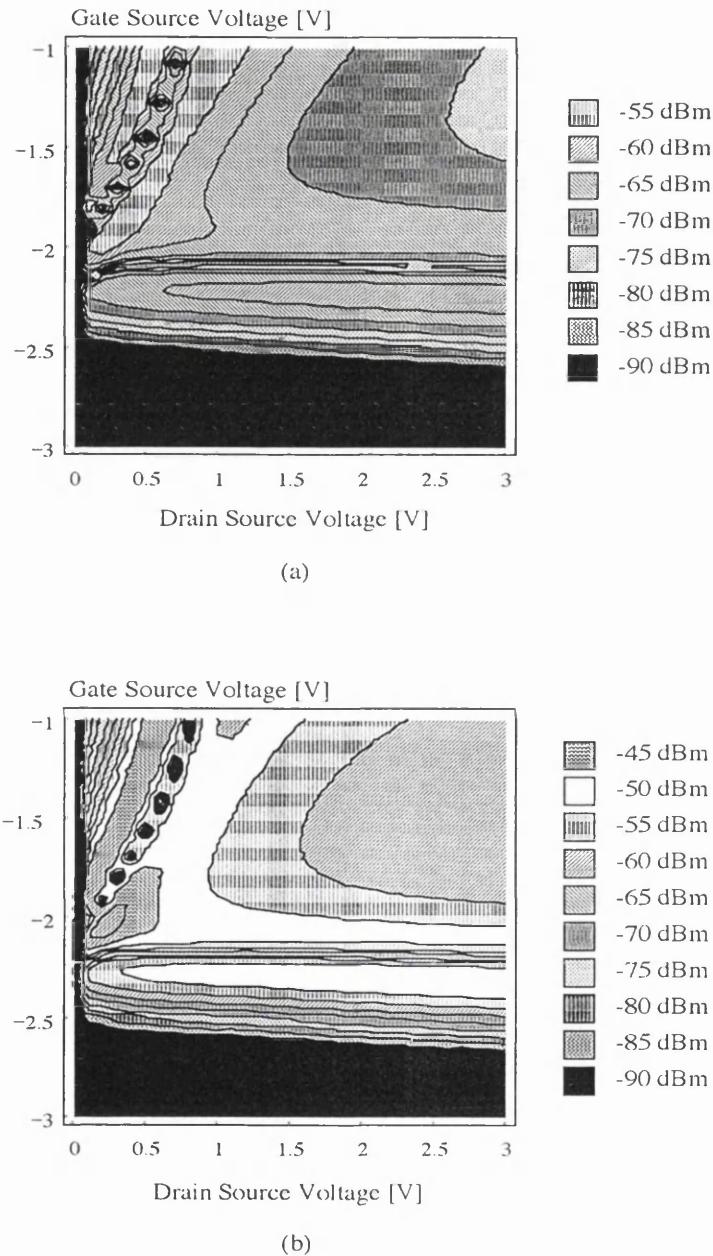

| 5.12 | Measured fundamental versus gate-source voltage and drain bias; input signal level is -10 dBm. (a) $R_{Load} = 32.6\Omega$ and (b) $R_{Load} = 150.8\Omega$ . The device is a CLY5 GaAs MESFET. . . . .      | 132 |

| 5.13 | Measured IMD2 versus gate-source voltage and drain bias; input signal level is -10 dBm. (a) $R_{Load} = 32.6\Omega$ and (b) $R_{Load} = 150.8\Omega$ . The device is a CLY5 GaAs MESFET. . . . .             | 133 |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.14 Measured IMD3 versus gate-source voltage and drain bias; input power level is -10 dBm. (a) $R_{Load} = 32.6\Omega$ and (b) $R_{Load} = 150.8\Omega$ . The device is a CLY5 GaAs MESFET. . . . .                                                                                                                                                                                                                    | 134 |

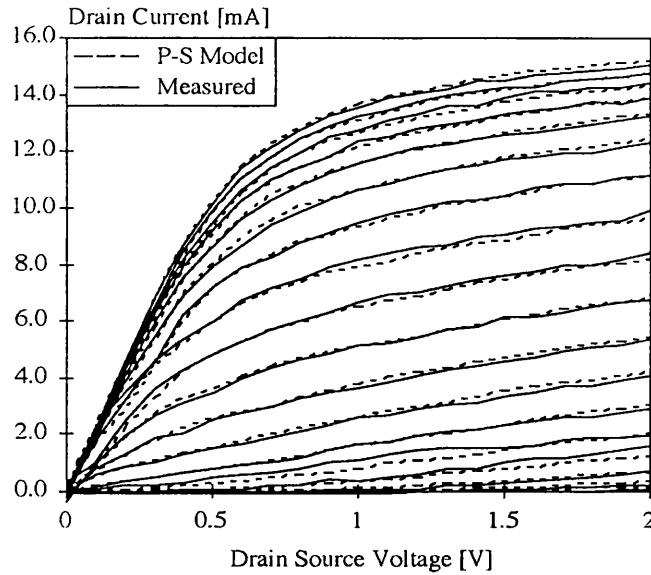

| 5.15 DC fit of the Parker Skellern model to measured CLY5 device. Gate bias is swept from -3 V to -1 V in 0.1 V steps. . . . .                                                                                                                                                                                                                                                                                          | 135 |

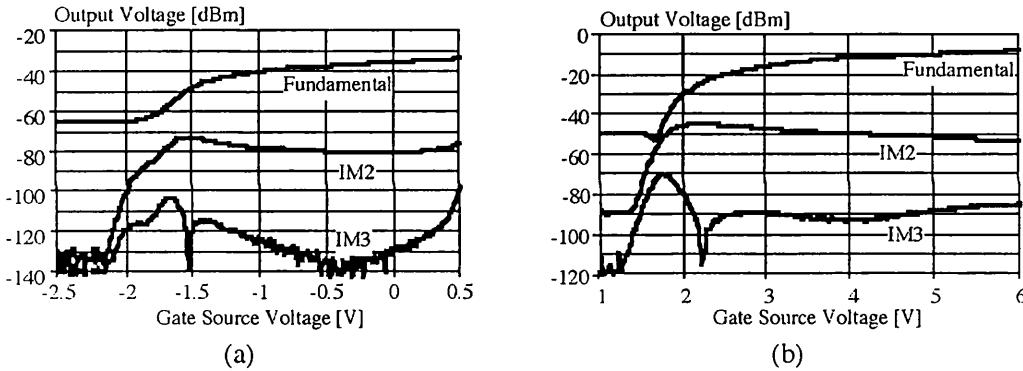

| 5.16 Measured bias dependent distortion for (a) a BF244 Si JFET and (b) a MC14007 Si MOSFET. . . . .                                                                                                                                                                                                                                                                                                                    | 135 |

| 5.17 Measured bias dependent distortion for (a) a MGF1400 GaAs MESFET and (b) a NE33284 AlGaAs/InGaAs PM HEMT. . . . .                                                                                                                                                                                                                                                                                                  | 136 |

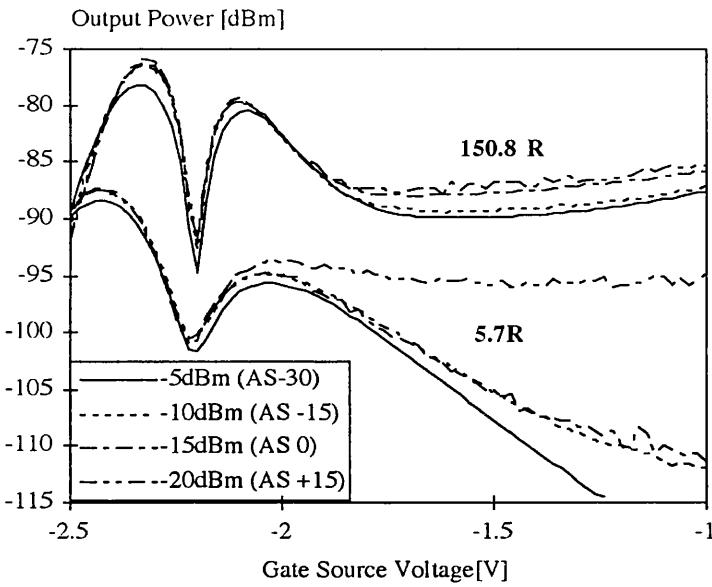

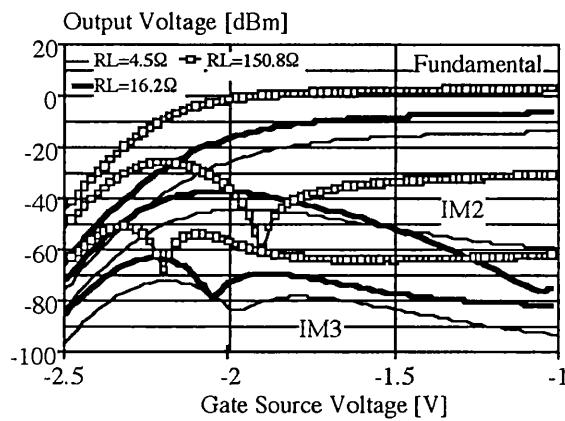

| 5.18 Measured bias dependent intermodulation distortion for a CLY5 GaAs MESFET for various load resistance values; input signal level is -17 dBm. . . . .                                                                                                                                                                                                                                                               | 137 |

| 5.19 Measured bias dependent intermodulation distortion for a NE33284A 0.2 $\mu$ m AlGaAs/InGaAs PM HEMT for various load resistance values; input signal level is -17 dBm. . . . .                                                                                                                                                                                                                                     | 137 |

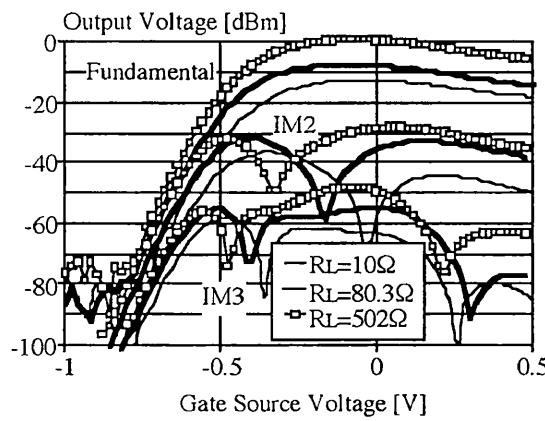

| 5.20 Effect of voltage gain on the measured intermodulation distortion for a CLY5 GaAs MESFET biased at $V_{GS} = -1V$ and $V_{DS} = 3V$ with input signal level of -17 dBm; a BF244A Si JFET biased at $V_{GS} = 0V$ and $V_{DS} = 2V$ with input signal level of -12.5 dBm and a NE33284A 0.2 $\mu$ m AlGaAs/InGaAs PM HEMT biased at $V_{GS} = 0V$ and $V_{DS} = 1.5V$ with input signal level of -17.5 dBm. . . . . | 138 |

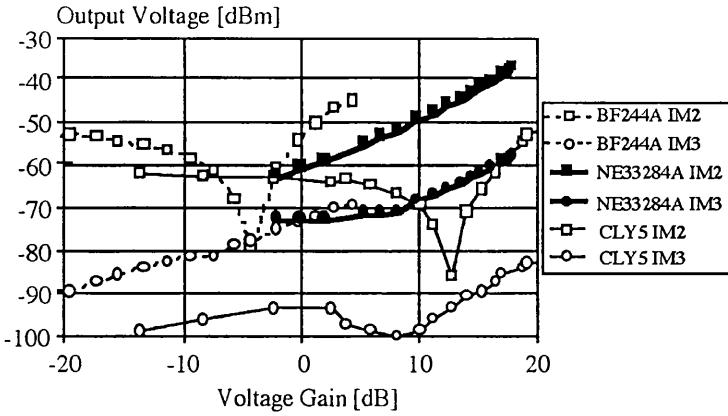

| 5.21 Effect of load resistance on the measured intermodulation distortion for a CLY5 GaAs MESFET biased at $V_{GS} = -1V$ and $V_{DS} = 3V$ with input signal level of -17.5 dBm. . . . .                                                                                                                                                                                                                               | 139 |

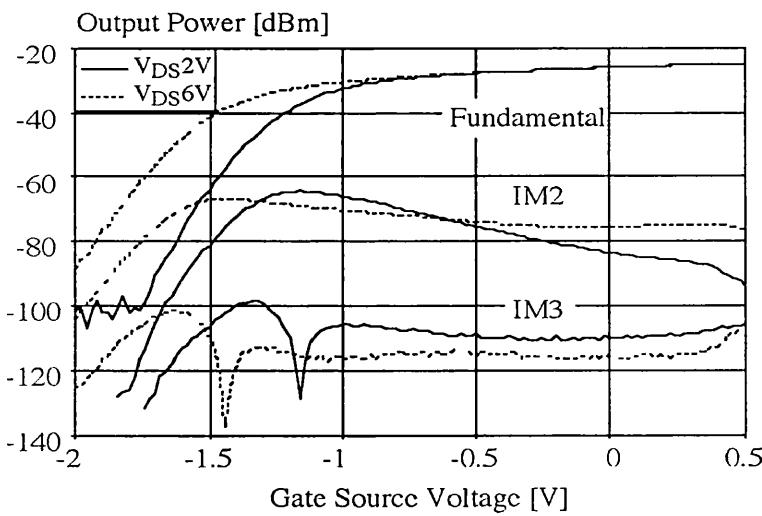

| 5.22 Effect of drain bias on measured bias dependent distortion of a MMT F20 6x100 $\mu$ m MESFET for $V_{DS} = 2V$ and $V_{DS} = 6V$ with load resistance of 10 $\Omega$ . Input signal level is -15 dBm. . . . .                                                                                                                                                                                                      | 139 |

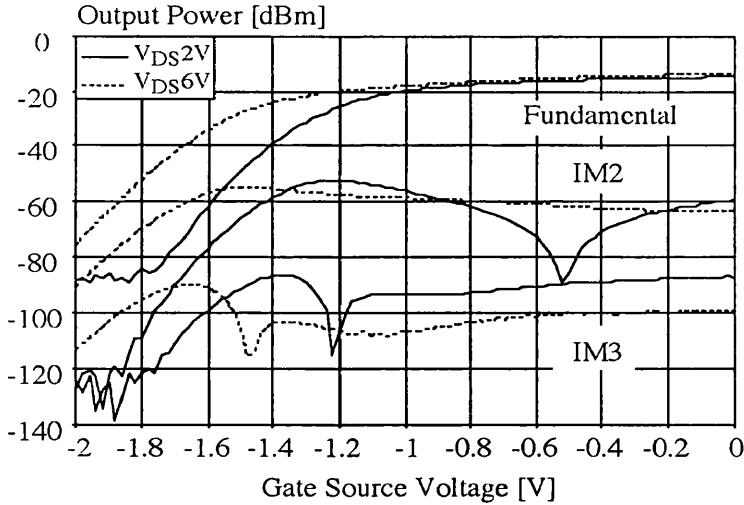

| 5.23 Effect of drain bias on measured bias dependent distortion of a MMT F20 6x100 $\mu$ m MESFET for $V_{DS} = 2V$ and $V_{DS} = 6V$ with load resistance of 50 $\Omega$ . Input signal level is -15 dBm. . . . .                                                                                                                                                                                                      | 140 |

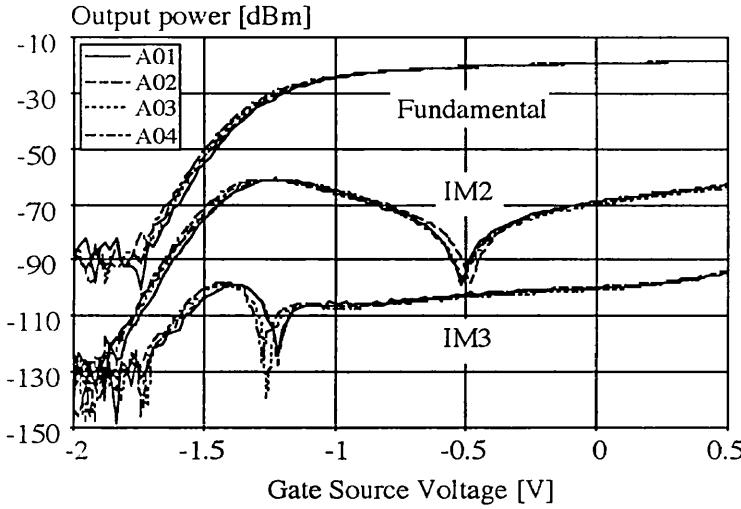

| 5.24 Example of sample to sample variation of measured bias dependent distortion for a MMT F20 6x100 $\mu$ m MESFET for $R_{Load} = 50\Omega$ and $V_{DS} = 2V$ . . . . .                                                                                                                                                                                                                                               | 141 |

|                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

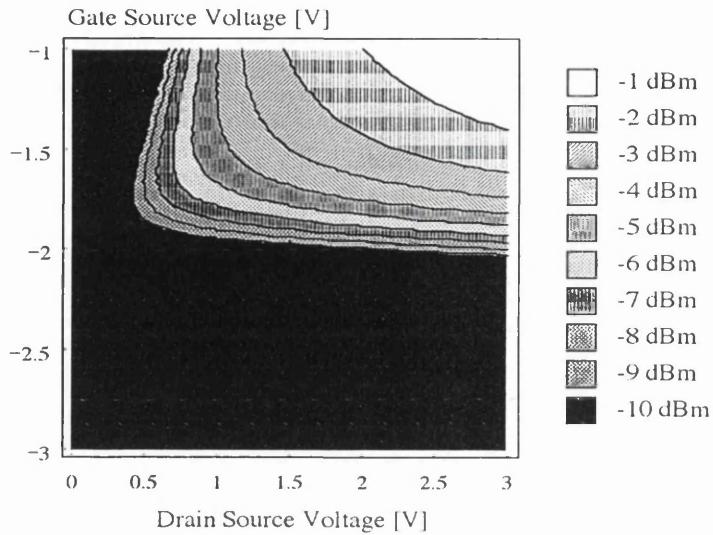

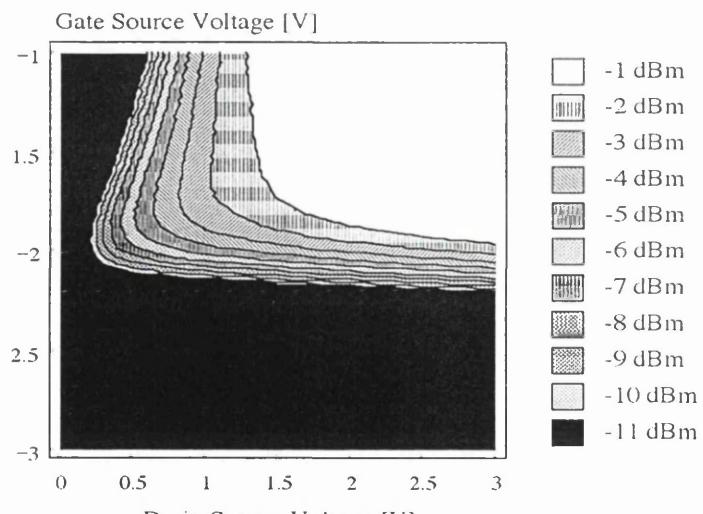

| 5.25 Selecting optimum bias and load for a low distortion amplifier (CLY5 GaAs MESFET). The contour plot is the measured 3rd order intermodulation distortion. The position of the 2nd order notch (solid line) and maximum power transfer (dotted line) are superimposed on the IMD3 contour. In put signal level is -17 dBm with a drain bias of 3 V. . . . .                                                        | 142 |

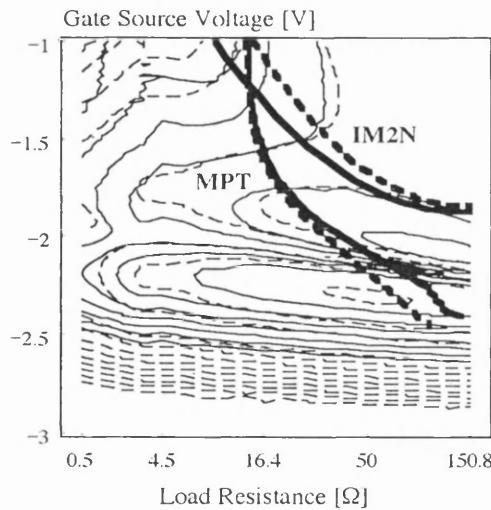

| 5.26 Effect of input power on optimum bias and load conditions for a low distortion amplifier (CLY5 GaAs MESFET). The contour plots shown are measured IMD3 for input signal levels of -7 dBm (dotted) and -17 dBm (solid). The positions of the IMD2 nulls (IM2N) and maximum power transfer (MPT) are shown as lines ( -7 dBm (dotted) and -17 dBm (solid) ) on top of the contour plots. Drain bias is 3 V. . . . . | 142 |

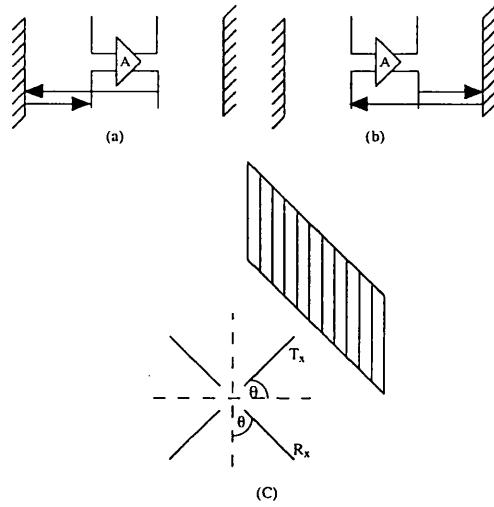

| 6.1 Individual amplifier cell, (a) and (b) show the two reflection paths and (c) represents the angle of rotation. . . . .                                                                                                                                                                                                                                                                                             | 146 |

| 6.2 Gain budget of the system. . . . .                                                                                                                                                                                                                                                                                                                                                                                 | 148 |

| 6.3 DC I-V fit of the P-S model to the 1x60 $\mu$ m UoG MONOFAST MESFET. Gate bias is swept from -1.2 V to +0.5 V in 0.1 V steps. . . . .                                                                                                                                                                                                                                                                              | 151 |

| 6.4 Proposed circuit for implementing $y = kx^3 + rx$ function. . . . .                                                                                                                                                                                                                                                                                                                                                | 152 |

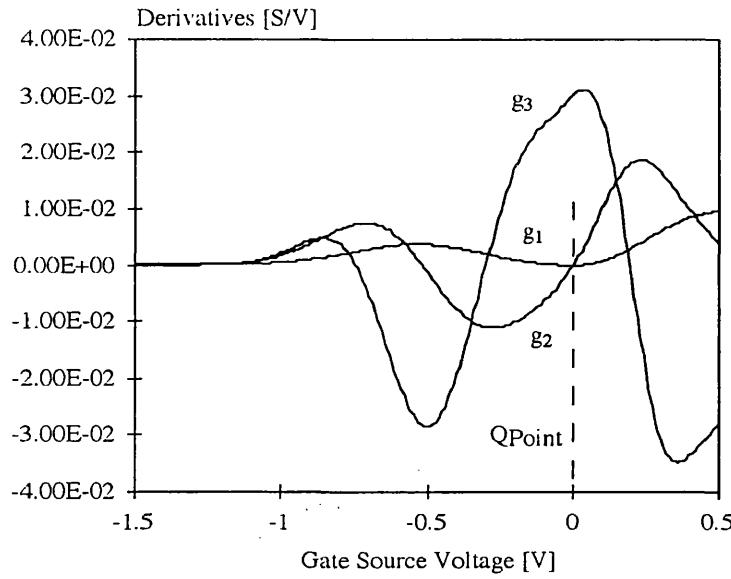

| 6.5 Derivative structure versus gate bias. . . . .                                                                                                                                                                                                                                                                                                                                                                     | 154 |

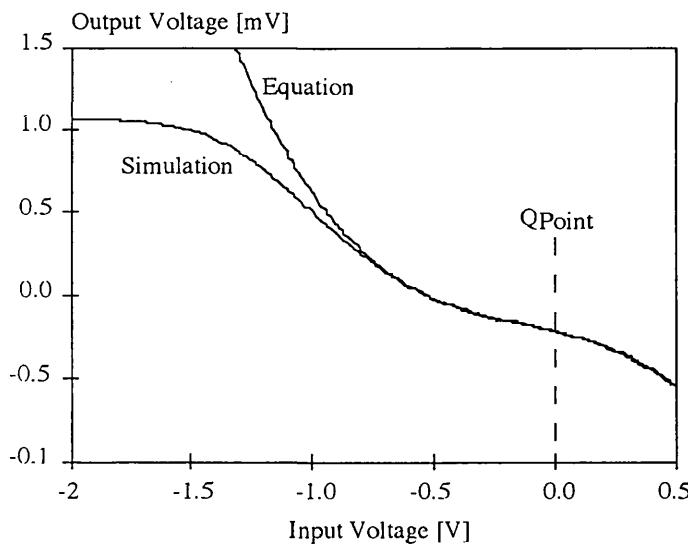

| 6.6 Dynamic transfer characteristic simulation with equation fit. . . . .                                                                                                                                                                                                                                                                                                                                              | 154 |

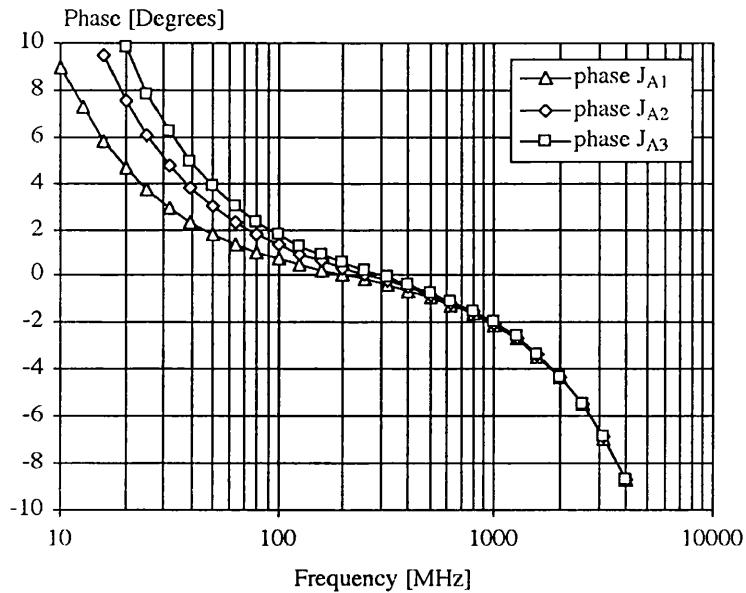

| 6.7 The phase response on the gates of the FETs. . . . .                                                                                                                                                                                                                                                                                                                                                               | 156 |

| 6.8 Differential pair with passive loading; connection to ground. . . . .                                                                                                                                                                                                                                                                                                                                              | 156 |

| 6.9 The transfer characteristic of the differential pair with passive loading; connection to ground. . . . .                                                                                                                                                                                                                                                                                                           | 157 |

| 6.10 Differential pair with passive loading; connection to -2 V rail. . . . .                                                                                                                                                                                                                                                                                                                                          | 158 |

| 6.11 The transfer characteristic of the differential pair with passive loading; connection to -2 V rail. . . . .                                                                                                                                                                                                                                                                                                       | 158 |

| 6.12 The common mode rejection ratio of the differential pair with passive loading; connection to -2 V rail. . . . .                                                                                                                                                                                                                                                                                                   | 159 |

| 6.13 The transient characteristic of the differential pair amplifier with passive loading; connection to -2 V rail. . . . .                                                                                                                                                                                                                                                                                            | 159 |

| 6.14 Differential pair with active loading. . . . .                                                                                                                                                                                                                                                                                                                                                                    | 160 |

| 6.15 The transfer characteristic of the differential pair with active loading; connection to -2 V rail. . . . .                                                                                                                                                                                                                                                                                                        | 161 |

| 6.16 The common mode rejection ratio of the differential pair with active loading; connection to -2 V rail. . . . .                                                                                                                                                                                                                                                                                                    | 161 |

|      |                                                                                                                                                                                                           |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

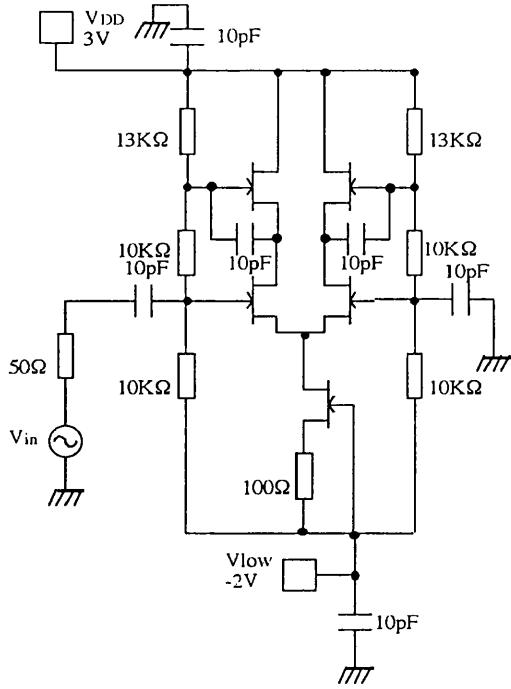

| 6.17 | Differential pair with cascode current source configuration. . . . .                                                                                                                                      | 162 |

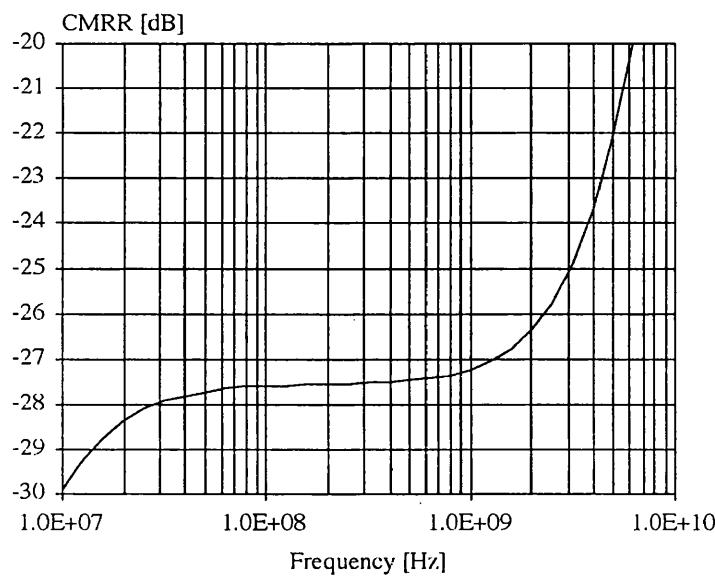

| 6.18 | The common mode rejection ratio of the differential pair with cascode current source configuration; 1 $\mu\text{m}$ gate length design. . . . .                                                           | 163 |

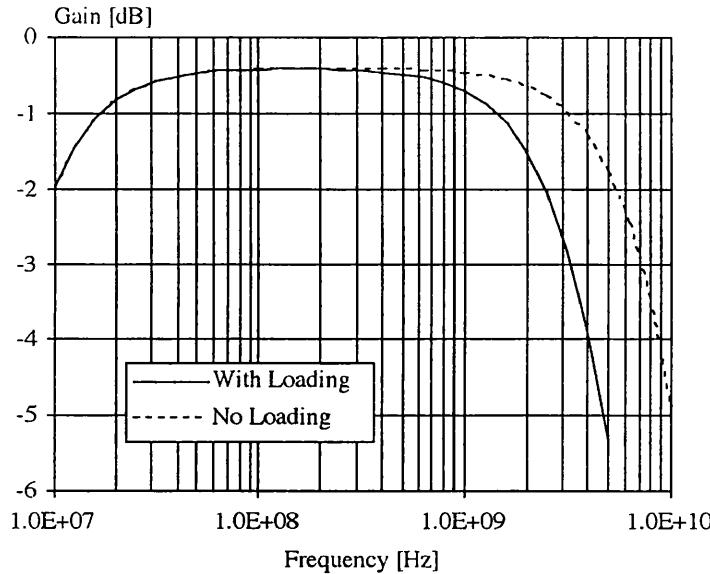

| 6.19 | The effect of the next stage (driver amplifier) loading on the performance of the differential pair amplifier with cascode current source configuration; 1 $\mu\text{m}$ design. . . . .                  | 163 |

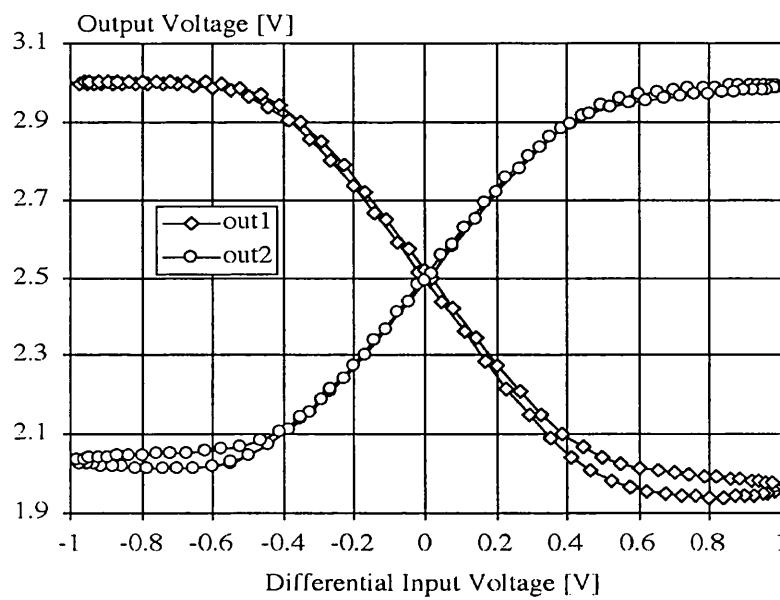

| 6.20 | The transfer characteristic of the differential pair with cascode current source configuration; 0.2 $\mu\text{m}$ gate length design. . . . .                                                             | 164 |

| 6.21 | The common mode rejection ratio of the differential pair with cascode current source configuration; 0.2 $\mu\text{m}$ gate length design. . . . .                                                         | 164 |

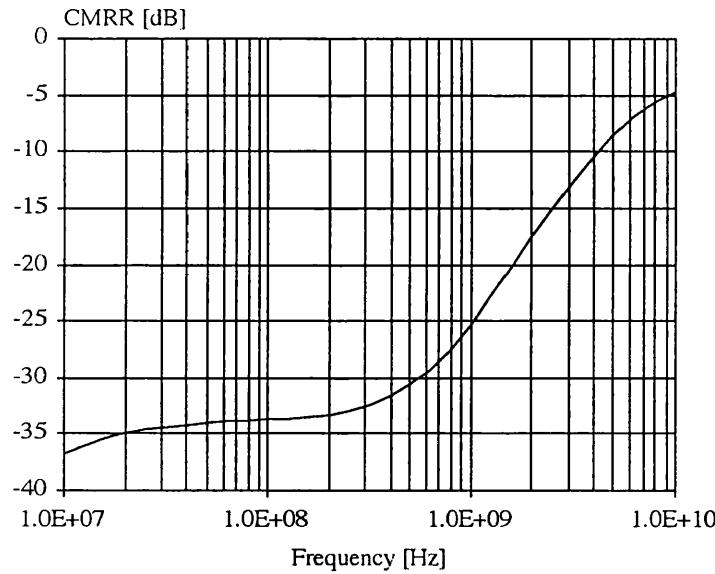

| 6.22 | The effect of the next stage (driver amplifier) loading on the performance of the differential pair amplifier with cascode current source configuration; 0.2 $\mu\text{m}$ gate length design. . . . .    | 165 |

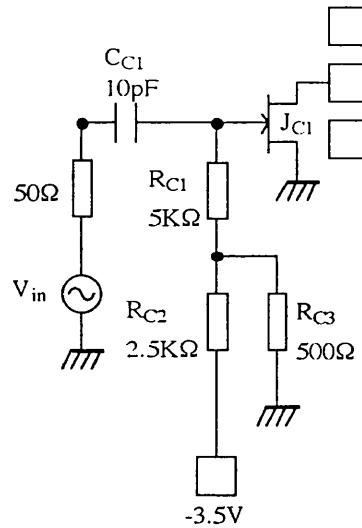

| 6.23 | The schematic diagram of the driver amplifier. . . . .                                                                                                                                                    | 166 |

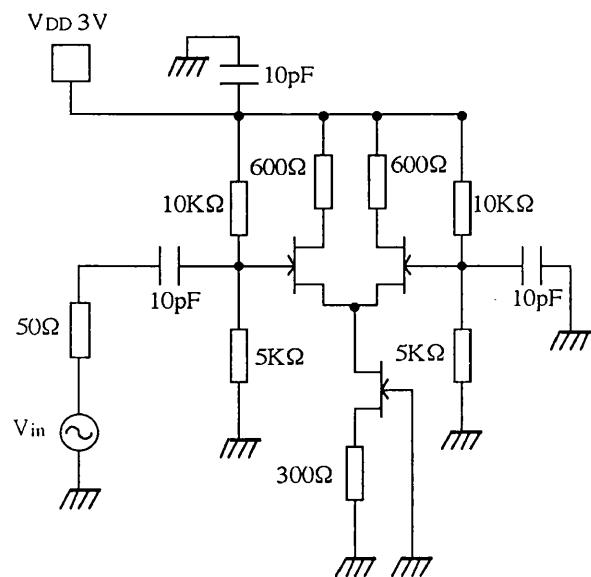

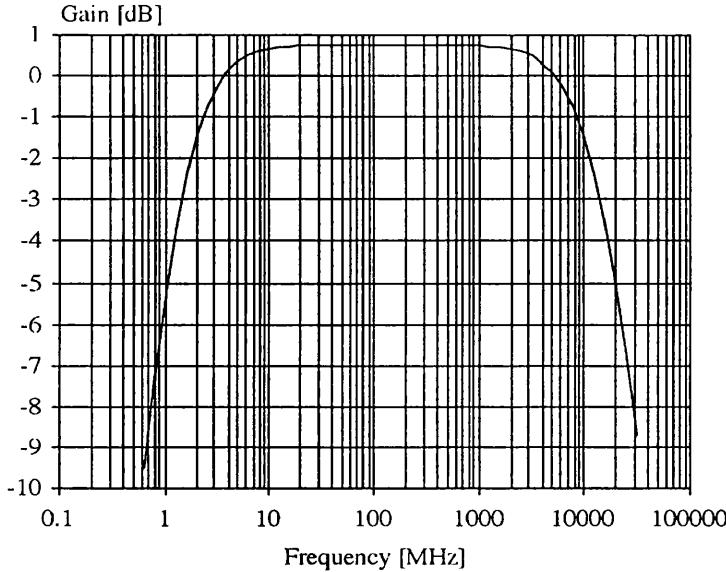

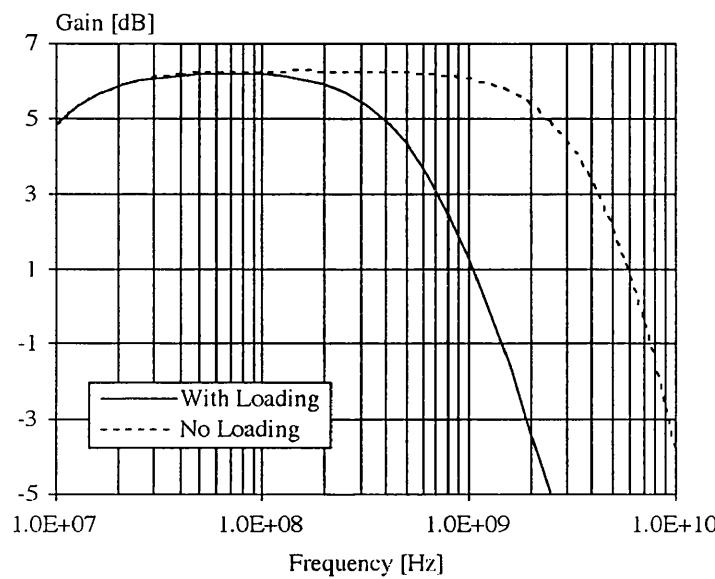

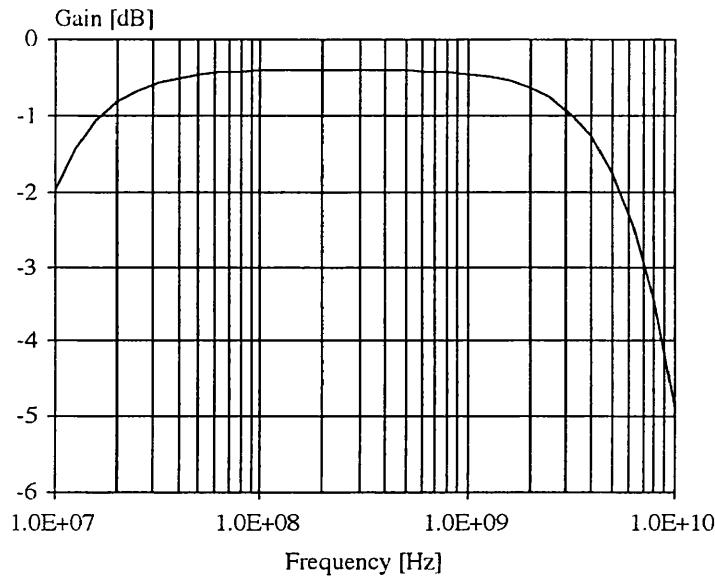

| 6.24 | The gain performance of the driver amplifier stage. . . . .                                                                                                                                               | 167 |

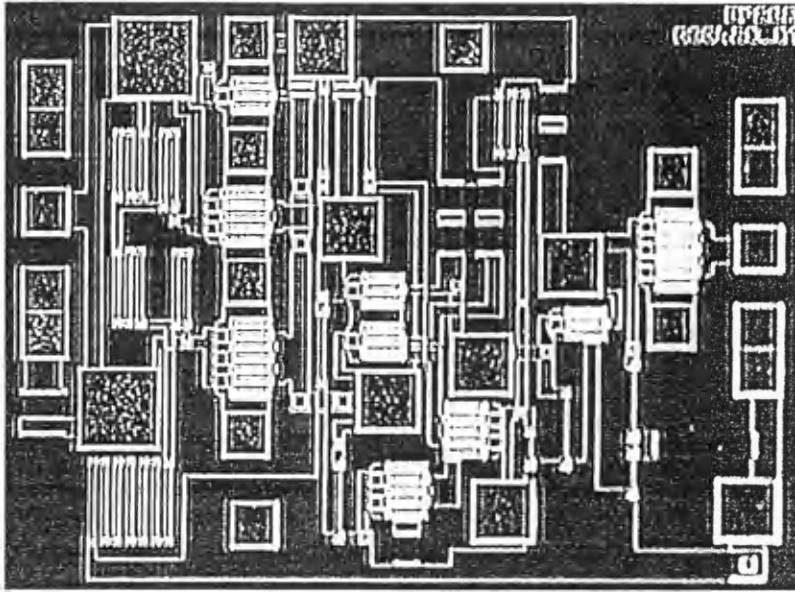

| 6.25 | Layout plot of the overall circuit. . . . .                                                                                                                                                               | 167 |

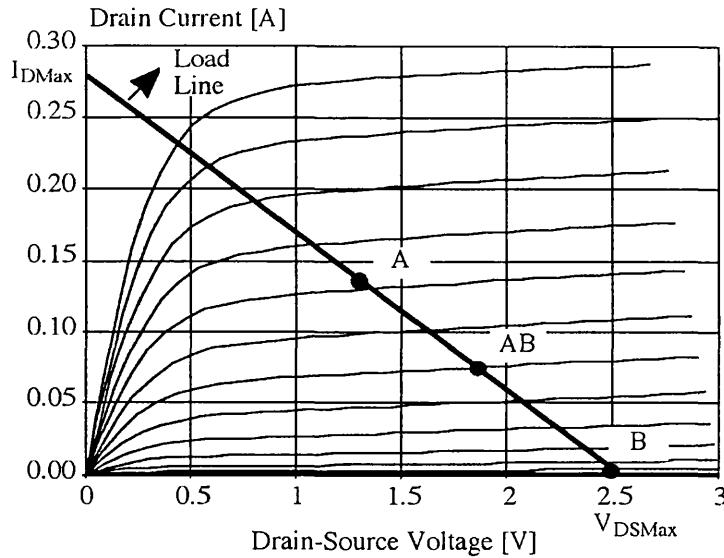

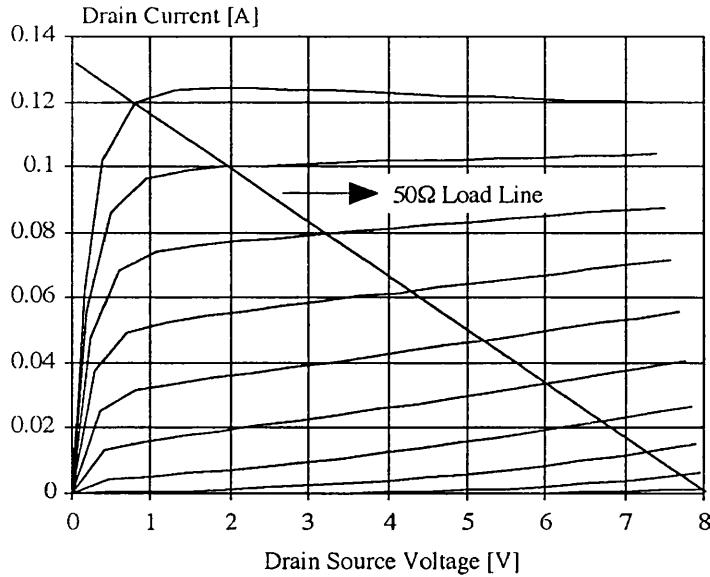

| 7.1  | Proposed load line for the design. Gate bias is swept from -2 V to +0.5 V in 0.25 V steps. . . . .                                                                                                        | 172 |

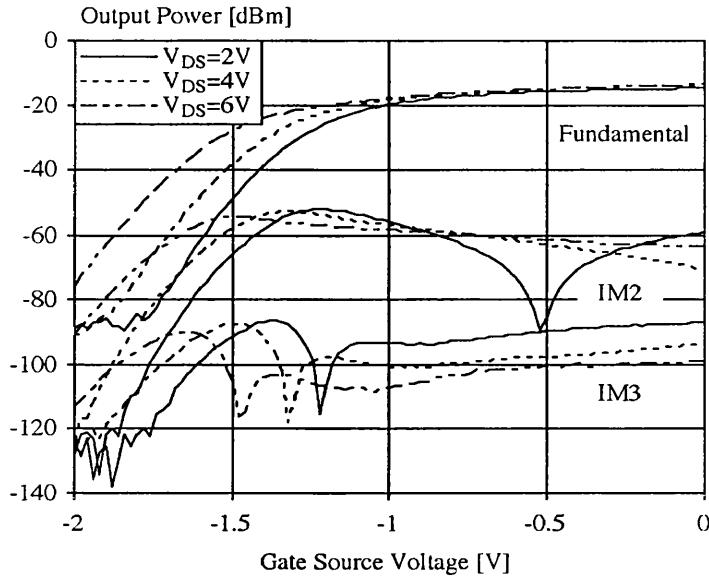

| 7.2  | Measured effect of different drain source voltages on a 6x100 $\mu\text{m}$ F20 GaAs MESFET. Input signal level is -15 dBm and load resistance is 50 $\Omega$ . . . . .                                   | 173 |

| 7.3  | Measured sample to sample study of five 6x100 $\mu\text{m}$ F20 GaAs MESFETs from the same wafer. . . . .                                                                                                 | 173 |

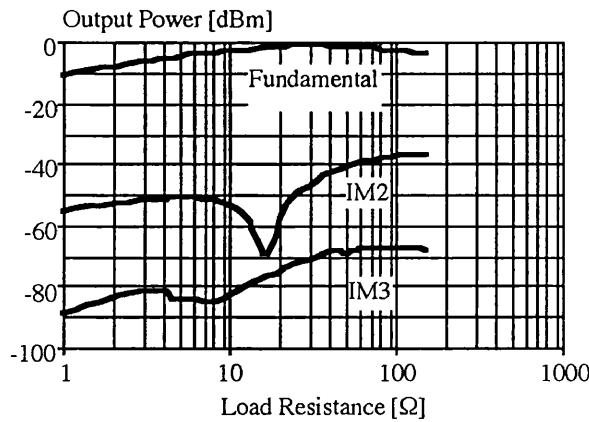

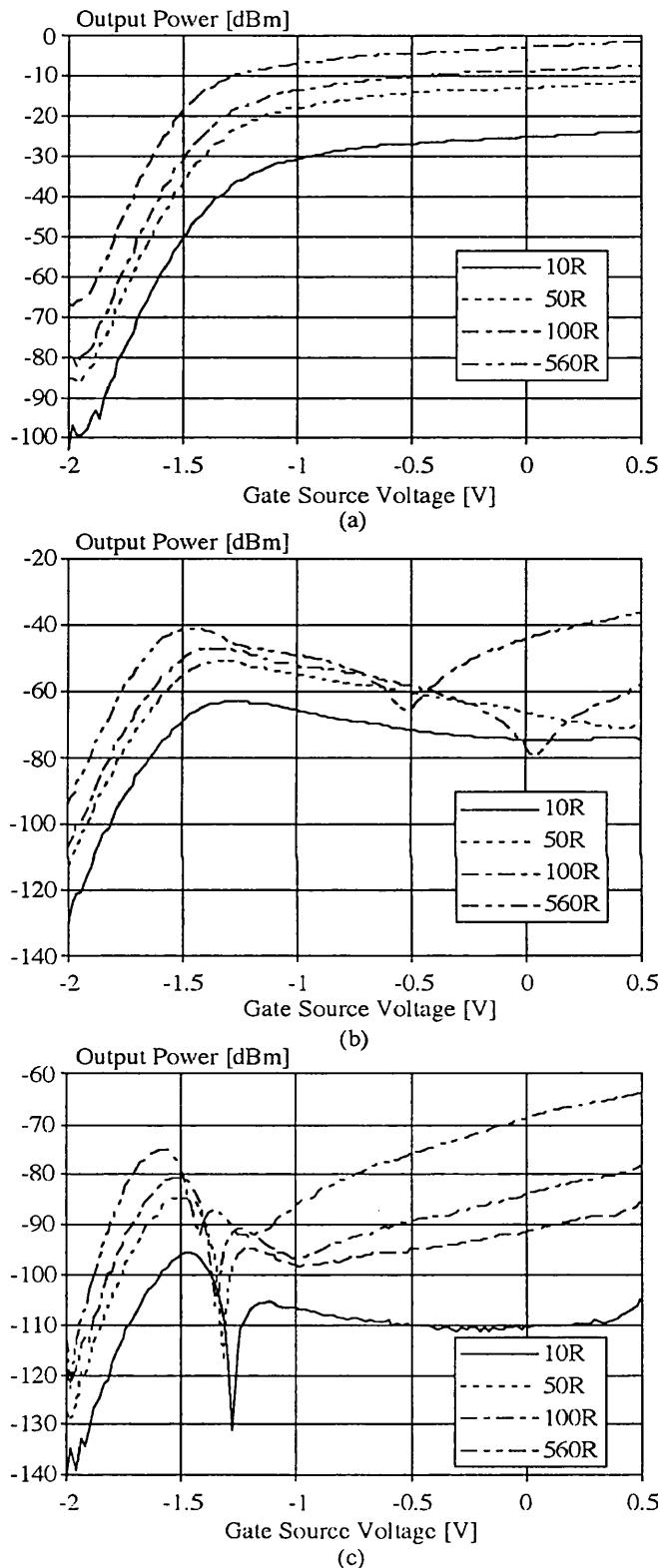

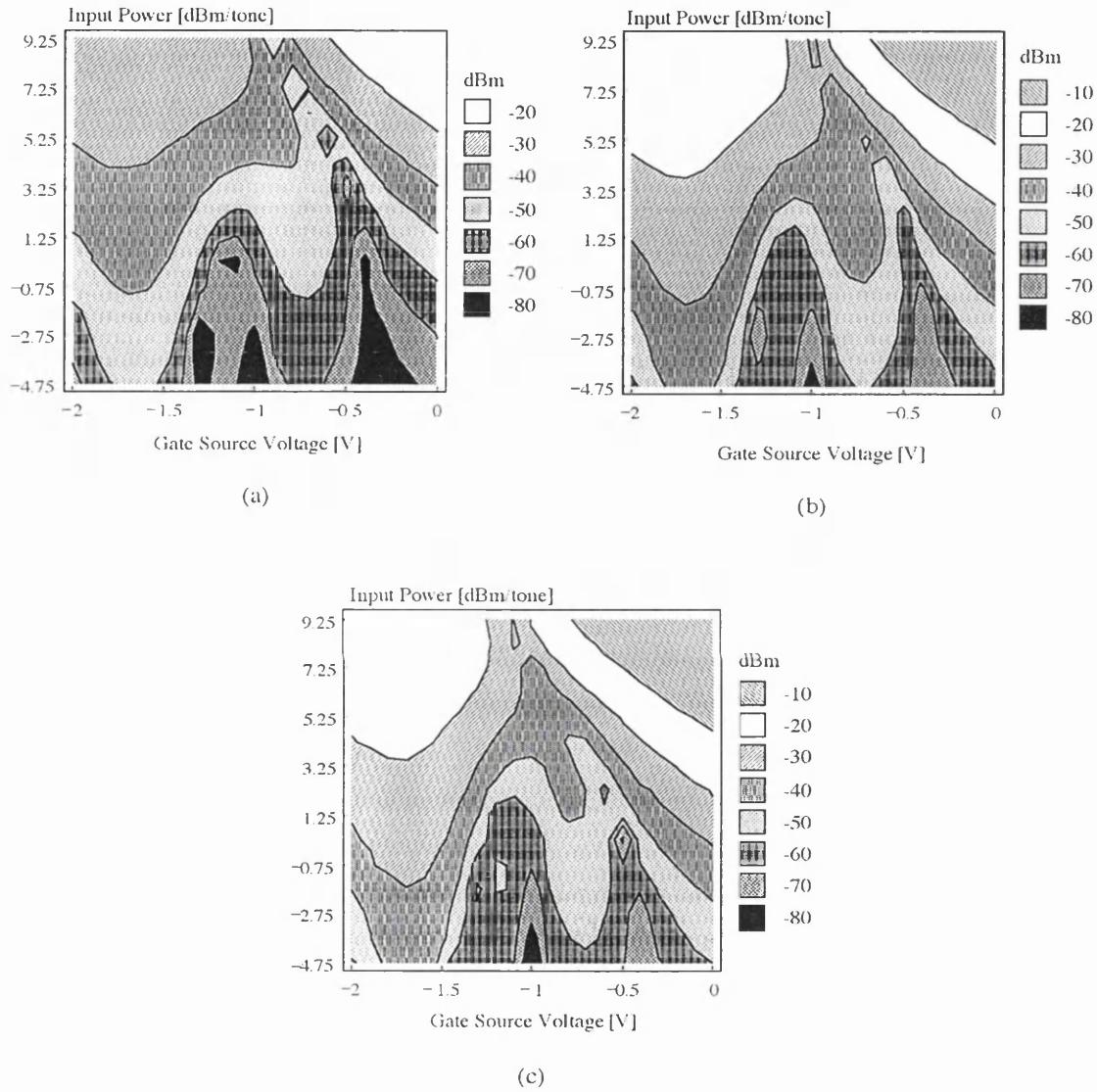

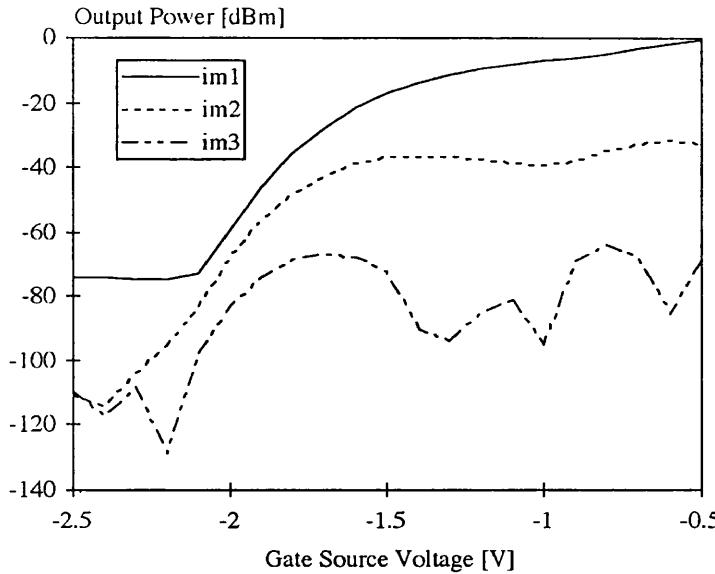

| 7.4  | Measured effect of load resistance on a 600 $\mu\text{m}$ F20 GaAs MESFET; (a) Fundamental, (b) IMD2 and (c) IMD3. . . . .                                                                                | 174 |

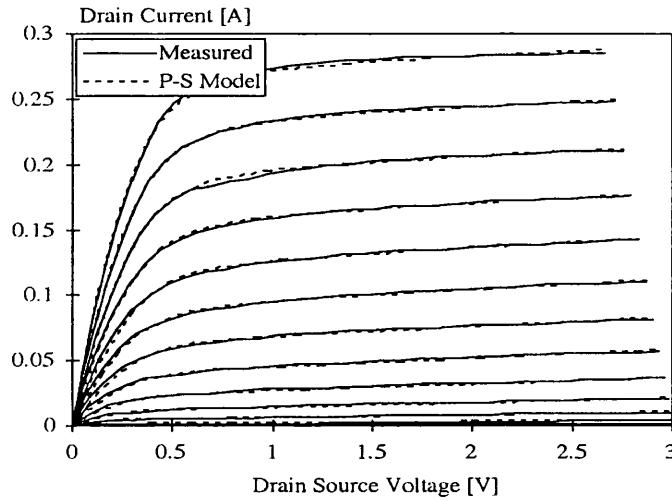

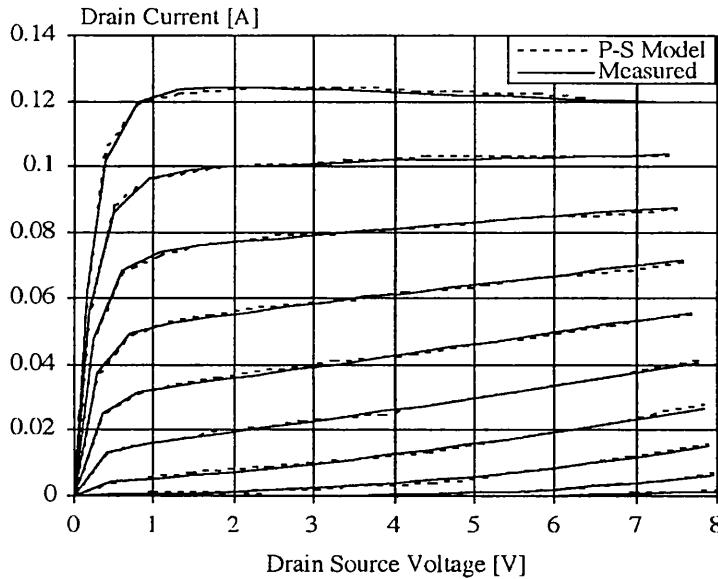

| 7.5  | DC I-V fit of the Parker Skellern model to the 6x100 $\mu\text{m}$ F20 GaAs MESFET. Gate bias is swept from -2 V to +0.5 V in 0.25 V steps. . . . .                                                       | 175 |

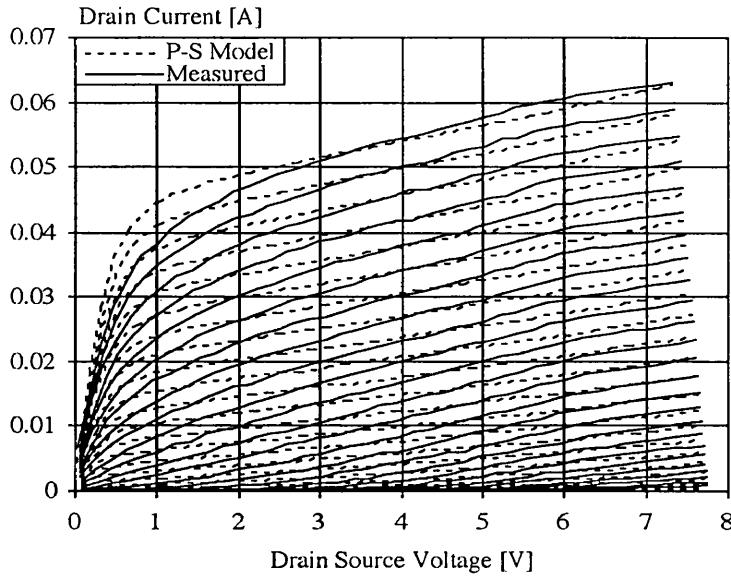

| 7.6  | Example fit of the Parker Skellern model to the pulsed I-V for a 300 $\mu\text{m}$ GaAs F20 MESFET device. Nominal $V_{GS} = -0.75V$ , $V_{DS} = 4V$ and Pulse is 1 $\mu\text{s}$ with 1 ms rest. . . . . | 177 |

| 7.7  | The block diagram of the derivative superposition amplifier. . . . .                                                                                                                                      | 178 |

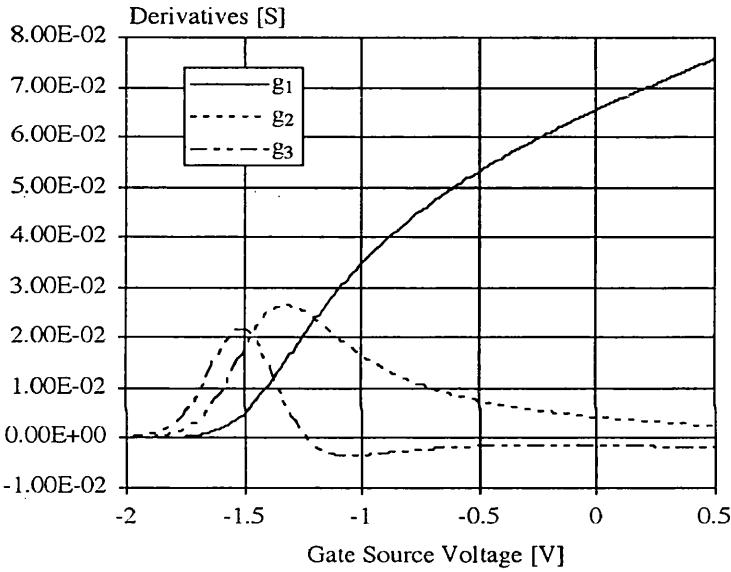

| 7.8  | The bias dependent derivatives of a single FET. . . . .                                                                                                                                                   | 178 |

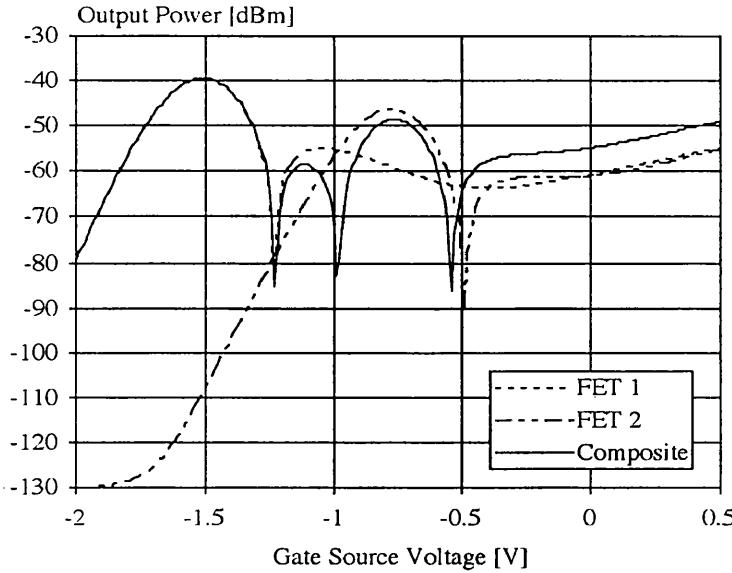

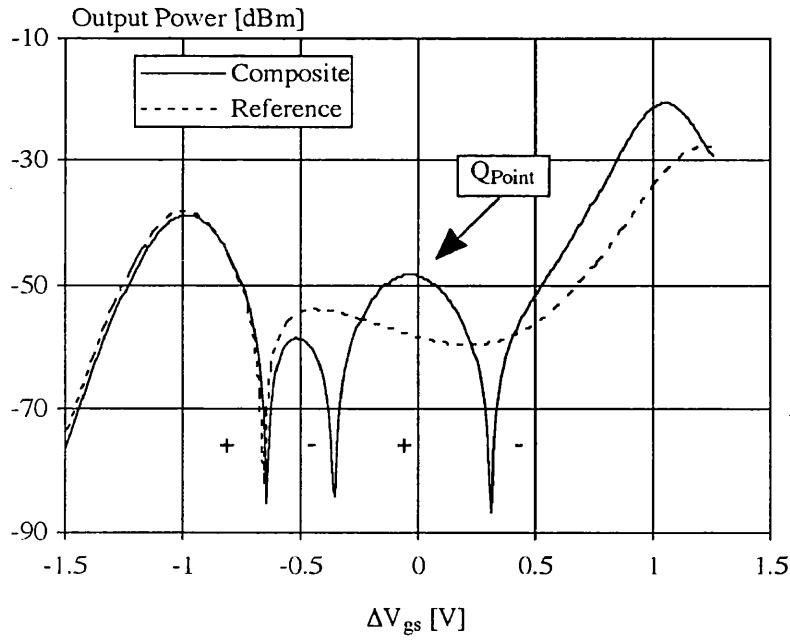

| 7.9  | The bias dependent small signal 3rd order distortion of the single FETs and the composite structure. . . . .                                                                                              | 179 |

|                                                                                                                                                                                                                                                                                                                                |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

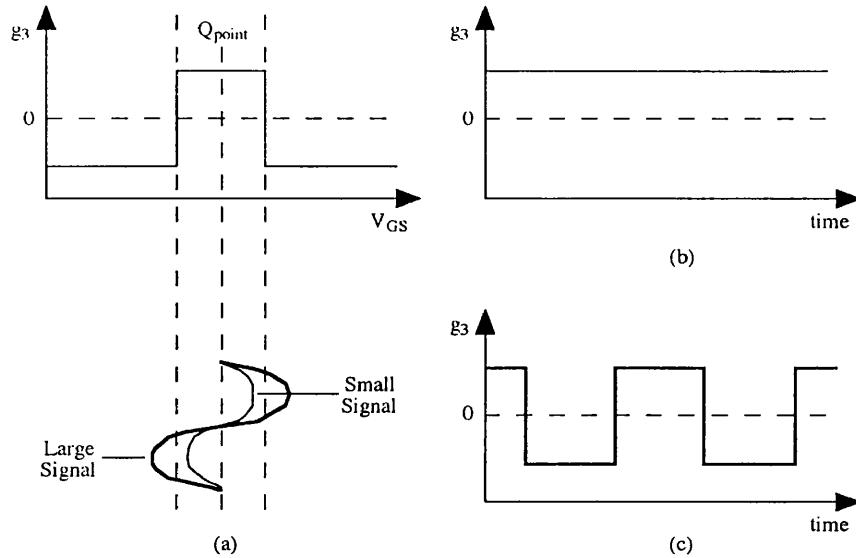

| 7.10 (a) Idealised variation of the 3rd derivative of drain current, $g_3$ , with gate source voltage for the DS power amplifier around its quiescent point. (b) Variation of $g_3$ with time under small signal excitation. (c) Variation of $g_3$ with time under large signal excitation. . . . .                           | 180 |

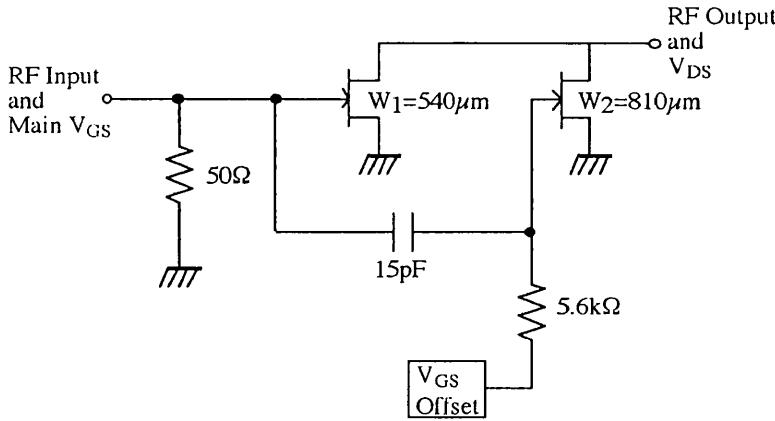

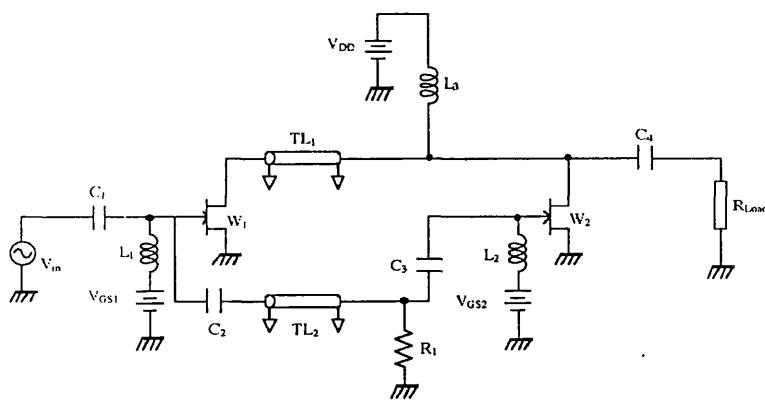

| 7.11 The schematic diagram of the derivative superposition amplifier. . . . .                                                                                                                                                                                                                                                  | 181 |

| 7.12 Simulated small signal distortion along the load line for a single 6x100 $\mu\text{m}$ F20 GaAs MESFET. $V_{GS} = -0.75V$ , $V_{DS} = 4V$ and $R_{Load} = 50\Omega$ . . . . .                                                                                                                                             | 182 |

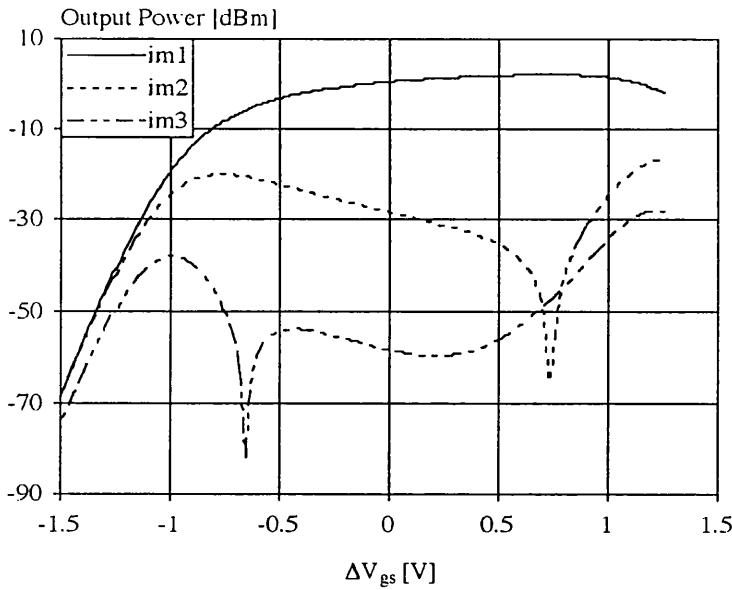

| 7.13 Simulated small signal 3rd order distortion along the load line for the single FET and the composite structure. $V_{GS} = -0.75V$ , offset= $-0.75V$ , $V_{DS} = 4V$ and $R_{Load} = 50\Omega$ . The gate width of the first FET is 540 $\mu\text{m}$ and the gate width of the second FET is 810 $\mu\text{m}$ . . . . . | 182 |

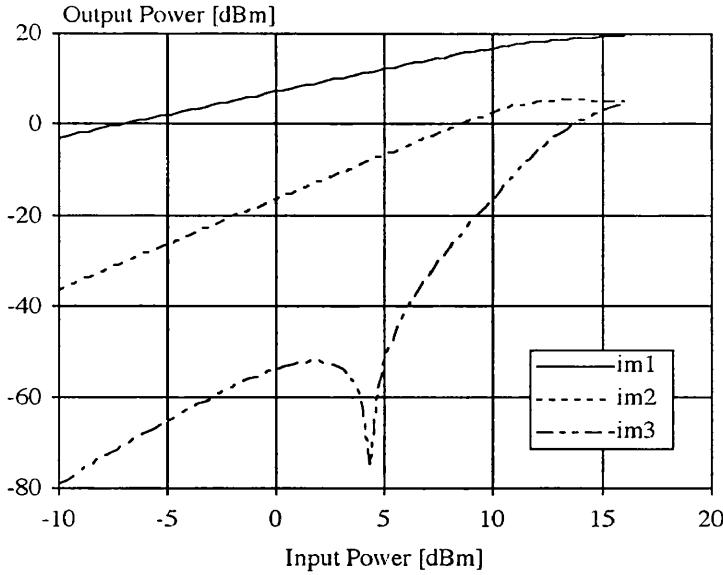

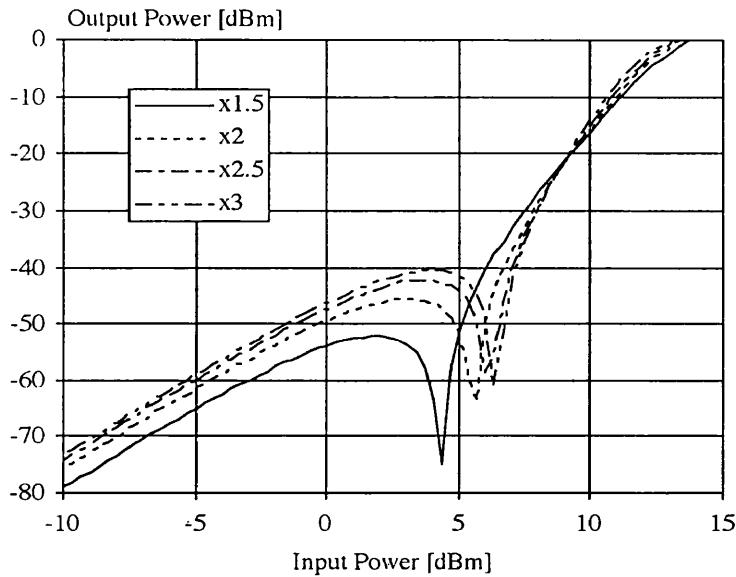

| 7.14 Simulated power sweep of the composite structure. $V_{GS} = -0.75V$ , offset= $-0.75V$ , $V_{DS} = 4V$ and $R_{Load} = 50\Omega$ . . . . .                                                                                                                                                                                | 183 |

| 7.15 Simulated small signal 3rd order distortion of the composite circuit for various secondary FET gate widths. . . . .                                                                                                                                                                                                       | 184 |

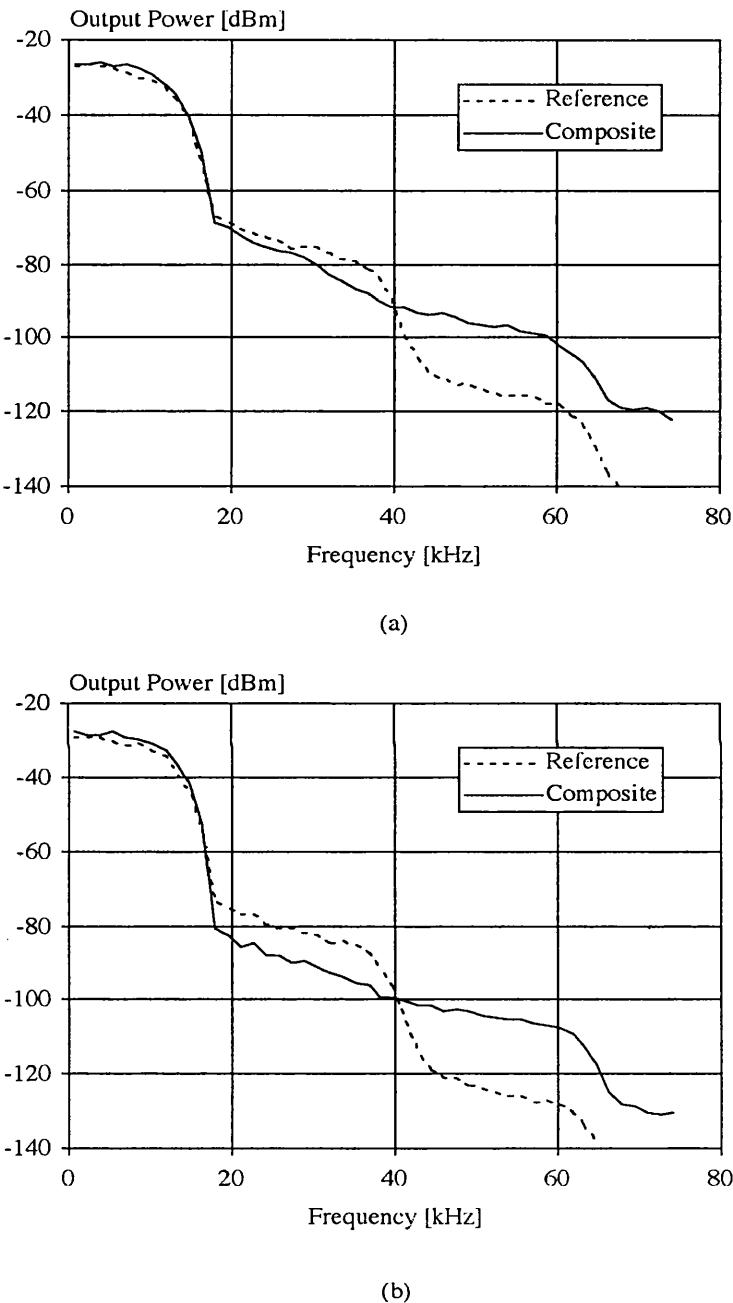

| 7.16 Simulated spectral regrowth comparison of the reference FET and the composite circuit; (a) at 2 dB back-off from 1 dB compression point and (b) at 4 dB back-off from 1 dB compression point. . . . .                                                                                                                     | 185 |

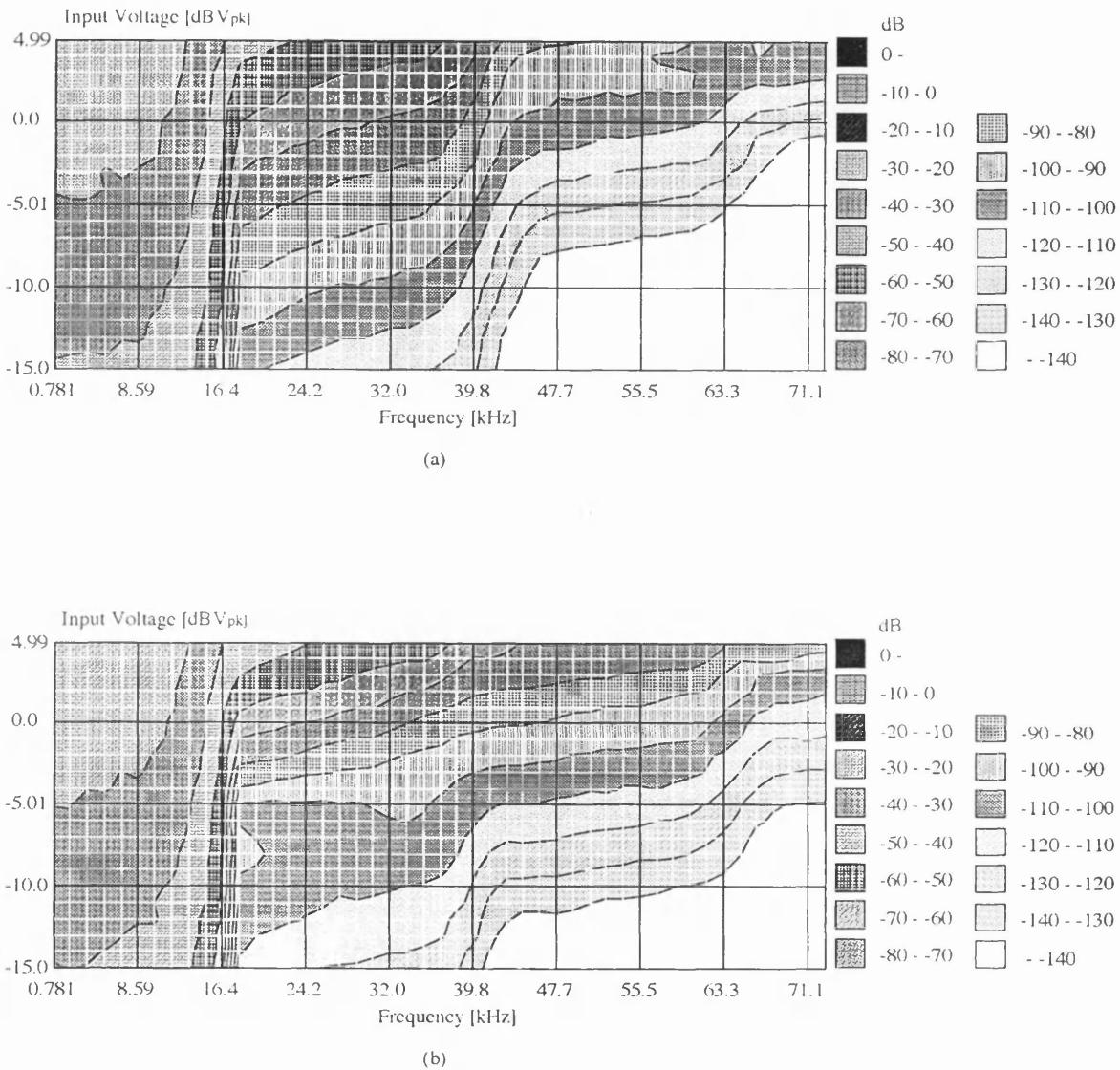

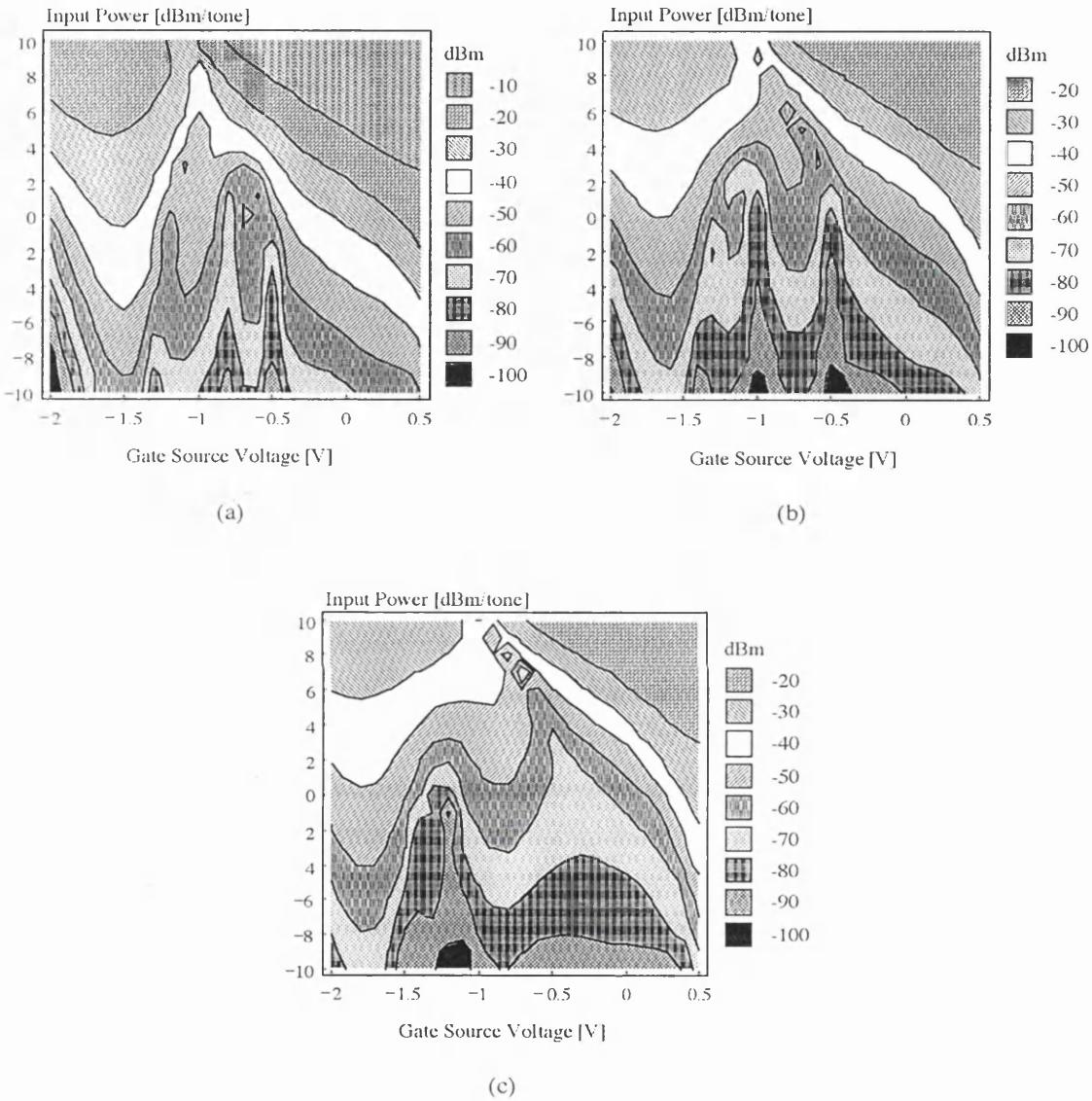

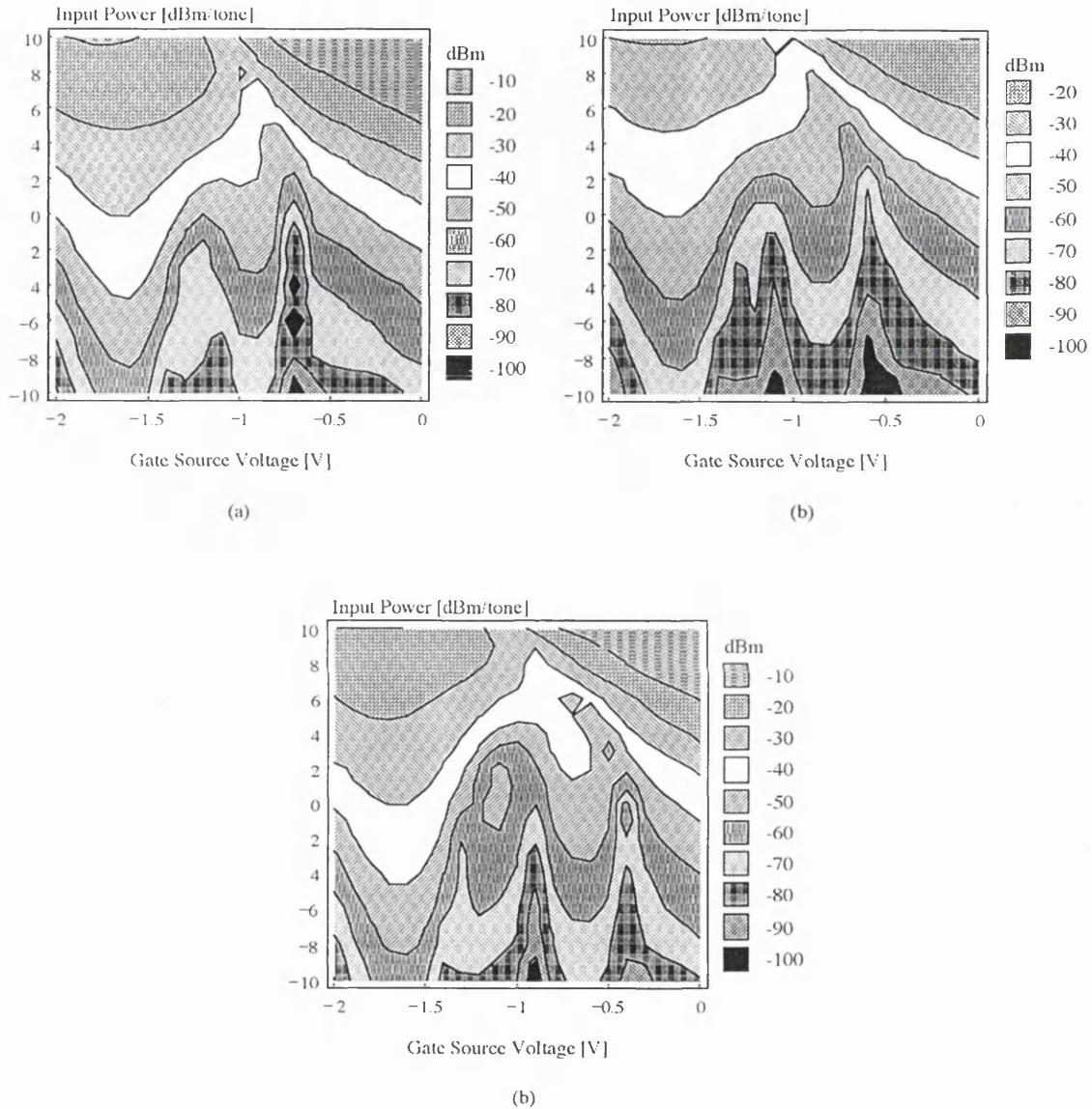

| 7.17 Simulated contour plots of the spectral regrowth for the reference FET and the DS amplifier; (a) reference FET and (b) composite circuit. 1 dB compression points of the reference FET and the composite circuit are 10.6 dBm and 12.0 dBm, respectively. . . . .                                                         | 186 |

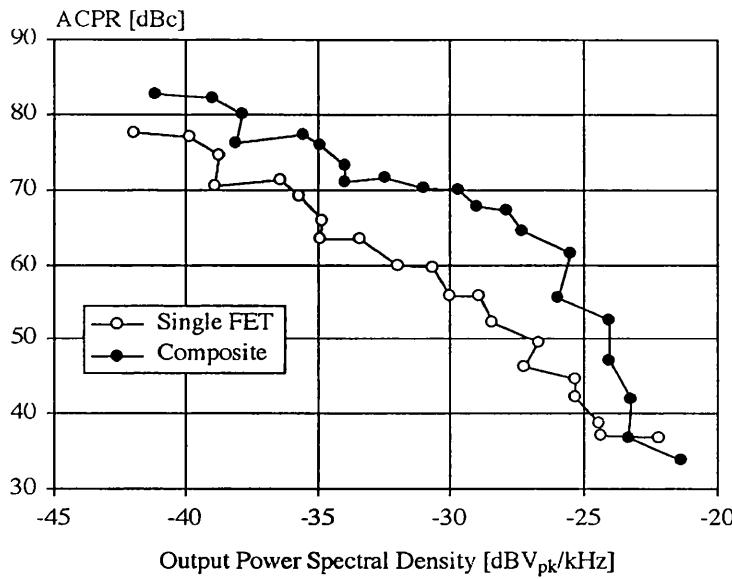

| 7.18 Simulated ACPR of the reference FET and the DS amplifier. . . . .                                                                                                                                                                                                                                                         | 187 |

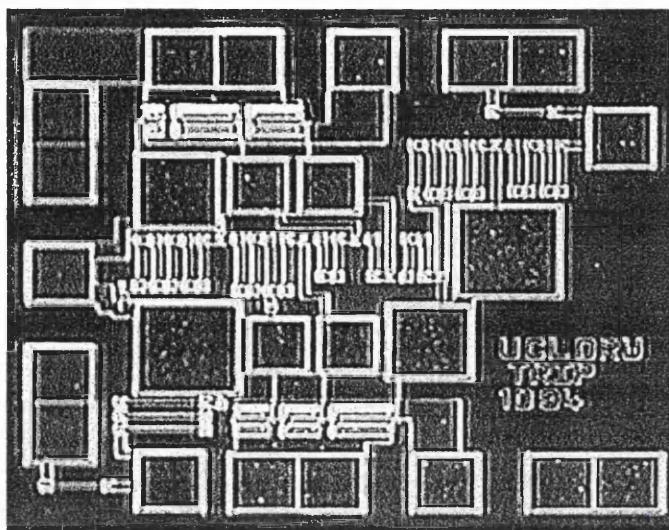

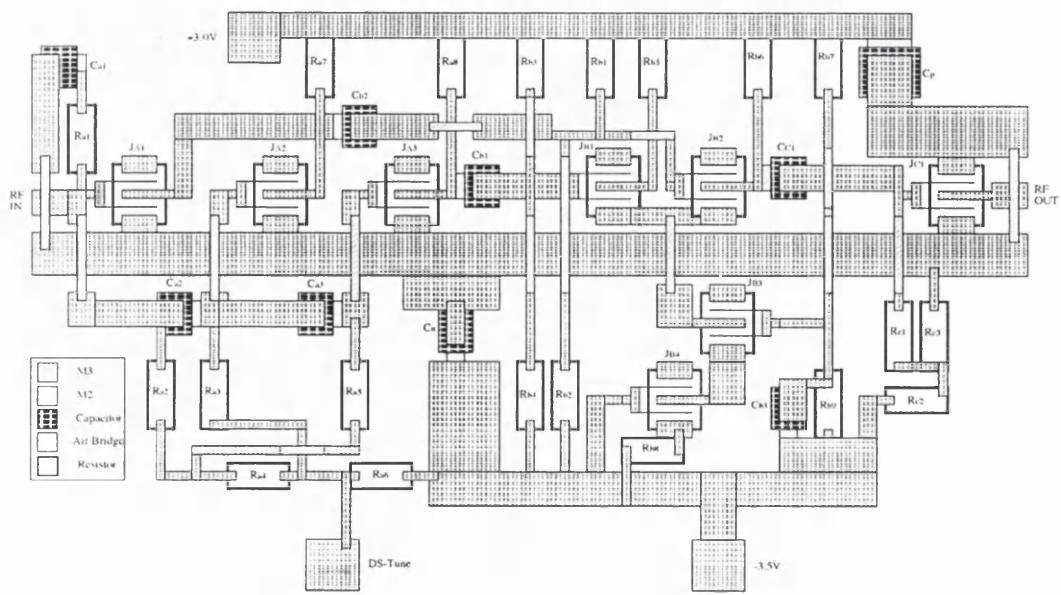

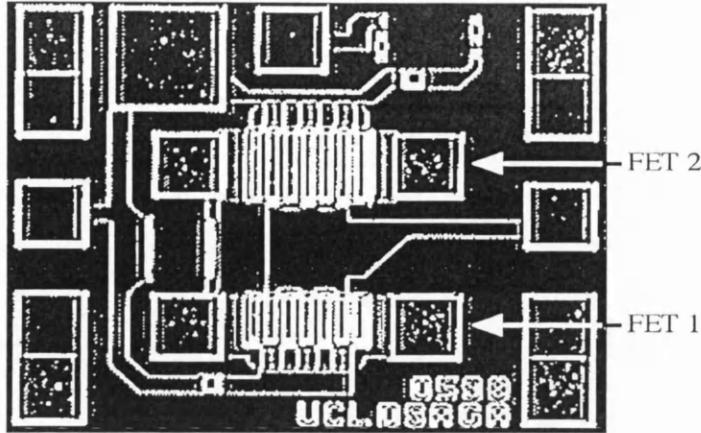

| 7.19 Photograph of the MMIC DS power amplifier. . . . .                                                                                                                                                                                                                                                                        | 188 |

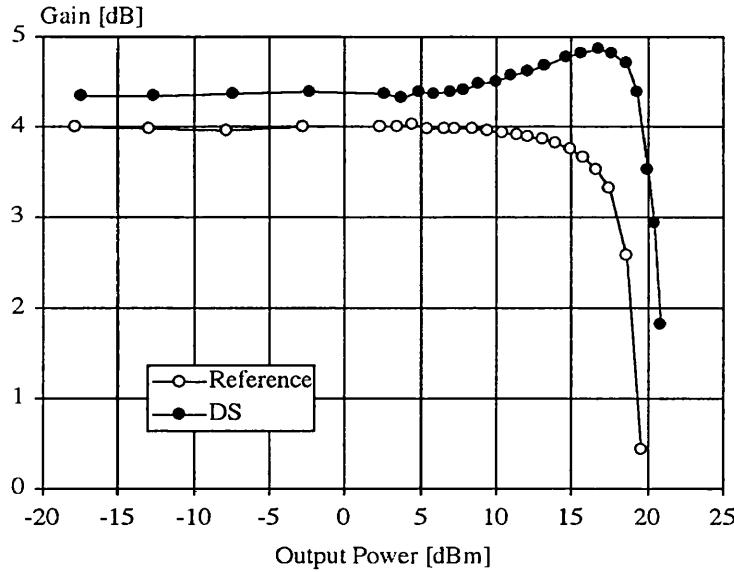

| 7.20 Measured variation of gain as a function of output power for the reference FET and the derivative superposition amplifier. . . . .                                                                                                                                                                                        | 189 |

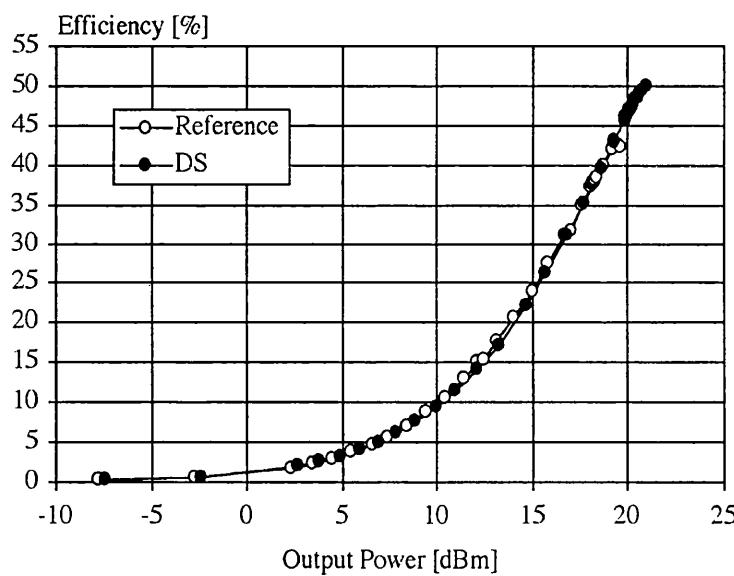

| 7.21 Measured single tone efficiency as a function of output power for the reference FET and the derivative superposition amplifier. . . . .                                                                                                                                                                                   | 189 |

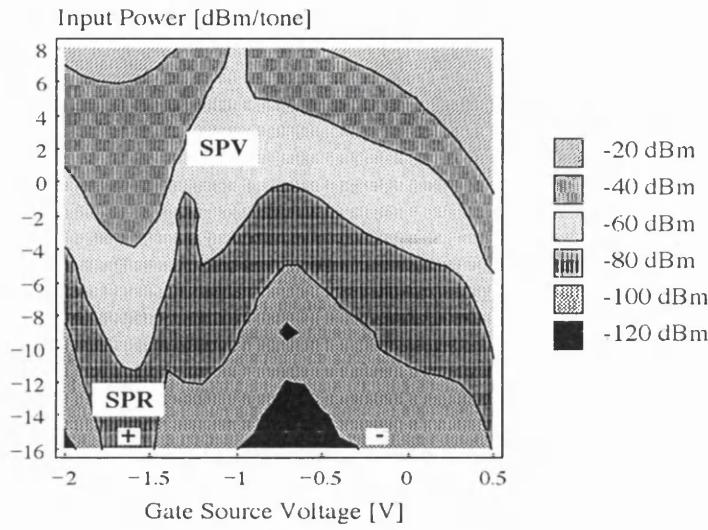

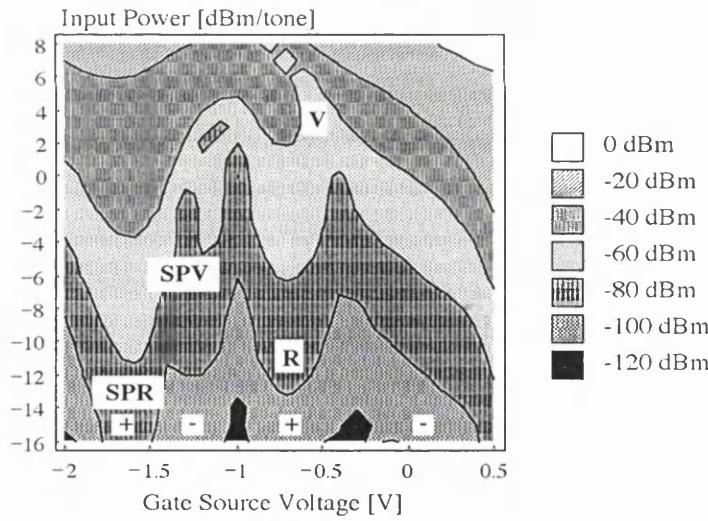

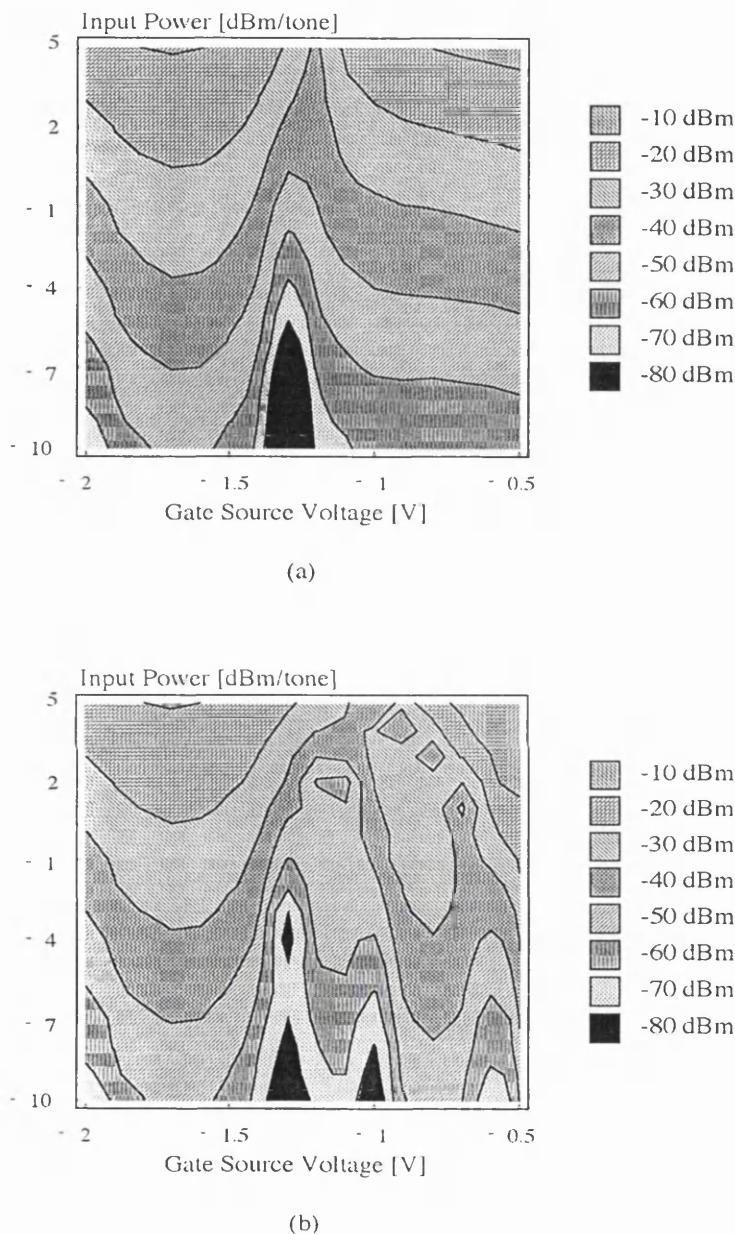

| 7.22 Measured contour plot of the 3rd order intermodulation distortion with gate source voltage and input power level; (a) reference FET and (b) derivative superposition amplifier. $V_{GS} = -0.75V$ , offset= $-0.8V$ , $V_{DS} = 4V$ and $R_{Load} = 50\Omega$ . . . . .                                                   | 190 |

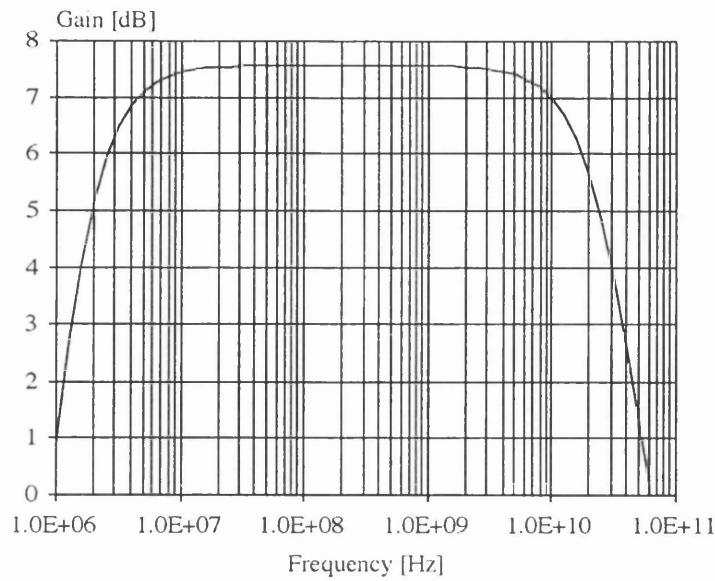

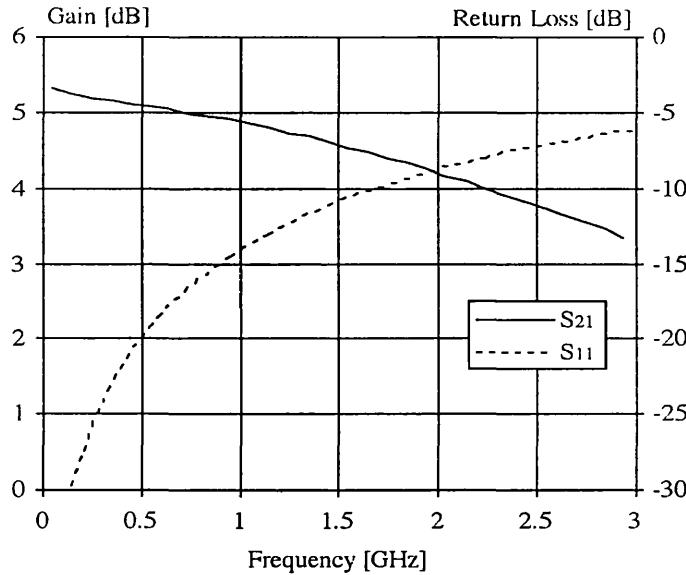

| 7.23 Measured frequency response of the derivative superposition amplifier.                                                                                                                                                                                                                                                    | 191 |

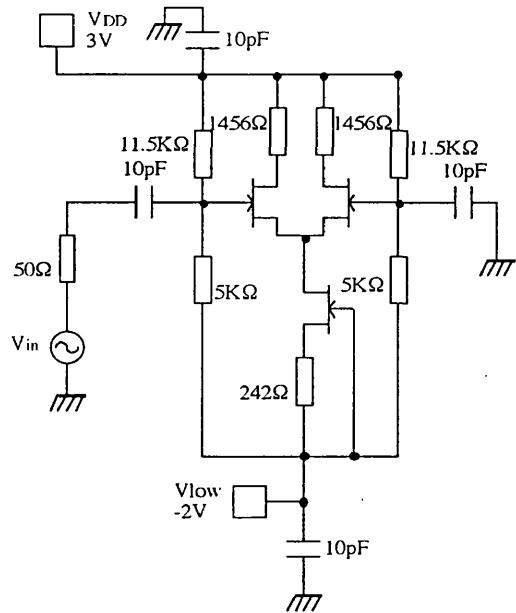

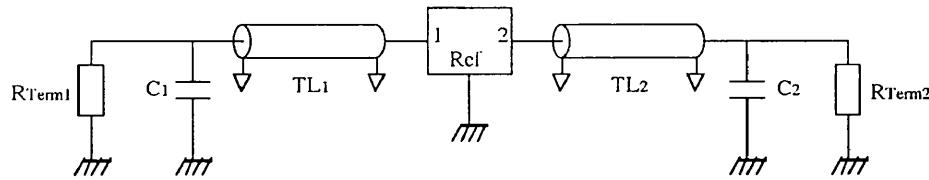

| 7.24 A possible off chip matching network for the DS power amplifier. .                                                                                                                                                                                                                                                        | 192 |

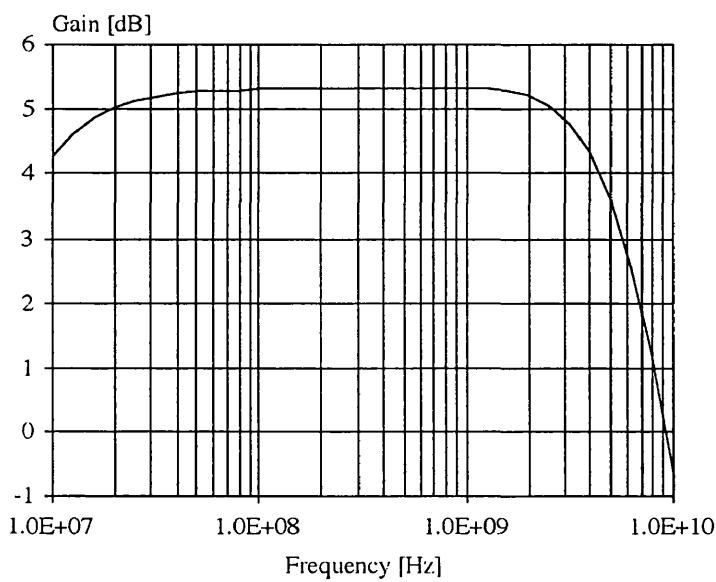

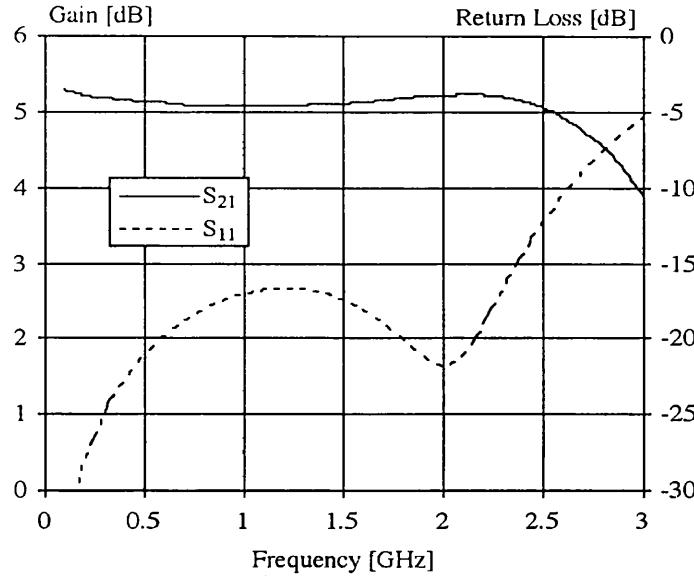

| 7.25 Response of the DS power amplifier with the designed matching network. . . . .                                                                                                                                                                                                                                            | 193 |

|                                                                                                                                                                                                                                                                                   |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

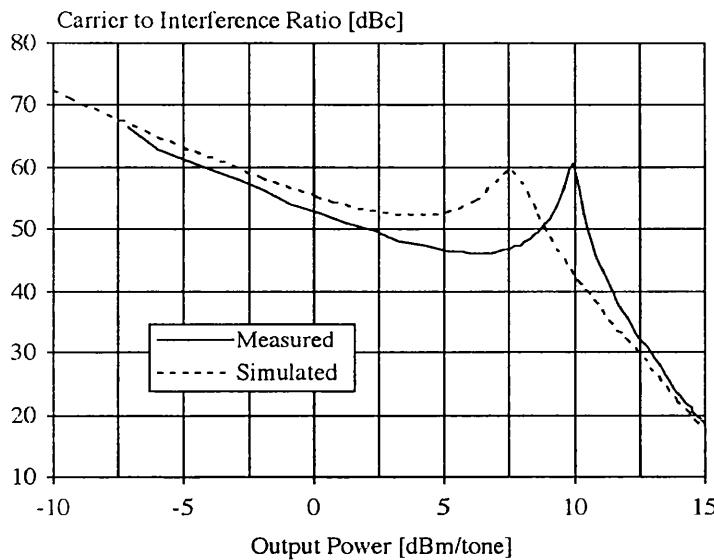

| 7.35 Measured and simulated (at 470 MHz and 480 MHz) c/i comparison of the DS amplifier. . . . .                                                                                                                                                                                  | 202 |

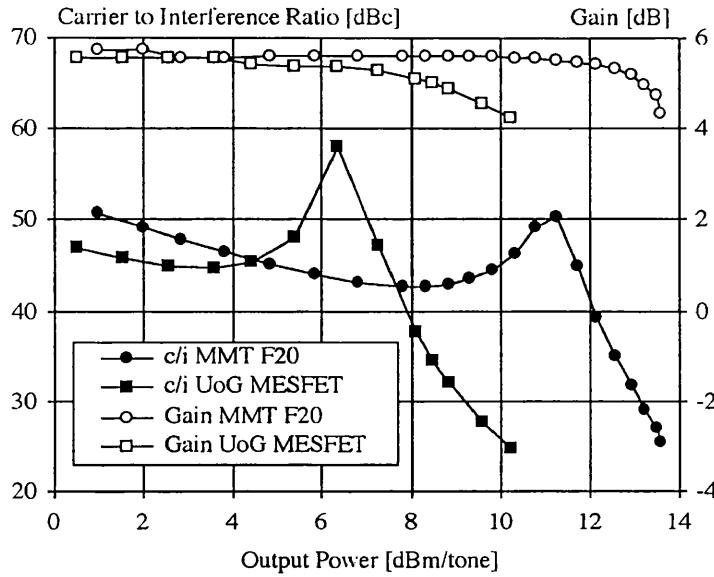

| 7.36 Measured (at 20 and 29.3 MHz) small signal intermodulation distortion of the DS amplifier using UoG MONOFAST MESFET process. . . . .                                                                                                                                         | 203 |

| 7.37 Measured (at 20 MHz and 29.3 MHz) contour plot of the 3rd order intermodulation distortion with gate source voltage and input power level; (a) reference FET and (b) DS amplifier using the UoG MONOFAST MESFET process. . . . .                                             | 205 |

| 7.38 Measured two tone c/i and gain (at 20 and 29.3 MHz) as a function of output power for the reference FET and the DS amplifier using UoG MONOFAST MESFET process. . . . .                                                                                                      | 206 |

| 7.39 Measured (at 20 MHz and 29.3 MHz) gain and c/i responses of the two DS amplifiers using different processing technologies. Load resistance of the DS amplifier using MMT F20 process is $50 \Omega$ and the DS amplifier using UoG MESFET process is $32.2 \Omega$ . . . . . | 207 |

| 7.40 Schematic diagram of the Doherty-DS composite structure. . . . .                                                                                                                                                                                                             | 208 |

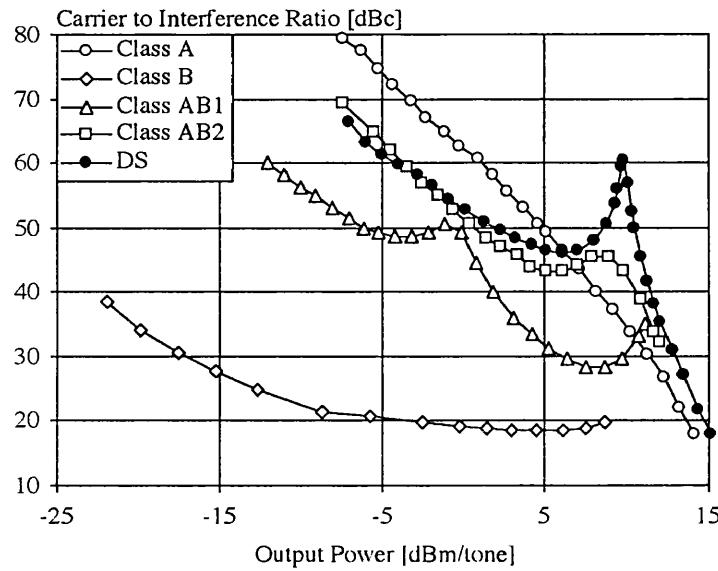

| 7.41 Simulated c/i versus output power responses of a reference FET, the Doherty circuit, the DS circuit and the composite Doherty-DS circuit. . . . .                                                                                                                            | 208 |

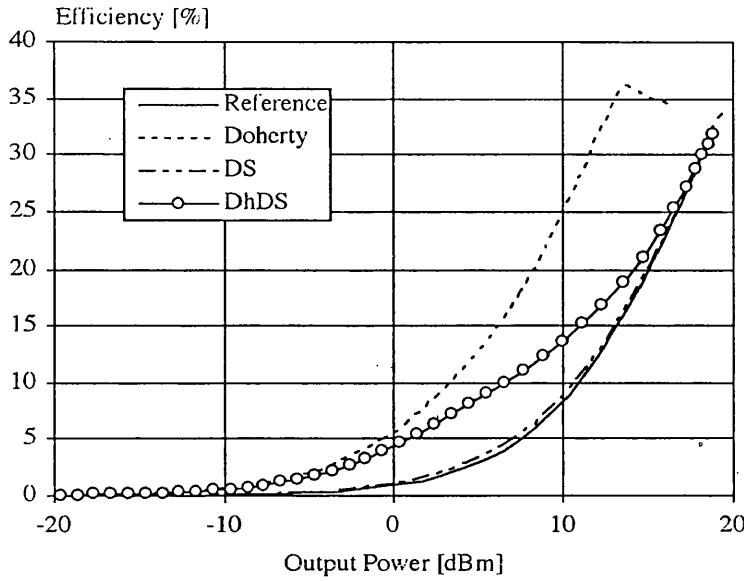

| 7.42 Simulated efficiency comparison of the reference FET, Doherty amplifier, DS amplifier and Doherty-DS composite structure. . . . .                                                                                                                                            | 210 |

| 8.1 The schematic diagram of the derivative superposition structure for implementing a frequency tripler. . . . .                                                                                                                                                                 | 216 |

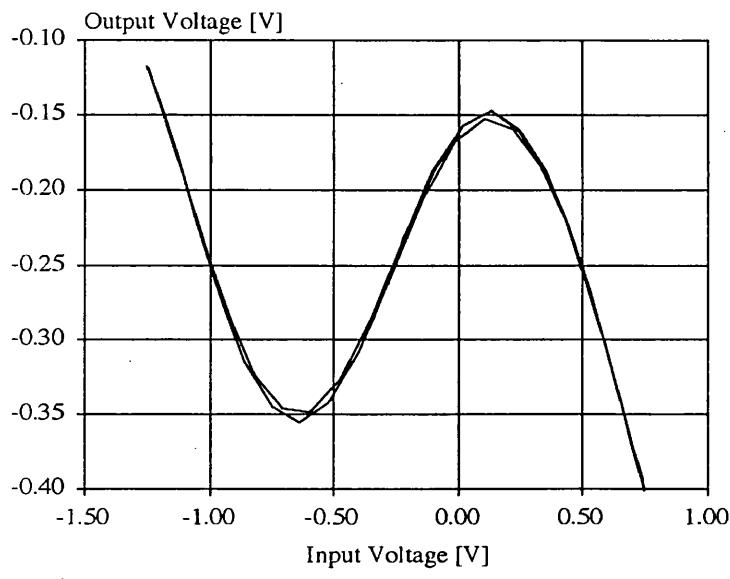

| 8.2 Simulated response of the DS section. (a) The dynamic transfer characteristic and (b) time domain response. . . . .                                                                                                                                                           | 217 |

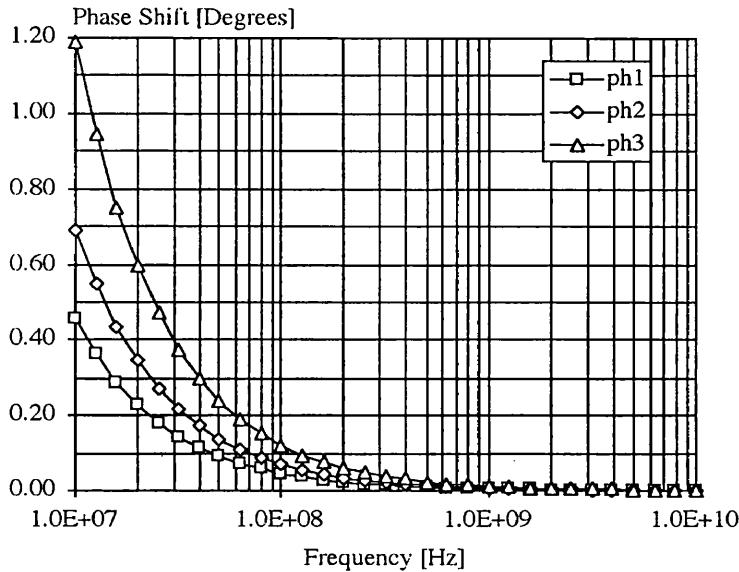

| 8.3 The phase shifts between the gates of the transistors of the DS section. $ph_1$ , $ph_2$ and $ph_3$ represents the phase shifts on the gates of the transistors $J_{A1}$ , $J_{A2}$ and $J_{A3}$ of Figure 8.1, respectively. . . . .                                         | 220 |

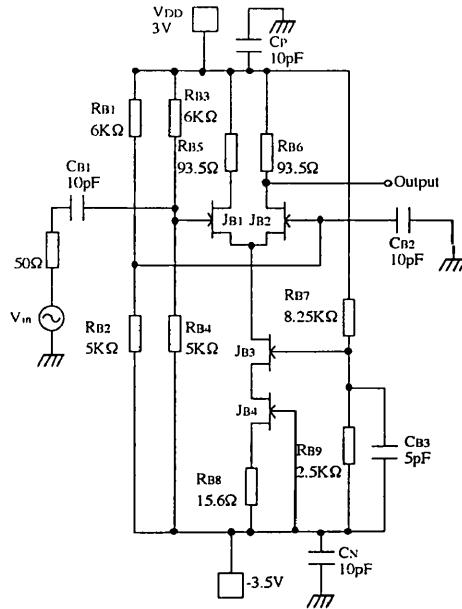

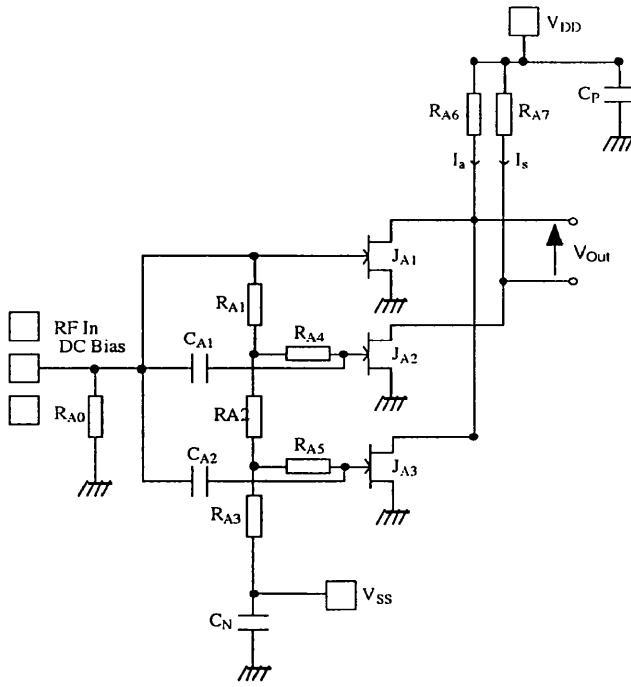

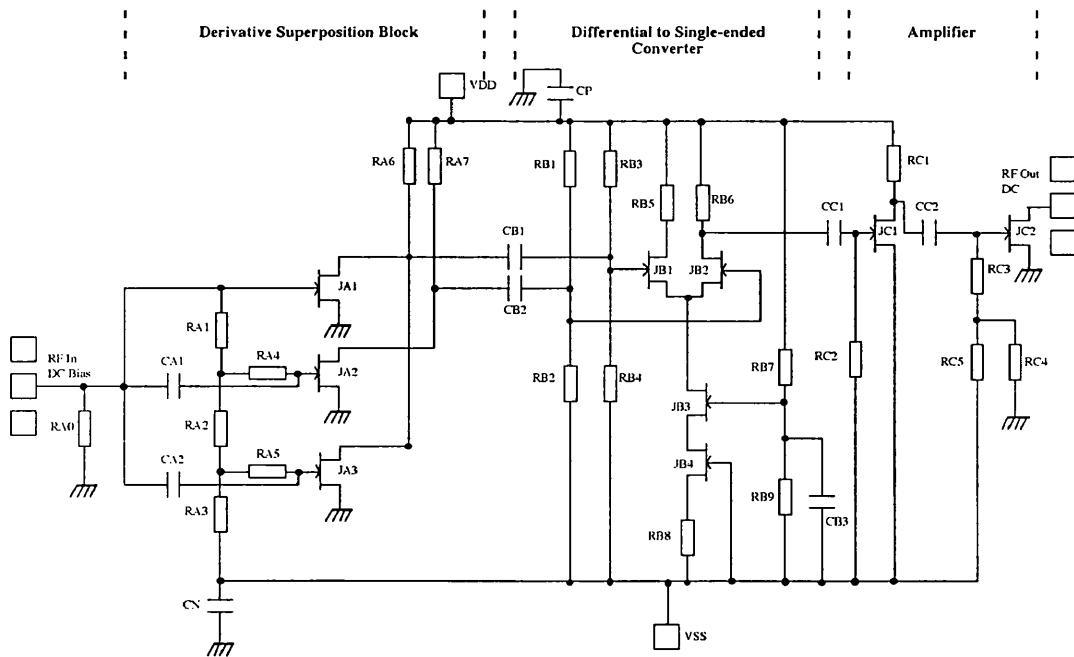

| 8.4 The schematic diagram of the entire DS frequency tripler circuit. . . . .                                                                                                                                                                                                     | 220 |

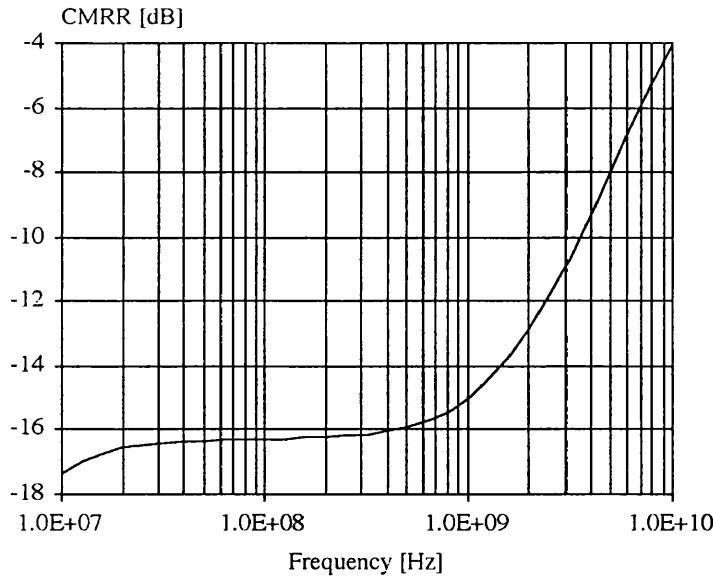

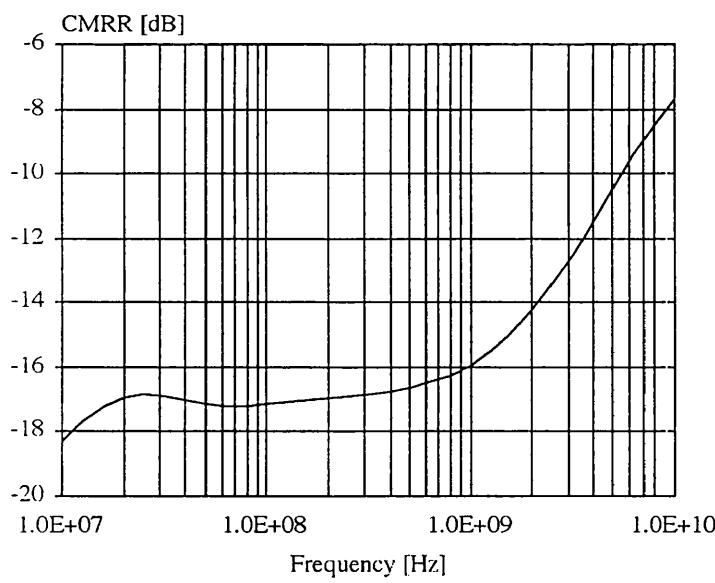

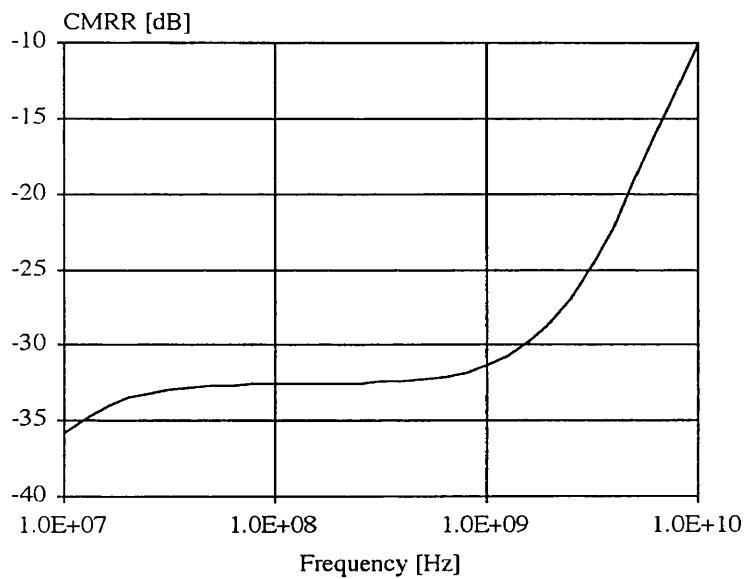

| 8.5 The CMRR of the differential pair section. . . . .                                                                                                                                                                                                                            | 221 |

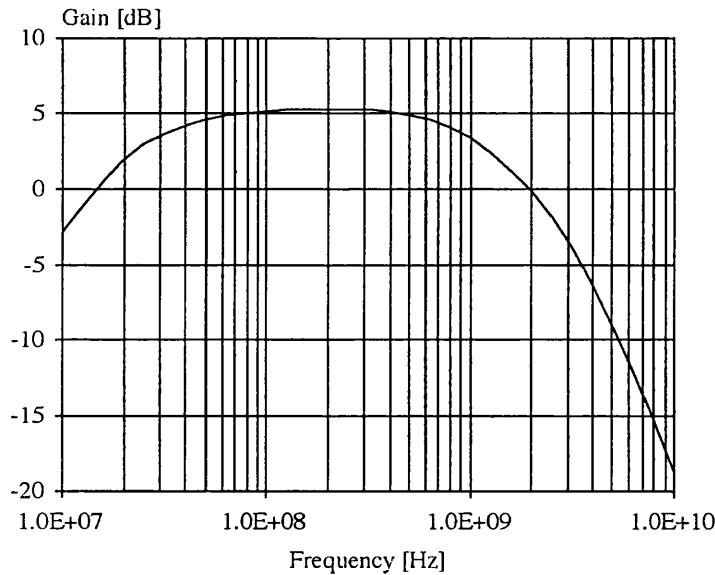

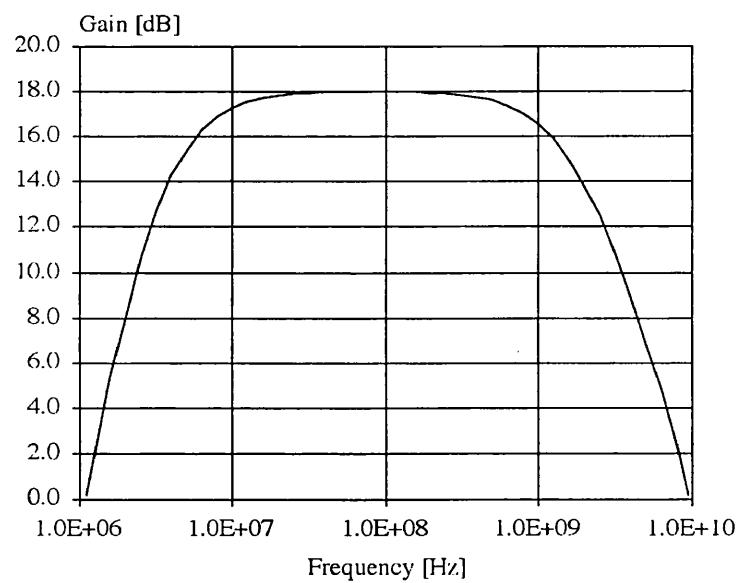

| 8.6 The gain response of the two stage driver amplifier. . . . .                                                                                                                                                                                                                  | 221 |

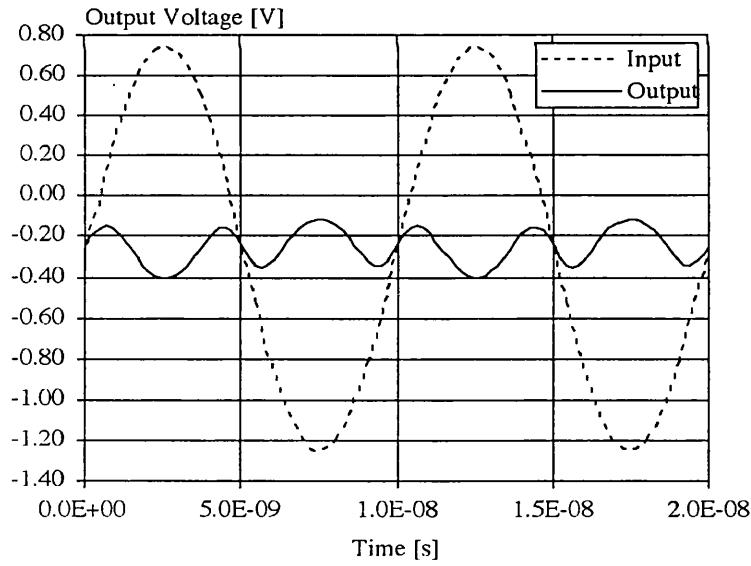

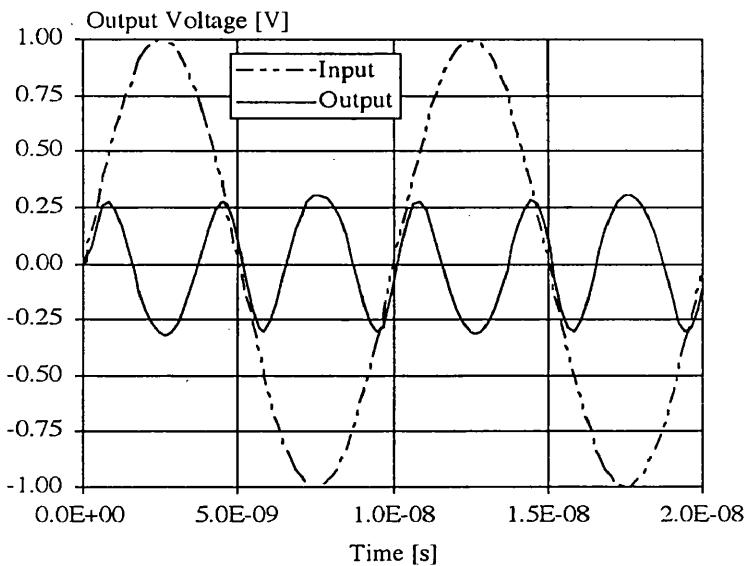

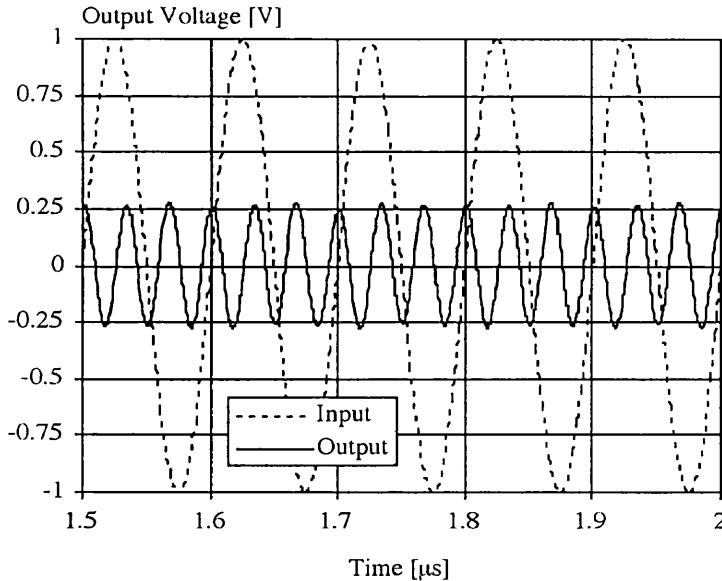

| 8.7 Simulated time domain responses of the entire circuit; (a) at 100 MHz input and (b) at 1 GHz input. . . . .                                                                                                                                                                   | 223 |

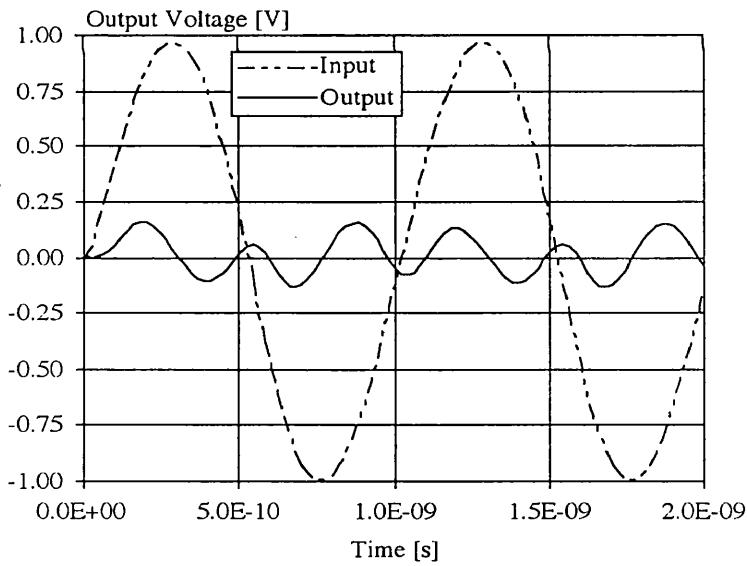

| 8.8 Simulated harmonic distortion (hd) versus input signal amplitude for the entire circuit; (a) at 100 MHz input and (b) at 1 GHz input. . . . .                                                                                                                                 | 224 |

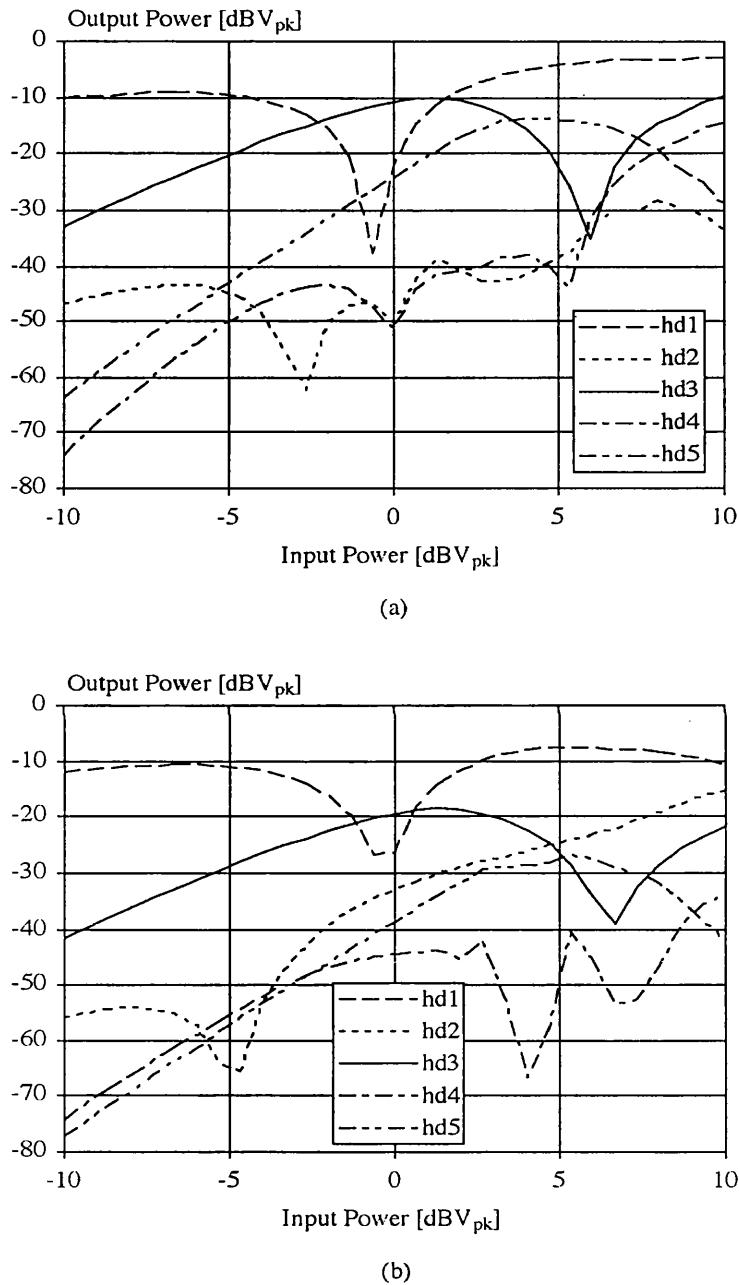

| 8.9 Photograph of the MMIC DS frequency tripler. . . . .                                                                                                                                                                                                                          | 225 |

|                                                                                                                                                                                                                 |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

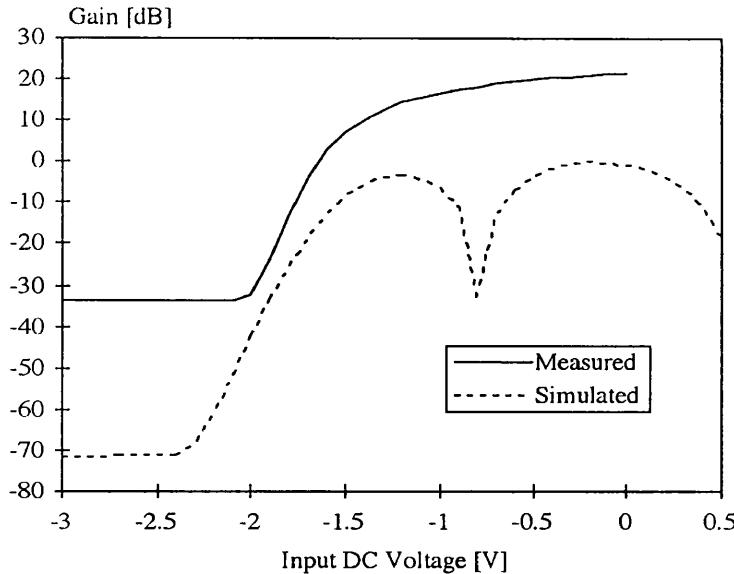

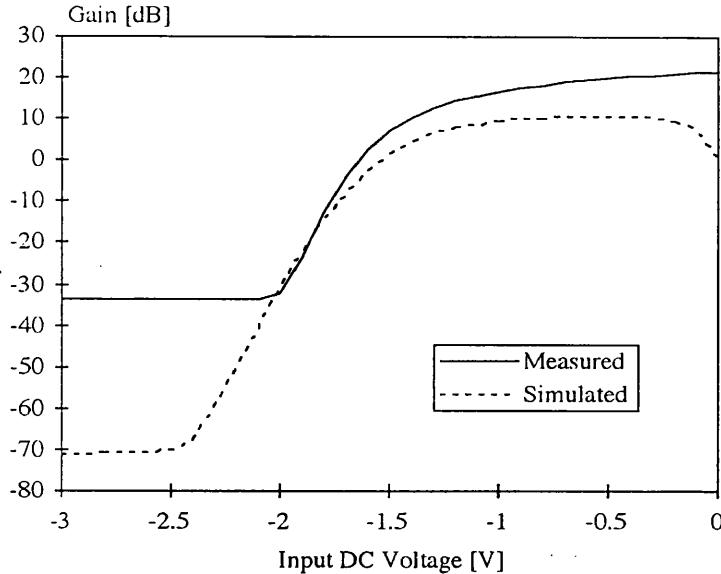

| 8.10 Measured and simulated comparison of the small signal gain of the MMIC frequency tripler. . . . .                                                                                                          | 226 |

| 8.11 Measured and simulated comparison of the small signal gain of the MMIC frequency tripler. Note that in the simulation the capacitor $C_{A2}$ of Figure 8.4 is short circuited. . . . .                     | 227 |

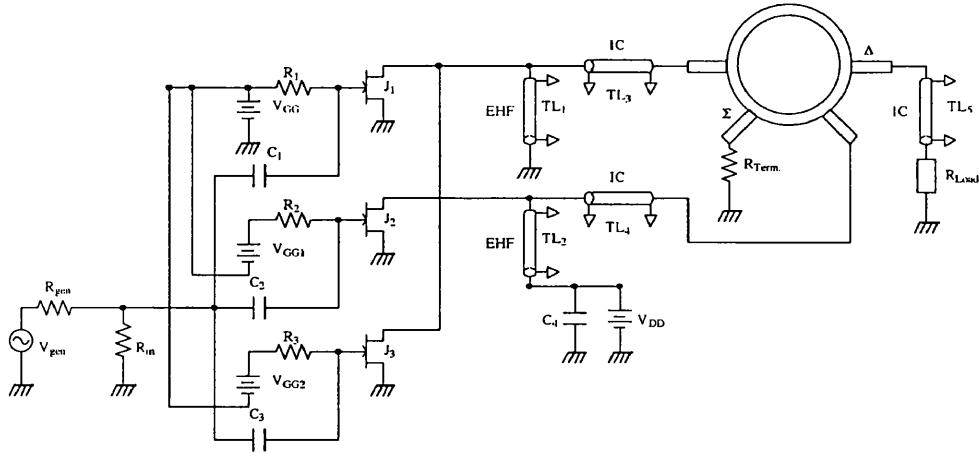

| 8.12 Schematic circuit diagram of the DS frequency tripler for microwave frequencies operation. EHF and IC transmission lines represent Even Harmonic Filters and Impedance Transformers, respectively. . . . . | 228 |

| 8.13 Simulated time domain response of the DS tripler at 1 GHz input. . . . .                                                                                                                                   | 230 |

| 8.14 Simulated harmonic distortion (hd) versus input signal amplitude of the DS tripler; (a) at 100 MHz input and (b) at 1 GHz input. . . . .                                                                   | 231 |