# Novel Architectures for Forward Error Control at Very High Bit Rates

Thesis Submitted in Candidature for the Degree of Doctor of Philosophy

September 1997

Richard Spencer Blake

Department of Electrical and Electronic Engineering

University College London

London

United Kingdom

ProQuest Number: 10106904

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10106904

Published by ProQuest LLC(2016). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code.

Microform Edition © ProQuest LLC.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

# Statement of Originality

The work presented in this thesis was carried out by the candidate. It has not been presented previously for any degree, nor is it at present under consideration by any other degree awarding body.

Candidate:

Richard Spencer Blake.

Director of Studies:

Professor John J. O'Reilly.

# Statement of Availability

I hereby give my consent for my thesis, if accepted, to be available for photocopying and for inter-library loan, and for the title and summary to be made available to outside organisations.

Candidate:

Richard Spencer Blake.

## Acknowledgements

I wish to extend my sincerest thanks to Professor John O'Reilly for his guidance and encouragement during the period of my studies. I would also like to thank him for his help in the preparation of my thesis.

I am also grateful to Dr Andy Popplewell for his informative comments and wealth of knowledge which proved invaluable during the early stages of this work.

Financial support for this research has been provided by the Physical and Engineering Research Council, BT Laboratories Martlesham and Professor John O'Reilly, for which I am very grateful.

Finally I would like to give a special mention to my mother Elizabeth, who has supported and encouraged me throughout my time in academia and Jane for believing in me and above all putting up with me - thank you both.

## Summary

This thesis is concerned with the design and assessment of novel architectures for the implementation of forward error correction (FEC) coding systems for very high bit rate operation. This is motivated by both the development of multi giga-bit (especially optical) transmission systems and the increasingly demanding error performance targets for digital telecommunications. It is shown that present serial FEC architectures are often inadequate for demanding high bit rate applications and can only achieve high data rates by separately encoding and then multiplexing several tributary data streams. Alternatively parallel encoders, whilst offering the prospect of increased operational speed, are often far too complex for all but the most trivial of codes.

To overcome these limitations series-parallel FEC techniques - derived from earlier work on *m*-sequence generation - are introduced and examined. By describing the functional specification of the encoding and error detection circuits in the form of a transition matrix it is possible, by matrix manipulation, to define alternative circuits which allow a trade off between circuit speed and complexity.

Having demonstrated how series-parallel techniques may be applied to high speed encoding and error detection attention is then focused on error correction. By taking advantage of transmission channel statistics and using high speed error detection, a buffered decoding arrangement is explored which is shown to operate at an average, rather than the worst case, speed. This decoder, used in conjunction with series-parallel encoding and error detection circuits, can provide the basis for the realisation of a complete high speed FEC system.

The thesis then concludes with an illustrative case study concerning the benefits of employing FEC to a new generation of long haul optically amplified submarine systems. Currently proposed error control strategies are reviewed; a comparison is effected with low complexity binary BCH codes which may be realised at the system line rate using the architectures and arrangements developed in this thesis.

# Contents

| 1 | Intr | roduction                             | 11 |

|---|------|---------------------------------------|----|

|   | 1.1  | Motivation and Background             | 11 |

|   | 1.2  | Thesis organisation                   | 12 |

|   | 1.3  | Summary of Main Contributions         | 14 |

|   | 1.4  | Summary                               | 15 |

| 2 | Err  | or Control Coding                     | 16 |

|   | 2.1  | Introduction                          | 16 |

|   | 2.2  | Error Control Coding                  | 17 |

|   | 2.3  | Classification of error control codes | 18 |

|   | 2.4  | Block Codes                           | 19 |

|   |      | 2.4.1 Cyclic Codes                    | 22 |

|   |      | 2.4.2 Systematic Codes                                                                                          | 3              |

|---|------|-----------------------------------------------------------------------------------------------------------------|----------------|

|   | 2.5  | Polynomial Representation of Codes                                                                              | <b>4</b>       |

|   | 2.6  | BCH Codes                                                                                                       | 24             |

|   |      | 2.6.1 Binary Codes                                                                                              | 25             |

|   |      | 2.6.2 Non-Binary Codes                                                                                          | 9              |

|   | 2.7  | Decoding of Linear Block Codes                                                                                  | 80             |

|   | 2.8  | Summary                                                                                                         | 32             |

| 3 | Stai | ndard Encoding and Error Detection Methods 33                                                                   | 3              |

|   | 3.1  | Introduction                                                                                                    | 3              |

|   |      |                                                                                                                 |                |

|   | 3.2  | Standard Encoding Architectures                                                                                 | 84             |

|   | 3.2  | Standard Encoding Architectures                                                                                 |                |

|   | 3.2  | 3.2.1 Serial Encoding                                                                                           |                |

|   | 3.2  | 3.2.1 Serial Encoding                                                                                           | 84             |

|   |      | 3.2.1 Serial Encoding                                                                                           | 34<br>46       |

| 4 | 3.3  | 3.2.1 Serial Encoding 3   3.2.2 Parallel Encoding Architectures 4   Error Detection Architectures 5   Summary 5 | 34<br>46<br>50 |

|   | 4.2                               | Series-Parallel Architectures                                                                                                                   | 5                |

|---|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|   |                                   | 4.2.1 $m$ -sequence Generation                                                                                                                  | 5                |

|   |                                   | 4.2.2 Series-Parallel Code Generation 6                                                                                                         | 1                |

|   |                                   | 4.2.3 Generator polynomial based circuits 6                                                                                                     | 2                |

|   |                                   | 4.2.4 Parity polynomial based circuits                                                                                                          | 2                |

|   |                                   | 4.2.5 Series-parallel error detection                                                                                                           | 8                |

|   | 4.3                               | Results                                                                                                                                         | 2                |

|   | 4.4                               | Summary 8                                                                                                                                       | 9                |

|   |                                   |                                                                                                                                                 |                  |

| 5 | Buf                               | ered Decoding 9                                                                                                                                 | 1                |

| 5 | <b>Buf</b> 5.1                    | ered Decoding         9           Introduction                                                                                                  |                  |

| 5 |                                   |                                                                                                                                                 | 1                |

| 5 | 5.1                               | Introduction                                                                                                                                    | 1                |

| 5 | <ul><li>5.1</li><li>5.2</li></ul> | Introduction                                                                                                                                    | 1 2 5            |

| 5 | <ul><li>5.1</li><li>5.2</li></ul> | Introduction       9         Buffered Decoding       9         Approximations of Buffer Length       9                                          | 1<br>2<br>5      |

| 5 | <ul><li>5.1</li><li>5.2</li></ul> | Introduction       9         Buffered Decoding       9         Approximations of Buffer Length       9         5.3.1 Worst case decoder       9 | 1<br>2<br>5<br>6 |

|   | 5.5 | Performance Impact                                 | 105 |

|---|-----|----------------------------------------------------|-----|

|   | 5.6 | Buffered Decoding using a standard RS decoder      | 109 |

|   | 5.7 | Approximations of Buffer Length and Decoding Speed | 111 |

|   |     | 5.7.1 Worst Case Decoder                           | 111 |

|   |     | 5.7.2 Optimised Decoding                           | 112 |

|   | 5.8 | Summary                                            | 115 |

| 6 | FEC | C applications study: High speed optical systems   | 117 |

|   | 6.1 | Introduction                                       | 117 |

|   | 6.2 | Transmission Impairments                           | 118 |

|   | 6.3 | Optically amplified submarine networks             | 121 |

|   | 6.4 | Current Proposal                                   | 124 |

|   | 6.5 | System Requirement                                 | 126 |

|   | 6.6 | ARQ Systems                                        | 127 |

|   | 6.7 | Low Complexity BCH Codes                           | 128 |

|   | 6.8 | Summary                                            | 129 |

| 7 | Con  | clusions 1                                         | 31  |

|---|------|----------------------------------------------------|-----|

|   | 7.1  | Research Outcomes                                  | 132 |

|   |      | 7.1.1 Series-parallel architectures                | 132 |

|   |      | 7.1.2 Buffered decoding                            | 133 |

|   |      | 7.1.3 FEC in long haul optically amplified systems | 134 |

|   | 7.2  | Summary of Thesis                                  | 135 |

|   | 7.3  | Suggestions for Further Work                       | 137 |

| A | Gal  | ois Field Arithmetic 1                             | .38 |

| В | Intr | oduction 1                                         | .42 |

|   | B.1  | Newton-Raphson Algorithm                           | 142 |

# List of Figures

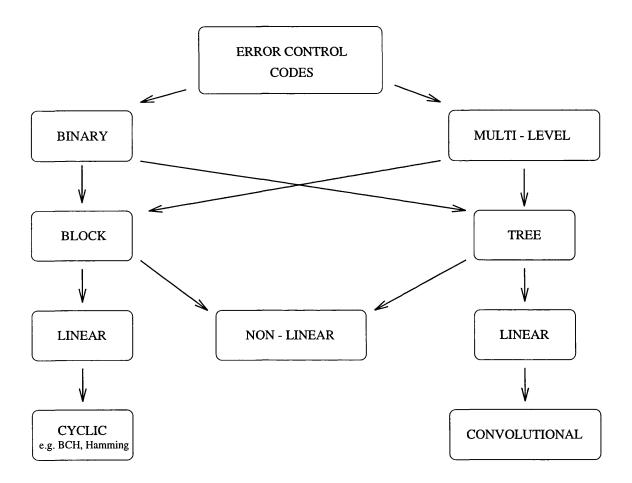

| 2.1 | Hierarchy of error control codes                                | 18 |

|-----|-----------------------------------------------------------------|----|

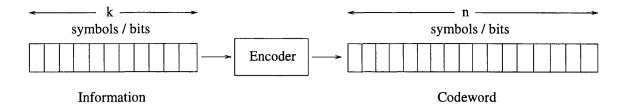

| 2.2 | Encoding procedure                                              | 20 |

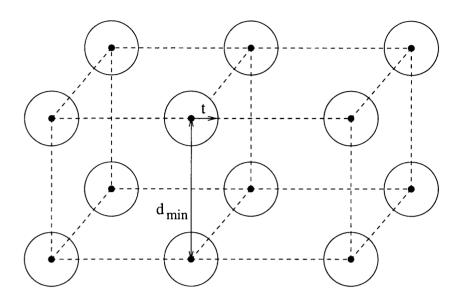

| 2.3 | Symbolic representation of a codeword set                       | 22 |

| 2.4 | Systematic format of a codeword                                 | 23 |

| 3.1 | Multiply by $g(X)$ circuit                                      | 36 |

| 3.2 | Multiply by $X^3 + X + 1$ circuit                               | 37 |

| 3.3 | Polynomial division encoder based on generator polynomial       | 39 |

| 3.4 | Systematic (7,4) Hamming encoder based on the generator polyno- |    |

|     | mial $g(X) = 1 + X + X^3$                                       | 40 |

| 3.5 | Systematic encoder based on parity polynomial                   | 42 |

| 3.6 | (7,4) Hamming encoder based on parity polynomial                | 43 |

| 3.7 | Parallel (7,4) Hamming Encoder                                  | 47 |

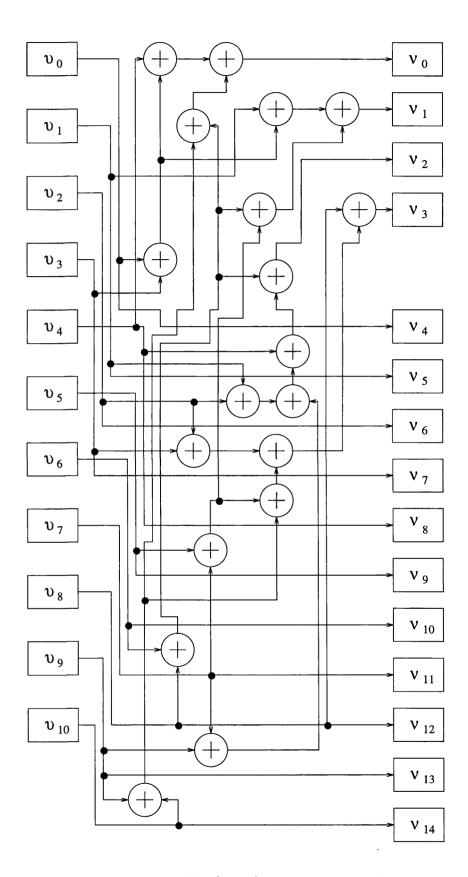

| 3.8  | Parallel (15,11) Hamming Encoder                                                                                                          | 49       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----------|

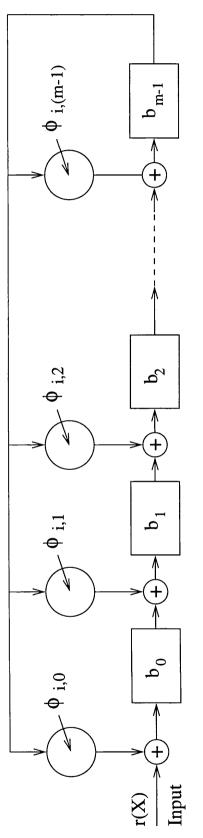

| 3.9  | Polynomial division based on the minimal polynomial $\Phi_i(X) = \phi_{i,0} + \phi_{i,1}X + \phi_{i,2}X^2 + + \phi_{i,m-1}X^{m-1}.     .$ | 51       |

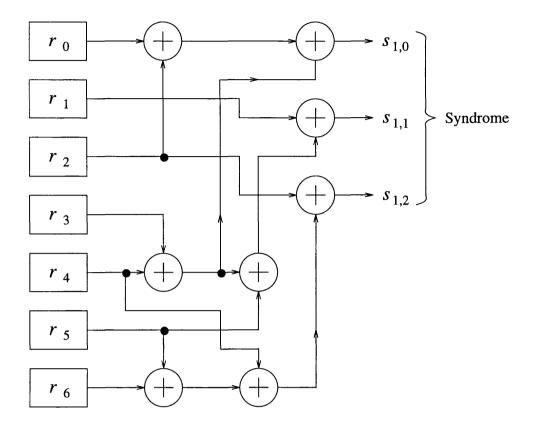

| 3.10 | Parallel syndrome calculation circuit                                                                                                     | 53       |

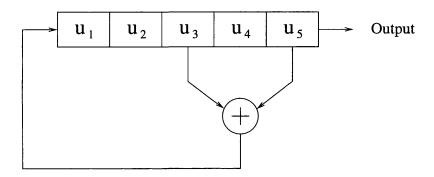

| 4.1  | Serial <i>m</i> -sequence generator                                                                                                       | 57       |

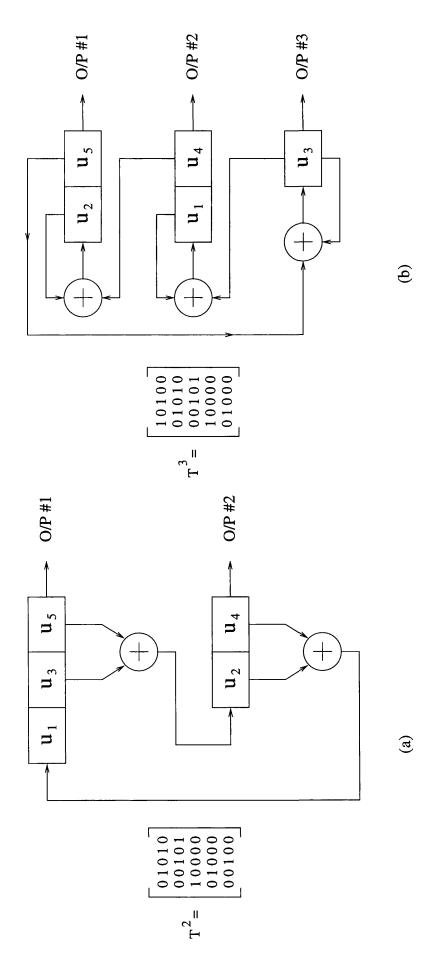

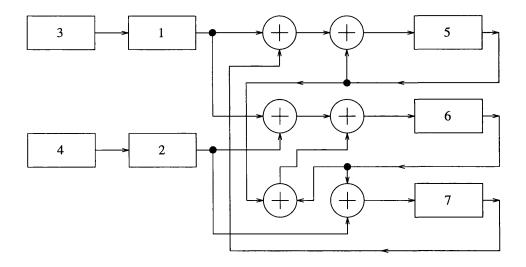

| 4.2  | Illustrative examples of series-parallel $m$ -sequence generation based                                                                   |          |

|      | on $T^2$ and $T^3$                                                                                                                        | 59       |

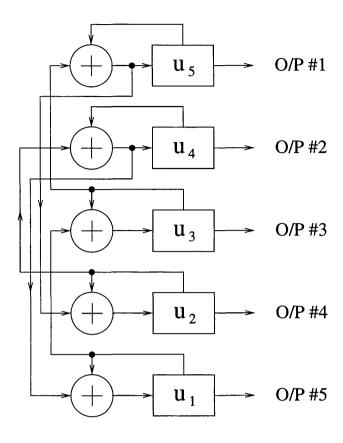

| 4.3  | Parallel <i>m</i> -sequence generator                                                                                                     | 61       |

| 4.4  | Autonomous circuit view of a serial encoder based on the generator                                                                        |          |

|      | polynomial                                                                                                                                |          |

| 4.5  | Serial Hamming (7,4) encoder                                                                                                              |          |

| 4.6  | Series-parallel (7,4) Hamming encoder                                                                                                     |          |

| 4.7  | Parallel Hamming (7,4) encoder                                                                                                            |          |

| 4.8  | General form of intermediate circuit.                                                                                                     | 70       |

| 4.9  | Autonomous view of a serial encoder based on the parity polynomial                                                                        | <b>-</b> |

|      | h(X)                                                                                                                                      |          |

|      | Serial Hamming (7,4) encoder based on $h(X) = 1 + X + X^2 + X^4$ .                                                                        |          |

| 4.11 | Series-parallel parity polynomial encoder based on $T^2$                                                                                  | 15       |

| nous view of a standard syndrome calculation circuit 79                                                         | 4.12 |

|-----------------------------------------------------------------------------------------------------------------|------|

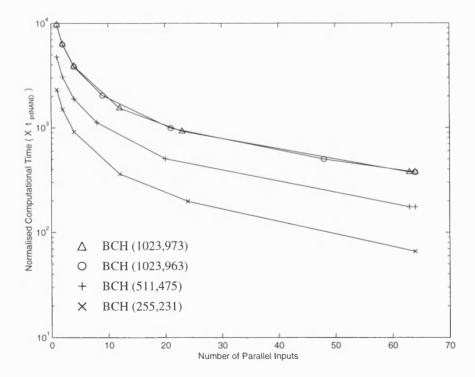

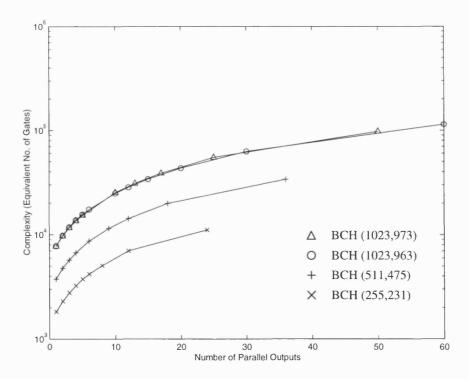

| ational time vs. degree of parallelism - generator polynomial coders                                            | 4.13 |

| ational time vs. degree of parallelism $\leq 64$ - generator polyased encoders                                  | 4.14 |

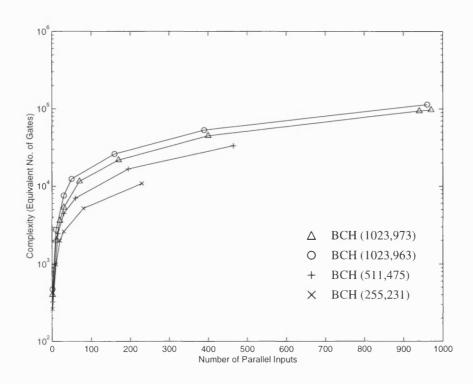

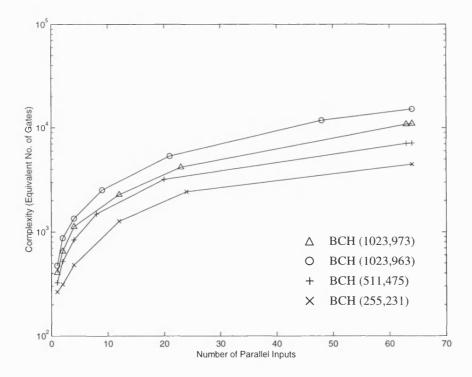

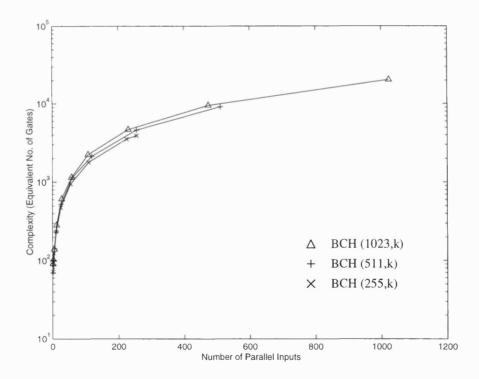

| ity vs. degree of parallelism - generator polynomial based                                                      | 4.15 |

| ty vs. degree of parallelism ≤ 64 - generator polynomial coders                                                 |      |

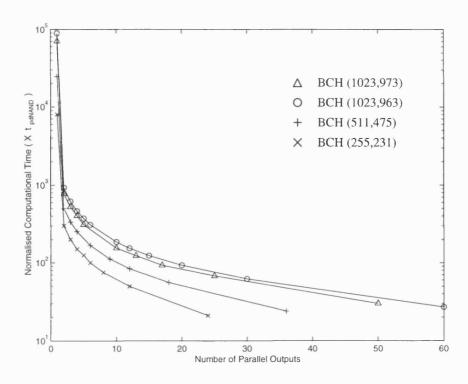

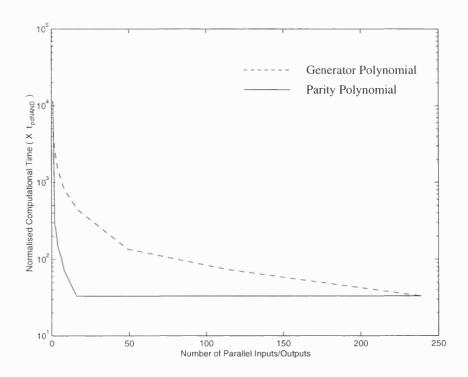

| ational time vs. degree of parallelism - parity polynomial coders                                               | 4.17 |

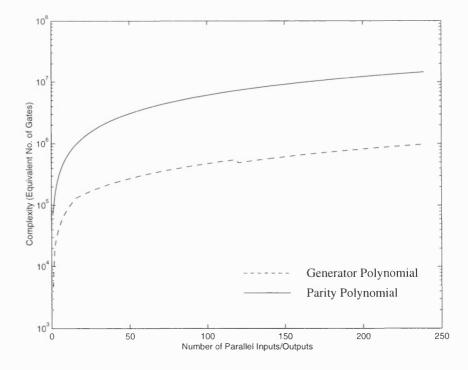

| ity vs. degree of parallelism - parity polynomial based en-                                                     | 4.18 |

| ative analysis of computational time between generator and olynomial based encoders for the RS(255,239) code 86 | 4.19 |

| ative analysis of circuit complexity between generator and olynomial based encoders for the RS(255,239) code 86 | 4.20 |

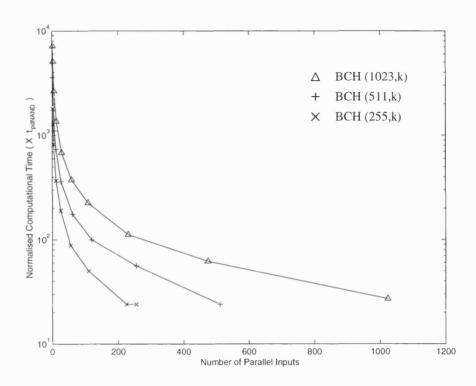

| ational time vs. degree of parallelism - syndrome calculation                                                   | 4.21 |

| city vs. degree of parallelism - syndrome calculation circuits 87                                               | 4.22 |

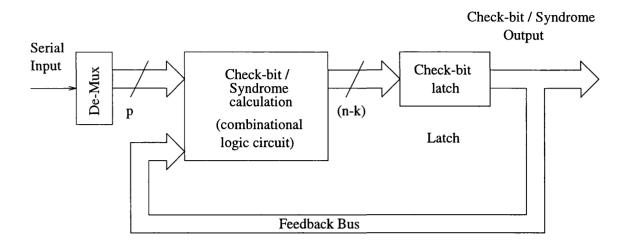

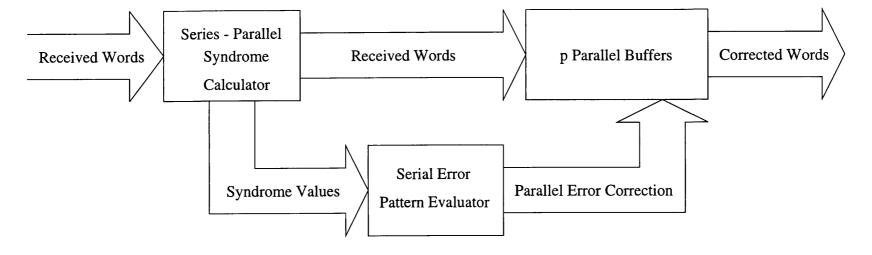

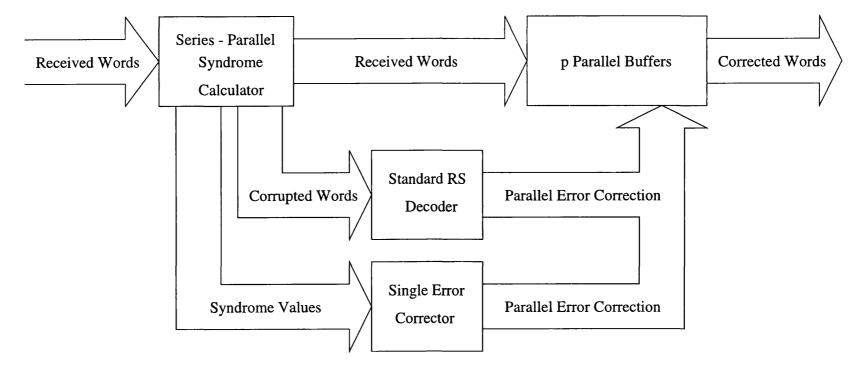

| 5.1  | Buffered decoding system incorporating series-parallel error detection. 93 |

|------|----------------------------------------------------------------------------|

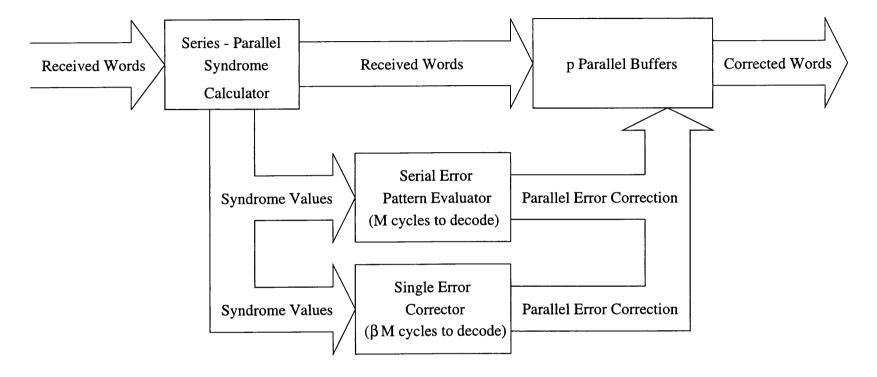

| 5.2  | Optimised buffered decoding system                                         |

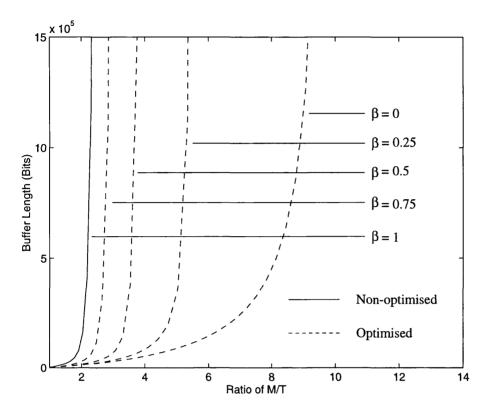

| 5.3  | Buffer lengths as functions of $M/T$ and $\beta$                           |

| 5.4  | Optimised buffered decoding system                                         |

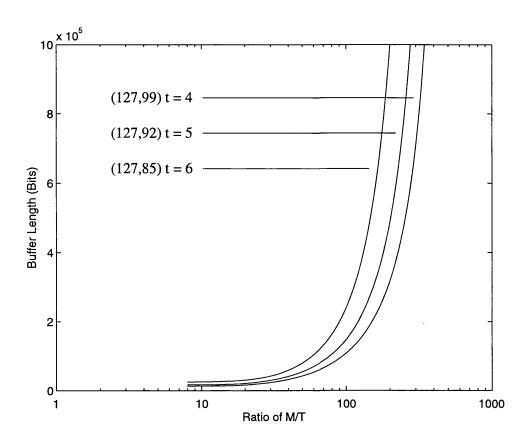

| 5.5  | Buffer length vs $M/T$ for $(127, k)$ codes                                |

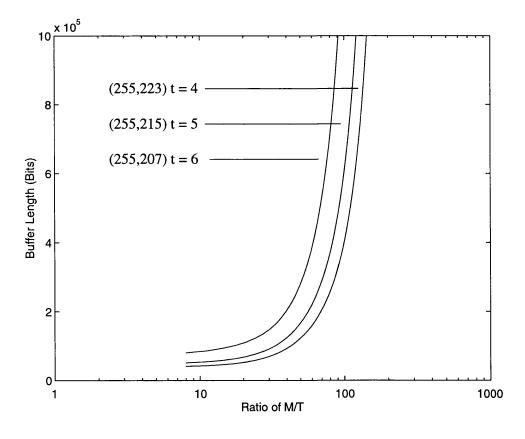

| 5.6  | Buffer length vs $M/T$ for $(225, k)$ codes                                |

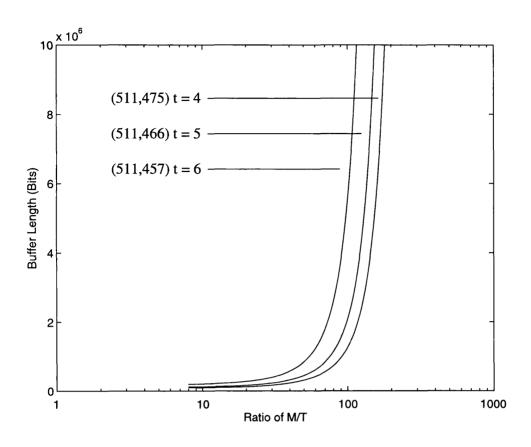

| 5.7  | Buffer length vs $M/T$ for $(511, k)$ codes                                |

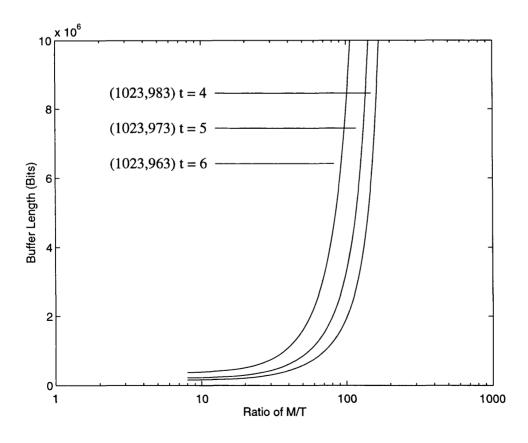

| 5.8  | Buffer length vs $M/T$ for $(1023, k)$ codes                               |

| 5.9  | Block diagram of series-parallel buffered decoding system                  |

| 5.10 | Optimised buffered decoding system                                         |

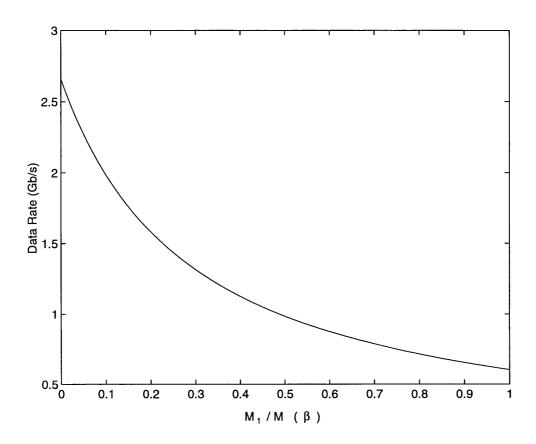

| 5.11 | Data rate vs Optimisation Parameter $(\beta)$                              |

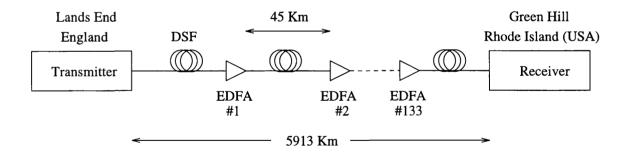

| 6.1  | Block diagram of UK-US segment of the TAT-12 submarine cable 121           |

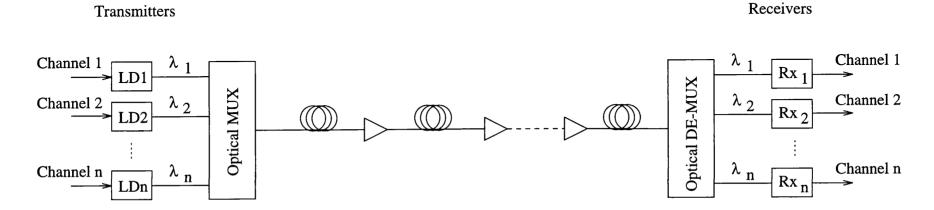

| 6.2  | Block diagram of an optically amplified multichannel WDM system 123        |

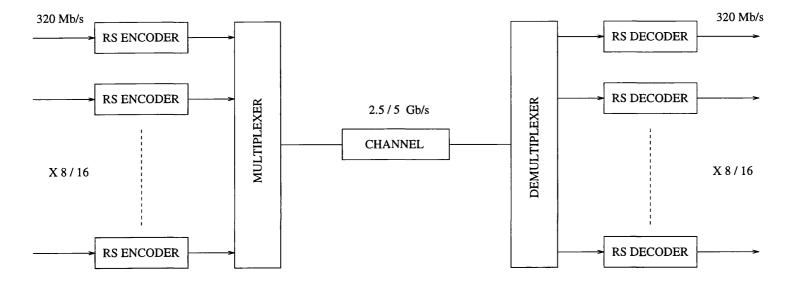

| 6.3  | Proposed tributary encoding/decoding architecture                          |

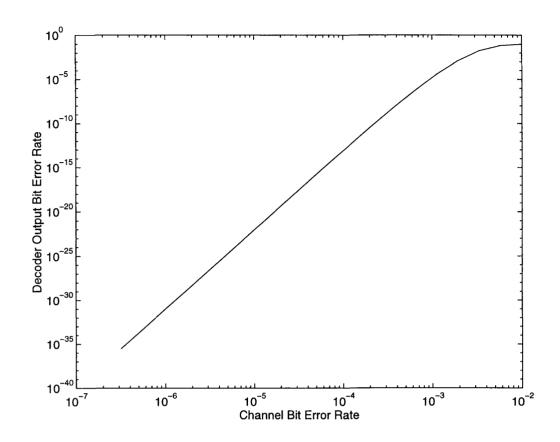

| 6.4  | Error performance of Reed-Solomon (255,239) code                           |

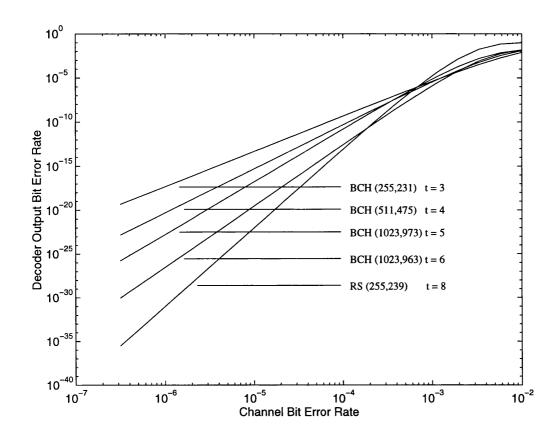

| 6.5  | Performance comparison of BCH codes                                        |

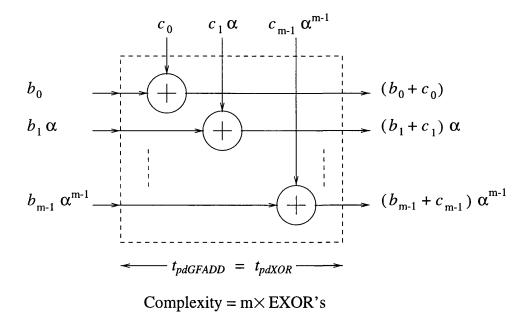

| A.1 Gal | lois Field addition | with symbols from | n GF $(2^m)$ | <br>139 |

|---------|---------------------|-------------------|--------------|---------|

|         |                     |                   |              |         |

10

List of Figures

# Chapter 1

# Introduction

## 1.1 Motivation and Background

Digital information transmission is now universally employed for long distance telecommunications [1]. Over the past two decades technical advances in this field have resulted in many new techniques and standards for digital transmission being developed [2-4]. As consumer demand for greater capacity and improved reliability of digital networks increases, this trend looks set to continue well into the next century.

An area which has benefited significantly from this continual research is fibre optic transmission systems. As device technology matured transmission bandwidths increased considerably from early systems operating at up to 140 Mbit/s to current systems operating at 2.5 Gbit/s and beyond [5]. As the boundaries of system performance are extended, with current experimental systems demonstrating capacities of 100 Gbit/s [6], the various transmission impairments encountered become increasingly significant.

At the same time, there have been significant advances in digital signal processing technology and in particular in forward error correction (FEC). Also there have been preliminary efforts to apply FEC as a means to ameliorating impairments in very long haul, high capacity optical fibre transmission systems, such as those used for trans-oceanic communications [7-12]. This makes it appropriate to study more generally the extent to which FEC may be adapted to meet the requirements of high data rate telecommunication transmission.

Accordingly, this research is concerned with the application and implementation of various coding schemes, placing emphasis on generic architectures appropriate to very high speed operation and on their attendant performance. As a particular application area, consideration is given to the requirements for a new generation of lightwave submarine transmission systems which exploit optical amplifiers.

## 1.2 Thesis organisation

Following this brief introduction chapter 2 provides a review of aspects of error control coding theory. Here the fundamental structure and algebraic nature of both binary and non-binary cyclic codes is examined. In particular attention is drawn to a class of powerful yet relatively simple random error correcting codes known as BCH codes. The chapter concludes with a brief overview of decoding methods using syndromes and acknowledges various error correction schemes based on time domain methods.

Building upon this, chapter 3 then illustrates common encoding arrangements based on both the generator and parity polynomial of a BCH code. In each case generalised examples of fully serial and fully parallel encoders are given which again relate to both binary and non-binary codes. The limitations of each arrangement are then discussed before concluding the chapter with serial and parallel error detection circuits based on minimal polynomials.

Having discussed the major limitations of conventional encoding/error detection circuitry, chapter 4 introduces series-parallel architectures which provide a trade off between the high speed of a parallel arrangement and the low complexity of a serial arrangement. Viewing the network of feedback shift registers as an autonomous circuit, a transition matrix may be defined which describes the functional specification of the circuit. Subsequent processing of this matrix allows intermediate circuit solutions to be generated which incorporate varying degrees of parallelism into the design of the encoder or error detector.

Although high speed encoding and error detection has been demonstrated in chapter 4 it is found that decoding, or more specifically error correction, proves to be more problematic. Chapter 5 examines how high speed decoding may be realised using buffered decoding techniques. By taking advantage of channel error statistics and high speed error detection circuits a decoding system may be realised which operates at speeds comparable to those of the encoding architectures presented in chapter 4. This is done with a view to providing a complete high speed error control system capable of operating in the multi giga-bit region.

In chapter 6 forward error control coding is considered in the context of long haul optically amplified submarine systems where transmission rates in excess of 2.5 Gb/s are found. Comparing currently proposed error control strategies with well established low complexity binary BCH codes offers the prospect of realising forward error control at the line rate by using the structures presented in the previous chapters. Furthermore, by encoding and decoding at the line rate the code may be potentially matched to anticipated channel error patterns associated with known

error inducing mechanisms and signal conditions.

Finally, chapter 7 concludes the thesis by summarising the main findings of this research and provides suggestions for further work.

## 1.3 Summary of Main Contributions

The research presented in this thesis investigates the possibility of implementing novel architectures to realise forward error control coding arrangements for application in long haul optically amplified submarine systems. The major contributions resulting from this work may be summarised as follows:

- Standard architectures used for encoding and error detection were evaluated and shown to be either too complex or too slow for modern high speed digital communication systems.

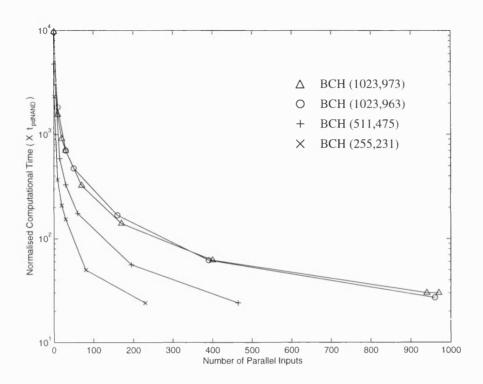

- The use of series-parallel architectures applied to error control circuitry indicated a trade off between circuit speed and complexity. Speeds in the giga-bit per second region may be achieved by these methods even when conventional logic families such as ECL and CMOS are used.

- Buffered decoding techniques have demonstrated the ability to provide an overall enhancement in decoding speed at the expense of decoding delay.

- Implementation of a buffered decoder using a standard RS decoding IC as the main error correction element has been investigated and shown to offer an increase in speed over stand alone devices. Further speed increases may be achieved if the decoder is optimised for certain error patterns.

• The use of low complexity BCH codes has been shown to offer comparable performance to that of multi-level Reed-Solomon codes in the presence of random errors. This offers the prospect of encoding and decoding at the line rate thereby allowing a certain degree of control over the transmitted signal.

The contributions made during the course of this research have led to the following publications to date:

- J.J. O'Reilly, A. Popplewell and R. Blake. 'Forward error control for international telecommunications transmission'. IEE Colloquium on International Transmission Systems, pp. 8/1-8/4, February 1994.

- Y. Bian, R. Blake, A. Popplewell, J. O'Reilly and S. Fragiacomo. 'FEC for Future Trans-Oceanic Optical Systems', Fifth IEE Conference on Telecommunications, Brighton, pp 78-82, March 1995.

- J J O'Reilly and R S Blake. 'Novel coding techniques for long-haul high capacity optical transmission systems'. Invited Presentation at 1st National Telecommunications Conference, Aveiro, Portugal, April 1997.

## 1.4 Summary

This chapter has presented the motivation and background for investigating novel architectures for the implementation of forward error control codes in the context of high speed digital communications systems. Having outlined the structure of the thesis and provided a summary of the main contributions we now move on, in chapter 2, to a general introduction to error control codes.

# Chapter 2

# **Error Control Coding**

## 2.1 Introduction

The theory of error control coding has long been established, in fact its origins may be traced back to the pioneering work of Shannon in 1948 [13] [14]. The 1950s and 60s saw many advances in this field with much time and effort being devoted to the formulation of new codes and coding techniques.

The rapid growth of digital technology over recent decades has seen the emphasis shift from a theoretical nature to a more applications-focussed approach. As a result Error Control Codes (ECCs) have now found many applications in field of digital communications and storage. Such applications range from satellite communications and computer disk drives to compact discs and more recently optical transmission systems.

In order to provide a foundation for following work this chapter will introduce and review some simple but none the less very important concepts of error control coding.

Starting with the basic ideas of error control coding we move on to review some of the properties associated with ECCs. The nature of cyclic codes is then considered along with the mathematical structure of a class of random ECCs known as BCH codes. The chapter concludes by discussing the various aspects and strategies associated with decoding. In particular, methods for error detection/correction are highlighted.

## 2.2 Error Control Coding

Simply stated, error control coding may be defined as the mapping of one data sequence onto another, thereby improving the overall reliability of the channel over which the data is transmitted. The process of error control coding involves the introduction of redundant information into the transmitted signal, thereby enabling error detection and/or error correction to be performed at the decoder. The manner in which this mapping occurs often defines the properties and nature of the code.

In general there are two main types of error control coding system, (i) Automatic repeat Request (ARQ) and (ii) Forward Error Correction (FEC). ARQ systems rely on the receiver or decoder to detect the presence of errors in the received codewords and then, via a feedback path, request re-transmission of any erroneous data. FEC systems however, are not only able to detect the presence of errors, but are structured in such a manner that error correction may be performed by the decoder thereby circumventing the need for a feedback path. It is often convenient, under certain circumstances, to combine these two schemes to produce a third option known as hybrid-ARQ. Although ARQ and hybrid-ARQ systems have their respective benefits, the following work will only concern itself with FEC. The prevalence of ARQ systems and their relation to high speed transmission systems will be discussed in a later chapter.

### 2.3 Classification of error control codes

The phrase "error control coding" is often used to describe a broad spectrum of coding topics. In order to differentiate between the various types of code it is appropriate to define the following coding hierarchy.

Figure 2.1: Hierarchy of error control codes.

It can clearly be seen that there exist two fundamental types of code, binary and non-binary or multi-level codes. A code is termed binary if the symbols used to generate its codewords are defined over a binary alphabet i.e. 0s and 1s, however if an alternative alphabet is used then the code is described as multi-level.

Both binary and multi-level codes can be further subdivided into block and tree codes. Tree codes may be distinguished from block codes as their codewords are generated from not only the current information word presented to the encoder but also the previous m transmitted words, where m is the memory of the encoder. In addition both block and tree codes may be partitioned into linear and non-linear codes. An important class of linear tree code which is commonly used in the field of telecommunications is the convolutional code. This type of code is often employed in mobile telephony and satellite systems [15].

For the purposes of this work attention will be directed towards a subset of binary and non-binary block codes called linear cyclic codes. In particular a class of cyclic codes known as (BCH) codes will be examined in both binary and non-binary form.

## 2.4 Block Codes

Block coding is a mathematical method of mapping a block of k information or source symbols onto a block of n codeword symbols using a pre-defined algorithm. The encoding process divides the message sequence into blocks of k symbols represented by the k-tuple vector  $\mathbf{u}=[u_0,u_1,...,u_{k-1}]$ . Each message block is then transformed into a corresponding codeword of n discrete symbols denoted by the n-tuple vector  $\mathbf{v}=[v_0,v_1,...,v_{n-1}]$ . The result is an (n,k) block code with the inserted n-k elements commonly known as parity check symbols or digits. For an (n,k) code with symbols from the Galois Field  $\mathrm{GF}(2^m)$  there exist  $(2^m)^k$  possible messages (for binary codes where m=1 there are just  $2^k$  possible messages). Figure 2.2 illustrates the encoding procedure.

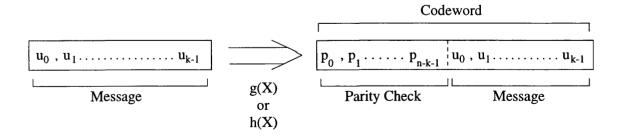

Figure 2.2: Encoding procedure.

As previously stated there are two main types of code to be considered, binary and non-binary. For simplicity the following theory and definitions will be restricted to binary codes, although it may easily be generalised and adapted to non-binary cases.

#### Definition 2.1

A block code of length n and  $2^k$  codewords is called a linear (n, k) code,  $\mathcal{C}$ , if and only if its  $2^k$  codewords form a k-dimensional subspace of the vector space of all the n-tuples over the Galois Field GF(2).

The implied algebraic structure of these linear codes together with definition 2.1 suggests that codewords may be generated from a set of k basis codewords. This property is of great practical significance as it enables long and complex codes to be generated with only modest resources.

#### Definition 2.2

The rate of a block code is defined as the ratio of the number of information symbols to that of the number of codeword symbols i.e.

$$Rate = \frac{k}{n} \tag{2.1}$$

This is an important metric as it defines the amount of redundancy introduced into the transmitted data by the encoding operation. High rate codes are favourable for two reasons: In the first instance if the transmission rate is limited then the amount of redundant data transmitted is kept to a minimum; secondly, for a constant data rate i.e. increased transmission rate, the noise penalty due to increased bandwidth is minimised.

#### Definition 2.3

The Hamming weight,  $w(\mathbf{v})$ , or weight of a codeword  $\mathbf{v}$  is defined as the number of non-zero elements of that codeword e.g. the codeword  $\mathbf{v}=1001100$  has  $w(\mathbf{v})=3$ .

#### Definition 2.4

The distance or Hamming distance  $d(\mathbf{v}, \mathbf{w})$  between two codewords,  $\mathbf{v}$  and  $\mathbf{w}$ , is the number of positions in which they differ. This result may be directly obtained by the modulo 2 addition of the two codewords.

#### Definition 2.5

The minimum distance  $d_{min}$ , of a code C, is defined as the smallest modulo 2 sum of any two codewords and it can be shown that this is equal to the minimum weight of the codeword set:

i.e.

$$d_{min} = \min\{ d(\mathbf{v}, \mathbf{w}) : \mathbf{v}, \mathbf{w} \in \mathcal{C}, \mathbf{v} \neq \mathbf{w} \}$$

Figure 2.3 symbolically illustrates the properties of a t error correcting block code. Each codeword is surrounded by a sphere of radius t. Contained within each sphere is not only a valid codeword but numerous n-tuple vectors which differ from the codeword in up to t places. Assuming that the error correcting capabilities of the code are not exceeded any received vector lying within a sphere will be correctly decoded as the codeword associated with that sphere. This is known as minimum distance decoding and it is this property that forms the basis of many error correction schemes. To ensure correct decoding no spheres may overlap, therefore for a t error

correcting code the distance between any two spheres must be greater than 2t i.e.  $d_{min} \ge 2t + 1$ .

### Codeword

Figure 2.3: Symbolic representation of a codeword set.

## 2.4.1 Cyclic Codes

Cyclic codes represent an important subclass of linear codes. Their cyclic nature allows encoding and error detection to be easily implemented by a network of Linear Feedback Shift Registers (LFSRs). The inherent algebraic structure of these codes results in various practical methods being used to decode them.

If the components of a codeword are  $\mathbf{v} = (v_0, v_1, ..., v_{n-1})$  then cyclically shifting each component one place to the right results in the n-tuple,

$$\mathbf{v}^{(1)} = (v_{n-1}, v_0, v_1, ..., v_{n-2})$$

which is called a cyclic shift of  $\mathbf{v}$ .

In general if the components of  $\mathbf{v}$  are shifted i places to the right then the resulting n-tuple is

$$\mathbf{v}^{(i)} = (v_{n-i}, v_{n-i+1}, ..., v_{n-1}, v_0, v_1, ..., v_{n-i-1}).$$

It can be clearly seen that cyclically shifting a codeword i places to the right is equivalent to cyclically shifting the same codeword n-i places to the left.

### Definition 2.6

An (n, k) linear code is called a cyclic code if every cyclic shift of a code vector in C is also a code vector in C.

### 2.4.2 Systematic Codes

It is often convenient from a design point of view to produce codes in a systematic format as shown in figure 2.4. The codeword is divided into two parts, a message part and a redundant parity check part. The message part consists of the k unaltered information symbols while the redundant parity check part consists of the (n-k) parity check symbols, which are linear sums of the information symbols.

Figure 2.4: Systematic format of a codeword.

## 2.5 Polynomial Representation of Codes

For encoding and decoding purposes it is often useful to represent a code in polynomial form. The codeword vector  $\mathbf{v}=[v_0, v_1, ..., v_{n-1}]$  is expressed as a polynomial of degree n-1 or less with the coefficients of  $X^j$  obtained from the  $j^{th}$  component of  $\mathbf{v}$

i.e.

$$v(X) = v_0 + v_1 X^1 + v_2 X^2 + \dots + v_{n-1} X^{n-1}$$

(2.2)

Similarly the information vector  $\mathbf{u} = [u_0, u_1, ..., u_{k-1}]$  can be represented as a polynomial of degree k-1 or less thus

$$u(X) = u_0 + u_1 X^1 + u_2 X^2 + \dots + u_{k-1} X^{k-1}$$

(2.3)

### 2.6 BCH Codes

One of the most important and powerful classes of linear block codes are BCH codes. Binary BCH codes were discovered by Hocquenghem in 1959 [16] and independently by Bose and Chaudhuri in 1960 [17]. In 1961 Gorenstein and Zierler [18] generalised these results to include codes with symbols from  $GF(p^m)$  where p is a prime. An important class of non-binary BCH codes are the Reed-Solomon (RS) codes [19].

BCH codes represent some of the most extensively studied random error correcting codes. Many good encoding and decoding arrangements have been devised over the years which take advantage of the highly algebraic structure and cyclic nature of these codes. It is appropriate here to review some of the more important properties of both binary and Reed-Solomon BCH codes.

### 2.6.1 Binary Codes

The most common BCH codes, known as primitive BCH codes, may be characterised as follows. For any given positive integer  $m \geq 3$  and  $t \leq 2^{m-1}$  there exists a binary BCH code with the following parameters:

Block Length:  $n = 2^m - 1$

Number of parity-check digits:  $n - k \le mt$

Minimum distance:  $d_{min} \ge 2t + 1$

A BCH code is uniquely defined in terms of its generator polynomial or parity polynomial. The generator polynomial for a t-error-correcting code of length  $n = 2^m - 1$  is specified in terms of its roots from the Galois field  $GF(2^m)$ . If  $\alpha$  is a primitive element in  $GF(2^m)$  then g(X) is the lowest degree polynomial which has

$$\alpha^1, \alpha^2, \alpha^3, ..., \alpha^{2t} \tag{2.4}$$

as its roots. Let  $\Phi_i$  be the minimal polynomial which has  $\alpha^i$  as a root. Then g(X) is the lowest common multiple of  $\Phi_1, \Phi_2, ..., \Phi_{2t}$  i.e.

$$g(X) = LCM\{\Phi_1(X)\Phi_2(X)\Phi_3(X), ..., \Phi_{2t}\}$$

(2.5)

It has been shown [20] that every even power of  $\alpha$  in the sequence 2.4 has the same minimal polynomial as some preceding odd power of  $\alpha$ . The generator polynomial uniquely describing a code can therefore be modified to:

$$g(X) = LCM\{\Phi_1(X)\Phi_3(X)...\Phi_{2t-1}(X)\}$$

(2.6)

With the resulting generator taking the form

$$g(X) = g_0 + g_1 X + g_2 X^2 + \dots + g_{n-k-1} X^{n-k-1} + X^{n-k}.$$

(2.7)

Alternatively a code may be uniquely specified by its parity polynomial h(X). For an (n, k) linear code this is related to the generator polynomial by the following

equation

$$\boldsymbol{h}(x) = \frac{X^n + 1}{\boldsymbol{g}(X)} \tag{2.8}$$

where h(X) is a polynomial of degree k with the following form:

$$h(X) = h_0 + h_1 X + h_2 X^2 + \dots + h_{k-1} X^{k-1} + X^k.$$

(2.9)

In both cases we may note that the coefficients of g(X) and h(X) are defined over GF(2) for a binary code. As an example consider the (15,7) double error correcting code. Constructing the Galois Field  $GF(2^4)$  from the primitive polynomial  $1 + X + X^4 = 0$  and using  $\alpha$  as a primitive element, we find the minimal polynomials which have  $\alpha$  and  $\alpha^3$  as roots as

$$\Phi_1(X) = 1 + X + X^4$$

$$\Phi_3(X) = 1 + X + X^2 + X^3 + X^4$$

Sine the generator polynomial is defined as

$$g(X) = LCM{\Phi_1(X)\Phi_3(X)}.$$

and  $\Phi_1(X)$  and  $\Phi_3(X)$  are in this case distinct irreducible polynomials,

$$g(X) = \Phi_1(X)\Phi_3(X)$$

$$= (1 + X + X^4)(1 + X + X^2 + X^3 + X^4)$$

$$= 1 + X^4 + X^6 + X^7 + X^8$$

and the parity polynomial for the (15,7) code may be calculated thus

$$h(X) = \frac{X^{15} + 1}{(1 + X^4 + X^6 + X^7 + X^8)}$$

$$= 1 + X^4 + X^6 + X^7.$$

To illustrate the encoding process we shall consider a simple (7,4) Hamming code based on the generator polynomial  $g(X) = 1 + X + X^3$ . Suppose the information

sequence to be encoded is 0 1 1 1, represented as a polynomial  $u(X) = X + X^2 + X^3$ . Encoding in a non-systematic form simply involves multiplying the information polynomial u(X) by the generator polynomial g(X) using binary modulo-2 addition and multiplication.

Where . denotes multiplication.

Table 2.1 shows an example of a (7,4) code in both systematic and non-systematic form. It can be clearly seen that for both cases the same codeword set is used, the only difference occurring in the mapping between the information vector and the codeword. For any given information vector a systematic codeword may easily be generated by simply selecting the non-systematic codeword which contains the corresponding k information bits in the highest order positions of the codeword.

|             | Codeword       |            |  |

|-------------|----------------|------------|--|

| Information | Non-Systematic | Systematic |  |

| 0 0 0 0     | 0 0 0 0 0 0 0  | 0000000    |  |

| 0 0 0 1     | 0001101        | 1010001    |  |

| 0010        | 0011010        | 1110010    |  |

| 0011        | 0010111        | 0100011    |  |

| 0100        | 0110100        | 0110100    |  |

| 0 1 0 1     | 0111001        | 1100101    |  |

| 0 1 1 0     | 0110100        | 1000110    |  |

| 0 1 1 1     | 0100011        | 0010111    |  |

| 1000        | 1101000        | 1101000    |  |

| 1001        | 1100101        | 0111001    |  |

| 1010        | 1110010        | 0011010    |  |

| 1011        | 1111111        | 1001011    |  |

| 1100        | 1011100        | 1011100    |  |

| 1101        | 1010001        | 0001101    |  |

| 1110        | 1000110        | 0101110    |  |

| 1111        | 1001011        | 1111111    |  |

Table 2.1: Systematic and Non-systematic form of codewords

#### 2.6.2Non-Binary Codes

The most important sub-class of non-binary BCH codes are the Reed-Solomon or RS codes. Named in honour of their discoverers, RS codes represent a class of highly efficient random error correcting codes with excellent burst error correcting capabilities when transmitted over binary channels.

The encoding and decoding of RS codes differs from binary codes in that all mathematical operations are performed on symbols rather than individual bits. Specifically, an (n, k) RS code maps a block of k information symbols into a block of n codeword symbols, with each symbol being represented by m bits, where  $m \geq 1$ .

For a t-error correcting code with symbols from  $\mathrm{GF}(2^m)$  there exists an RS code with the following parameters:

Block Length:

$$n = 2^m - 1$$

Number of parity-check digits: n - k = 2t

$$n-k=2t$$

Minimum distance:

$$d_{min} = 2t + 1$$

We may note that the length of the code is one less than the radix of a code symbol and the minimum distance is one greater than the number of parity check symbols. The highly efficient use of redundancy compared with binary codes and their flexibility, in terms of block length and symbol size, makes RS codes very attractive for commercial use.

Like the binary code the RS code is specified in terms of its roots defined over  $GF(2^m)$ . However the generator polynomial of a t error correcting RS code is defined as:

$$g(X) = \sum_{i=1}^{2t} (X + \alpha^{i})$$

$$= g_{0} + g_{1}X + g_{2}X^{2} + \dots + g_{2t-1}X^{2t-1} + X^{2t}.$$

(2.10)

Where  $\alpha$  is a primitive element in  $GF(2^m)$ . The parity polynomial of an RS code is derived in the same way to that of the binary BCH codes.

#### Definition 2.7

A cyclic code C is constructed by multiplying a generator polynomial g(X) by all polynomials of degree k-1 or less.

## 2.7 Decoding of Linear Block Codes

The decoding of linear block codes may be regarded as three discrete operations; error detection, error correction and the recovery of the message or information sequence. For codewords in systematic form the recovery of the information becomes a trivial process as the message is present and unaltered in the transmitted codeword. It is therefore only necessary to discard the (n-k) parity check digits once any error correction has taken place. Of the two remaining operations error detection is by far the simplest. This involves calculating a syndrome vector in order to determine if the received vector, r(X), is a valid codeword. For an (n,k) cyclic code where  $n=2^m-1$  the syndrome is represented by a vector containing 2t m-tuples thus  $S=\{S_1, S_2, ..., S_{2t}\}$ . The components of S are defined as

$$S_i = \boldsymbol{r}(\alpha^i) \tag{2.11}$$

for  $1 \leq i \leq 2t$  where  $r(\alpha^i)$  is the received vector evaluated at  $\alpha^i$ . The received vector may be represented as a linear combination of a valid codeword and error vector

e(X) thus

$$r(X) = c(X) + e(X). \tag{2.12}$$

By definition 2.7 each codeword is a multiple of g(X) and therefore must also be a multiple of  $\Phi_i(X)$  for  $1 \le i \le 2t$  (see equation (2.5)). Equation (2.12) can now be written as

$$\mathbf{r}(X) = \mathbf{a}(X)\mathbf{\Phi}_i(X) + \mathbf{e}(x) \tag{2.13}$$

for  $1 \leq i \leq 2t$ . Substituting values of  $\alpha^i$  gives

$$\boldsymbol{r}(\alpha^i) = \boldsymbol{e}(\alpha^i) \tag{2.14}$$

since  $\Phi_i(\alpha^i)=0$ . As the syndrome component  $S_i$  is defined as  $\boldsymbol{r}(\alpha^i)$  we obtain the following

$$S_i = \mathbf{e}(\alpha^i). \tag{2.15}$$

That is to say, the syndrome components are dependent only on the error pattern and not the transmitted codeword. Clearly  $S=\underline{0}$  if and only if r(X) is a codeword, and  $S\neq\underline{0}$  if and only if r(X) is not a codeword. Therefore, when  $S\neq\underline{0}$  we know that r(X) is not a codeword and the presence of errors has been detected. However, if the error pattern is such that it transforms the transmitted codeword into another valid codeword i.e. the error pattern is itself a valid codeword then  $S=\underline{0}$ . Error patterns of this kind are called undetectable error patterns and cause decoding errors.

In contrast to error detection, error correction proves to be somewhat more involved. Many good algorithms exists for error correction [20-23], nearly all of which employ information gained from the syndromes. One possible strategy involves storing the syndromes associated with every correctable error pattern. By matching the syndrome of a received codeword to one that is already stored it is possible to find the error pattern. Unfortunately for large codes or codes which are capable of correcting

a large number of errors this option is not feasible. Alternatively, the error pattern may be calculated by another method. One such method is the Berlekamp-Massey algorithm [24] which involves using finite field arithmetic in order to solve a set of simultaneous equations and calculate the roots of an error locator polynomial. Although relatively simple in theory the practical requirements of such a method often demand considerable complexity. This has lead to many coding theorists developing alternative sub-routines in an attempt to reduce complexity. Many other solutions exist which take advantage of the cyclic nature of BCH codes [25] [26]. For example an error trapping decoder [27] does not directly calculate the error locations but assumes that errors occur in specific patterns. As a result a decoder of reduced complexity, and often increased speed, can be implemented. Therefore it is often the application and implementation factors which dictate what type of decoding arrangement is required.

## 2.8 Summary

In summary the process of error control coding introduces redundancy into the message sequence to enable error detection and/or error correction. The mapping between the information sequences and codewords is unique and is performed over a finite field. The algebraic structure of the codes often makes the encoding and error detection process a simple matter. However, error correction is usually more complex but can, with careful planning, be achieved with relative ease.

We now continue, in the next chapter, by examining some standard architectures for the encoding and error detection of BCH codes. We then proceed by introducing some new concepts which will effect a considerable increase in speed.

# Chapter 3

# Standard Encoding and Error

# **Detection Methods**

#### 3.1 Introduction

Following the general review of ECC in the last chapter a brief appraisal of well established techniques devised for the realisation of encoding and error detection systems is now given. Current serial architectures based on both the generator and parity polynomial of a code will be reviewed and the attributes of each method discussed. In addition, parallel encoding arrangements will be introduced and shown to provide a substantial gain in operational speed at the cost of greatly increased circuit complexity.

Having examined various encoding arrangements, error detection circuits based on minimal polynomials are then presented. After noting the similarities to encoding architectures it is shown that both serial and parallel configurations are subject to similar speed/complexity constraints.

## 3.2 Standard Encoding Architectures

The implementation of cyclic block codes has traditionally involved the use of Linear Feedback Shift Register (LFSR) networks to achieve polynomial division or multiplication. This section introduces and briefly reviews standard architectures used for the generation of BCH codes.

Initially, common serial encoding arrangements derived from the generator and parity polynomials of an arbitrary code will be considered. For each arrangement an illustrative example, based on a binary Hamming code, will be given. After highlighting the key differences which exist between each method, the respective merits and disadvantages of the two arrangements are discussed. An alternative solution to the problem of codeword generation is then introduced. The direct extraction of the parity check bits via the parity check equations offers the prospect of high speed encoding at the expense of greatly increased circuit complexity.

## 3.2.1 Serial Encoding

A method often employed for the generation of BCH codewords is one based on algebraic polynomial division or multiplication. By exploiting the strong algebraic structure of cyclic codes it is possible to implement an encoder based on a appropriately configured network of feedback shift registers. Circuits of this nature can be based on either the generator polynomial, g(X), or parity polynomial, h(X), of a code [27]. Attention is initially focused on architectures derived from the generator polynomial.

Encoding of cyclic codes based on the generator polynomial is normally achieved in one of two ways. The underlying principle common to both methods arises from the fact that a valid codeword must be a multiple of g(X) [28]. Consequently codewords may be generated in either non-systematic form, by directly multiplying the information polynomial by g(X), or in systematic form, by placing the information symbols in either the highest or lowest order positions of the codeword vector and generating the corresponding parity check symbols by suitable polynomial division. The most straightforward of these two methods is the generation of codewords in non-systematic form which, as stated, involves the simple multiplication or convolution of the information polynomial by the generator polynomial g(X).

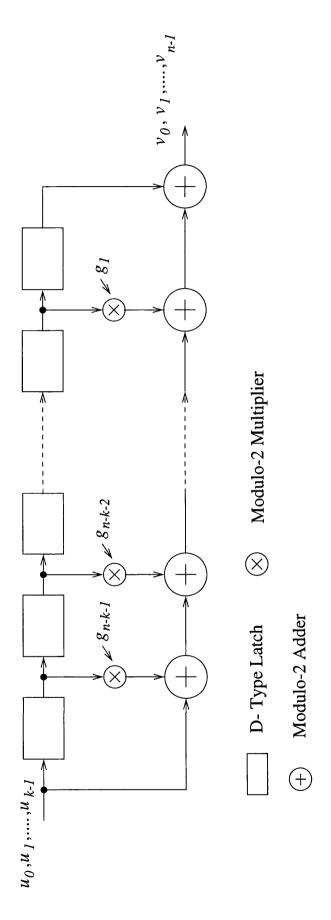

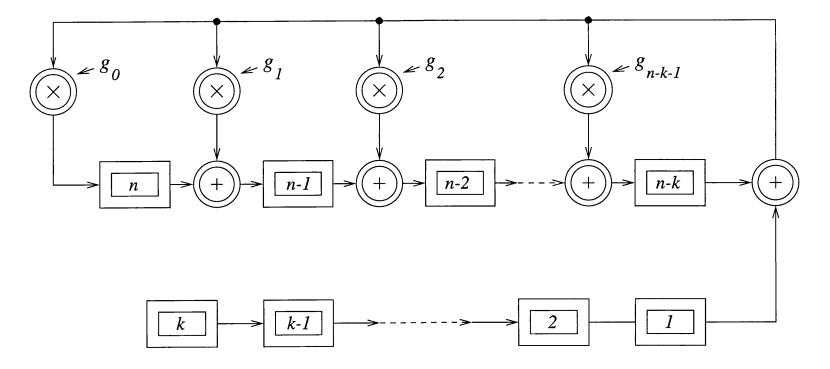

Figure 3.1 illustrates a circuit for multiplying an arbitrary information polynomial, u(X), by the generator polynomial  $g(X) = 1 + g_1X + ... + g_{n-k-1}X^{n-k-1} + X^{n-k}$ , where for simplicity the coefficients of u(X) and g(X) are defined over GF(2) i.e. a binary code. The information bits enter the circuit from the left hand side with the most significant bit entering first, it is assumed that the shift registers initially contain zeros. After n successive clock cycles a codeword corresponding to the information vector will have been generated on a bit-by-bit basis.

The linear nature and operation of this autonomous circuit results in a one to one mapping between an information vector and a codeword. This approach to codeword generation allows all  $2^k$  binary codewords to be produced in an efficient manner without the need for large look up tables.

Figure 3.1: Multiply by g(X) circuit.

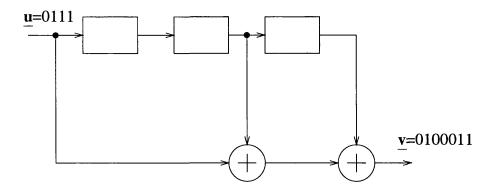

To clarify the operation of such a circuit a simple example based on the (7,4) Hamming code with generator polynomial  $g(X) = 1 + X + X^3$  is considered. Suppose the information vector to be encoded is  $\underline{\mathbf{u}} = 0111$ , or represented in polynomial form,  $u(X) = X + X^2 + X^3$ . The corresponding codeword is then given by the modulo-2 multiplication of u(X) and g(X) i.e.

Message

$$u(X)$$

Encoding Codeword  $v(X)$  0 1 1 1  $u(X).g(X)$  0 1 0 0 0 1 1  $X + X^2 + X^3$   $(X + X^2 + X^3).(1 + X + X^3)$   $X + X^5 + X^6$

Where . denotes multiplication.

The circuit of figure 3.1 now translates into that of figure 3.2, where the modulo-2 multipliers are realized by a short circuit for multiply by 1 and an open circuit for multiply by 0.

Figure 3.2: Multiply by  $X^3 + X + 1$  circuit.

Although a valid method for producing codewords, circuits of this nature are seldom used. As may be observed from this example the codeword does not contain the information vector in its original form. Instead the information has been embedded in the codeword by the encoding process. In order to recover the original message the decoder must now divide the received message by g(X) once any error detection/correction has been performed. To overcome the need for additional circuitry

it is common practice to generate codewords in systematic form using polynomial division circuits. In chapter 2 a systematic codeword was shown to contain the unaltered information vector in the high order positions and the parity check symbols in the low order positions. Consequently, a decoder may now be constructed which recovers the original message by simply discarding the parity check symbols following any error detection/correction. For an (n, k) cyclic code, systematic encoding may be achieved as follows.

- 1. Premultiply the message, u(X), by  $X^{n-k}$ .

- 2. Obtain the remainder, or parity check symbols, by dividing  $u(X).X^{n-k}$  by the generator polynomial g(X).

- 3. Combine the parity check symbols with the information symbols to form a codeword.

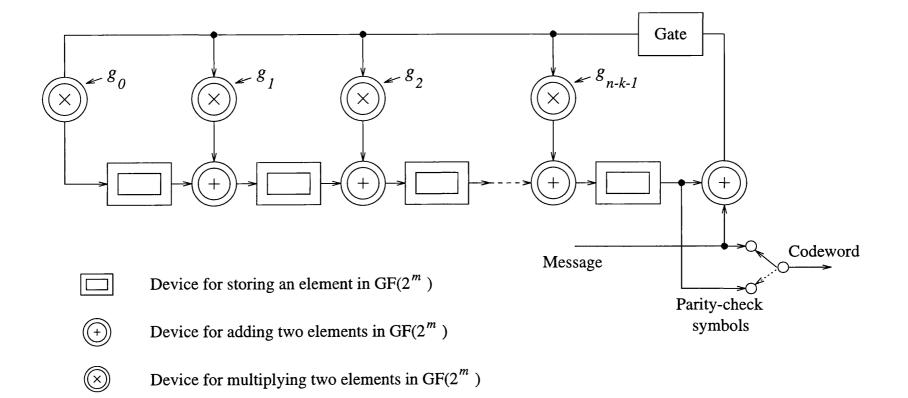

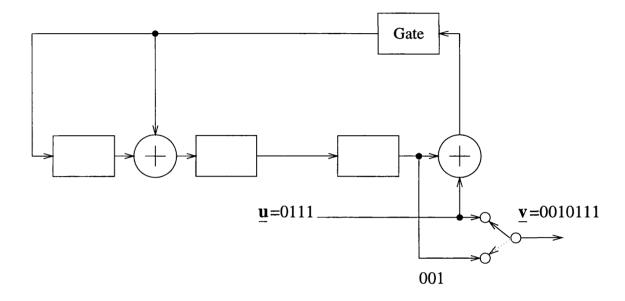

Figure 3.3 illustrates a commercially available encoder, based on polynomial division techniques, for generating an (n, k) cyclic code with symbols from  $GF(2^m)$  [29]. In order to generate a codeword the circuit performs the three previously described steps as follows: Step 1, pre-multiplication by  $X^{n-k}$  is implicit by the configuration of the circuit. Note that with the gate closed the message enters the circuit from the right hand side as opposed to the left hand side of figures 3.1 and 3.2. Step 2, calculation of parity check symbols, starts with the information vector simultaneously entering the transmission channel and circuit through the closed gate. After all k symbols have entered the parity check symbols are contained within the (n-k) storage elements. Finally, step 3 is achieved by clocking the contents of the storage elements into the transmission channel with the feedback gate open to realise a contiguous n symbol codeword. The storage elements are then reset to zero and the process repeated for subsequent information vectors.

Figure 3.3: Polynomial division encoder based on generator polynomial.

Returning to the previous example of the (7,4) Hamming code, the following circuit may be constructed.

Figure 3.4: Systematic (7,4) Hamming encoder based on the generator polynomial  $g(X) = 1 + X + X^3$ .

Again, using the information vector  $\underline{\mathbf{u}}$ =0111 as an example the following table illustrates the shift register contents for each successive clock cycle. With the initial

| Input | Register Contents |                         |  |

|-------|-------------------|-------------------------|--|

|       | 000               | Initial state           |  |

| 1     | 110               | $1^{\mathrm{st}}$ shift |  |

| 1     | 101               | $2^{\rm nd}$ shift      |  |

| 1     | 010               | $3^{\rm rd}$ shift      |  |

| 0     | 001               | $4^{ m th}$ shift       |  |

Table 3.1: Shift register contents.

contents of the registers set to zero it may be observed that during the first 4 clock cycles the information enters both the circuit and transmission channel. On comple-

tion of the fourth shift the parity check digits have been calculated and are stored within the three registers. For the final 3 clock cycles the switch is placed in the down position and the parity check digits 001 are clocked out of the circuit and combined with the information vector to form the complete codeword  $\mathbf{v}$ =0010011.

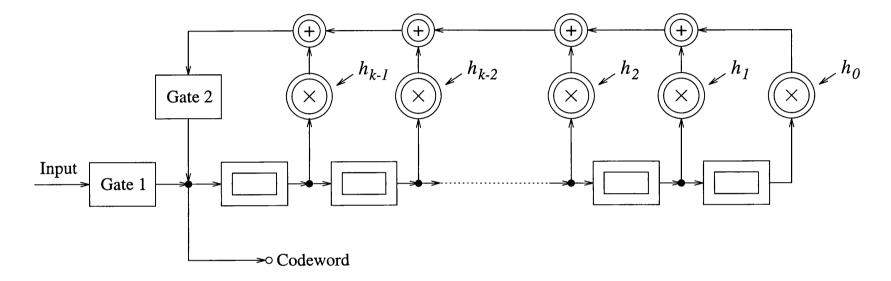

Encoding of a cyclic code can also be accomplished by using its parity polynomial. Figure 3.5 shows the general form of a systematic encoder based on the parity polynomial  $h(X) = h_0 + h_1 X + h_2 X^2 + ... + h_{k-1} X^{k-1} + X^k$ .

The function of this circuit is to realise the recursive or difference equation (3.1):

$$v_{n-k-j} = \sum_{i=0}^{k-1} h_i v_{n-i-j} \qquad 1 \le j \le n-k$$

(3.1)

i.e.

$$v_{n-k-1} = h_0 v_{n-1} + h_1 v_{n-2} + \dots + h_{k-1} v_{n-k}$$

$$= u_{k-1} + h_1 u_{k-2} + \dots + h_{k-1} u_0$$

(3.2)

$$v_{n-k-2} = h_0 v_{n-2} + h_1 v_{n-3} + \dots + h_{k-1} v_{n-k-1}$$

$$= u_{k-2} + h_1 u_{k-3} + \dots + h_{k-2} u_0 + h_{k-1} v_{n-k-1}$$

$$\vdots \qquad \vdots \qquad \vdots \qquad (3.3)$$

$$v_0 = v_k + h_1 v_{k-1} + \ldots + h_{k-1} v_1 \tag{3.4}$$

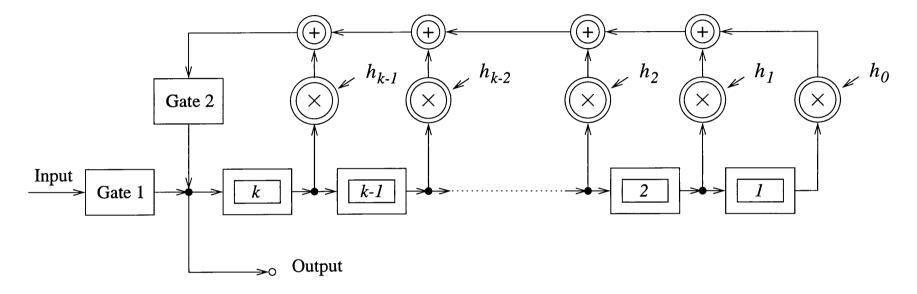

The functionality of this circuit is described as follows. With Gate 1 closed and Gate 2 open, the information vector is simultaneously clocked into the circuit and transmission channel. When all k information symbols have entered, Gate 1 is opened and Gate 2 closed. Each subsequent clock cycle then represents a single summation of equation (3.1) i.e. the circuit systematically computes  $v_{n-k-j}$  for  $1 \le j \le n-k$ . The (n-k) parity symbols are then clocked out of the circuit to form the codeword. As with generator polynomial based encoders, the storage elements are then reset to zero ready for the following information vectors.

Figure 3.5: Systematic encoder based on parity polynomial.

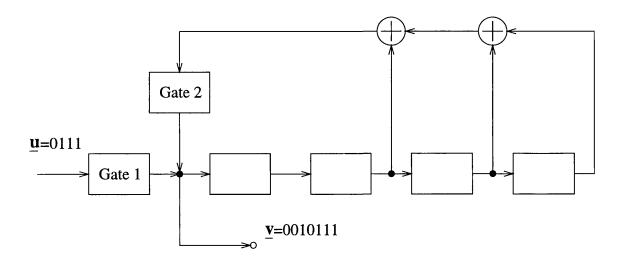

In the case of the (7,4) Hamming code defined by the parity polynomial  $h(X) = 1 + X + X^2 + X^4$  the encoder shown in figure 3.6 can be constructed.

Figure 3.6: (7,4) Hamming encoder based on parity polynomial.

|              | Input  | Register Contents |                       |

|--------------|--------|-------------------|-----------------------|

|              |        | 0000              | Initial state         |

|              | 1      | 1000              | 1 <sup>st</sup> shift |

| Information  | 1      | 1100              | 2 <sup>nd</sup> shift |

| Vector       | 1      | 1110              | 3 <sup>rd</sup> shift |

|              | 0      | 0111              | $4^{ m th}$ shift     |

|              | Output |                   |                       |

| Parity Check | 1      | 1011              | 5 <sup>th</sup> shift |

| Bits         | 0      | 0 1 0 1           | 6 <sup>th</sup> shift |

|              | 0      | 0010              | 7 <sup>th</sup> shift |

Table 3.2: Contents of shift registers.

By examining the contents of each register, as shown in table 3.2, it may be observed that the initial parity check digit is formed after the fourth cyclic shift of the LFSR network. The circuit then yields a further parity check digit on each successive shift

of the registers until all (n-k) digits have been generated.

Although the previous examples relate only to binary codes the operation and construction of such circuits can be easily extended to multi-level codes. Having demonstrated the operation of several encoding circuits it is now appropriate to consider the various performance and complexity issues relating to each arrangement.

Code generation by polynomial multiplication, while offering a more direct approach, often requires a more complex decoding arrangement. Producing codewords in systematic form, by either polynomial division or encoders based on a code's parity polynomial, effectively eliminates this need for additional decoding circuitry. Although the two systematic encoders produce identical codes there exist a number of subtle differences between them.

In hardware terms, generating codes by polynomial division requires a circuit containing (n-k) storage elements with the check symbols being formed after the  $k^{th}$  cyclic shift. In contrast, generating codes via the parity polynomial involves a circuit containing k storage elements which is clocked (n-k) times, with each successive shift producing one additional parity symbol.

In order to minimise circuit complexity most commercially available encoders are based on architectures derived from the generator polynomial. Consider, for example, the RS (255,239) code. Generating this code would require a circuit consisting of either 239 storage elements for a parity polynomial based encoder or 16 storage elements for a generator polynomial based encoder.

Having identified which circuit architecture is more efficient in terms of hardware, the factors determining the maximum operational speed of each encoding arrangement are now considered. Each encoder must be clocked a total of n times in order to generate a complete codeword. With every clock cycle resulting in the transmission

of a single codeword symbol, the data throughput of each arrangement is determined by the maximum clock frequency that can be applied to each circuit.

It is clear from figures 3.3 and 3.5 that the minimum clock period, and hence the maximum clock frequency, is dependent on several timing parameters. These parameters include: the propagation delays due to the addition and multiplication devices plus the propagation delay, minimum set-up time and minimum hold time associated with the storage elements. Assuming all these factors are constant for both the parity and generator polynomial based circuits, the minimum clock period is determined by the longest delay encountered by a codeword symbol.

By observation of figure 3.3 a codeword/information symbol will, in any one clock cycle, traverse through one multiplication device, a storage element and at most two addition devices. In contrast, an encoder based on the parity polynomial (see figure 3.5) will have an equal delay due to a single multiplication device and storage element, but will have an increased delay due to the  $(n_h - 2)$  addition elements, where  $n_h$  is the number of non-zero coefficients in the parity polynomial. Generally this value is much greater than the delay due to the two addition devices found in generator polynomial based circuits. As a result of the increased delays imposed by such an arrangement, encoders based on the parity polynomial are rarely used in high speed applications.

In summary, it has been demonstrated that architectures based on the generator polynomial of a cyclic code can generally provide a solution which is both faster and less complex than that of parity polynomial based circuits.

#### 3.2.2 Parallel Encoding Architectures

In the previous section encoders based on serial architectures were introduced. Although convenient to implement, the necessary cyclic shifting of the LFSR network required to generate codewords made such arrangements somewhat slow. In order to overcome these speed limitations it is possible to generate the codewords, or the parity check symbols, directly from the parity check equations. We may recall from the previous section that the expansion of equation (3.1) produced (n-k) linearly independent equations. While a serial encoder based on the parity polynomial calculates each of the parity check digits sequentially it is possible to construct an encoder which will calculate all the parity check digits simultaneously.

For an (n, k) cyclic code in systematic form, the information digits  $u_0, u_1, ..., u_{k-1}$  form the components  $v_{n-k}, v_{n-k+1}, ..., v_{n-1}$  of the code vector. Given the k information symbols, equations [3.2 - 3.4] define the (n - k) parity check symbols  $v_0, v_1, ..., v_{n-k-1}$ . For the (7,4) hamming code defined by the parity polynomial  $h(X) = 1 + X + X^2 + X^4$  the resulting parity check equations are:

$$v_2 = v_6 + v_5 + v_4$$

$$= u_3 + u_2 + u_1 \tag{3.5}$$

$$v_1 = v_5 + v_4 + v_3$$

$$= u_2 + u_1 + u_0 \tag{3.6}$$

$$v_0 = v_4 + v_3 + v_2$$

$$= u_3 + u_2 + u_0 \tag{3.7}$$

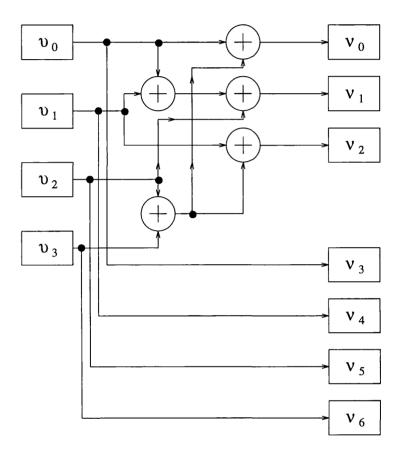

Figure 3.7 illustrates an encoder based on the three parity check equations of the previous example. As may be observed, the information vector is now presented to the encoder in a parallel form. It is this inherent parallelism which provides the

basis for increased operational speed. Since all parity check digits are calculated from the already present information bits no feedback path is required. As a result the operational speed of such a circuit is determined by the asynchronous delay of the EXOR-gate network.

Figure 3.7: Parallel (7,4) Hamming Encoder.

However, while offering the prospect of a potentially fast solution, circuits of this nature are generally too complex for all but the most trivial of codes. To demonstrate this, figure 3.8 illustrates a parallel encoder capable of generating a (15,11) single error correcting code, based on the parity polynomial  $h(X) = 1 + X + X^2 + X^3 + X^5 + X^7 + X^8 + X^{11}$ .

Using the parity polynomial and equation (3.1) it is once again possible to define the following parity check digits.

$$v_3 = u_{10} + u_9 + u_8 + u_7 + u_5 + u_3 + u_2 (3.8)$$

$$v_2 = u_9 + u_8 + u_7 + u_6 + u_4 + u_2 + u_1 (3.9)$$

$$v_1 = u_8 + u_7 + u_6 + u_5 + u_3 + u_1 + u_0 (3.10)$$

$$v_0 = u_{10} + u_9 + u_8 + u_6 + u_4 + u_3 + u_0 (3.11)$$

By comparing the encoder of figure 3.8 with that of figure 3.7 it is clear that the overall circuit complexity has increased substantially. In this example a four fold increase in the number of EXOR-gates is the result of approximately doubling the codeword length. This problem is further compounded at larger block lengths and therefore limits the effectiveness of this approach to encoding.

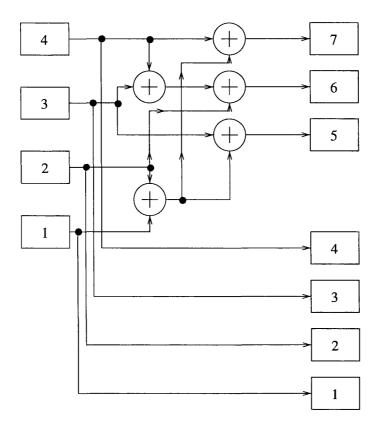

Figure 3.8: Parallel (15,11) Hamming Encoder.

Having presented various encoding strategies in the previous sections attention is now directed towards error detection or syndrome calculation circuits based on similar architectures.

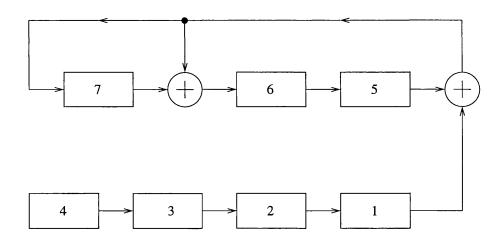

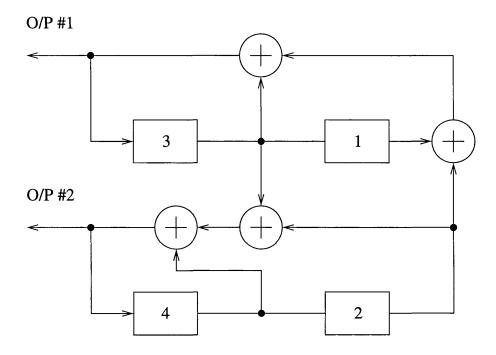

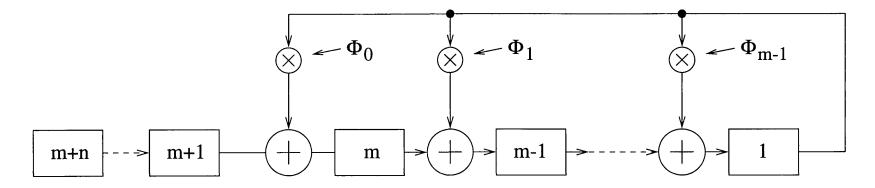

#### 3.3 Error Detection Architectures

In a manner resembling the encoding process syndrome calculation may be achieved by a network of LFSRs configured to perform polynomial division. Here only binary structures are considered since multi-level error detection circuits prove to be trivial extensions. Figure 3.9 illustrates a binary polynomial division circuit which calculates the remainder resulting from the division of  $\mathbf{r}(X) = r_0 + r_1 X + ... + r_{n-1} X^{n-1}$  by the minimal polynomial  $\Phi_i(X) = \phi_{i,0} + \phi_{i,1} X + \phi_{i,2} X^2 + ... + \phi_{i,m-1} X^{m-1}$ , where  $\Phi_i(X)$  has  $\alpha^i$  as a root. This, however, only represents part of the error detection process. To enable  $S_i$  to be calculated additional logic must be incorporated in order to evaluate the remainder at  $\alpha^i$ . Since this logic consists merely of addition elements and operates only on the output of the circuit it does not impede the operational speed and can therefore be ignored in any further timing analysis. For a t error correcting code of length  $n = 2^m - 1$ , t such circuits each containing m storage elements are required in order to calculate the syndromes  $S_1, S_3, ..., S_{2t-1}$ .

As figure 3.9 demonstrates, the syndrome calculation circuit is similar to that of the encoding circuit based on the generator polynomial. The only difference being the received vector enters the circuit from the left hand side. Consequently the operational speed of this circuit is also governed by the longest path encountered by a received symbol, which in this example is an addition element, a multiplier and a storage device. However, in this instance the delay due to the multiplier may be ignored as it would be replace by either an open or short circuit in any practical implementation.

Figure 3.9: Polynomial division based on the minimal polynomial  $\Phi_i(X) = \phi_{i,0} + \phi_{i,1}X + \phi_{i,2}X^2 + ... + \phi_{i,m-1}X^{m-1}$ .

After each of the t syndrome circuits has been clocked a total of n times the syndrome components  $S_i = \{s_{i,0}, s_{i,1}, ..., s_{i,m-1}\}$  are held within the m storage elements. Although convenient to implement, this solution is again restricted by the cyclic shifting required to generate syndrome elements. With this in mind parallel syndrome circuits are now considered.

To implement error detection in a parallel form the syndrome components based on the parity check equations are re-defined. This simply involves re-calculating the parity check digits from the received vector and comparing them to the actual values. To illustrate this the syndrome vector,  $S_1 = \{s_{1,0}, s_{1,1}, s_{1,2}\}$ , for the (7,4) Hamming code is defined as follows:

$$s_{1,0} = r_0 + r_3 + r_5 + r_6 (3.12)$$

$$s_{1,1} = r_1 + r_3 + r_4 + r_5 (3.13)$$

$$s_{1,2} = r_2 + r_4 + r_5 + r_6 (3.14)$$

If no errors have occurred then  $r_i = v_i$  for  $0 \le i \le n-1$  and the syndrome vector is found to be zero. These equations can now be used to define the following parallel error detection circuit.

As figure 3.10 illustrates the parallel syndrome calculation circuits have a similar form to that of the parallel encoding circuits. Although accommodating high speed operation it is again evident that circuits of this nature are restricted, by constraints placed on the circuit complexity, to simple codes with short block lengths.

Figure 3.10: Parallel syndrome calculation circuit.

# 3.4 Summary

In this chapter standard architectures for the realisation and error detection of BCH codes have been described. In the case of serial arrangements it was demonstrated that the necessary cyclic shifting of the LFSR networks rendered such arrangements unsuitable for high speed applications. An alternative approach, which overcomes these limitations, was presented in the form of parallel circuits. Although offering the prospect of increased operational speed it was found that circuit complexity increases rapidly with codeword length. In the following chapter new architectures will be developed and investigated which will allow high speed encoding and error detection to be performed in an efficient manner.

# Chapter 4

# Series-Parallel Encoding and Error Detection

### 4.1 Introduction

Chapter 3 introduced standard architectures employed for the realisation of encoding and error detection systems. It was demonstrated that such architectures were often too slow or too complex to be of any value in high speed applications. Consequently, new techniques devised for encoding and error detection at very high bit rates are now investigated.

Specifically these make use of what are termed series-parallel arrangements which offer the prospect of a trade off between operational speed and circuit complexity, the degree of parallelism adopted influencing the achievable coded line rate relating to the overall system clock rate.

Using *m*-sequence generation architectures to introduce series-parallel concepts, these techniques are then adapted to encoding arrangements where previous results are extended to encompass non-binary as well as binary coding arrangements. We then examine how the series-parallel circuit techniques may be applied to syndrome calculation or error detection circuits. The speed/complexity trade off afforded by these arrangements are then quantified and summarised graphically.

#### 4.2 Series-Parallel Architectures

In previous sections two distinct approaches to encoding and error detection have been clearly defined. The serial approach where the speed of operation is compromised in favour of reduced circuit complexity and the parallel approach where an increase in speed is obtained at the expense of a prohibitively large increase in circuit complexity. In an attempt to find a solution which offers a compromise between these two extremes we turn our attention to series-parallel architectures.

## 4.2.1 *m*-sequence Generation

In order to provide a background for series-parallel architectures we make recourse to previous work concerning m-sequence generation. Pseudo-random bit sequences are traditionally generated in a serial manner by a network of linearly interconnected feedback shift registers. The configuration of such a network is chosen so as to produce an m-sequence of maximal length  $2^m - 1$ , where m is the number of shift registers. However, generating m-sequences in such a manner is often restrictive when operating at high speeds. Previously reported solutions to this problem have relied on several pairs of shift registers operating in parallel with their outputs

phase shifted [30]. Here the number of replicated shift register networks employed determines the overall bit rate. Although convenient to implement at relatively modest speeds, this approach becomes unduly complex when operating at high bit rates (e.g. > 500 Mb/s), especially when long sequences are required.

This led O'Reilly [31] to develop architectures based on series-parallel concepts. Here the m-sequences are generated as sets of non-overlapping k-bit words and unlike the previous approach this method achieves high speed operation using only a single LFSR network.

To effect a speed increase the serial LFSR network is mapped into an equivalent series-parallel form by way of a matrix description of the circuit. The transition matrix defines the functional specification of circuit and allows the subsequent state of the registers to be derived from their present state.

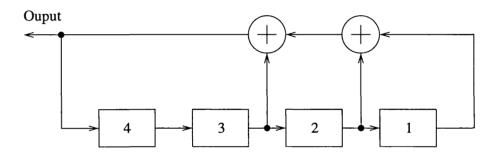

For a LFSR of length m we define U(j) as a  $(m \times 1)$  column vector which describes the contents of the m registers after the j<sup>th</sup> clock cycle and T, the transition matrix, as an  $(m \times m)$  matrix with elements defined over the binary field GF(2). If each stage of the LFSR is numbered sequentially, as shown in figure 4.1, then each row of the transition matrix defines the excitation of that stage in the network. For example the circuit in figure 4.1, as described by the following transition matrix, generates an m-sequence of maximal length 31 with the output sequence being derived from register five.

$$T = \begin{bmatrix} 0 & 0 & 1 & 0 & 1 \\ 1 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \end{bmatrix}$$

$$(4.1)$$

From this matrix we see that row 1 implies that stage 1 is derived from the modulo-2 addition of stages 3 and 5, row 2 implies that stage 2 is derived from stage 1 and so on.

Figure 4.1: Serial *m*-sequence generator.

The state of the LFSR resulting from each successive clock cycle is defined as the modulo-2 multiplication of U(j), the present register contents, and T thus

$$U(j+1) = T.U(j) \tag{4.2}$$

$$U(j+2) = T.U(j+1)$$

$$= T^2.U(j) \tag{4.3}$$

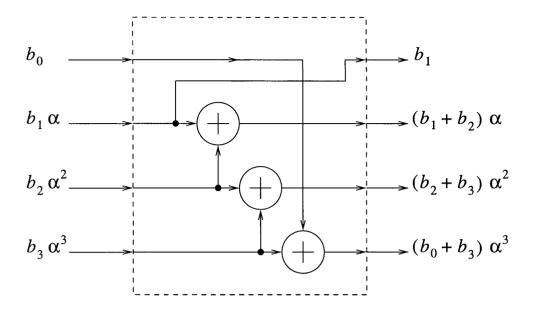

: :