# Strategies for the Analysis and Design of a Low Noise, Frequency Agile Synthesiser

by

### Ian Thompson

A thesis submitted to the University of London for the Degree of Doctor of Philosophy in Electronic Engineering

Department of Electronic & Electrical Engineering

University College London

**May 2003**

ProQuest Number: 10016052

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10016052

Published by ProQuest LLC(2016). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code.

Microform Edition © ProQuest LLC.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### **ABSTRACT**

Frequency synthesisers have become the heart of many modern communications systems as they offer a repeatable means of producing a phase coherent signal source of almost arbitrary frequency and precision. In effect, they can be considered as very high-Q tracking filters capable of being digitally programmed to any integer or non-integer multiple of a reference frequency, with a limited amount of extraneous noise. Their relative simplicity and extraordinary benefit to communications systems has led to their success.

This thesis explores new strategies aimed at advancing our understanding of the noise and agility performance limits of modern phase locked loop frequency synthesisers and, in turn, allowing their better optimisation. A principal aim of this work is the development of a set of comprehensive models with which to analyse the noise performance of the common synthesiser elements and the system as a whole. A complete rigorous mathematical noise model of a sampled closed-loop phase locked loop synthesiser is developed and compared with measured results from a working prototype synthesiser. To complement this work, a detailed study of the mathematics of loop filter design is offered which does not compromise the loop bandwidth. Further work is presented to determine the fundamental noise limitations in such systems and to optimise the design rationale of synthesisers taking into account sampling effects, which are highly significant in high performance applications. Finally, a novel architecture offering the potential for low noise agile frequency synthesis, "the hybrid PLL/DDS synthesiser", is proposed and assessed both theoretically and experimentally.

....to Melanie.

#### **ACKNOWLEDGEMENTS**

Throughout the course of this work there have been many difficult and challenging tasks, none more so than properly acknowledging the contributions of those people who helped in this work. Unfortunately it is not possible to acknowledge everyone, however their contribution certainly is not forgotten.

I would like to thank my parents, Catherine and Vernon Thompson for always being there, my son James for being so tolerant and my wife Melanie, for her immeasurable support and encouragement. Never once has she reminded me of my chores around the house, instead she has quietly assumed the extra workload and always been there when I needed her. Melanie, all I can say is thank you for your support, which has never wavered for a moment and has made this possible for me.

Being a natural worrier and believing myself to be a perfectionist, I must have appeared as a constant threat to the sanity of my supervisor, Dr. Paul Brennan, whom I wish to especially thank for his eternal patience. Through his skill and dedication, he has managed to guide me through my studies with apparent ease for which I shall always remain grateful. Thank you Paul.

I would like to acknowledge Nigel King and Charles Page who introduced me to the art of frequency synthesis especially fractional-n, turning the subject into a life-long fascination for me. Dr. Mahmoud Zadeh who initiated the Ph.D. studies through his skilful negotiation with Nokia. Lynne Lewis who diligently sourced all the publications I requested, no matter how obscure, which have proved invaluable to me throughout the course of these studies.

A special debt of gratitude is extended to Maggie Findlay for her help in keeping me sane during the worst moments.

To express my thoughts succinctly has proved to be one of the greatest challenges throughout my Ph.D. studies and leaves me permanently indebted to Prof. A. Seeds, (UCL), Dr. P. Brennan, (UCL), Dr. T. Busby, (Managing Director, Power Wave UK),

#### Acknowledgements

Mr. M. Ward, (Analog Devices) and my father for the time they spent reviewing and commenting on extracts from this document. This significantly increased my confidence in submitting this document.

Finally I would like to remember my Grandfather, Stanley Wood-Higgs, who conspired with Melanie one memorable weekend in February 1988, to kick me back in to further education when I most needed it.

"... life is around the wrong way".

Stanley E. Wood-Higgs, OBE, FCIS, FAAI, FSAE, FBIM,

Freeman of the City of London.

|                                                                         | Commish   |  |

|-------------------------------------------------------------------------|-----------|--|

|                                                                         | Copyright |  |

| The copyright of this thesis rests nformation derived from it, may be p |           |  |

|                                                                         |           |  |

|                                                                         |           |  |

# **CONTENTS**

| ABS' | TRAC   | CT                                               | 3 |

|------|--------|--------------------------------------------------|---|

| ACK  | NOW    | /LEDGEMENTS                                      | 5 |

| CON  | TEN.   | ΓS                                               | 9 |

| LIST | OF F   | FIGURES                                          | 3 |

| LIST | OF T   | TABLES                                           | 7 |

| LIST | OF F   | PRINCIPAL SYMBOLS1                               | 8 |

| LIST | OF A   | ABBREVIATIONS2                                   | 3 |

| 1    | . INTI | RODUCTION2                                       | 5 |

|      | 1.1    | Frequency Synthesis in Mobile Communications     | 5 |

|      | 1.2    | Scope Of The Thesis                              | 6 |

|      | 1.3    | Principal Contributions Of This Work             | 7 |

|      | 1.4    | Thesis Outline                                   | 8 |

| 2    | .THE   | HISTORY OF FREQUENCY SYNTHESIS                   | 0 |

|      | 2.1    | The Origins Of Frequency Synthesis               | 0 |

|      | 2.2    | Fractional-N Synthesisers                        | 2 |

|      | 2.3    | The Direct Digital Synthesiser                   | 6 |

| 3    | . DEF  | INING FREQUENCY SYNTHESISERS4                    | 0 |

|      | 3.1    | Introduction                                     | 0 |

|      | 3.2    | Overview of Frequency Synthesiser Configurations | 0 |

### Contents

|   | 3.3   | Mixed Signal Frequency Synthesisers                           | 41  |

|---|-------|---------------------------------------------------------------|-----|

|   | 3     | 3.1 Integer-N Single Loop Synthesisers                        | 41  |

|   | 3.    | 3.2 Fractional-N Single Loop Frequency Synthesisers           | 42  |

|   | 3.    | 3.3 Multiple Loop Synthesisers                                | 46  |

|   | 3.4   | Elements of Mixed Signal Frequency Synthesisers               | 47  |

|   | 3.4   | 4.1 Phase Frequency Detectors                                 | 47  |

|   | 3.4   | 4.2 The Loop Filter                                           | 51  |

|   | 3.4   | 4.3 The VCO                                                   | 56  |

|   | 3.4   | 4.4 Digital Dividers                                          | 62  |

|   | 3.4   | 4.5 Analogue Mixers                                           | 65  |

|   | 3.5   | Elements of Direct Digital Synthesisers                       | 66  |

|   | 3     | 5.1 The Digital Accumulator                                   | 67  |

|   | 3.:   | 5.2 The Sine Look Up Table                                    | 68  |

|   | 3.:   | 5.3 The Digital to Analogue Converter                         | 71  |

|   | 3.6   | Summary                                                       | 77  |

| 4 | . MOE | DELLING PLL PHASE NOISE                                       | 78  |

|   | 4.1   | Introduction                                                  | 78  |

|   | 4.2   | Mathematical Preliminaries                                    | 79  |

|   | 4.3   | Phase Noise in a PLL                                          | 80  |

|   | 4.4   | Sampled N-Divider and Reference Signal Noise at the PFD Input | 81  |

|   | 4.5   | Thermal Noise in Loop Filter Components                       | 84  |

|   | 4.6   | Sampled VCO Noise                                             | 88  |

|   | 4.7   | N Dividers                                                    | 94  |

|   | 4.8   | Sampling Spurious Products                                    | 95  |

|   | 4.9   | Summary Of Loop Response To Each Noise Input                  | 97  |

|   | 4.10  | Experimental Results                                          | 100 |

### Contents

|   | 4.11  | Summary                                                              | 103 |

|---|-------|----------------------------------------------------------------------|-----|

| 5 | . PFD | NOISE LIMITATIONS                                                    | 104 |

|   | 5.1   | Introduction to the PFD Problem                                      | 104 |

|   | 5.2   | PFD Noise Model                                                      | 105 |

|   | 5.2   | 2.1 PFD Noise Processes                                              | 105 |

|   | 5.2   | 2.2 PFD Timing Jitter Analysis                                       | 107 |

|   | 5.2   | 2.3 Additive Thermal Noise                                           | 109 |

|   | 5.2   | 2.4 Flicker Noise Analysis                                           | 111 |

|   | 5.3   | Experimental Results                                                 | 112 |

|   | 5.4   | Discussion                                                           | 115 |

|   | 5.5   | Summary                                                              | 117 |

| 6 | .LOO  | P FILTER DESIGN                                                      | 118 |

|   | 6.1   | Introduction                                                         | 118 |

|   | 6.2   | The Mathematics                                                      | 120 |

|   | 6.2   | 2.1 Type II, Third-Order Loop Filter Design                          | 120 |

|   | 6.2   | 2.2 Type II, Fourth-Order Loop Filter Design                         | 122 |

|   | 6.3   | Maximum Allowable Attenuation for a Fourth-Order Loop Filter         | 130 |

|   | 6.4   | Accounting for the Effects of Sampling in Passive Loop Filter Design | 131 |

|   | 6.5   | An Evaluation of the Loop Filter in the Sampled Loop                 | 133 |

|   | 6.6   | Summary                                                              | 137 |

| 7 | . HYB | RID PLL/DDS BASED SYNTHESISER                                        | 139 |

|   | 7.1   | Introduction                                                         | 139 |

|   | 7.2   | System Specification                                                 | 140 |

|   | 7.3   | System Design Criteria                                               | 141 |

|   | 7.3   | 3.1 Preferred Solution                                               | 141 |

### Contents

|      | 7.    | 3.2 Tested Solution                                          | 19             |

|------|-------|--------------------------------------------------------------|----------------|

|      | 7.    | 3.3 Lock Time Considerations                                 | 50             |

|      | 7.4   | Measurement Results                                          | 53             |

|      | 7.5   | Summary                                                      | 58             |

| 8    | . CON | ICLUSIONS AND FURTHER WORK16                                 | 50             |

|      | 8.1   | Conclusions                                                  | 50             |

|      | 8.2   | Further Work                                                 | 53             |

| REFI | EREN  | CES                                                          | <b>5</b> 5     |

| APPI | ENDI  | CES                                                          | 13             |

| A1   | DEF   | INITION OF SSB PHASE NOISE17                                 | 74             |

| A2   | .PRO  | PAGATION OF ERRORS 17                                        | 16             |

| A3   | . MIX | ER INTERMODULATION ANALYSIS17                                | 78             |

| A4   |       | LYSIS OF MODULATED CHARGE PUMP CURRENT, PULSE WIDTH DULATION |                |

| A5   | . CAN | DIDATES PUBLICATIONS18                                       | 34             |

| A6   | OTH   | ER MAGAZINE PUBLICATIONS                                     | <del>)</del> 2 |

| A7   | . МАТ | TLAB LISTING                                                 | <b>)</b> 4     |

# LIST OF FIGURES

| Figure 2.1 Wendt's proposal for a phase locked loop, [12, fig 5]                               |

|------------------------------------------------------------------------------------------------|

| Figure 2.2 Summary of evolution of fractional-n through relevant published diagrams 34         |

| Figure 2.3 Cutler, [31], implementation of a sigma delta modulator                             |

| Figure 2.4 Typical complete DDS + DAC architecture [45]                                        |

| Figure 3.1 Classification of different synthesiser types, [47]                                 |

| Figure 3.2 Integer-n and fractional-n single loop synthesisers compared                        |

| Figure 3.3 Comparison between fractional and integer-n SSB phase noise performance43           |

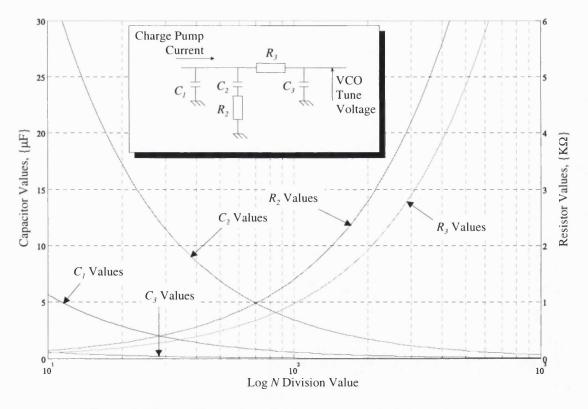

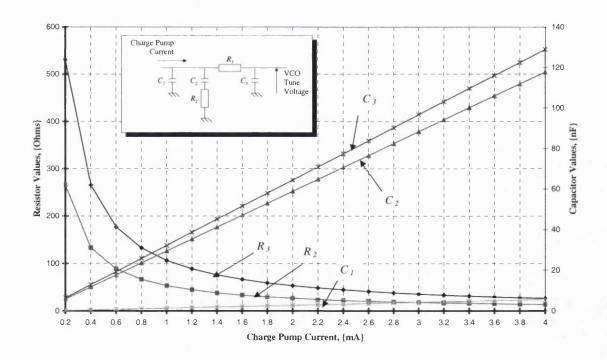

| Figure 3.4 Loop filter values for increasing n-division values                                 |

| Figure 3.5 Typical variation of loop filter values for increasing charge pump gain 45          |

| Figure 3.6 Example of a multiple loop synthesiser                                              |

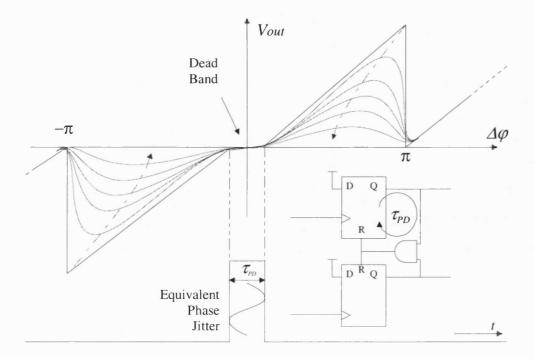

| Figure 3.7 Typical PFD transfer characteristic showing dead-band region                        |

| Figure 3.8 Combination of PFD and charge pump to offset the dead-band region 49                |

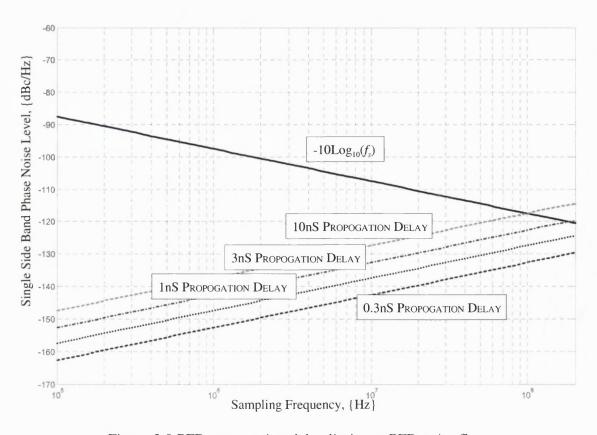

| Figure 3.9 PFD propagation delay limits on PFD noise floor                                     |

| Figure 3.10 Loop filter model with all parasitics added                                        |

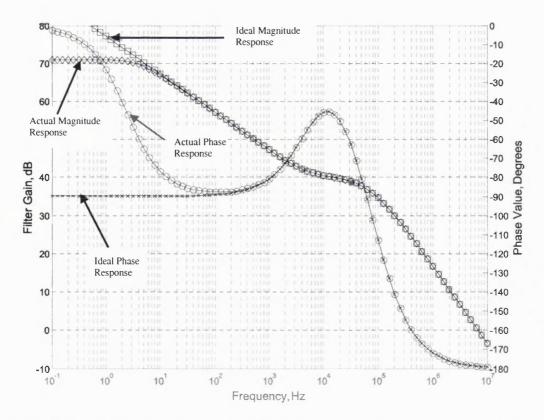

| Figure 3.11 Bode plot showing effects of finite charge pump resistance on loop filter response |

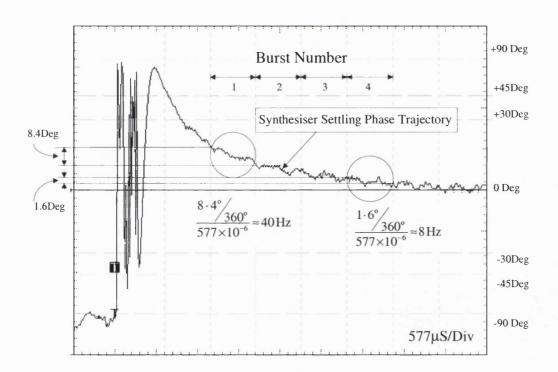

| Figure 3.12 Measured phase error across multiple burst periods and their frequency error       |

### List of Figures

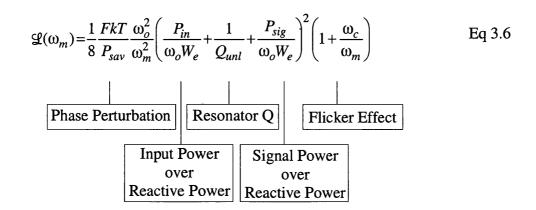

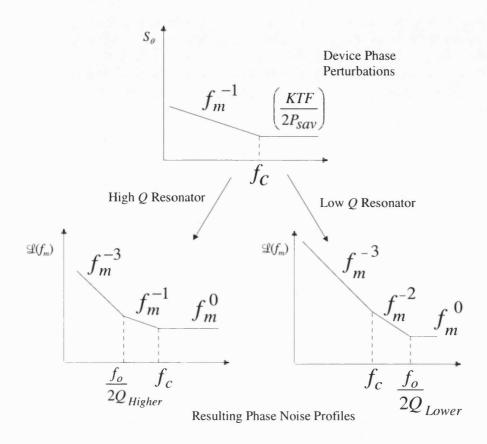

| Figure 3.13 Scherer's description of Leeson's phase noise model, [60]                                             | 57  |

|-------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.14 Effect of high and low-Q resonators on amplification of device noise, [60]                            | ]60 |

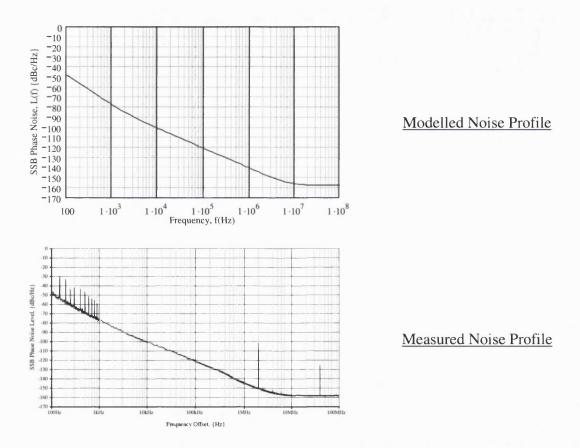

| Figure 3.15 Comparison between VCO phase noise model and measurements                                             | 61  |

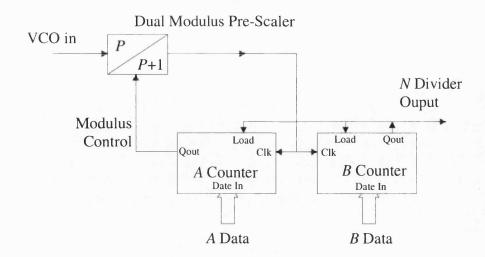

| Figure 3.16 Typical dual modulus divider circuit                                                                  | 63  |

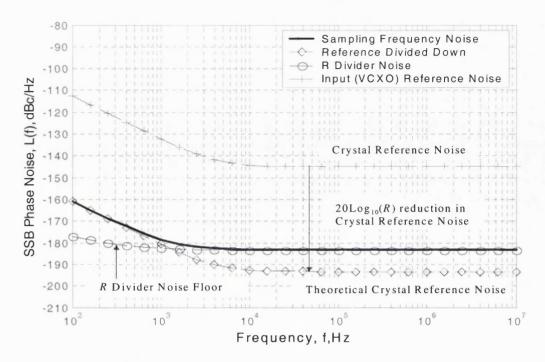

| Figure 3.17 Effect of R division on crystal reference noise into PFD                                              | 65  |

| Figure 3.18 Digital translation of frequency word to phase value in accumulator                                   | 67  |

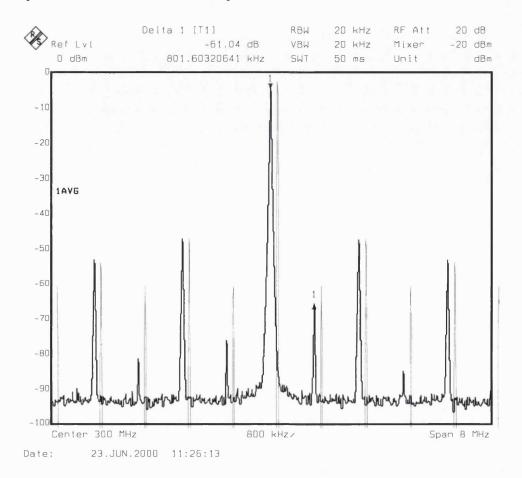

| Figure 3.19 Plot showing correlation between simulated and measured DDS MSB accumulator output frequency spectrum | 68  |

| Figure 3.20 Sunderland sin look up table system, [39]                                                             | 70  |

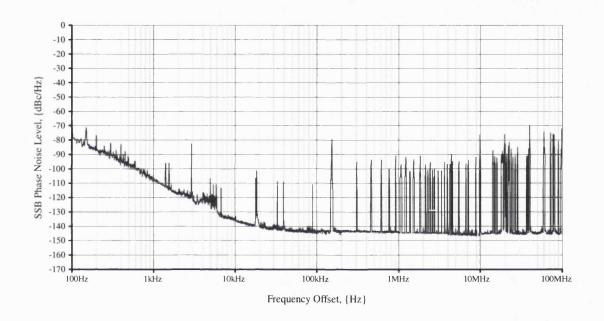

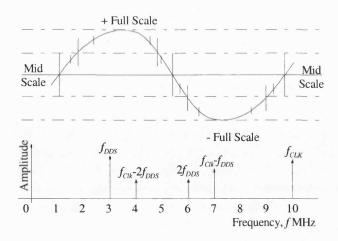

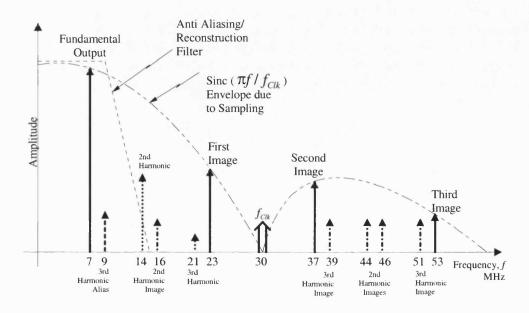

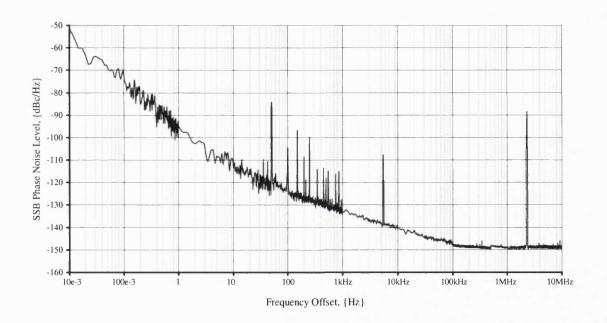

| Figure 3.21 Measured phase noise and spurious performance of the AD9858 DDS                                       | 71  |

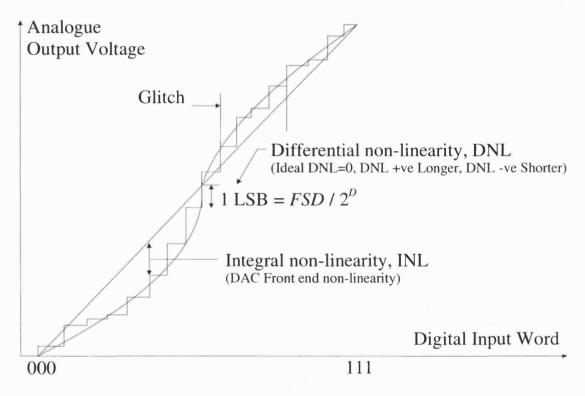

| Figure 3.22 Diagram illustrating typical DAC non-linearity's in a full output sweep, [66]                         | 72  |

| Figure 3.23 Effects of code dependent DAC glitches on spectral output, [66]                                       | 74  |

| Figure 3.24 DDS output showing effects of sampling and DAC non linearity, [63]                                    | 75  |

| Figure 3.25 Measured DDS DAC noise floor                                                                          | 76  |

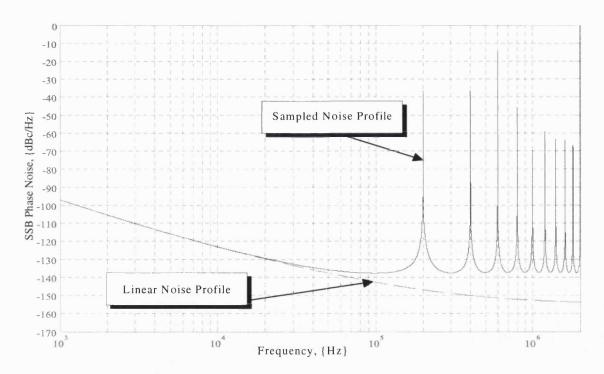

| Figure 4.1 Reference and n-divider noise diagrams                                                                 | 82  |

| Figure 4.2 Sampled reference source phase noise profile                                                           | 83  |

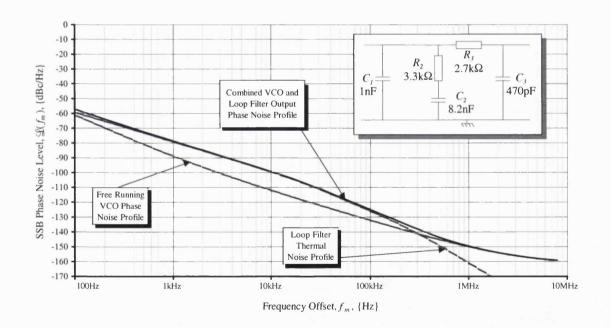

| Figure 4.3 Typical loop filter thermal noise profiles                                                             | 84  |

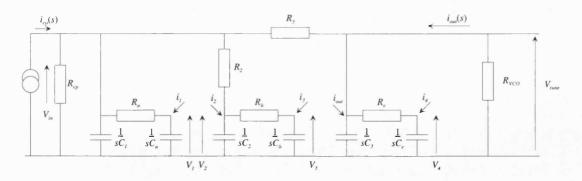

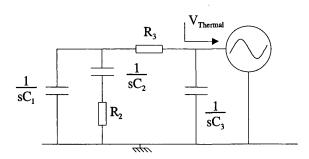

| Figure 4.4 Loop filter thermal noise model                                                                        | 86  |

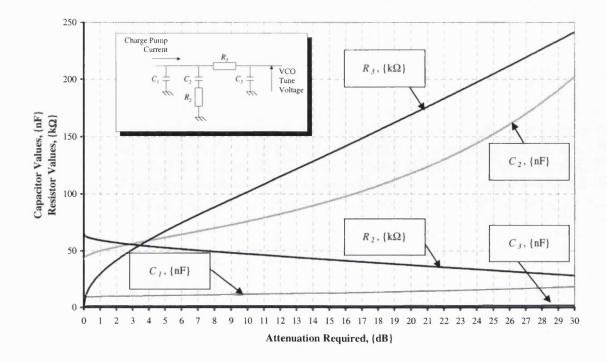

| Figure 4.5 Typical variation of loop filter component values for increasing attenuation requirements              |     |

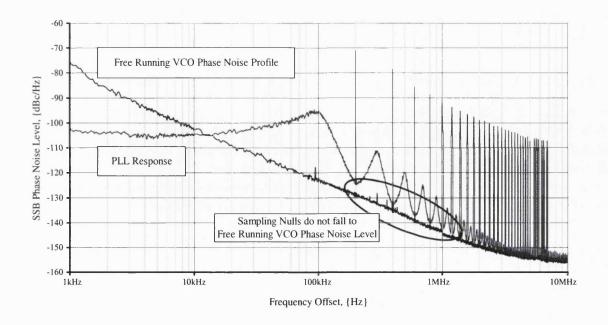

| Figure 4.6 Overlay of two phase noise plots showing null depths                                                   | 88  |

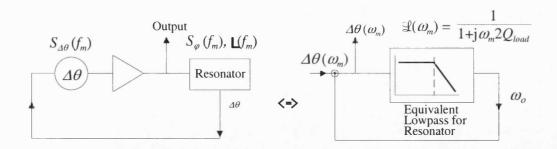

| Figure 4.7 Model of VCO noise injected into closed loop PLL                                                       | 89  |

## List of Figures

| Figure 4.8 Model for aliased VCO noise                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.9 Graphical description of VCO noise terms described in Eq 4.24                                                                                               |

| Figure 4.10 Diagram indicating individual noise source variation through an n-divider chain                                                                            |

| Figure 4.11 VCO Modulation Waveform Caused by Leakage Currents Around the Loop Filter                                                                                  |

| Figure 4.12 Loop noise modulation characteristics from each node to PLL output 99                                                                                      |

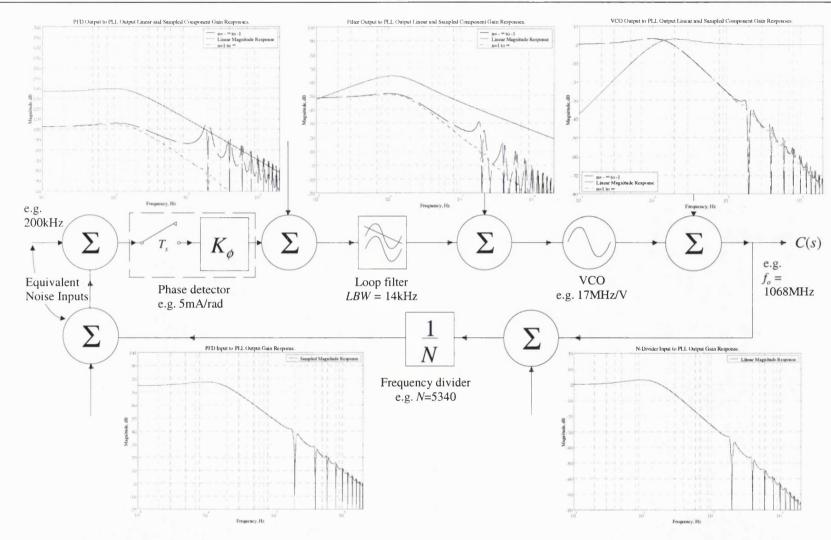

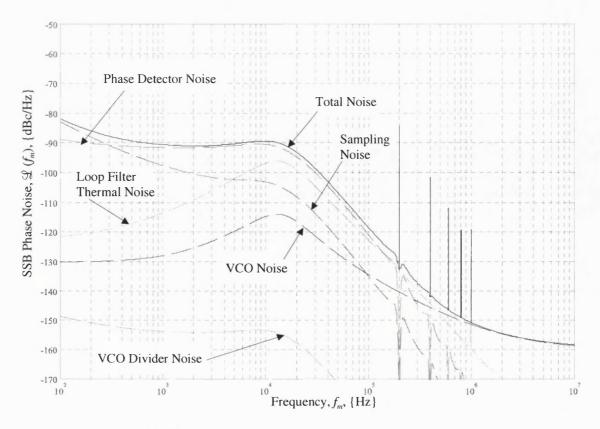

| Figure 4.13 Theoretical composition of measured SSB phase noise                                                                                                        |

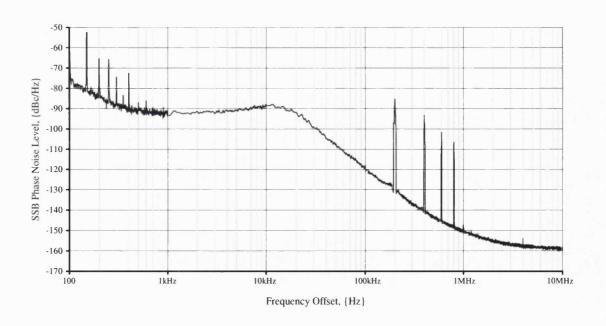

| Figure 4.14 Measured SSB phase noise profile of PLL modelled in Figure 4.13 102                                                                                        |

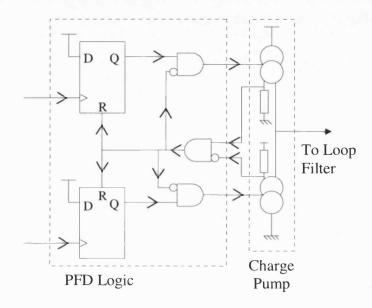

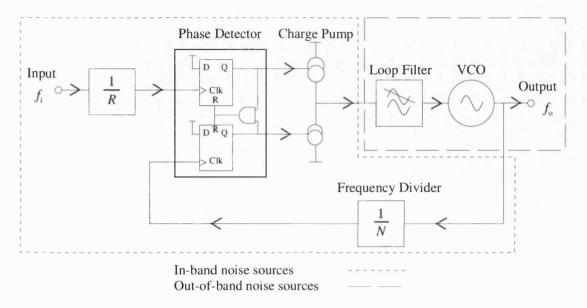

| Figure 5.1 Phase/frequency detector under consideration, within synthesiser 105                                                                                        |

| Figure 5.2 Logic transfer characteristic at the D-type input of the PFD [85] 106                                                                                       |

| Figure 5.3 Effects of pulse duration and timing jitter for increasing PFD operating frequencies                                                                        |

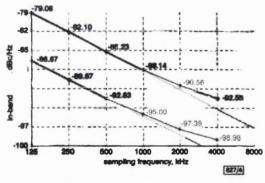

| Figure 5.4 Normalised distribution of measured in-band phase noise                                                                                                     |

| Figure 5.5 Residual phase noise set-up used for three-device measurements                                                                                              |

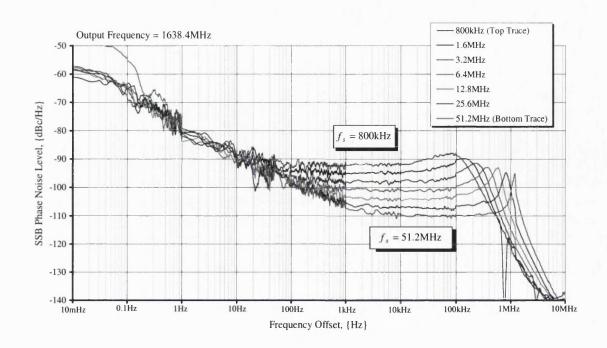

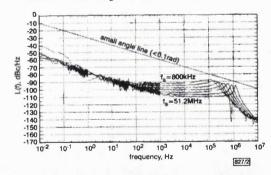

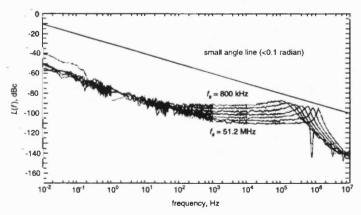

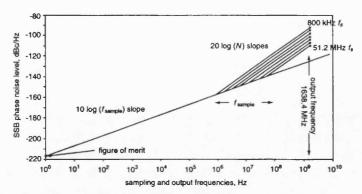

| Figure 5.6 Measured phase noise profiles in a 3 <sup>rd</sup> order, type II PLL synthesiser for PFD operating frequencies of 0.8, 1.6, 3.2, 6.4, 12.8, 25.6 & 51.2MHz |

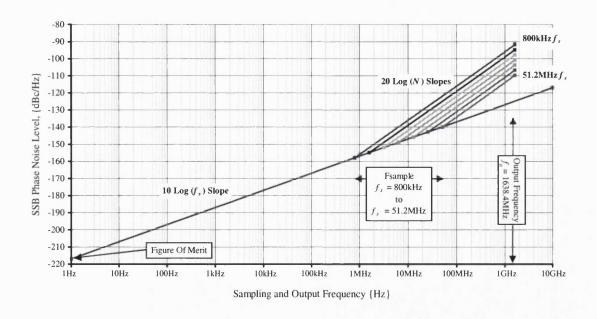

| Figure 5.7 White noise plateaux for different sampling frequencies and $f_o = 1638.4 \text{MHz} 11$                                                                    |

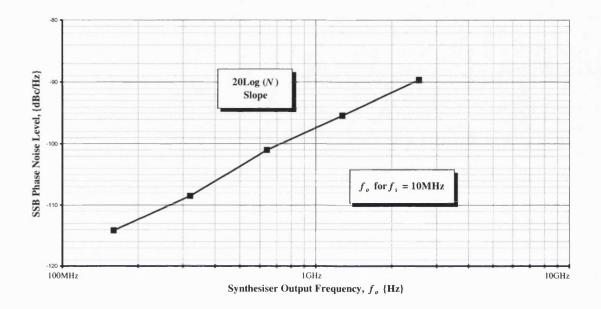

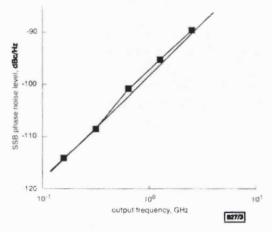

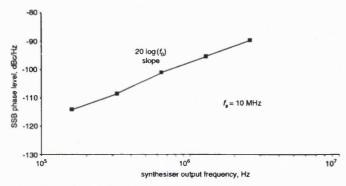

| Figure 5.8 Measured in-band phase noise variations with output frequency for constant sampling frequencies                                                             |

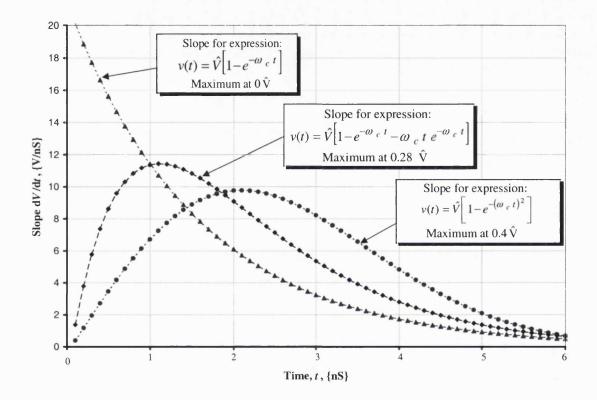

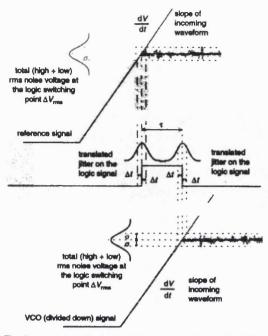

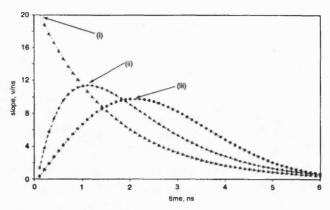

| Figure 5.9 Optimal switching points for different PFD input slope types                                                                                                |

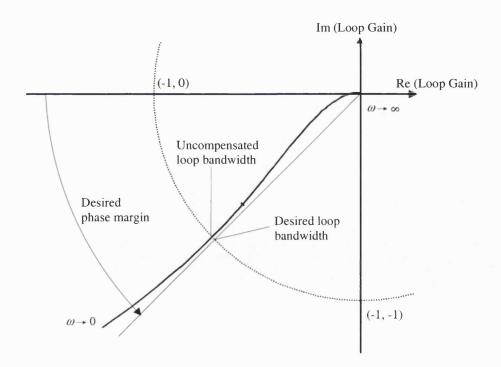

| Figure 6.1 Polar plot of uncompensated type II, fourth-order loop design                                                                                               |

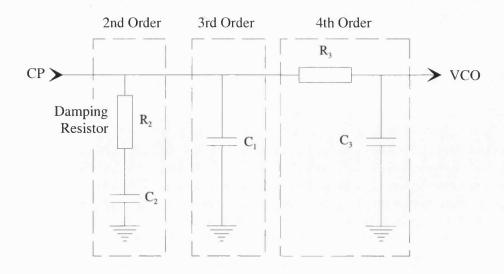

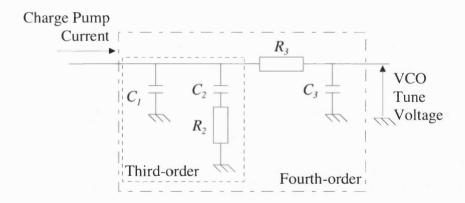

| Figure 6.2 Standard passive loop filter component designations                                                                                                         |

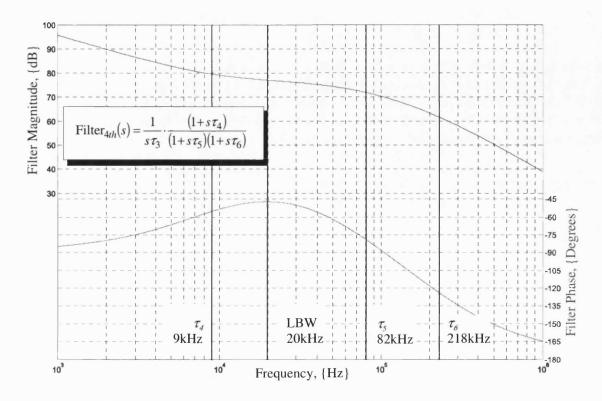

| Figure 6.3 Typical type II, fourth-order loop filter Bode plot showing breakpoints 124                                                                                 |

### List of Figures

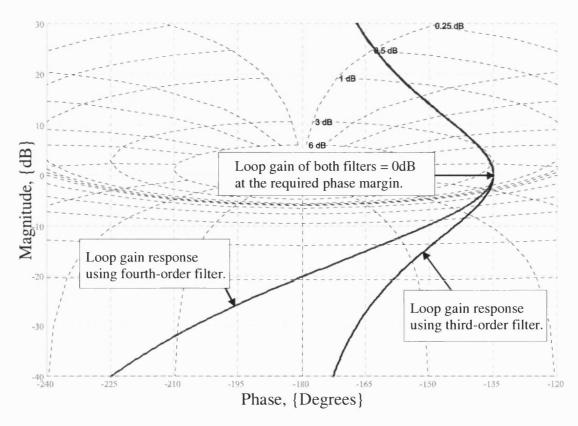

| Figure 6.4 Nichols plot presenting loop gain trajectories using above design formulae126                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

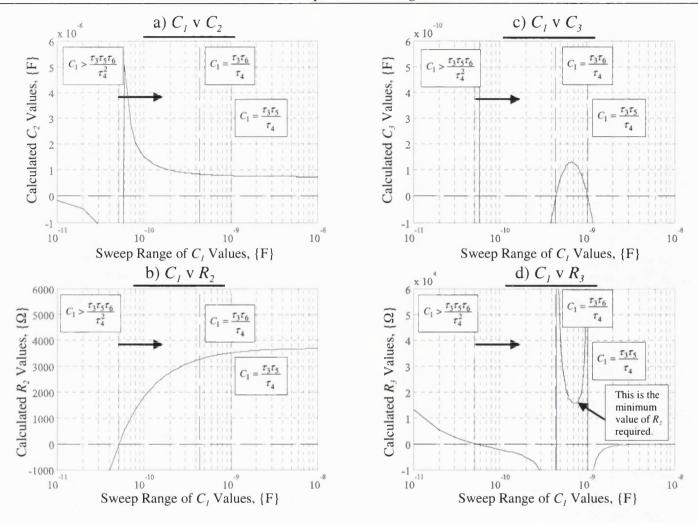

| Figure 6.5 Variation of $C_2$ , $C_3$ , $R_2$ and $R_3$ passive loop filter component values 129                                                                  |

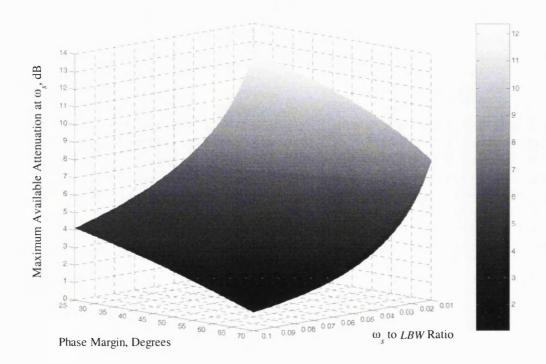

| Figure 6.6 Plot showing variation of maximum attenuation achievable for a given sampling frequency to loop natural frequency ratio at different phase margins 131 |

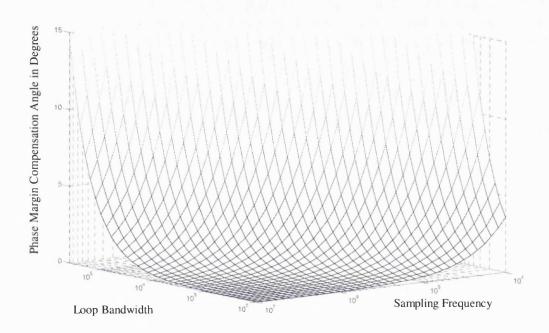

| Figure 6.7 Phase margin variation for differing loop natural frequency to sampling frequencies                                                                    |

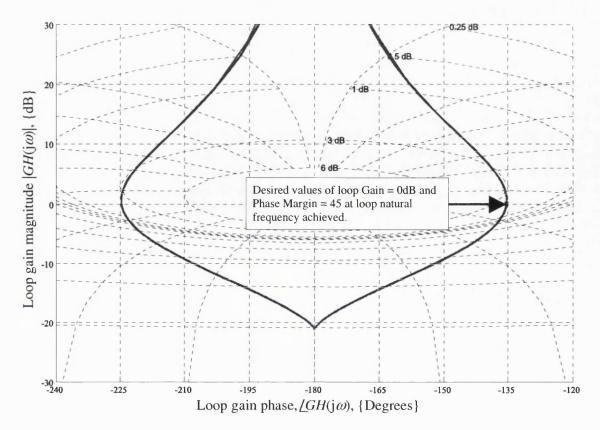

| Figure 6.8 Nichols plot of type II, fourth-order sampled loop trajectory                                                                                          |

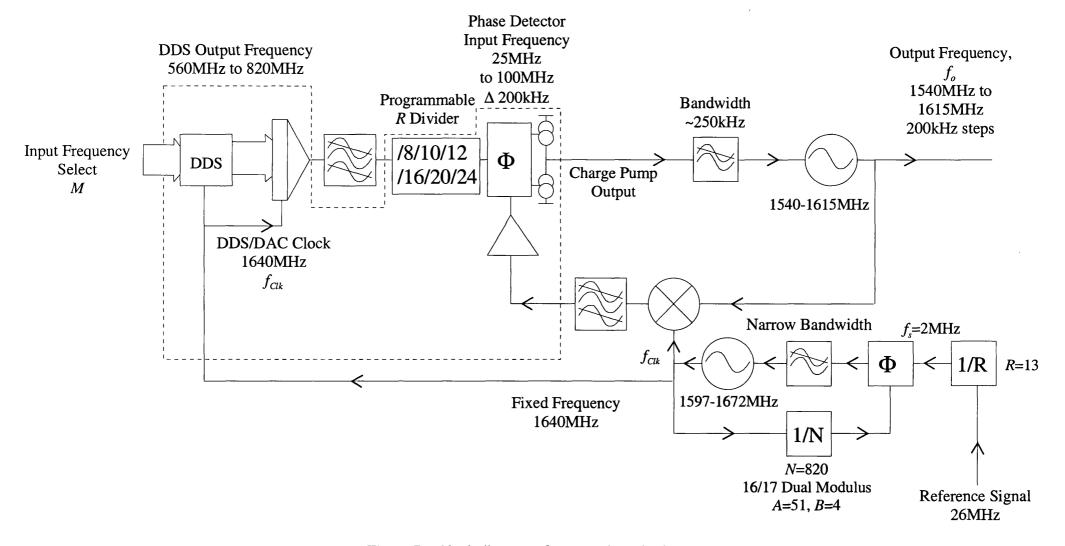

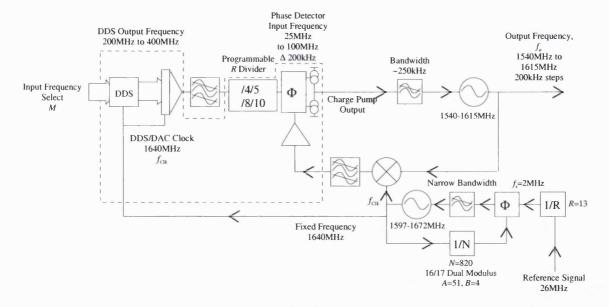

| Figure 7.1 Block diagram of proposed synthesiser                                                                                                                  |

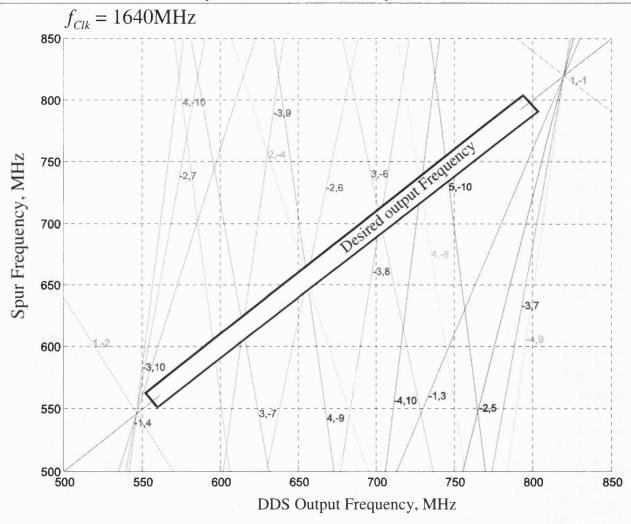

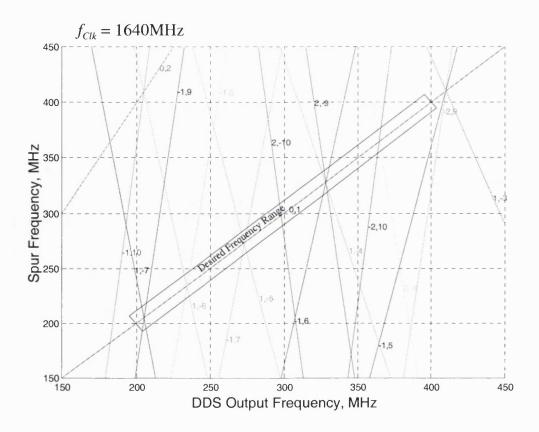

| Figure 7.2 Predicted intermodulation, (spurious) product output from DDS148                                                                                       |

| Figure 7.3 DDS output frequency range and <i>R</i> -divider settings tested                                                                                       |

| Figure 7.4 Spurious prediction for tested DDS set up in synthesiser                                                                                               |

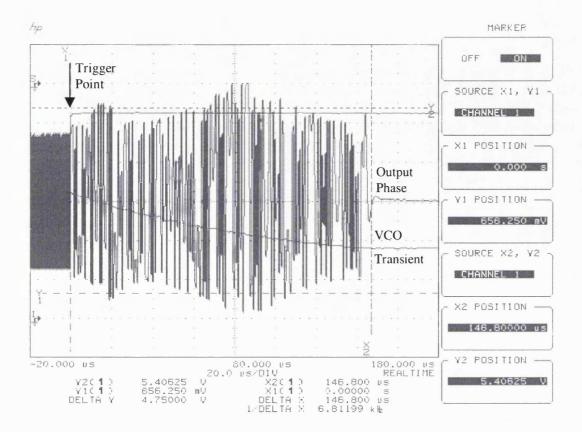

| Figure 7.5 Measured lock time on DDS synthesiser                                                                                                                  |

| Figure 7.6 DAC compensation for loop filter charge                                                                                                                |

| Figure 7.7 Calculated loop filter values for both synthesisers                                                                                                    |

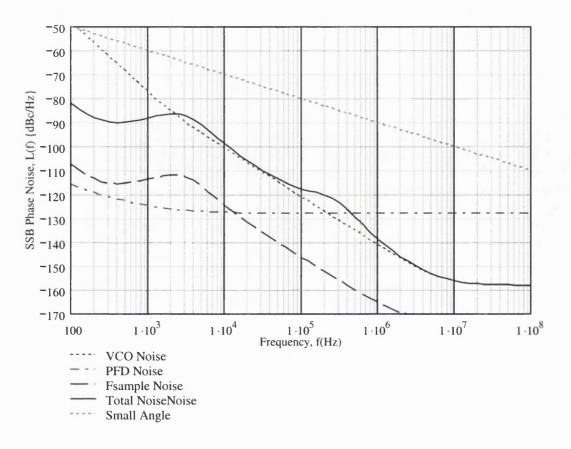

| Figure 7.8 Predicted 1640MHz PLL phase noise profile                                                                                                              |

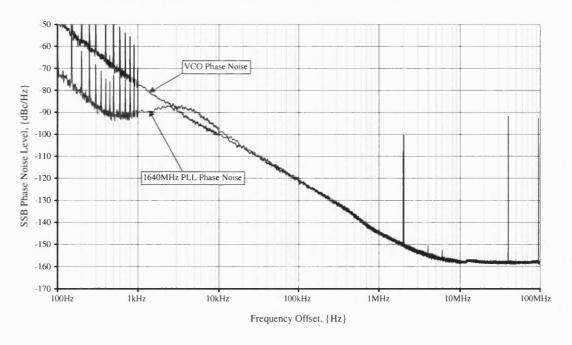

| Figure 7.9 Measured 1640MHz PLL and its free running VCO at 1640MHz 155                                                                                           |

| Figure 7.10 Predicted hybrid DDS PLL phase noise profile                                                                                                          |

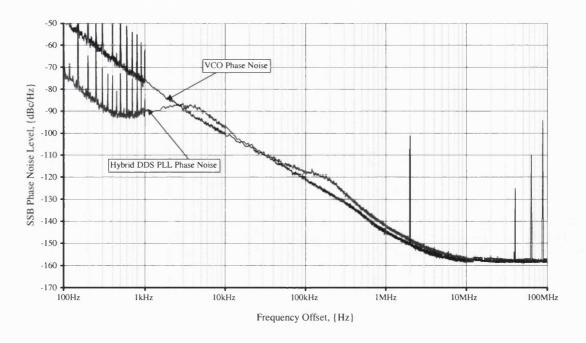

| Figure 7.11 Measured hybrid DDS PLL and its free running VCO at 1552-4MHz 156                                                                                     |

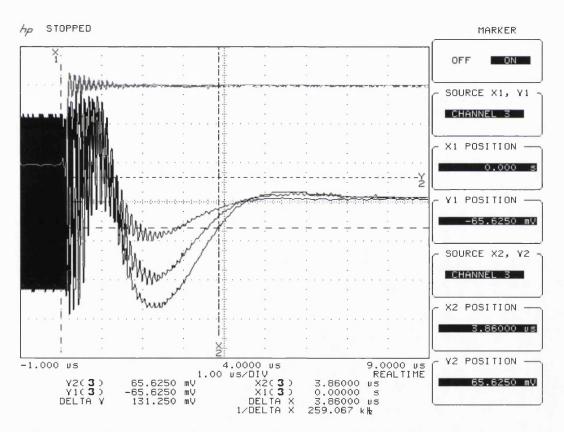

| Figure 7.12 Measured lock time with DAC showing distribution due to voltage variations                                                                            |

# LIST OF TABLES

| Table 3.1 Charge pump driven passive loop filter configurations        | 52  |

|------------------------------------------------------------------------|-----|

| Table 7.1 Generic synthesiser specification for the hybrid Synthesiser | 140 |

| Table 7.2 DDS output frequency range and r-divider settings            | 146 |

| Table 7.3 Loop filter design parameters                                | 153 |

## LIST OF PRINCIPAL SYMBOLS

| SYMBOL                                      | DEFINITION                                                 | UNIT    |

|---------------------------------------------|------------------------------------------------------------|---------|

| $\Delta\phi$                                | Phase Error.                                               | rad     |

| $\Delta\phi_{in}$                           | Input phase jitter.                                        | rad     |

| $\Delta\phi_{pk-pk}(t)$                     | Phase jitter caused by propagation delay in PFD.           | rad     |

| $\Delta \phi_{RMS}(t)$                      | RMS value of phase jitter caused by PFD propagation delay. | rad     |

| $\Delta\phi(\omega_m)$                      | Phase fluctuations at a frequency offset.                  | rad     |

| arDelta arphi                               | PFD input phase difference.                                | rad     |

| $\Delta f_{peak}$                           | Peak frequency deviation.                                  | Hz      |

| $\Delta f_{RMS}$                            | RMS frequency deviation.                                   | Hz      |

| $\Delta V_{RMS}$                            | RMS noise at logic switching point.                        | V       |

| $\Delta t$                                  | Timing jitter.                                             | S       |

| Φ                                           | Phase.                                                     | Deg     |

| α, β, λ                                     | Segments of binary word fed into sine look up table.       | -       |

| $\Delta t$                                  | Timing jitter.                                             | S       |

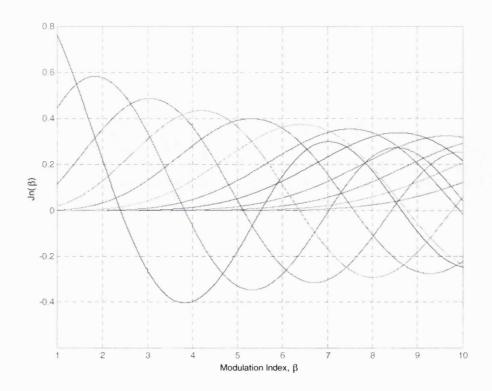

| β                                           | Modulation index.                                          | -       |

| $	heta_d$                                   | Peak phase deviation.                                      | rad     |

| δ                                           | Dielectric loss.                                           |         |

| $\boldsymbol{\mathcal{E}}$                  | Average  DNL  of the DAC.                                  | -       |

| $\phi$                                      | Generic phase value.                                       | Deg     |

| $\phi$ jitter                               | Phase jitter.                                              | rad     |

| $\phi^2_{\ jitter}$                         | RMS phase jitter.                                          | $rad^2$ |

| $\sigma$                                    | Standard deviation.                                        | -       |

| $\tau_1$ , $\tau_2$ , $\tau_3$ , $\tau_4$ , | Generic loop filter time constants.                        | S       |

| $\tau_5$ , $\tau_6$ , $\tau_7$              |                                                            |         |

| $	au_{PD}$                                  | Phase detector propagation delay.                          | S       |

| $	au_{cp}$                                  | Charge pump on period.                                     | S       |

| $\omega$                                    | Angular frequency.                                         | rad/s   |

| $\omega_c$                         | Cut-off frequency.                                    | rad/s |

|------------------------------------|-------------------------------------------------------|-------|

| $\omega_{in}$                      | Angular input frequency.                              | rad/s |

| $\omega_{\!\scriptscriptstyle LO}$ | Angular Local Oscillator frequency.                   | rad/s |

| $\omega_m$                         | Angular modulating frequency offset.                  | rad/s |

| $\omega_n$                         | Loop natural frequency.                               | rad/s |

| $\omega_{o}$                       | Angular output frequency.                             | rad/s |

| $\omega_{\!\scriptscriptstyle RF}$ | Angular Radio Frequency.                              | rad/s |

| $\omega_{s}$                       | Angular Sampling frequency.                           | rad/s |

| A                                  | -Width of digital word in DDS accumulator.            | -     |

|                                    | -Digital divider down counter word.                   | -     |

|                                    | -Signal amplitude.                                    | V     |

| A(t)                               | Amplitude modulated component.                        | V     |

| Atten                              | Attenuation.                                          | dB    |

| a                                  | Generic phase term used in trigonometric identity.    | rad   |

| В                                  | -Bandwidth.                                           | Hz    |

|                                    | -Digital divider down counter word.                   | -     |

| b                                  | Generic phase term used in trigonometric identity.    | rad   |

| C(s)                               | Generic Laplace output signal.                        | -     |

| $C_1$ , $C_2$ , $C_3$              | Loop filter capacitor values.                         | F     |

| D                                  | Width of digital input word applied to DAC.           | -     |

| $Div_{fl}$                         | First Divider flicker noise breakpoint frequency.     | Hz    |

| dv(t)/dt                           | Slope of waveform.                                    | V/s   |

| E(s)                               | Error signal before sampling, (s-domain).             | -     |

| E*(s)                              | Sampled error signal, (s-domain).                     | -     |

| F                                  | Noise factor.                                         | -     |

| F(s)                               | Loop filter Laplace transfer function.                | -     |

| f                                  | Fourier frequency (sideband, offset, baseband).       | Hz    |

| $f_{Clk}$                          | Clock signal frequency supplied to the DDS and mixer. | Hz    |

| $f_c$                              | -Corner frequency.                                    | Hz    |

|                                    | -Cut-off frequency.                                   | Hz    |

| $f_d$                              | Frequency deviation.                                  | Hz    |

| $f_{DDS}$                          | DDS output frequency.                                 | Hz    |

| $f_{LO}$                           | Local Oscillator frequency.                           | Hz    |

| $f_i$                   | Input frequency.               |                                              | Hz     |

|-------------------------|--------------------------------|----------------------------------------------|--------|

| $f_m$                   | Modulating frequency.          |                                              | Hz     |

| $f_m^0$ ,               | Slope of spectral density:     | White phase.                                 |        |

| $f_m^{-1}$ ,            |                                | Flicker phase.                               |        |

| $f_m^{-2}$ ,            |                                | Random walk phase (white FM).                |        |

| $f_m^{-3}$              |                                | Flicker FM.                                  |        |

| $f_o$                   | Output frequency.              |                                              | Hz     |

| $f_{\it offset}$        | Offset frequency from carrie   | r.                                           | Hz     |

| $f_{RF}$                | Radio Frequency.               |                                              | Hz     |

| $f_s$                   | Sampling frequency.            |                                              | Hz     |

| G(s)                    | Open loop forward gain of P    | LL.                                          | Rad/s  |

| GH(s)                   | Loop gain of PLL.              |                                              | Rad/s  |

| h                       | Planck's constant, (6.626×10   | ) <sup>-34</sup> ).                          | J      |

| H(s)                    | Feedback gain.                 |                                              | Rad/s  |

| $I_{Diode}$             | Diode current.                 |                                              | A      |

| $I_{Sat}$               | Diode Saturation current.      |                                              | A      |

| i                       | Current.                       |                                              | A      |

| $i_{cp}$                | Charge pump current into lo    | op filter.                                   | Α      |

| $i_L$                   | Leakage current profile.       |                                              | Α      |

| $i_n(s)$                | Laplace representation of cu   | rrent source into node n.                    | Α      |

| $i_{out}(s)$            | Laplace representation of cu   | rrent out of loop filter.                    | Α      |

| $J_i(oldsymbol{eta})$   | Bessel function of the first k | ind, order $i$ and argument $\beta$ .        | -      |

| K                       | Collective gain of all PLL fr  | equency independent constants.               | mA/V   |

| $K_{VCO}$               | VCO gain.                      |                                              | Hz/V   |

| $K_\phi$                | Phase detector gain.           |                                              | A/rad  |

| $\boldsymbol{k}$        | Boltzmann's constant, (1.38    | $\times 10^{-23}$ ).                         | J/K    |

| $\mathcal{L}(f_m)$      | Single side band phase noise   | e at offset frequency $f_m$ .                | dBc/Hz |

| $\mathcal{L}(\omega_m)$ | Single sideband signal to car  | rrier ratio at offset frequency $\omega_m$ . | dBc/Hz |

| L                       | Binary word length.            |                                              | -      |

| LBW                     | Loop Band Width.               |                                              | Hz     |

| l                       | LSB size in to DAC.            |                                              | -      |

| M                       | The binary equivalent of the   | DDS input word.                              | -      |

| m                       | Multiplier of radio frequency  | y.                                           | -      |

| N                                | Generic n-divider division value.                        | -        |

|----------------------------------|----------------------------------------------------------|----------|

| $N_{Ndiv}(s)$                    | N divider noise.                                         | dBc/Hz   |

| $N_{PFD}(s)$                     | Phase Frequency Detector noise.                          | dBc/Hz   |

| $N_{Rdiv}(s)$                    | Reference divider noise.                                 | dBc/Hz   |

| $N_{Ref}(s)$                     | Reference source noise.                                  | dBc/Hz   |

| $N_{v1}, N_{v2}, N_{v3}, N_{v4}$ | Divider noise voltages.                                  | V        |

| $N_{VCO}(s)$                     | VCO noise.                                               | dBc/Hz   |

| n                                | -Multiplier of local oscillator frequency.               | -        |

|                                  | -Linear value of required loop filter attenuation.       | -        |

| P                                | Dual modulus pre-scaler division value.                  | -        |

| $P_{in}$                         | Input power to active device.                            | W        |

| $P_{out}$                        | Power out.                                               | W        |

| $P_{sav}$                        | Average power to active device.                          | W        |

| $Plateau_{Div}$                  | Divider far out noise floor.                             | dBc/Hz   |

| $Plateau_{Ref}$                  | Reference Oscillator far out noise floor.                | dBc/Hz   |

| $Plateau_{VCO}$                  | VCO far out noise floor.                                 | dBc/Hz   |

| PM                               | Phase Margin.                                            | Deg      |

| Q                                | -Quality factor.                                         | -        |

|                                  | -Capacitor charge.                                       | C        |

| $Q_{load}$                       | Loaded $Q$ of the tuned circuit.                         | -        |

| $Q_{\it unl}$                    | Unloaded $Q$ of the tuned circuit.                       | -        |

| q                                | Charge on an electron, $(1.6 \times 10^{-19})$ .         | C        |

| R                                | Generic R-divider value.                                 | -        |

| R'                               | Resistor resistance value.                               | $\Omega$ |

| $R_2$ , $R_3$                    | Loop filter resistor values.                             | $\Omega$ |

| $\mathit{Ref}_{\mathit{fl}}$     | Reference oscillator flicker noise breakpoint frequency. | Hz       |

| $Ref_{f2}$                       | Reference oscillator half resonator bandwidth frequency. | Hz       |

| RMS                              | Root Mean-Square.                                        | -        |

| $R_{ u}$                         | Equivalent resistance of the varactor diode.             | Ω        |

| S                                | Width of digital word into sine look up table.           | -        |

| $S*_{Flicker}$                   | Sampled spectrum of flicker noise.                       | rad²/Hz  |

| $S_{Flicker}$                    | Spectrum of flicker noise.                               | rad²/Hz  |

| $S_{\Delta\phi}(f_m)$            | Spectral density of phase fluctuations.                  | rad²/Hz  |

| $S\phi_{in}(f_m)$   | Input double-sided spectral density of phase fluctuations.   | rad²/Hz |

|---------------------|--------------------------------------------------------------|---------|

| $S\phi_{out}(f_m)$  | Output double-sided spectral density of phase fluctuations.  | rad²/Hz |

| S                   | Laplace operator.                                            | -       |

| T                   | Absolute temperature.                                        | K       |

| $T_{Clk}$           | Clocking Period.                                             | S       |

| $T_{jitter}$        | Time jitter.                                                 | S       |

| $T_{Ref}$           | Reference cycle period.                                      | S       |

| $T_{\mathcal{S}}$   | Sampling cycle period into phase frequency detector.         | S       |

| t                   | Time.                                                        | S       |

| t <sub>jitter</sub> | RMS DAC aperture jitter.                                     | S       |

| Ŷ                   | Peak amplitude of voltage swing.                             | V       |

| $\overline{V^2}$    | Mean square voltage.                                         | $V^2$   |

| $VCO_{fl}$          | VCO half resonator bandwidth frequency.                      | Hz      |

| $VCO_{f2}$          | VCO flicker noise breakpoint frequency.                      | Hz      |

| $V_{FS}$            | Full-scale DAC output voltage.                               | V       |

| $V_{in}$            | -Input voltage applied to loop filter.                       | V       |

|                     | -Voltage across a diode.                                     | V       |

| $V_{LO}$            | Local oscillator signal voltage.                             | V       |

| $V_n(s)$            | Laplace representation of voltage at node $n$ .              | V       |

| $V_{RF}$            | RF signal voltage (applied to a mixer input).                | V       |

| $V_{\it thermal}$   | -Noise in DAC LSB.                                           | V       |

|                     | -Loop filter thermal noise applied to VCO input.             | V       |

| $V_{tune}$          | voltage applied to VCO input by PLL from loop filter output. | V       |

| $v_n(t)$            | Generic voltage at node n at time t.                         | V       |

| v(s)                | Voltage signal, Laplace domain.                              | V       |

| v(t)                | Voltage Signal, time domain.                                 | V       |

| $W_e$               | Reactive energy within the resonator.                        | W       |

# LIST OF ABBREVIATIONS

| SYMBOL | DEFINITION                                                                           | UNIT                |

|--------|--------------------------------------------------------------------------------------|---------------------|

| 16QAM  | 16 Quadrature Amplitude Modulation.                                                  | -                   |

| 3G     | Third Generation, (WCDMA).                                                           | -                   |

| 3GPP   | 3 <sup>rd</sup> Generation Partnership Project.                                      | -                   |

| AM     | Amplitude Modulation.                                                                | -                   |

| API    | Automatic Phase Interpolation.                                                       | -                   |

| BCD    | Binary Coded Decimal.                                                                | -                   |

| CMOS   | Complementary Metal Oxide Semiconductor.                                             | -                   |

| CP     | Charge Pump.                                                                         | -                   |

| DAC    | Digital to Analogue Converter.                                                       | -                   |

| DC     | Direct Current.                                                                      | -                   |

| DDFS   | Direct Digital Frequency Synthesiser.                                                | -                   |

| DDS    | Direct Digital Synthesis.                                                            | -                   |

| DNL    | Differential Non-Linearity.                                                          | -                   |

| DUT    | Device Under Test.                                                                   | -                   |

| ENOB   | Effective Number Of Bits.                                                            | -                   |

| EVM    | Error Vector Magnitude.                                                              | %                   |

| FET    | Field Effect Transistor.                                                             | -                   |

| FOM    | Figure Of Merit.                                                                     | dBc/Hz <sup>2</sup> |

| FSD    | Full Scale Deviation.                                                                | -                   |

| GSHF   | Generalised Sample-Hold Function.                                                    | -                   |

| GSPS   | Giga Samples Per Second.                                                             | Hz                  |

| GSM    | Global System for Mobile communications, (formally known as Groupe Speciale Mobile). | -                   |

| HSDPA  | High Speed Data Packet Access.                                                       | -                   |

| IC     | Integrated Circuit.                                                                  | -                   |

| IEE    | Institute of Electronic Engineers.                                                   | -                   |

| IF     | Intermediate Frequency.                                                              | Hz                  |

### List Of Abbreviations

| INL   | Integral Non-Linearity.                                 | -      |

|-------|---------------------------------------------------------|--------|

| InP   | Indium Phosphate.                                       | -      |

| IQ    | In-phase, Quadrature-phase.                             | -      |

| LO    | Local Oscillator.                                       | -      |

| LSB   | Least Significant Bit.                                  | -      |

| MSB   | Most Significant Bit.                                   | -      |

| NCO   | Numerically Controlled Oscillator.                      | -      |

| PCB   | Printed Circuit Board.                                  | -      |

| PFD   | Phase Frequency Detector.                               | -      |

| PDF   | Probability Density Function.                           | -      |

| PLL   | Phase Locked Loop.                                      | -      |

| PM    | Phase Modulated.                                        | -      |

| PSD   | Power Spectral Density, (single side-band phase noise). | dBc/Hz |

| PWM   | Pulse Width Modulated.                                  | -      |

| ROM   | Read Only Memory.                                       | -      |

| RF    | Radio Frequency.                                        | Hz     |

| RMS   | Root Mean Square.                                       | -      |

| SD    | Standard Deviation.                                     | -      |

| SFDR  | Spurious Free Dynamic Range.                            | -      |

| SNR   | Signal to Noise Ratio.                                  | _      |

| SSB   | Single Side-Band.                                       | -      |

| TDMA  | Time Division Multiple Access.                          | -      |

| VCO   | Voltage Controlled Oscillator.                          | -      |

| WCDMA | Wide-band Code Division Multiple Access.                | -      |

| ZOH   | Zero Order Hold.                                        | -      |

#### 1 INTRODUCTION

#### 1.1 Frequency Synthesis in Mobile Communications

Over the last decade, the extraordinarily rapid growth in mobile communications for an ever-expanding variety of different applications has resulted in undue stress on the principal bottleneck of radio spectrum. This precious commodity has recently led to vast sums of money being exchanged for very small allocations of radio space. Universal to all systems and standards competing for this radio space are specifications defining the allowable amount of frequency drift and spurious emissions that each system can impart on its neighbours. For a limited number of applications simple stable oscillators will suffice, however, almost all higher frequency applications use a frequency synthesiser to meet the system specifications, irrespective of whether the system requires phase coherency or not, [1]. As a result, frequency synthesisers have become an intrinsic part of all modern coherent communications systems. Their value lies in their ability to synthesise another frequency from a given reference source and then continue to maintain phase coherence with that reference source.

Throughout this decade, the evolution of synthesiser technology within mobile communications has been a cyclic process dependent upon the demands of the standard commanding the highest attention at any given time. Within mobile communications, the base station has always borne the stress of the tightest operational specifications, which has continually pushed their synthesised local oscillator sources to their operational limits. For second generation GSM base station applications using baseband hopping, simple synthesisers were used to meet the basic GSM blocking and far out noise specifications. With the advent of third generation GSM systems requiring frequency agility in addition to phase noise performance, the universally adopted solution was a compromise between phase noise and a mediocre settling time using two identical synthesisers operating in parallel, (the "ping-pong" synthesiser). The preferred

solution remains a single synthesiser, which has yet to be satisfactorily fulfilled. Currently the evolution of mobile communications into 3G WCDMA systems has shifted the emphasis to power amplifier and power control performance, whilst re-using the well-established second-generation GSM local oscillator sources whose refined performance now exceeds WCDMA requirements. This downturn in synthesiser performance expectations is likely to be short lived with commercial pressure striving for a universal system capable of supporting multiple carriers with different standards across multiple bands, (the "Multi-Radio" concept) and the proposed introduction of different modulation formats in 3GPP WCDMA systems<sup>1</sup>. To simultaneously satisfy these combined applications requires synthesisers capable of meeting a composite of the most challenging aspects from each specification, for each application.

This thesis focuses on understanding and modelling the noise and spurious products within a combination of analogue phase-locked loop, (PLL) and direct digital synthesis, (DDS) units and how to manage these quantities in the design of one example of a frequency agile, low noise synthesiser.

#### **1.2** Scope Of The Thesis

The objective of this work is to produce a synthesiser capable of meeting the exacting demands of a multi-radio application. To achieve this, the philosophy has been to thoroughly understand and evaluate the performance of each element used within the synthesiser and exploit the most promising techniques to arrive at the solution offered here. This necessarily requires that each element is pushed to the edge of its performance envelope, within the confines of current technology. The purpose of this investigation is to predict these limits through simulation, then to design a suitable synthesiser to verify these models against measurements from the proposed system.

<sup>&</sup>lt;sup>1</sup> Version 5 of the 3GPP standard is expected to introduce HSDPA capability [2], whilst Version 6 is expected to introduce 16QAM modulation, [3].

#### 1.3 Principal Contributions Of This Work

As a direct result of this work the following advances have been achieved.

- 1) Two original techniques have been developed (and patents filed):

- The DAC at the output of a direct digital synthesiser is replaced by a VCO, (controlled by the DDS accumulator), giving a greater level of spectral purity and requires less DC power. Although this idea was not implemented within this work, its inception was a consequence of thoroughly understanding the DDS architecture, section 3.5.

- ii The speed-up technique developed to overcome the problems of cycle slipping proved particularly effective. Because no references to this technique were found, Nokia has applied for a patent to protect this idea.

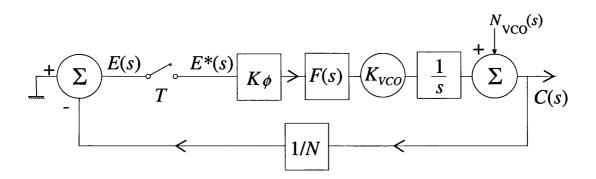

- 2) In chapter 4, an original analysis, (valid for sampled systems), has been developed which is used to account for each uncorrelated noise source within a sampled phase locked loop.

- In chapter 5 an original mathematical analysis is presented which accounts for the contribution of the PFD noise to in-band synthesiser phase noise and how it is related to device parameters. This work has been published in IEE Electronics Letters, [4], and IEE Proceedings, appendix A5.

- 4) In chapter 6, a novel and simple method is presented for type II, fourth-order loop filter design<sup>2</sup>.

- In chapter 7 an original hybrid synthesiser technique is introduced which has been incorporated in the latest Analog Devices DDS chip, the AD9854, [6]. This part has now been released for sale, prompting a good deal of commercial interest. This hybrid DDS based application was displayed on the front cover of the September 2002 edition of the Wireless Systems Design magazine, appendix A6.

<sup>&</sup>lt;sup>2</sup> During the course of this investigation over a dozen different publications were found addressing this problem each with their own interpretation of third and fourth order loop filter design.

#### 1.4 Thesis Outline

The principal contributions of this work are spread across the three chapters that are concerned with phase noise modelling and the verification of these noise models within this demanding application.

Chapter 2 provides a brief history of frequency synthesisers and how they have subdivided into fractional-n and DDS synthesisers.

Chapter 3 considers the basic frequency synthesiser in its many forms with particular emphasis on the building blocks used within the integrated PLL and DDS solution considered in chapter 7.

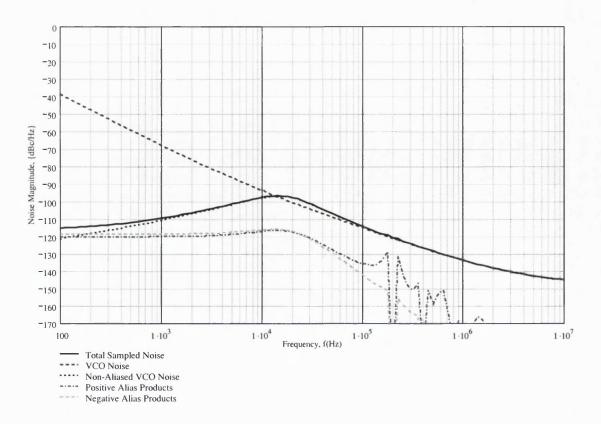

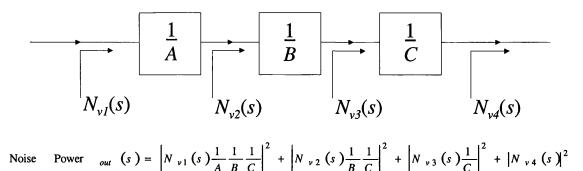

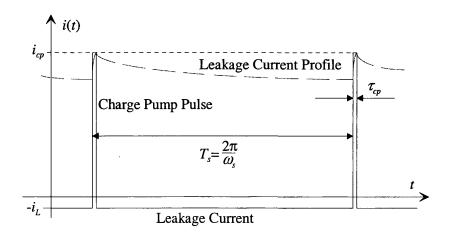

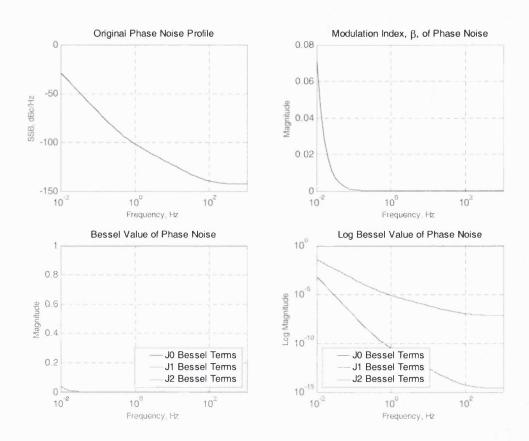

Chapter 4 provides an in-depth mathematical analysis of the different phase noise mechanisms found within a closed-loop PLL system. Attention is drawn to the mathematics developed in this chapter, which deal with the modelling of different phase noise sources in the sampled loop. The complete noise transfer formulae constructed from the summation of each uncorrelated noise source within the sampled phase locked loop, give results that match practical measurement results. However, several precursory laboratory measurements soon demonstrated the inadequacies of many of the noise models commonly offered, especially when pushed to their limits. These findings expanded the work, requiring the development of more rigorous mathematical models to accurately predict the digital phase frequency detector noise performance within a synthesiser, when pushed to its extremes, as in this study.

Chapter 5 demonstrates the significance of the PFD noise and its impact on in-band<sup>3</sup> phase noise and accordingly pays special attention to deriving an accurate noise model, correctly reflecting the PFD noise behaviour in all synthesiser applications. Contained within this chapter is an innovative mathematical insight into how the PFD device noises are manifest in the overall PLL phase noise profile, which became the subject of both an IEE Electronics Letter and an IEE Proceedings paper.

<sup>&</sup>lt;sup>3</sup> The term "in-band" will be used throughout this document to describe the performance inside the loop bandwidth.

To complement the sampled loop phase noise analysis, chapter 6 considers the design of third and fourth-order loop filters, to ensure the required phase margin is achieved. The fourth-order loop filter design equations described in chapter 6, are believed to be new and creative.

Building on this foundation work, a low noise, frequency agile synthesiser solution is presented in chapter 7, with measurement results to verify the phase noise predictions. This synthesiser uses a DDS based hybrid architecture, which was considered to be sufficiently original that Analog Devices used the concept as the model for a new generation, 1GSPS DDS based synthesiser chip, the AD9858 that they were developing. This part has now been released and has since become the subject of a cover feature in the Wireless Systems Design magazine, appendix A6, which describes the integration of this chip in this synthesiser architecture.

Chapter 8 concludes with a summary of the work to date, and how it could proceed to investigate those areas that fell outside the remit of this study.

As a consequence of this study and the innovation required to overcome some practical implementation difficulties, Nokia submitted two patent applications. The first of these two patents successfully passed the prosecution stage in October 2002.

### 2 THE HISTORY OF FREQUENCY SYNTHESIS

#### 2.1 The Origins Of Frequency Synthesis

Perhaps the earliest mention of a sampled, phase locked oscillating system, was by McCrea in 1929, [7]. In this system, the phase of a precision pendulum, used as a reference source, was electrically monitored and compared with the angular position of a synchronous motor, (linked to some large electric generators), to provide a pulse width modulated error signal. This error signal adjusted the spring loading on the governor and thereby corrected the frequency of the generator by changing its load. The techniques used in this system are still applied to modern, charge pump driven, phase locked loops.

One of the earliest descriptions of a free running electronic oscillator, (the key controlled element within a synthesiser), can be found in a patent filed in 1916 by Alexanderson, [8]. Whilst it was only much later in 1932 that the first published account of frequency locking an oscillator was given by De Bellescize, [9], in which an oscillator is described as locked to the incoming radio signal. In 1935, in his paper on frequency control, Travis [10], summarised the need for frequency synthesis as:

"some way of supplementing the accuracy of manual tuning by more or less automatic means. Some method of bringing the signal carrier precisely to the centre of its intermediate-frequency band and anchoring it there in spite of small maladjustments of tuning or others that subsequently arise from thermal changes and the like".

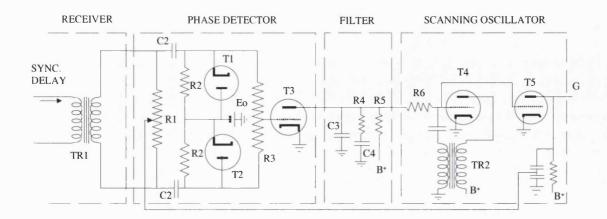

In these early applications the emphasis was on frequency alignment using frequency discriminators whose operation was well understood, [11]. It was only later, in 1943, when the concepts of television were being developed that phase and frequency control were proposed by Wendt, [12], and Finden, [13], using systems which are familiar

today, Figure 2.1. These advances were necessary to ensure the phase coherence essential for proper television display reproduction, [14].

Figure 2.1 Wendt's proposal for a phase locked loop, [12, fig 5]

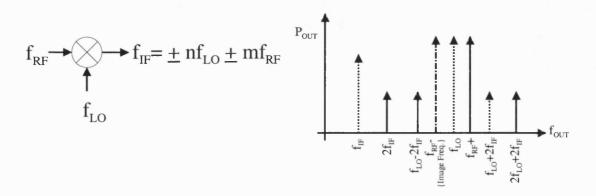

To synthesise one signal from another, non-linear circuit elements were commonly used, [15], however these were open-loop systems that suffer the disadvantages of noise degradation and distortion due to variations of the non-linear elements through ageing and thermal effects. A typical synthesiser would use a combination of multipliers, dividers and mixers to synthesise the required frequency, with each new frequency requiring a different configuration dependent upon the division and multiplication ratios available. Surprisingly, one of the earliest references to the use of digital dividers as the feedback element in a closed loop system is in a patent, "Frequency Multiplier and Frequency Waveform Generator" filed by Sepe *et al.* in 1968, [16]<sup>4</sup>. Using digital dividers in the feedback path of a phase locked loop, (PLL), allowed frequency synthesisers to easily provide output frequencies, which were not derived by cascaded, multiply, divide and mix systems but instead were a simple multiplication of the PLL's sampling frequency.

It was around the 1960s that the concept of the digital phase accumulator became reality, splitting the evolution of frequency synthesisers into two paths; i.e. direct digital synthesis, (DDS), and fractional-n techniques, each using the digital accumulator as their core. Subtly, there is a distinct difference in the purpose of the digital accumulator

<sup>&</sup>lt;sup>4</sup> A patent should not be granted if *prior art* can be established or the concept is deemed obvious to someone "skilled in the art". Patents have been adopted as the milestones in the history of frequency synthesis because their very existence suggests no previous knowledge of the technique was known, thus classifying them as new at that time.

between fractional-n and DDS applications. Within fractional-n, the carry-out (overflow) signal accounts for a complete cycle overflow when driving the integer n-dividers. Conversely for DDS, the digital word representing the current phase value held in the digital accumulator, is used as the basis of the DDS output sinusoid. With the evolution of the digital accumulator came the ability to accurately track phase within digital dividers, which moved analogue synthesiser evolution into fractional-n development.

#### 2.2 Fractional-N Synthesisers

Fractional-n frequency synthesis is a frequency technique that seeks to increase the phase frequency detector, (PFD), sampling frequency beyond the minimum PLL resolution achievable using integer-n dividers. This increase in PFD sampling frequency offers the freedom of larger loop bandwidths than would otherwise be possible with integer-n loops requiring small raster values. Furthermore, the increase in PFD sampling frequency reduces the level of in-band phase noise, facilitating increased loop bandwidths to improve the synthesiser's overall noise performance. To achieve this objective, the integer-n dividers are digitally modulated so that their mean division value equals the desired integer plus fractional division value required to raise the PFD sampling frequency relative to the desired output frequency.

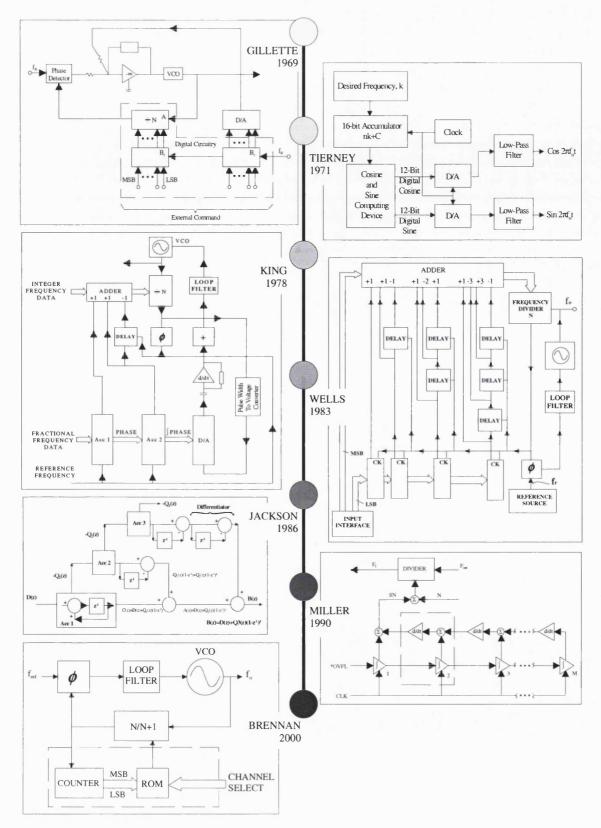

The evolution of fractional-n techniques is commercially very sensitive and is perhaps best traced through some key patents released over the last three decades, Figure 2.2. Although nowadays the trend has been towards using all digital, sigma delta noise shaping techniques, arguably the roots of fractional-n frequency synthesis stem from the Digiphase® principle described by Gillete, [17, 18]. Within this technique a second register tracks the required fractional offset and adds back the missing cycle by incrementing the n-division value for one reference period. Complications arise due to the addition of this additional cycle causing unwanted modulation sidebands to appear, therefore a compensation digital to analogue converter, (DAC), was required to minimise the DC ripple caused on the VCO tune line. This technique is limited because it requires accurate open-loop DAC current balancing to achieve substantial improvements of in-band phase noise performance, [19]. With the introduction of DDS in 1971, [20], the concept of using a digital accumulator to control phase was adopted,

however using a single digital accumulator in a synthesiser still requires an analogue to digital converter to correct for the strong n-divider modulation products thereby generated. The use of a DAC to correct for the fractional-n modulation is often referred to as automatic phase interpolation, (API). In 1978<sup>5</sup> the landmark patent by King, [22], was filed whose significance lies in the cascade of two digital accumulators. This technique, sometimes referred to as "Kingphase", introduced two important features; 1) to provide an integrated phase correction signal into the DAC, thereby reducing the stress on DAC performance, and more importantly, 2) a digital delay of the second accumulator carry signal which is weighted and summed with the carry out of the first digital accumulator before being applied as the n-divider fractional modulation. Concept 2) was expanded by Wells in 1983, [23], to arrive at a cascade of digital accumulators whose respective carry-out signals were delayed, weighted and summed in accordance with Pascal's triangle before being applied as the fractional n-divider modulation, giving the first all digital noise shaping sequence and making the DAC redundant<sup>6</sup>. Jackson's patent, [24], released in 1986, developed the multiple accumulators into the first sigma delta architecture used within a PLL and included the mathematics to demonstrate the noise shaping properties. In 1990, two almost identical patents by Miller and Gaskell et al., [25, 26], were simultaneously released detailing full sigma delta architectures spawning the current multitude of patents each offering their own improved version of sigma delta noise shaping algorithm. One of the latest patents offered by Brennan et al., [27], offers an almost perfect high speed sigma delta system using sigma delta coefficients which are calculated off-line using floating point arithmetic developed by Walkington, [28], to a very high degree of accuracy.

<sup>5</sup> All references to patent dates are in terms of their original filing date.

<sup>&</sup>lt;sup>6</sup> Worthy of mention at this point is that in 1977 Ritchie proposed a higher order sigma delta loop filter using a cascade of integrators, [21].

Figure 2.2 Summary of evolution of fractional-n through relevant published diagrams

Although sigma delta modulation techniques have been universally adopted as the answer to fractional-n frequency synthesis, they have their origins in work carried out in the 1940's and 1950's primarily for voice transmission in telephony applications, [29].

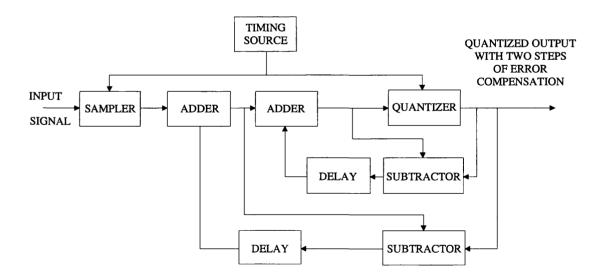

One of the earliest accounts of digital noise shaping can be traced back to the delta modulator described in 1952 by de Jager [30]. The better-known patent by Cutler *et al.* filed in 1954, [31], quickly superseded his work and describes the sigma delta modulator concept, Figure 2.3. The fundamental difference between sigma delta and a delta sigma, which has led to much confusion, is in the placement of the filtering either in the forward or in the feedback path of the system and the subsequent introduction of the two terms. Later in 1962 Inose *et al.*, [32], extended the concept by introducing the delta sigma modulator and presenting the first detailed mathematical analysis of this noise-shaping technique. Starting in 1974, Candy, [33], released a succession of articles that introduced the term "sigma delta" and its application in analogue to digital converters, which Ritchie extended in 1977 to give higher-order sigma delta filtering, by using a cascade of integrators, [21].

As described in the aforementioned text, sigma delta techniques were adopted in frequency synthesis as a repeatable means of increasing the PFD sampling frequency, whilst still confined to using integer-n dividers in the feedback path of a PLL. Digitally controlled sigma delta modulation of the integer-n dividers provides a reliable mean fractional division value, whilst minimising the spurious products thus produced.

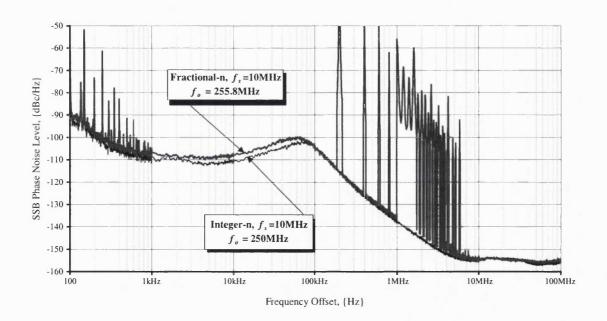

Figure 2.3 Cutler, [31], implementation of a sigma delta modulator

To date, not one commercially available single-chip fractional-n part has been released which demonstrates the expected phase noise improvement theoretically available whilst still offering the spurious performance of integer-n synthesisers. Unfortunately, neither fractional nor integer-n based synthesisers are likely to offer the in-band phase

noise performance required to increase the loop bandwidths to the necessary offsets essential to meet the demanding single synthesiser GSM requirements, for lock time.

It is worth noting that there have been several very successful single-loop fractional-n, laboratory grade signal generators, available within the test equipment market, which also deploys analogue noise suppression techniques to achieve their superior phase noise performance [34, 35].

In contrast to fractional-n synthesiser evolution has been the parallel development of direct digital synthesis, which also relies on the digital accumulator to retain the synthesiser's phase at any given moment in time.

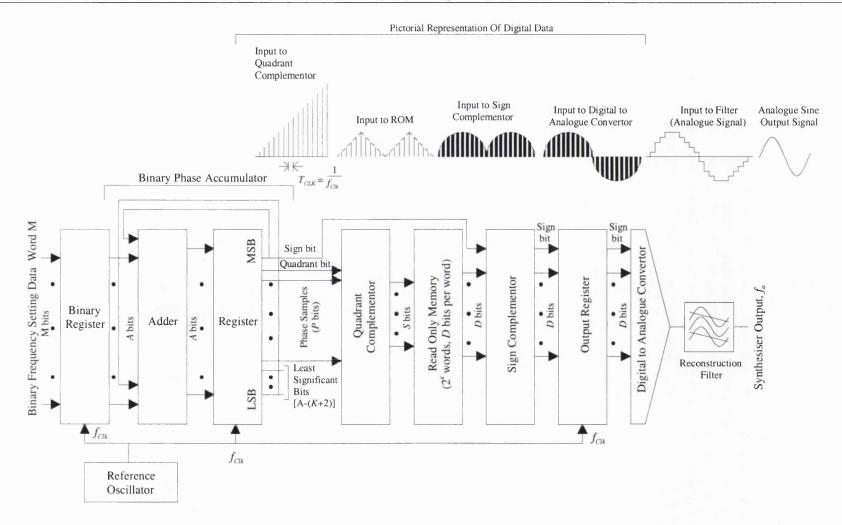

#### 2.3 The Direct Digital Synthesiser

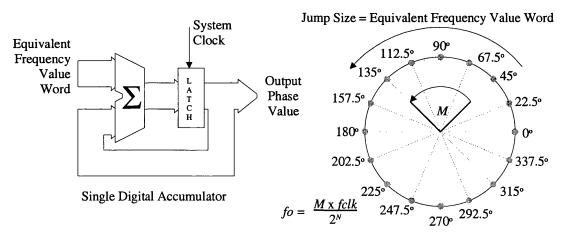

Direct digital synthesis, (DDS) is an all-digital frequency synthesis scheme that employs a single digital accumulator, which is clocked by the input clock signal to maintain the current sine wave phase value, Figure 2.4. The roll over rate of this digital accumulator is set by the digital input word, which is constantly being added to the result from the previous summation, processed by the digital accumulator. The output of the digital accumulator is non-linearly mapped onto the equivalent sine wave amplitude value before being converted to an analogue signal value by the output digital to analogue converter.

One of the earliest accounts of direct digital frequency synthesis, (DDS), can be traced to a patent filed by Cliff in 1966, for an all-digital synthesiser, [36]. This synthesiser was capable of synthesising a pulse sequence from a master clock source using a digital accumulator and an array of digital divider circuits. Later in 1970 Webb, [37], filed a patent for a "Digital Signal Generator Synthesizer" in which he proposed using a digital accumulator with a "Sum Register" and memory to convert  $\omega_o T_{Clk}$  to  $\cos(\omega_o T_{Clk})$  to feed a DAC giving a low frequency function generator. Co-incidentally, an influential paper was published in 1971 by Tierney *et al.*, [20], offering a thorough analysis of a complete DDS architecture using a digital accumulator, sine look up table and DAC, Figure 2.4. It is generally accepted that this landmark paper, almost undoubtedly

written in isolation<sup>7</sup> of Webb's patent because of the time scales and processing of each of these two publications, defines the DDS architecture that has been universally adopted today.

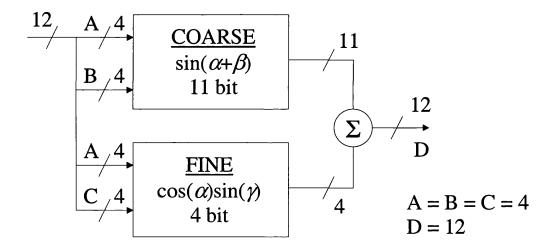

Several notable modifications to the DDS core aimed at raising the maximum operational speed have addressed the compression algorithm used in the sine look up table. A technique first proposed by Hutchinson, [38], was further modified by Sunderland *et al.*, [39], to give what is perhaps one of the most popular and simple look up table compression schemes. An interesting alternative to the look up table, which has been adopted in DDS applications, is the Cordic algorithm first proposed in 1960 by Volder, [40], which generates the sine amplitude data in real-time. To overcome the infamous DDS spurious problem, Wheatley *et al.*, [41], are credited with using dithering as a means of reducing the level of some DDS spurious products.

Many alternative systems have since been offered to reduce spurious products, for example in 1991, Wilson, et al., [42] offered an alternative DDS based synthesiser that employed two DACs at the DDS output suitably configured such that pseudo random noise added to the main DAC is cancelled by the second DAC. This technique helps reduce the level of the DDS spurious products and minimise the rise in the noise floor.

There are essentially three principal bottlenecks that limit the speed of a DDS unit; the digital accumulator, the non-linear phase to amplitude conversion and the maximum DAC operating speed that gives acceptable performance. DDS evolution over the last decade has been limited by the available technology and the methodology used in the design of these three elements, with the slowest element defining the maximum operating speed of the DDS unit. In 1991, Saul [43, 44], is recognised as being responsible for the design of the SP2002 device whose maximum operational speed of 2GHz driving two 8-bit output DACs up to 500MHz, remains an outstanding achievement. The SP2002 is still a viable product available today. Other DDS units, at that time, were limited to speeds of 20MHz.

37

<sup>&</sup>lt;sup>7</sup> Patent time scales require that after 18 months of filing a patent a "Publication" is released irrespective of whether there are any outstanding questions concerning its legal value. Only after Granting the patent is the Prosecution process concluded and the patent becomes valid.

Figure 2.4 Typical complete DDS + DAC architecture [45]

Over the last decade, the maximum operating speed of other commercial DDS units has crept up, with the latest unit, the AD9858, [6], offering 1GHz operation throughout, including an integrated 10-bit output DAC. Aside from these commercial DDS units other technologies such as Indium Phosphate, InP, have been applied using novel accumulator, look up table and DAC architectures, thus allowing the demonstration of DDS units up to a 9·2GHz operating speed, [46], with typically 40dB of SFDR. Clearly the evolution of DDS has accelerated in the last few years and now the phase noise, speed, bandwidth, and hence potential of DDS, make it a dominant factor in system planning.

The omnipresent DDS concept has become the topic of many interesting papers, patents and application notes which illustrate the flexibility and applicability of DDS in such diverse applications as radar, frequency scanning and modern signalling as well as in NCO cores used within mixed signal IC's. However, DDS fundamental limitations of spurious and operational speed have prevented it from replacing analogue frequency synthesisers, nevertheless, the ability of DDS to instantaneously change frequency digitally, with very high levels of precision and excellent noise performance, has ensured its place in synthesiser system planning. Hybrid synthesisers that use DDS are usually designed to exploit this frequency agility and resolution whilst simultaneously using the complete synthesiser architecture to suppress spurious products to a suitable level for the application.

# DEFINING FREQUENCY SYNTHESISERS

#### 3.1 Introduction

3

The purpose of this chapter is to consider different candidate architectures and their building blocks, which can be reconfigured in a variety of combinations to solve the conflicting specification requirements of phase noise, lock time and spurious performance. Each of the building blocks is presented to a sufficient level as a foundation for further development in subsequent chapters. The main reasons why neither fractional-n nor DDS can be used as the simple solution for meeting a low noise, frequency agile local oscillator specification are identified.

During the assessment stages of different synthesisers described in this chapter, the idea for a novel form of DDS synthesiser was proposed leading to a patent application by Nokia.

# 3.2 Overview of Frequency Synthesiser Configurations

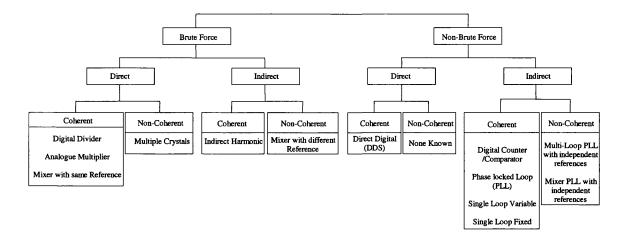

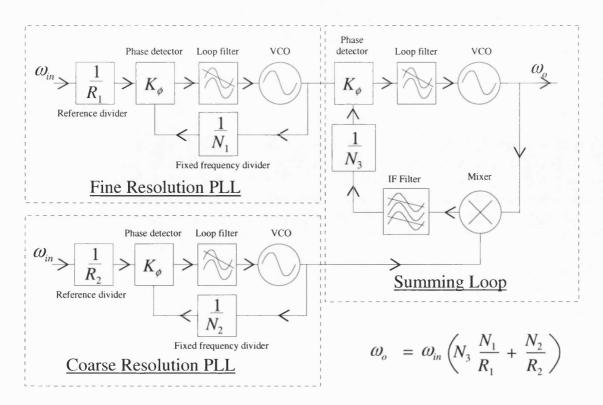

Behind the commonly accepted phase locked loops, exist a whole range of different frequency synthesisers, which can broadly be sub-divided into brute force and non-brute force techniques, [47]. Their difference depends upon the techniques used to synthesise the signal, which range from cumbersome hardware intensive techniques to the very elegant hardware efficient direct form of frequency synthesiser. If greater operational performance is required, a variety of different techniques are often integrated to give a hybrid solution. Figure 3.1 categorises the known techniques for frequency synthesis. In general, most non-demanding synthesisers use only one of the simpler systems listed for reasons of convenience, cost and simplicity, whilst more demanding applications require a combination of techniques, each one designed to exploit a particular feature. The objective of this research work is to understand the performance of some of these

synthesisers and develop a combination of the most promising, to meet the most demanding specifications, without resorting to an unduly complicated synthesiser.

Figure 3.1 Classification of different synthesiser types, [47]

### 3.3 Mixed Signal Frequency Synthesisers

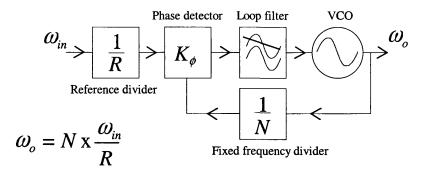

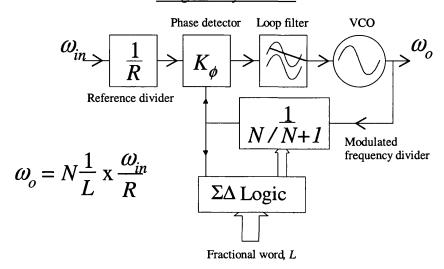

There exist two fundamental categories of single loop synthesiser; that of the integer-n and the fractional-n frequency synthesiser, Figure 3.2. Their respective evolution has been one of continued improvement of each element within the integer-n synthesiser structure, or advances in noise shaping techniques within fractional-n systems.

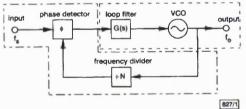

### 3.3.1 Integer-N Single Loop Synthesisers

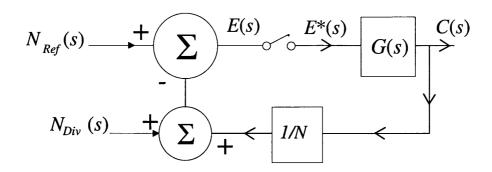

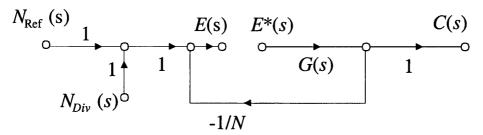

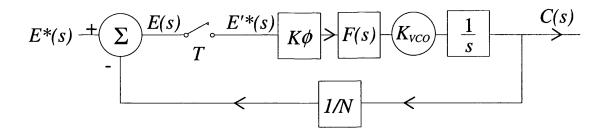

Integer-n synthesisers are single loop synthesisers using a forward path comprised of phase detector followed by the loop filter, which controls the VCO. Phase lock is achieved by the n-divider feedback path that divides the VCO output signal to provide a comparison signal, at the same frequency as the reference signal for phase detection. Fractional-n synthesisers use the same architecture with the subtle difference that the feedback n-dividers are modulated to give a lower mean division value, Figure 3.2

### Integer-N Synthesiser

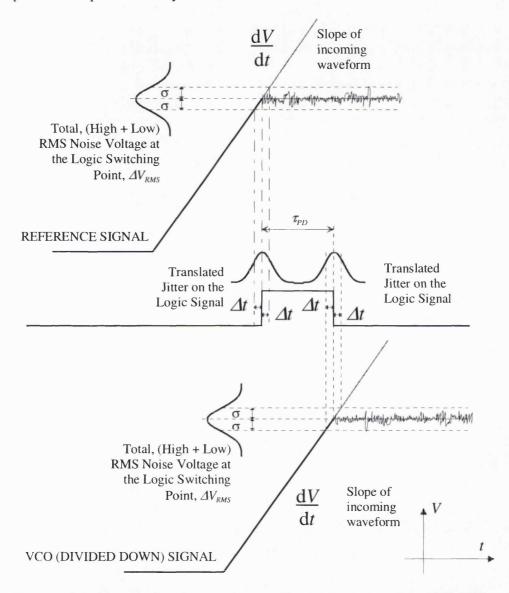

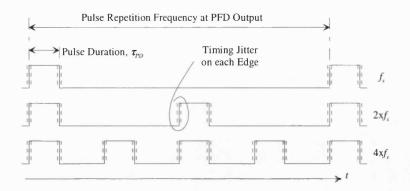

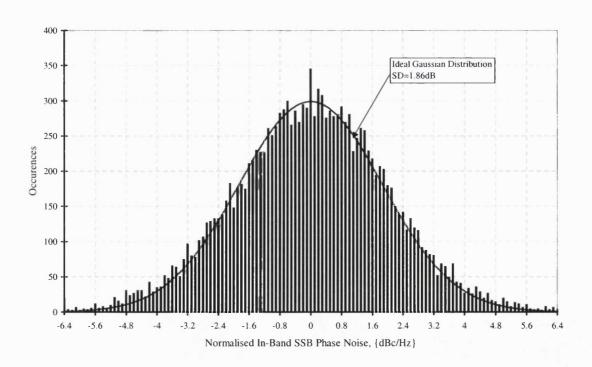

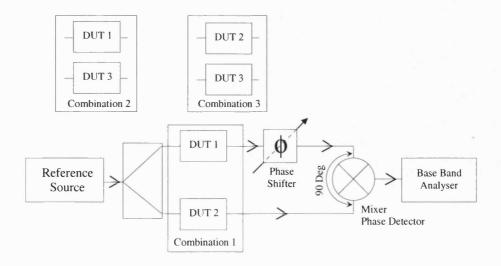

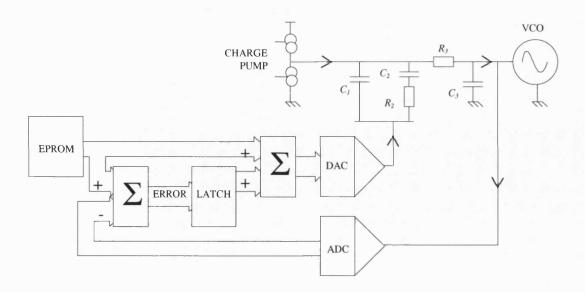

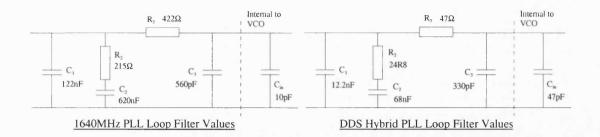

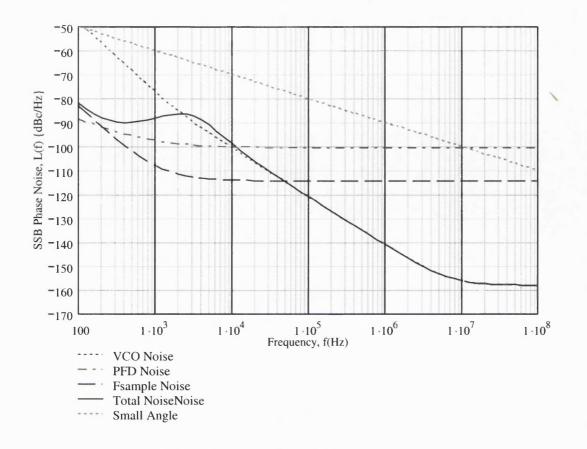

Fractional-N Synthesiser