UNIVERSITY COLLEGE LONDON

*A Practical Hardware Implementation of

Systemic Computation*

by

Christos Sakellariou

A thesis submitted in partial fulfilment for the

degree of Doctor of Engineering

in the

Faculty of Engineering

Department of Computer Science

December 2013

# Declaration of Authorship

I, *Christos Sakellariou*, declare that this thesis *A Practical Hardware Implementation of Systemic Computation* and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at University College London.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at University College London or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

---

Date:

---

# *Abstract*

Faculty of Engineering, Department of Computer Science

UNIVERSITY COLLEGE LONDON

Doctor of Engineering

by Christos Sakellariou

It is widely accepted that natural computation, such as brain computation, is far superior to typical computational approaches addressing tasks such as learning and parallel processing. As conventional silicon-based technologies are about to reach their physical limits, researchers have drawn inspiration from nature to find new computational paradigms. Such a newly-conceived paradigm is Systemic Computation (SC). SC is a bio-inspired model of computation. It incorporates natural characteristics and defines a massively parallel non-von Neumann computer architecture that can model natural systems efficiently.

This thesis investigates the viability and utility of a Systemic Computation hardware implementation, since prior software-based approaches have proved inadequate in terms of performance and flexibility. This is achieved by addressing three main research challenges regarding the level of support for the natural properties of SC, the design of its implied architecture and methods to make the implementation practical and efficient.

Various hardware-based approaches to Natural Computation are reviewed and their compatibility and suitability, with respect to the SC paradigm, is investigated. FPGAs are identified as the most appropriate implementation platform through critical evaluation and the first prototype Hardware Architecture of Systemic computation (HAoS) is presented.

HAoS is a novel custom digital design, which takes advantage of the inbuilt parallelism of an FPGA and the highly efficient matching capability of a Ternary Content Addressable Memory. It provides basic processing capabilities in order to minimize time-demanding data transfers, while the optional use of a CPU provides high-level processing support. It is optimized and extended to a practical hardware platform accompanied by a software framework to provide an efficient SC programming solution. The suggested platform is evaluated using three bio-inspired models and analysis shows that it satisfies the research challenges and provides an effective solution in terms of efficiency versus flexibility trade-off.

## *Acknowledgements*

I sincerely believe I could not have been luckier when I first emailed Peter Bentley about five years ago on the prospect of working under his supervision towards a doctoral degree. I am extremely thankful to him for his tremendous level of support during these five years. I hugely appreciate all his help along this journey and clearly acknowledge that this thesis would not have been possible without his guidance and encouragement. I enjoyed the fact he is a person that I could talk to freely and count on being listened every single time. I am grateful to consider him as a friend from whom I learned a lot.

I also wish to thank the other researchers of my research group. Special thanks go to Erwan Le Martelot for sharing with me early drafts of his thesis when I started my studies. Further thanks go to Hooman Shayani, Arturo Araujo and Marjan Rouhipour for sharing parts of their work on Systemic Computation that greatly helped me move forward. I would also like to thank other colleagues at UCL: my second supervisor Prof. Steve Hailes and Prof. Izzat Darwazeh for their guidance during the reviews of my progress reports. I also would like to express my thanks to my industrial sponsor Toumaz Technology and especially to my industrial supervisor Alison Burdett for her invaluable support on the initial application towards my doctorate degree and the financial support along its duration. I further wish to acknowledge the EPSRC, the EngD VEIV doctoral centre and the department of Computer Science in UCL for their financial support and for hosting me along my studies.

I would like to thank all my friends that supported me during happy and rough times during these last five years (thank you so much guys for endless coffees and nights in and out!!): my good friends from Greece Psilos, Spirakos, Thomas and Giannakis, my good Toumaz friend Andrikos, my Physics friends Thiseas and Thanos, my soton friend Giannis, my UCL friends Melinos, Dimitris, Theo, Tim and Alexis, my weekend ciccilones friends Pippo, Adrian, Vero and Andreea, my Reading friends Stamo and Dia, my neighbours Bogo and Stella, my childhood friends Sakis, Nantia, Zetta, Stelios and Panagiotakis, my Imperial friend Dimos, all my dear cousins and so many more that need to be here and aren't due to my long-lasting sleep deprivation.. :)

Of course I want to thank my family for their continuous support before, along and beyond my studies. Special thanks to my parents, Aspasia and Thomas, and my little sister Kleiw for their unconditional love. Further thanks to all my extended family (grandparents, uncles, aunts and cousins) for helping me become who I am. Last but not least, I'd like to express my gratitude to my loving partner Marilia for always being there for me along these years, following and supporting me on every step of the way.

## Table of Contents

|                                                              |    |

|--------------------------------------------------------------|----|

| Abstract.....                                                | 3  |

| Acknowledgements.....                                        | 4  |

| List of Figures .....                                        | 10 |

| List of Tables .....                                         | 14 |

| List of Listings .....                                       | 16 |

| List of Algorithms .....                                     | 16 |

| Chapter 1     Introduction.....                              | 17 |

| 1.1    Introduction to Natural Computation.....              | 17 |

| 1.2    Introduction to Systemic Computation .....            | 20 |

| 1.3    Systemic Computation in Practice .....                | 21 |

| 1.4    Hypothesis.....                                       | 23 |

| 1.5    Objectives.....                                       | 25 |

| 1.6    Publications .....                                    | 26 |

| 1.7    Thesis Organization .....                             | 27 |

| Chapter 2     Background .....                               | 29 |

| 2.1    Approaches to Natural Computation.....                | 30 |

| 2.1.1    Software Approaches.....                            | 31 |

| 2.1.2    Alternative Paradigms .....                         | 32 |

| 2.2    Hardware-based Approaches to Natural Computation..... | 33 |

| 2.2.1    Conventional Hardware Approaches .....              | 33 |

| 2.2.2    Unconventional Hardware Approaches .....            | 38 |

| 2.2.3    Other silicon-based designs .....                   | 55 |

| 2.2.4    Hardware Approaches Summary.....                    | 62 |

|           |                                                              |    |

|-----------|--------------------------------------------------------------|----|

| 2.3       | Systemic Computation .....                                   | 63 |

| 2.4       | Prior Systemic Computation Implementations .....             | 68 |

| 2.4.1     | Original SC Implementation .....                             | 68 |

| 2.4.2     | High-level SC Implementation.....                            | 70 |

| 2.4.3     | GPU SC Implementation .....                                  | 71 |

| 2.5       | Summary .....                                                | 72 |

| Chapter 3 | Designing a Suitable Hardware Architecture for SC .....      | 77 |

| 3.1       | Potential Architectures.....                                 | 77 |

| 3.1.1     | Virtual SC .....                                             | 78 |

| 3.1.2     | Fundamental Processing Element.....                          | 79 |

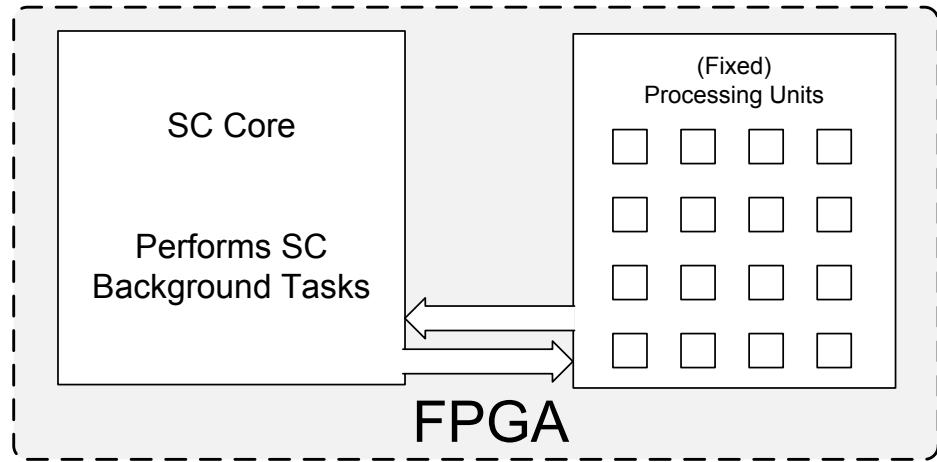

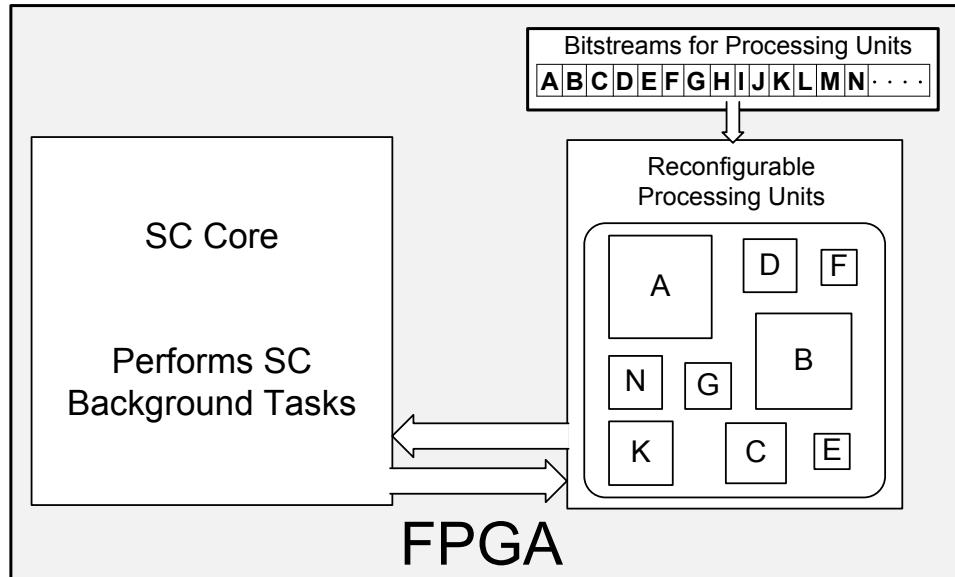

| 3.1.3     | Reconfigurable Predetermined Processing Elements Array ..... | 80 |

| 3.1.4     | SC2HDL .....                                                 | 82 |

| 3.1.5     | GPUplusFPGA .....                                            | 83 |

| 3.1.6     | Summary .....                                                | 84 |

| 3.2       | Design Analysis of the SC Architecture .....                 | 85 |

| 3.2.1     | Local Knowledge & Scope Definition Method .....              | 86 |

| 3.2.2     | Scopes Support.....                                          | 86 |

| 3.2.3     | Valid Triplet Generation & Schemata Matching.....            | 87 |

| 3.2.4     | Threshold Matching.....                                      | 89 |

| 3.2.5     | Systems Representation & Coding Method .....                 | 89 |

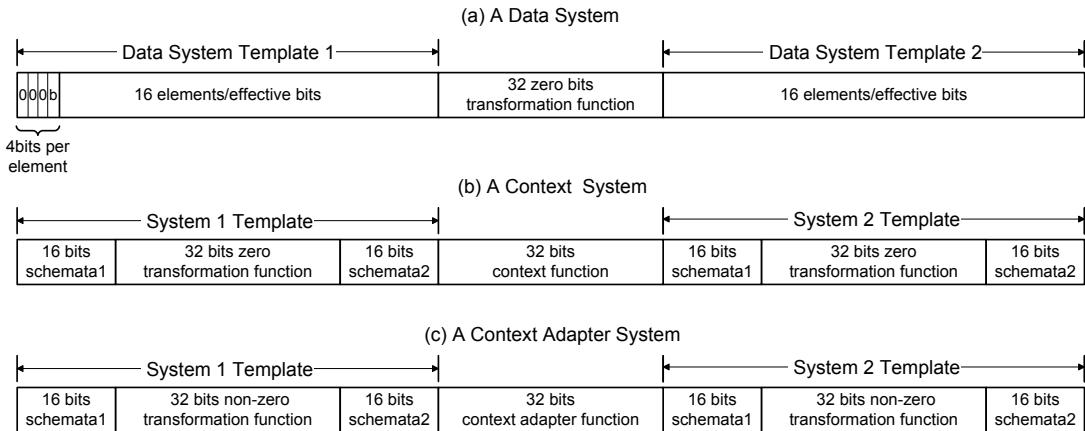

| 3.2.6     | The Compiler .....                                           | 91 |

| 3.2.7     | Interactions Order.....                                      | 91 |

| 3.2.8     | SC Architectural Features Summary .....                      | 93 |

| 3.3       | HAoS Instruction Set .....                                   | 94 |

|           |                                                                    |     |

|-----------|--------------------------------------------------------------------|-----|

| 3.4       | HAoS Architecture .....                                            | 98  |

| 3.5       | The Control Unit.....                                              | 99  |

| 3.6       | The SC Core .....                                                  | 100 |

| 3.6.1     | The Core Memory Elements .....                                     | 101 |

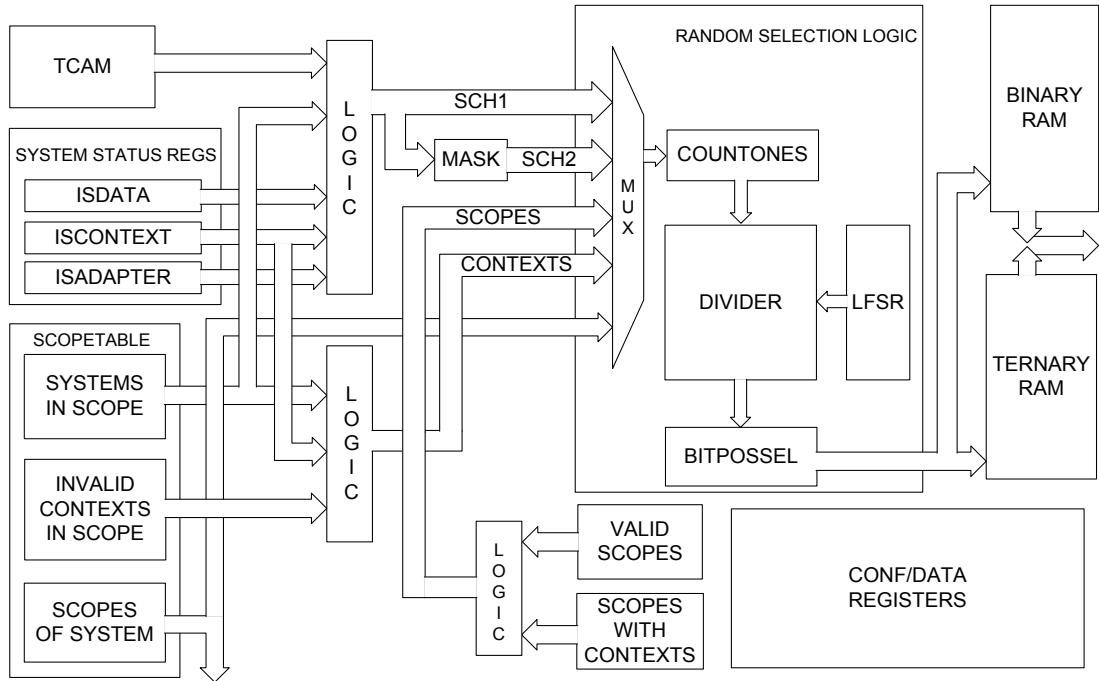

| 3.6.2     | The Random Selection Logic.....                                    | 102 |

| 3.7       | Programming HAoS.....                                              | 108 |

| 3.8       | Initial Testing .....                                              | 113 |

| 3.8.1     | Functional Verification.....                                       | 113 |

| 3.8.2     | Implementation Statistics.....                                     | 117 |

| 3.9       | Summary .....                                                      | 117 |

| Chapter 4 | The HAoS Programming Platform .....                                | 119 |

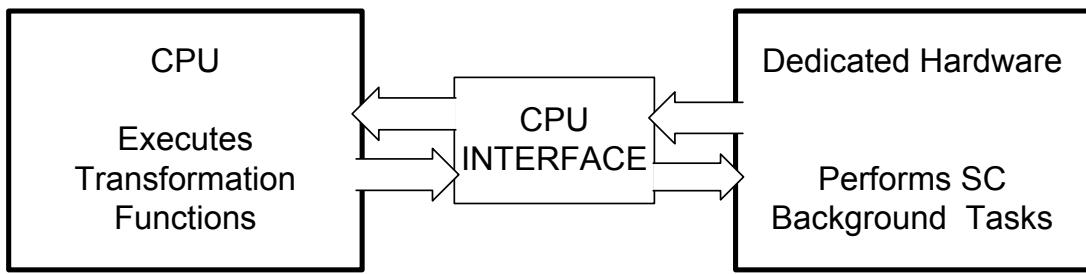

| 4.1       | HAoS-CPU Communication Interface Investigation .....               | 119 |

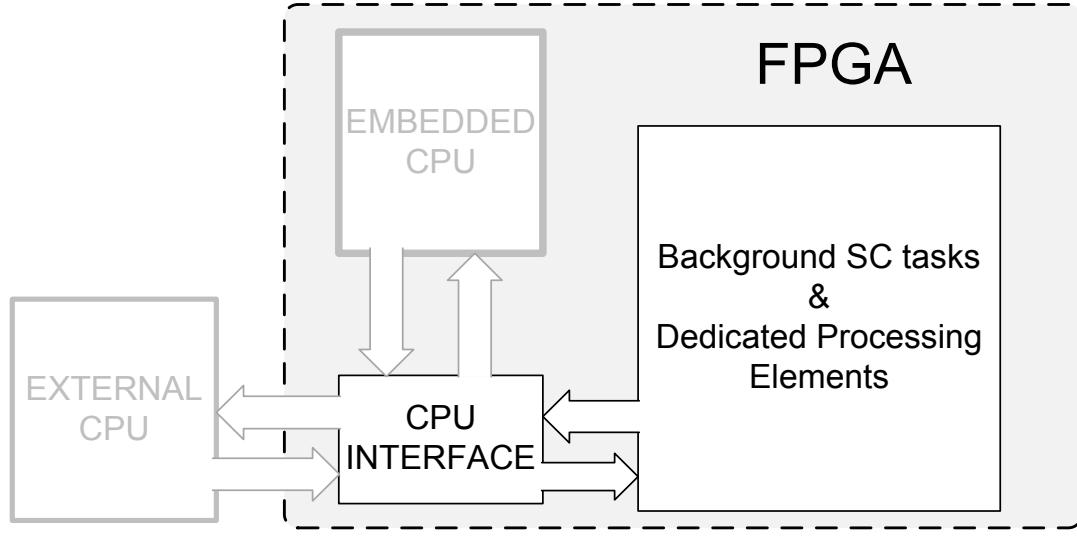

| 4.2       | CPU Subsystem Integration .....                                    | 127 |

| 4.3       | Optimizations and Enhancements.....                                | 128 |

| 4.3.1     | Refining the Random Selection Logic .....                          | 128 |

| 4.3.2     | Minimizing the Schemata-Matching Overhead.....                     | 129 |

| 4.3.3     | Further Addressing I/O Efficiency .....                            | 130 |

| 4.3.4     | Further Addressing User-Friendliness with a Functional Model ..... | 132 |

| 4.3.5     | Further Addressing Programmability .....                           | 133 |

| 4.3.6     | Refinements Results .....                                          | 137 |

| 4.4       | Addressing Scalability for Single-Chip Implementations.....        | 138 |

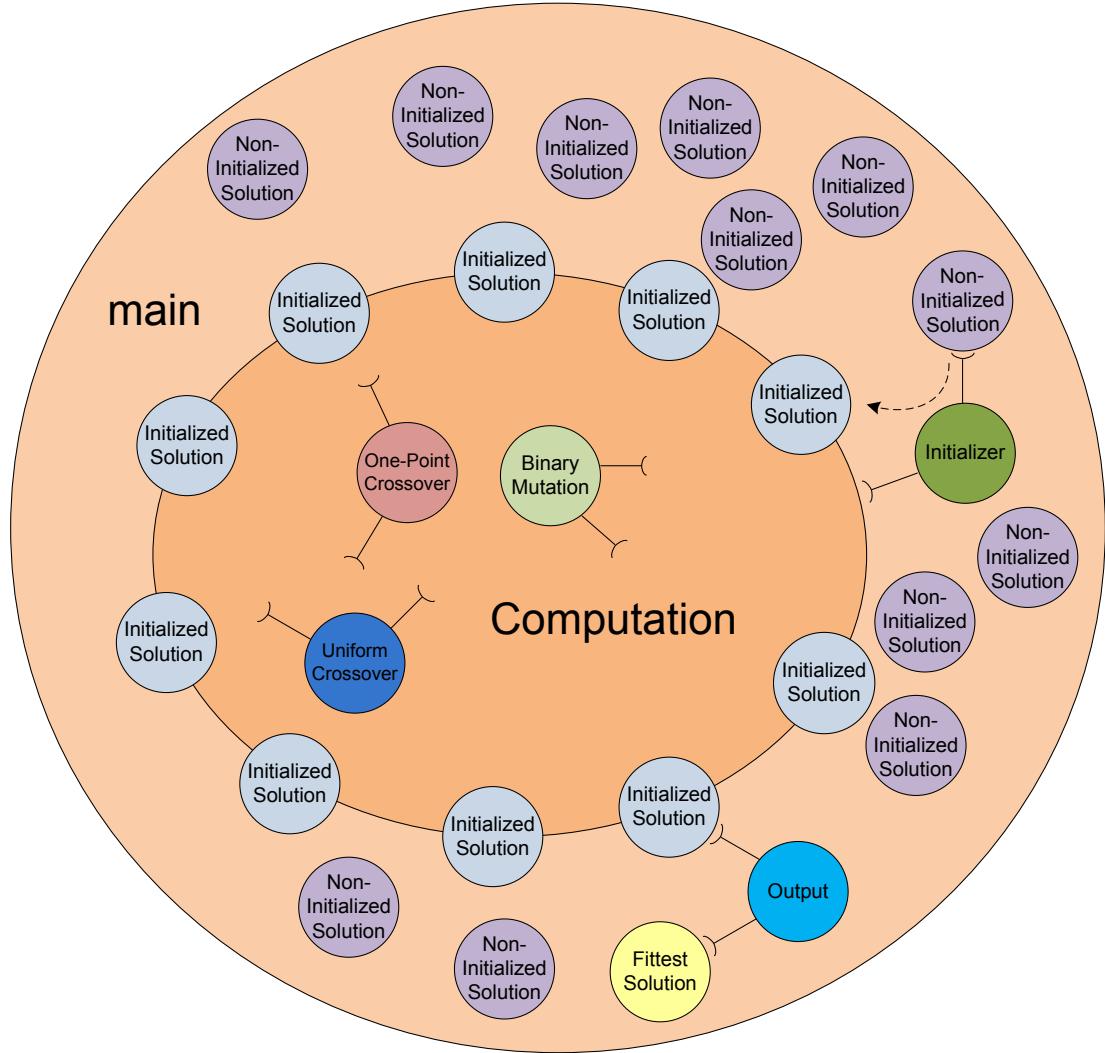

| 4.5       | HAoS Model Development Methodology.....                            | 140 |

| 4.6       | Summary .....                                                      | 143 |

| Chapter 5 | Verification and Evaluation .....                                  | 144 |

|           |                                                                                                                              |     |

|-----------|------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1       | A Genetic Algorithm Optimization of the Binary Knapsack Problem .....                                                        | 145 |

| 5.1.1     | The Binary Knapsack Problem.....                                                                                             | 145 |

| 5.1.2     | Applying a Genetic Algorithm to the Binary Knapsack Problem .....                                                            | 146 |

| 5.1.3     | Systemic Analysis .....                                                                                                      | 148 |

| 5.1.4     | SC Binary Knapsack Model Implementation.....                                                                                 | 150 |

| 5.1.5     | Results .....                                                                                                                | 153 |

| 5.1.6     | Analysis .....                                                                                                               | 154 |

| 5.2       | Simulation of a Biochemical Process with HAoS: the MAPK Signalling Cascade .....                                             | 157 |

| 5.2.1     | The MAPK Signalling Cascade.....                                                                                             | 157 |

| 5.2.2     | Systemic Analysis .....                                                                                                      | 158 |

| 5.2.3     | SC MAPK Signalling Cascade Model Implementation .....                                                                        | 162 |

| 5.2.4     | Results .....                                                                                                                | 165 |

| 5.2.5     | Analysis .....                                                                                                               | 167 |

| 5.3       | Modelling the Effect of Chromosome Misseggregation and Typical Cancer Therapy Approaches in Tumour Evolution with HAoS ..... | 168 |

| 5.3.1     | The Cancer Model .....                                                                                                       | 170 |

| 5.3.2     | Systemic Analysis .....                                                                                                      | 174 |

| 5.3.3     | SC Cancer Model Implementation .....                                                                                         | 187 |

| 5.3.4     | Results .....                                                                                                                | 193 |

| 5.3.5     | Analysis .....                                                                                                               | 201 |

| 5.4       | Summary .....                                                                                                                | 210 |

| Chapter 6 | Conclusion .....                                                                                                             | 212 |

| 6.1       | Summary of Work Revisiting the Objectives .....                                                                              | 212 |

| 6.2       | Contributions .....                                                                                                          | 216 |

|     |                                                                              |     |

|-----|------------------------------------------------------------------------------|-----|

| 6.3 | Critical Evaluation .....                                                    | 217 |

| 6.4 | Future Work .....                                                            | 220 |

| 6.5 | Closing Words .....                                                          | 223 |

|     | References .....                                                             | 226 |

|     | Appendix A. SC Example Test Programs Source Code .....                       | 245 |

|     | Appendix B. CPU Subsystem Integration Details .....                          | 248 |

|     | Appendix C. RSL Optimisations Details .....                                  | 250 |

|     | Appendix D. Revising the TCAM Design .....                                   | 253 |

|     | Appendix E. Provided HAoS API .....                                          | 255 |

|     | Appendix F. File Types used along HAoS Model Development .....               | 256 |

|     | Appendix G. Cancer Models SC Source Code .....                               | 257 |

|     | Appendix H. HAoS Binary-To-ASCII Conversion Resulting Text File Format ..... | 262 |

## List of Figures

|                                                                                                                   |    |

|-------------------------------------------------------------------------------------------------------------------|----|

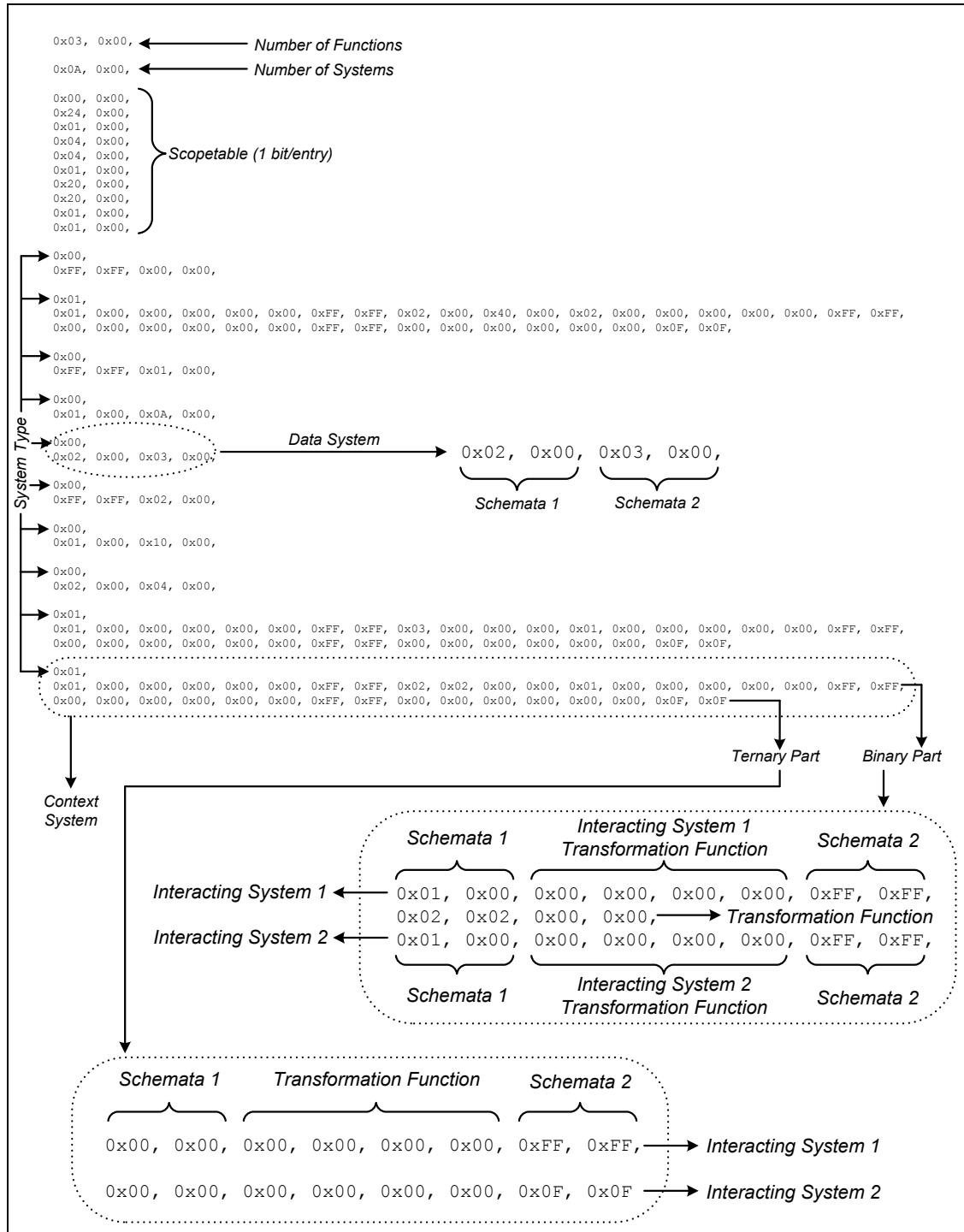

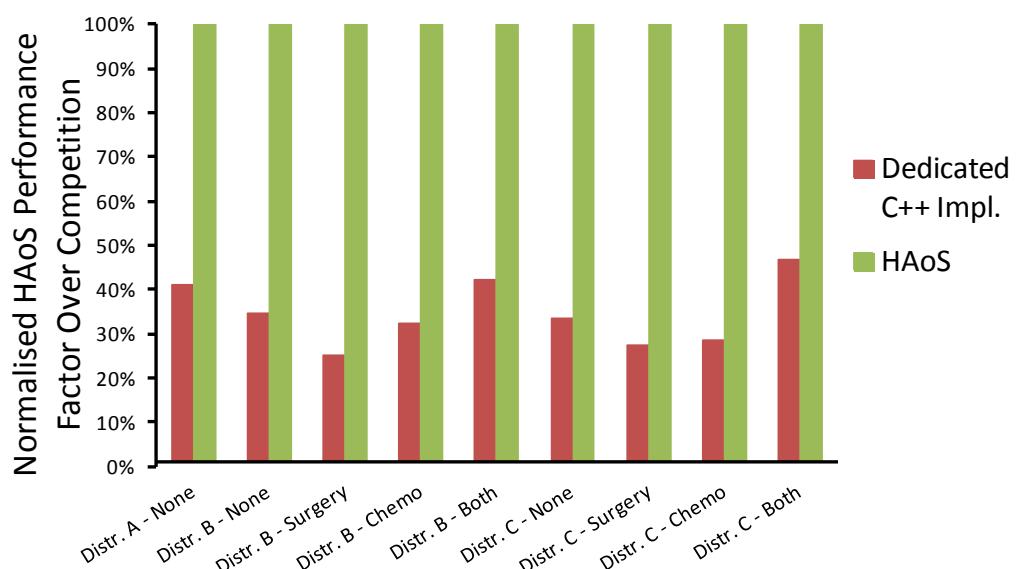

| Figure 1.1. Comparison in flexibility and efficiency of prior software SC implementations .....                   | 22 |

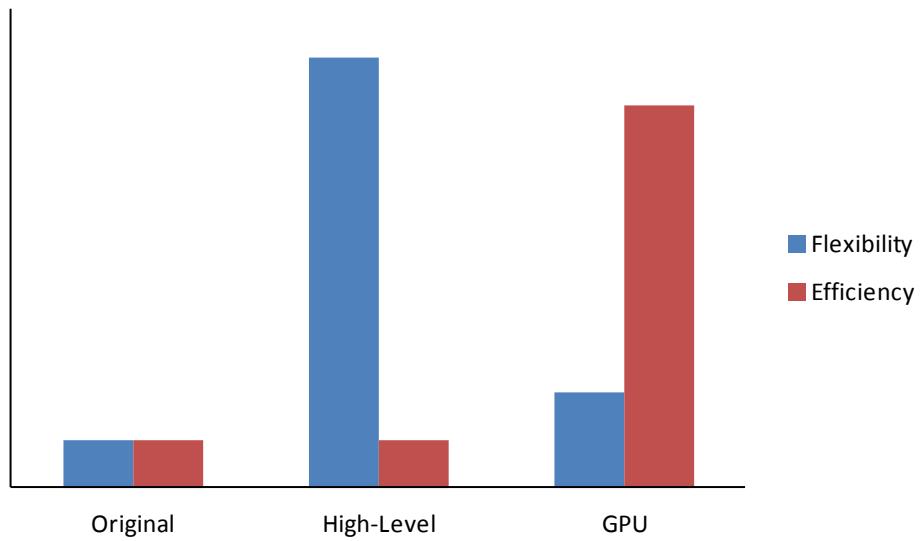

| Figure 1.2. Breakdown and organisation of thesis investigation .....                                              | 25 |

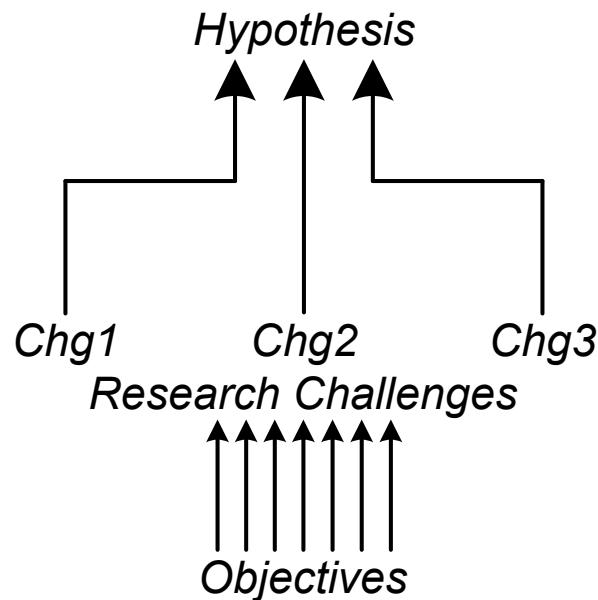

| Figure 2.1. Example organisation of a computer cluster .....                                                      | 36 |

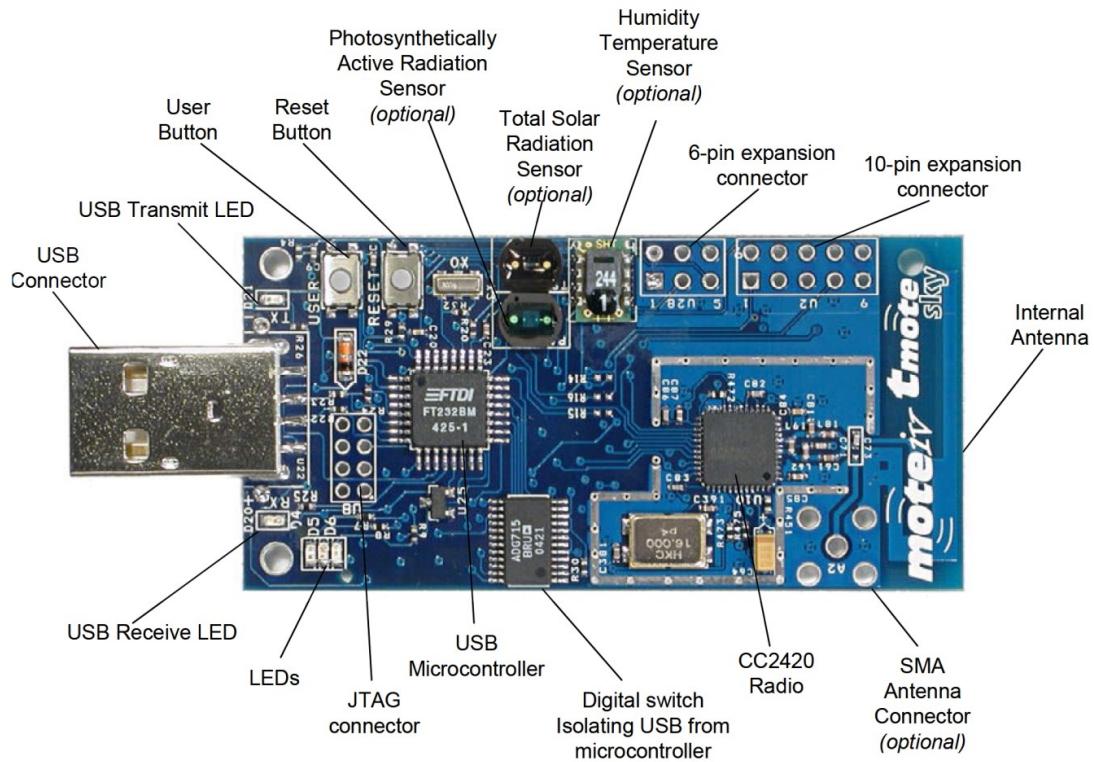

| Figure 2.2. Anatomy of a WSN node. ....                                                                           | 40 |

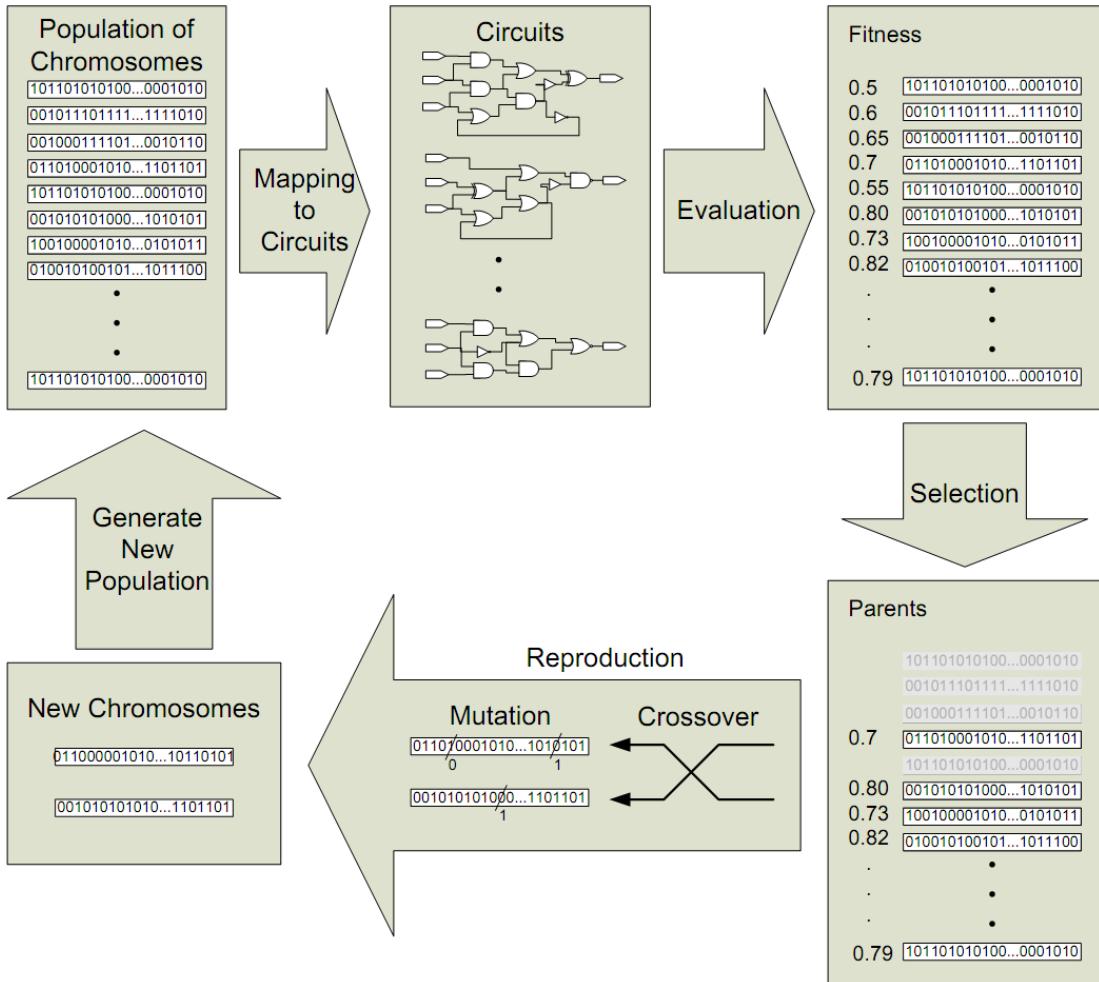

| Figure 2.3. Hardware Evolution using a Genetic Algorithm. ....                                                    | 45 |

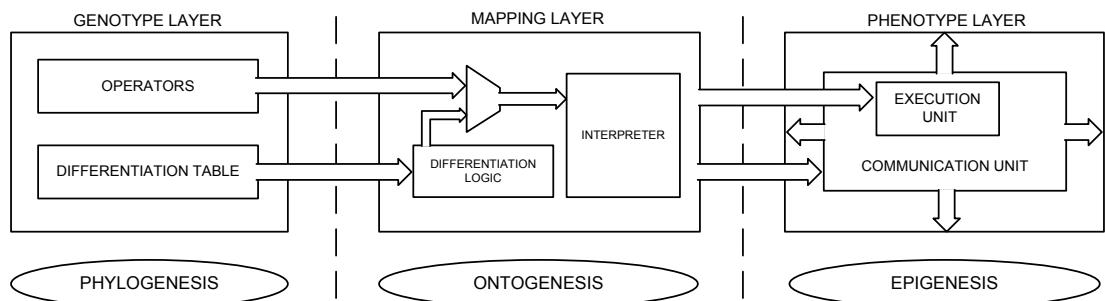

| Figure 2.4. The three organizational layers of the POEtic tissue. ....                                            | 47 |

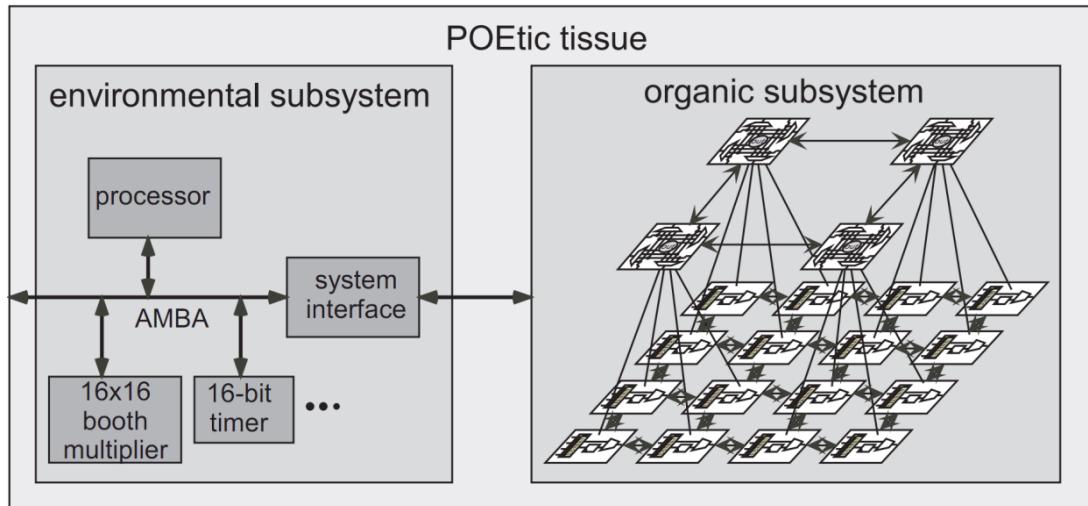

| Figure 2.5. Overview of the POEtic tissue architecture. ....                                                      | 48 |

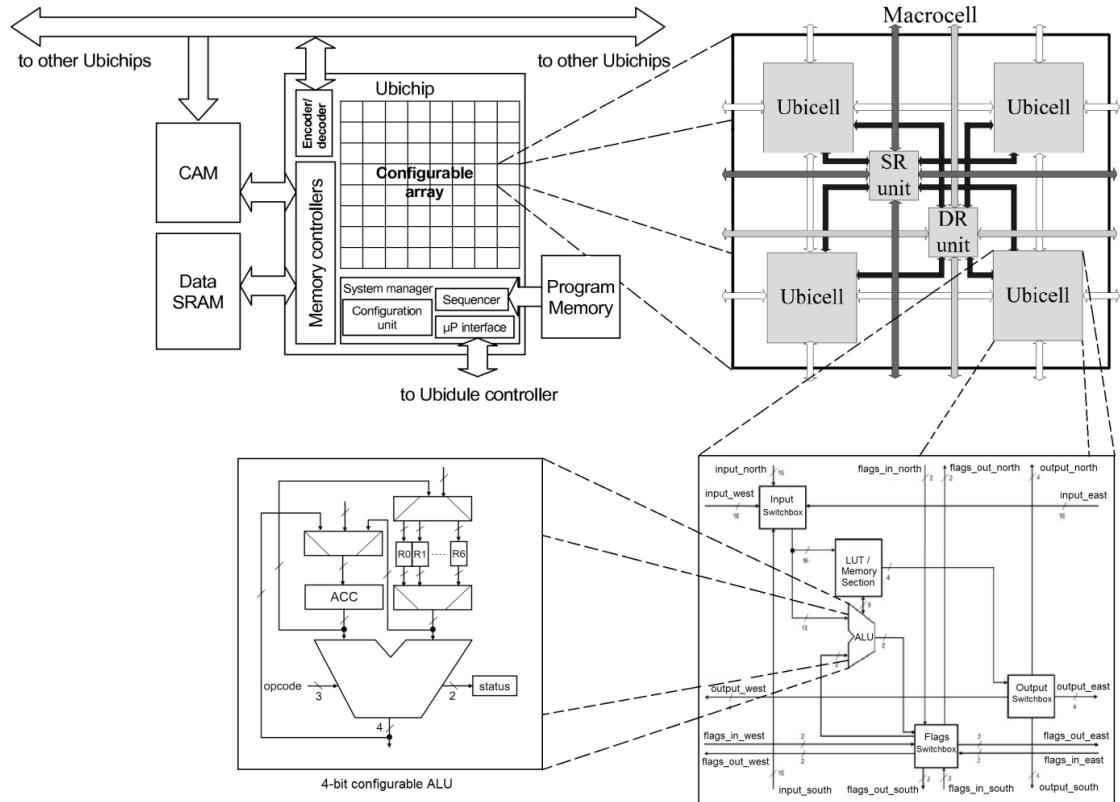

| Figure 2.6. Organisation of the Ubichip architecture. ....                                                        | 50 |

| Figure 2.7. SpiNNaker CMP chip organisation.....                                                                  | 56 |

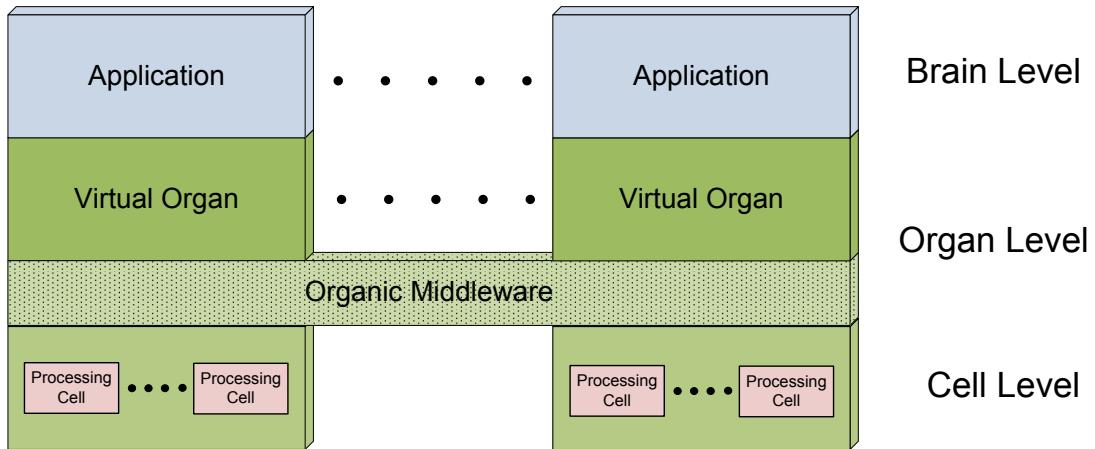

| Figure 2.8. Organic System Architecture. ....                                                                     | 59 |

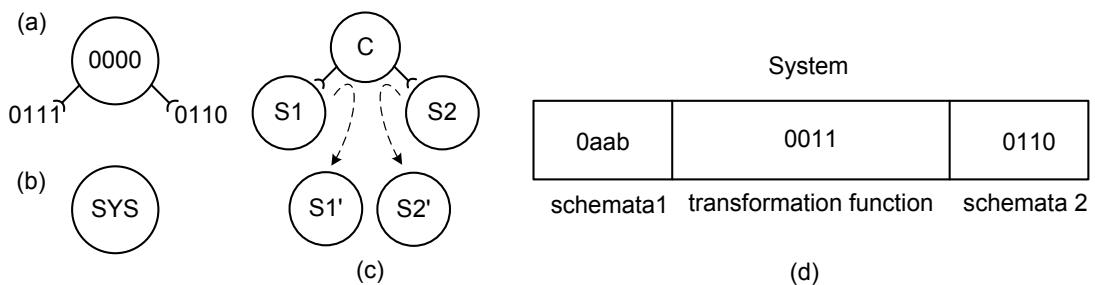

| Figure 2.9. SC notation and systems representation.....                                                           | 64 |

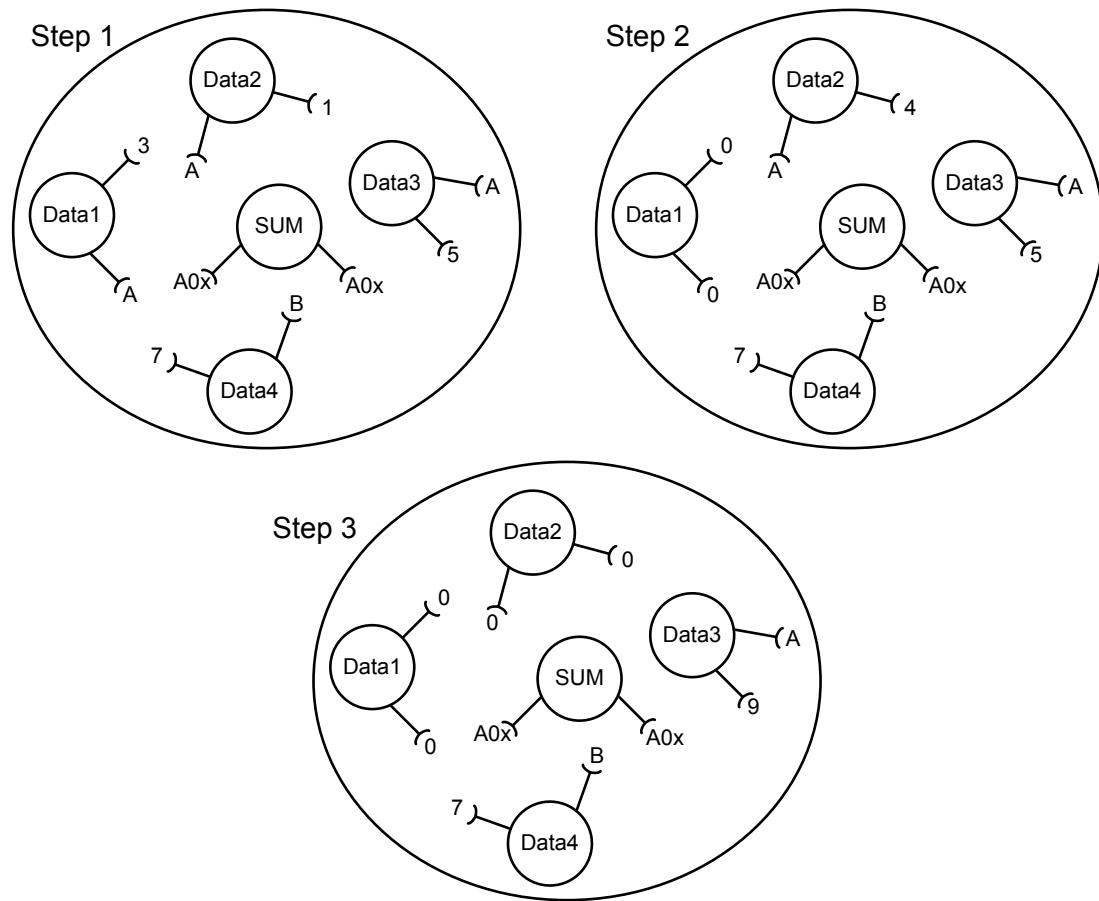

| Figure 2.10. Illustration of a sum operation on a pool of data systems using SC notations. ....                   | 65 |

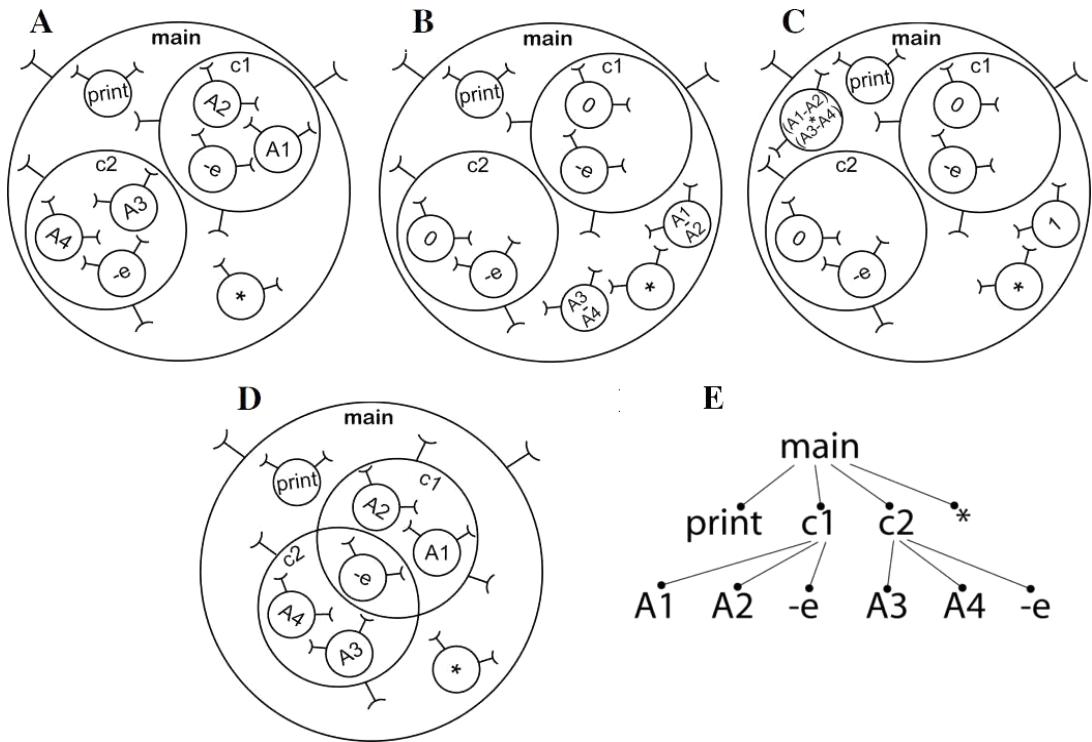

| Figure 2.11. SC calculation of PRINT((A1-A2)*(A3-A4)).....                                                        | 67 |

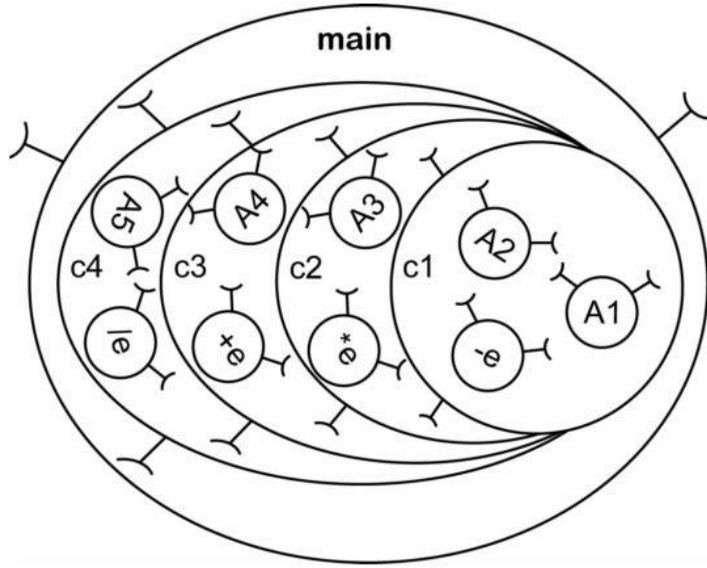

| Figure 2.12. SC calculation of the linear expression (((A1-A2)*A3)+A4)/A5). ....                                  | 68 |

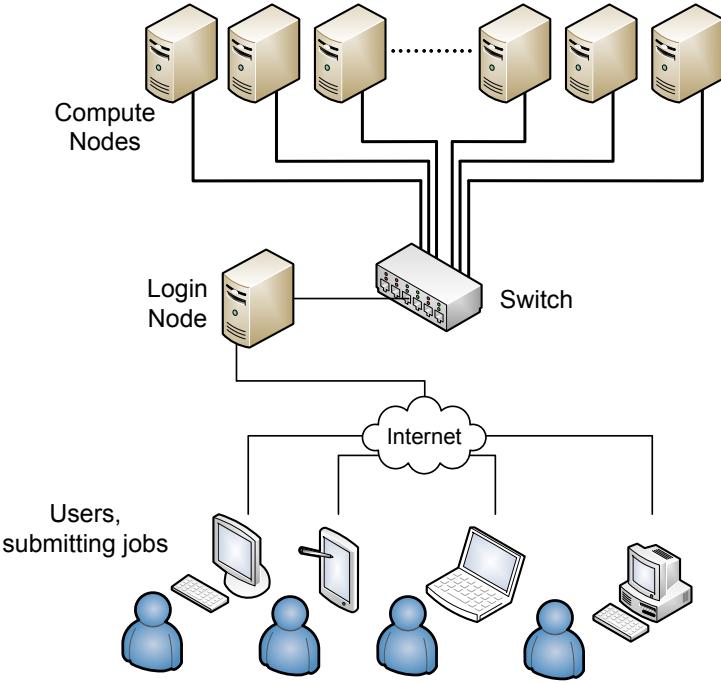

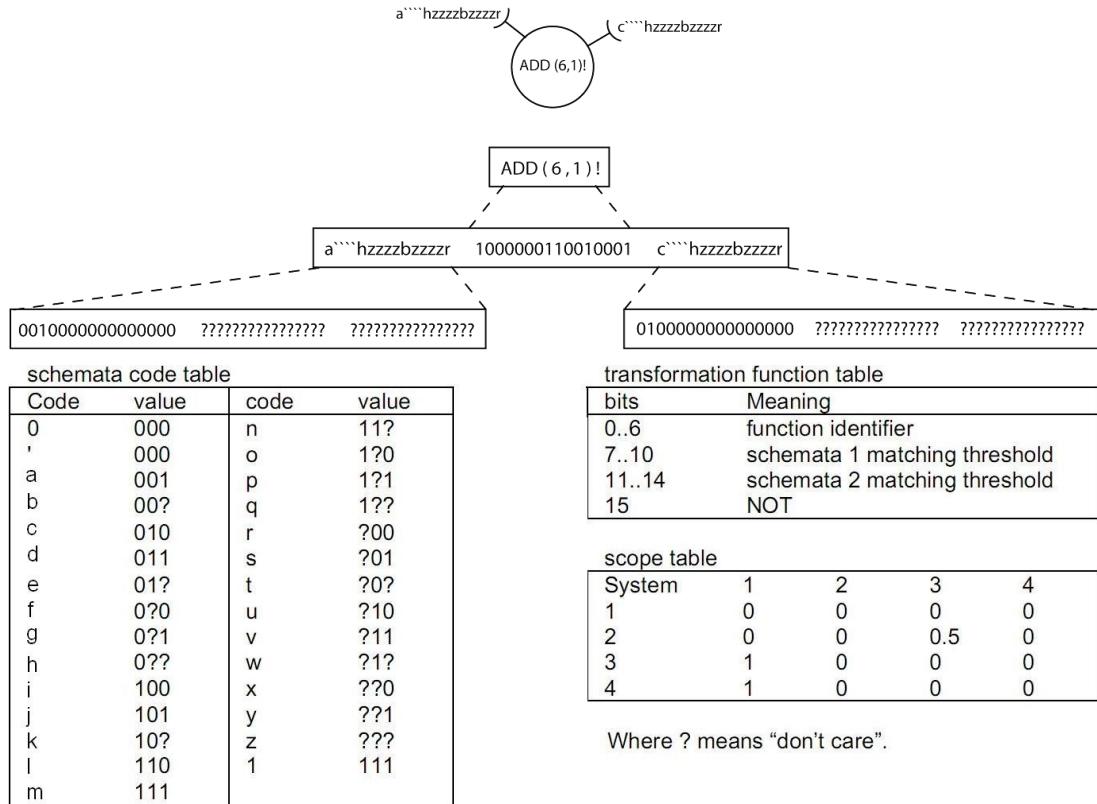

| Figure 2.13. System representation, schemata decoding scheme and scope table of the original SC version. ....     | 69 |

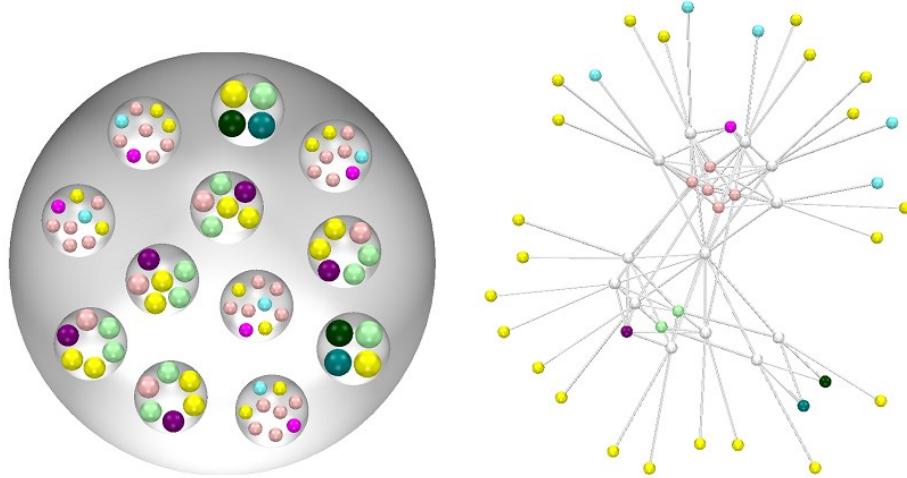

| Figure 2.14. Visualisation of a SC model using SCoPE .....                                                        | 70 |

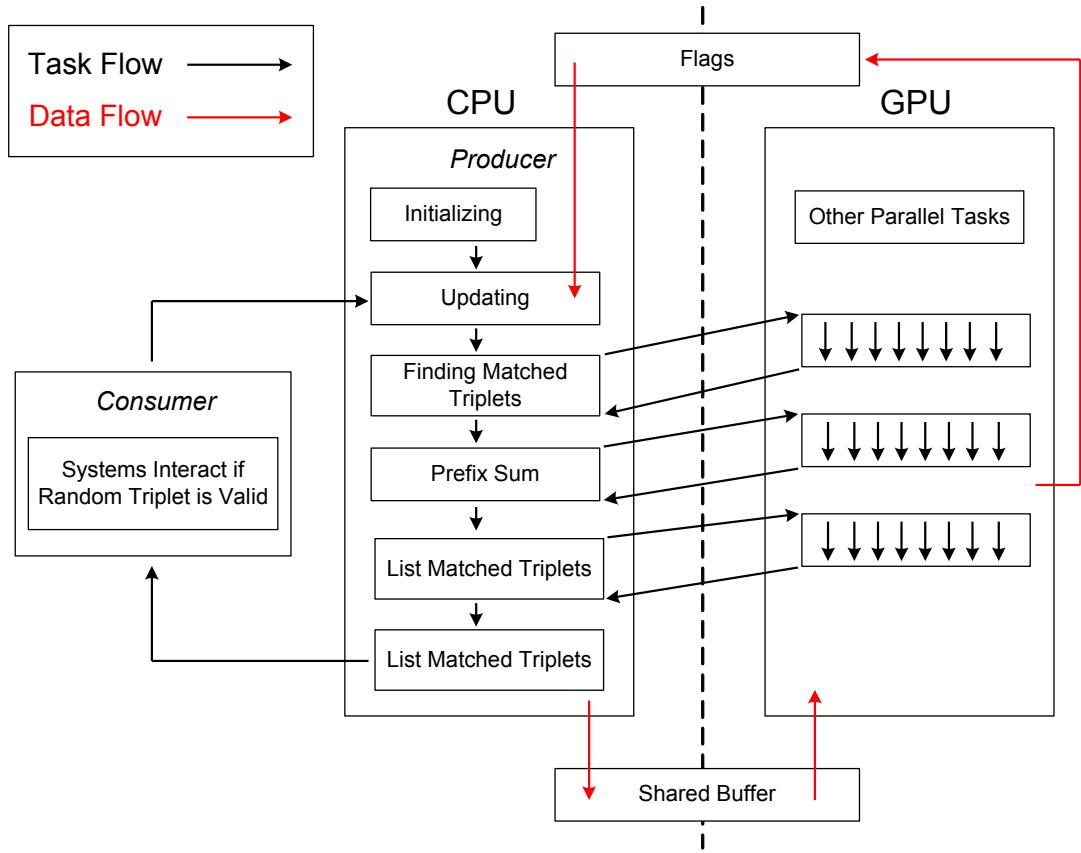

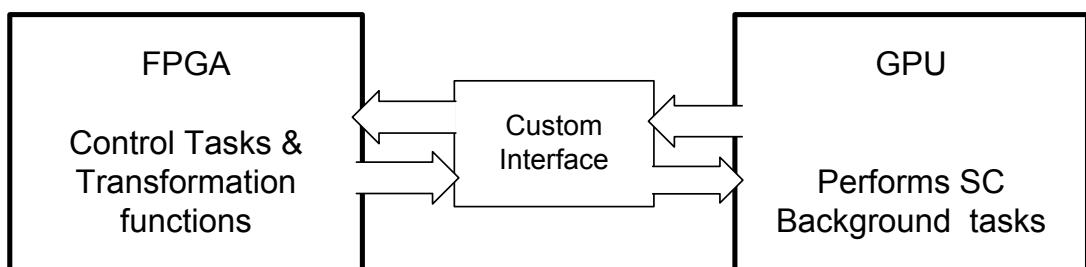

| Figure 2.15. Overview of the task and data flows in GPU SC.....                                                   | 72 |

| Figure 3.1. Virtual SC architecture simplified block diagram .....                                                | 79 |

| Figure 3.2. SC Fundamental Processing Element architecture simplified block diagram                               | 80 |

| Figure 3.3. SC Reconfigurable Predetermined Processing Elements Array architecture simplified block diagram ..... | 81 |

|                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------|-----|

| Figure 3.4. GPUplusFPGA architecture simplified block diagram .....                                     | 83  |

| Figure 3.5. The suggested hybrid design .....                                                           | 85  |

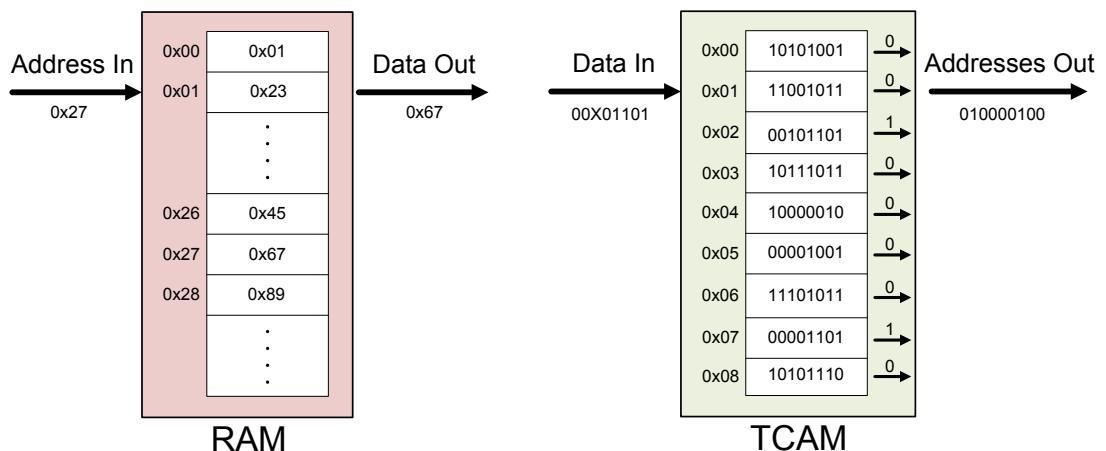

| Figure 3.6. Typical RAM and TCAM usage .....                                                            | 88  |

| Figure 3.7. HAoS TCAM usage .....                                                                       | 89  |

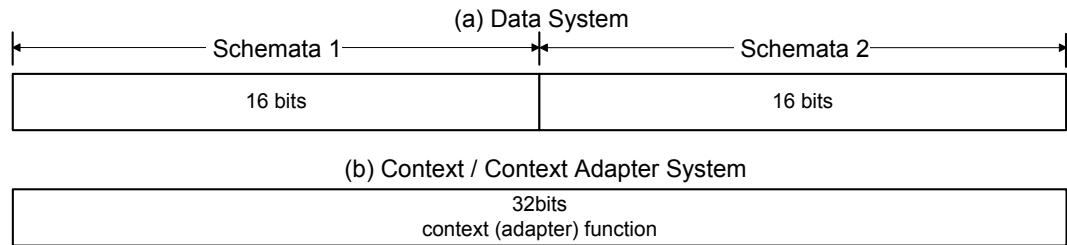

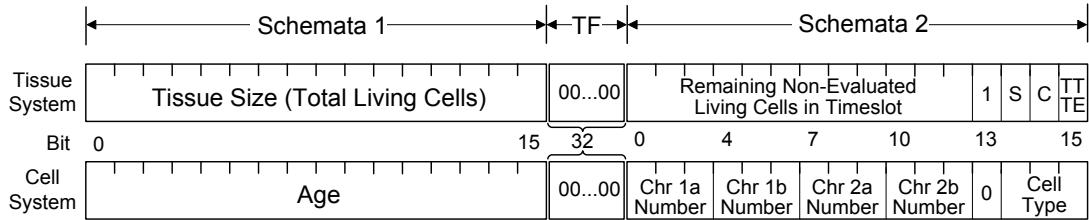

| Figure 3.8. HAoS Systems Representation .....                                                           | 90  |

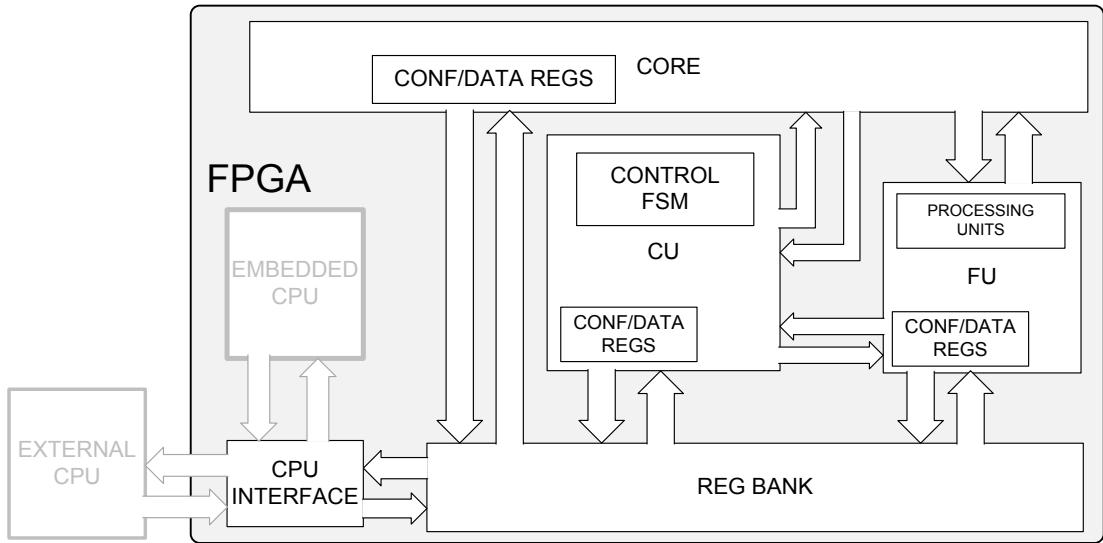

| Figure 3.9. HAoS Top-Level Architecture .....                                                           | 98  |

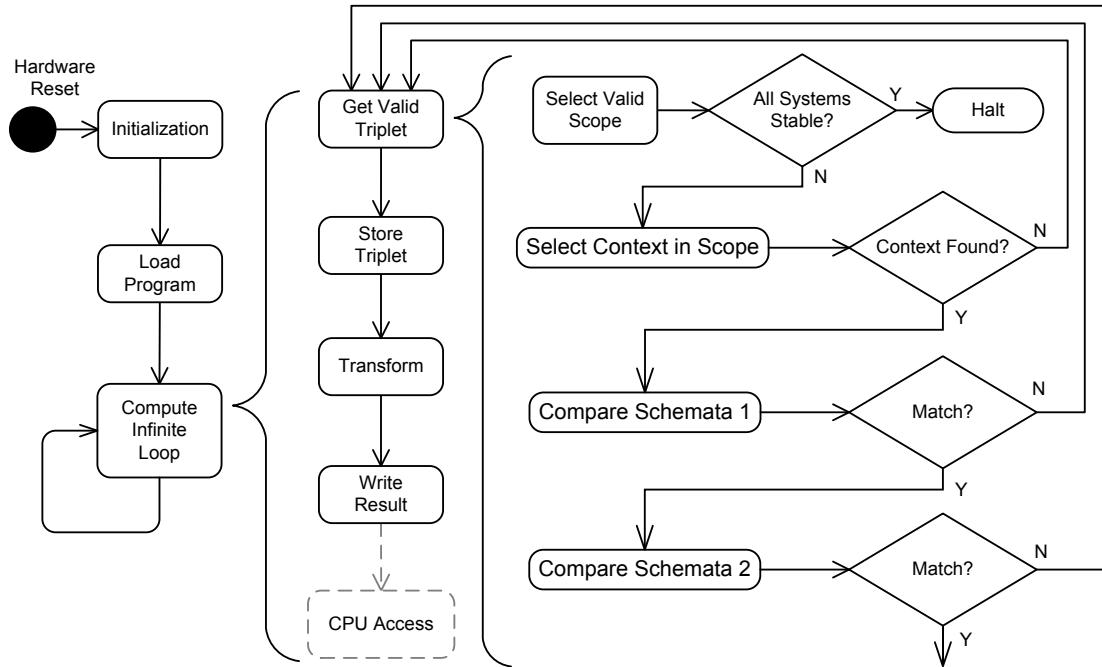

| Figure 3.10. HAoS Program Control Flow .....                                                            | 100 |

| Figure 3.11. HAoS Core basic building blocks .....                                                      | 101 |

| Figure 3.12. The TCAM contents .....                                                                    | 102 |

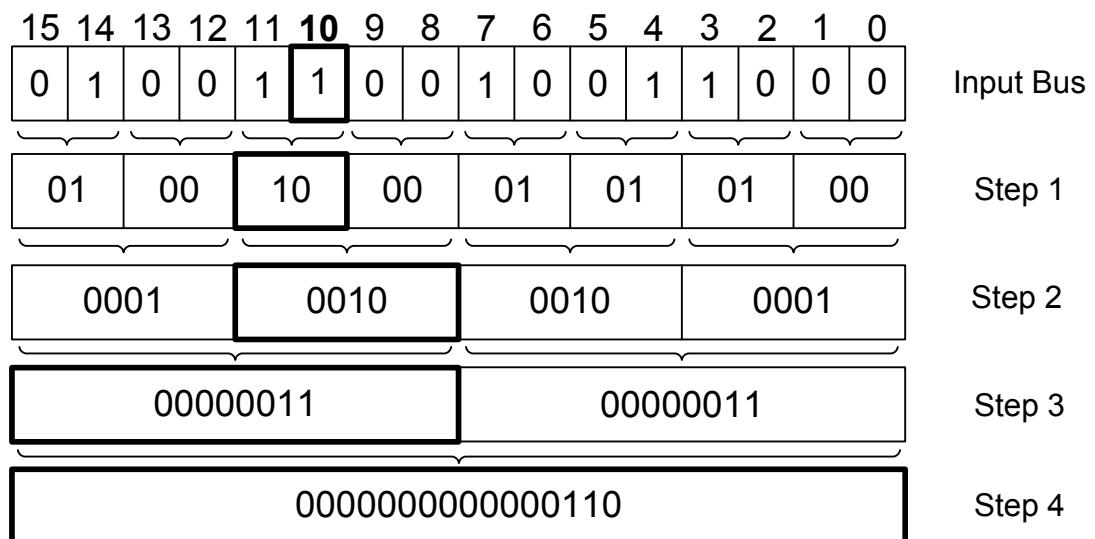

| Figure 3.13. Parallel Bit Count Example .....                                                           | 103 |

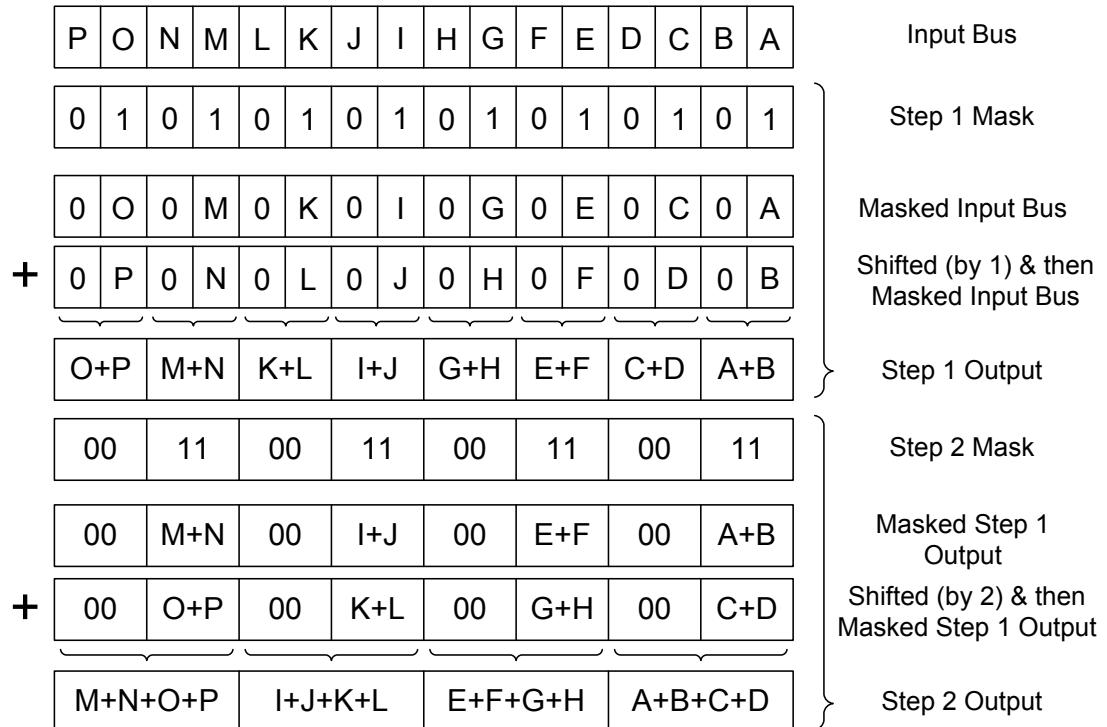

| Figure 3.14. Shift-and-Add implementation of the parallel bit-count mechanism .....                     | 104 |

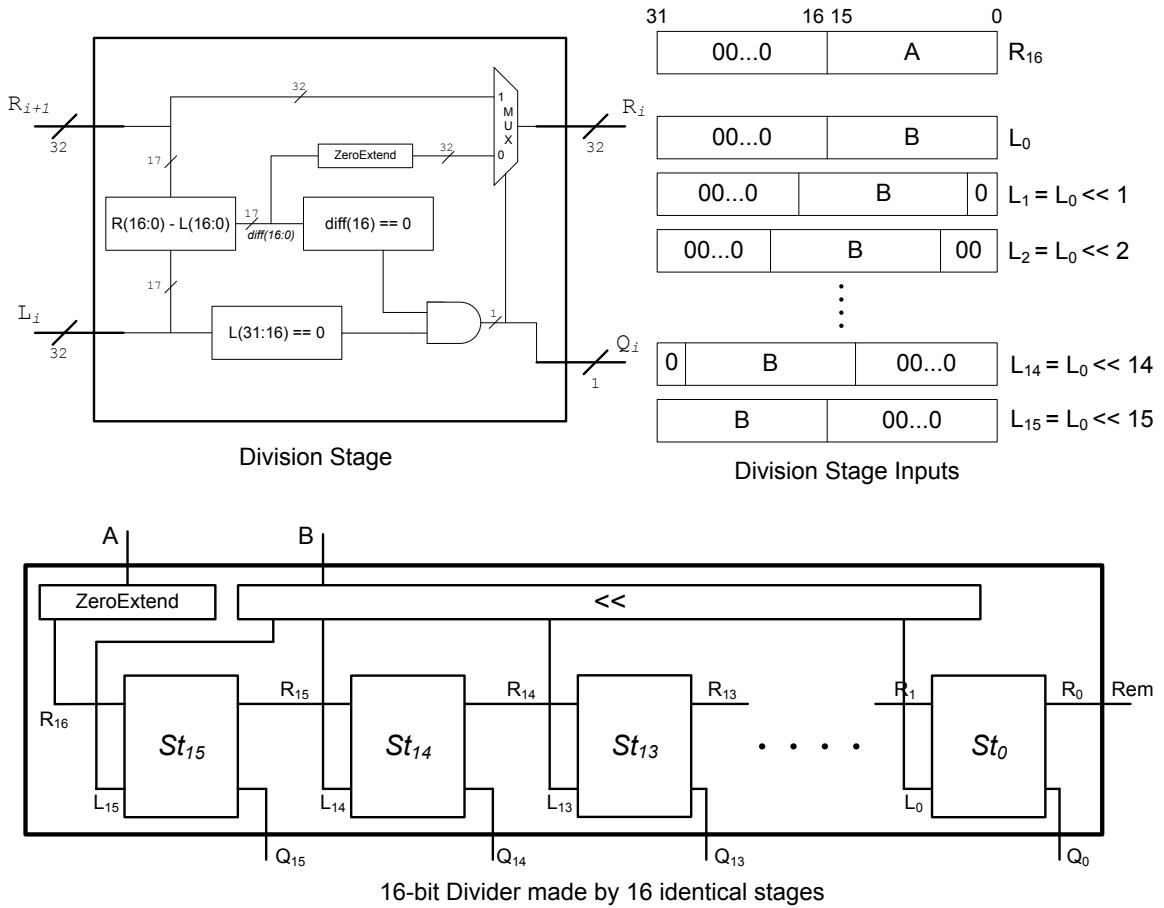

| Figure 3.15. HAoS Divider based on a modular approach .....                                             | 105 |

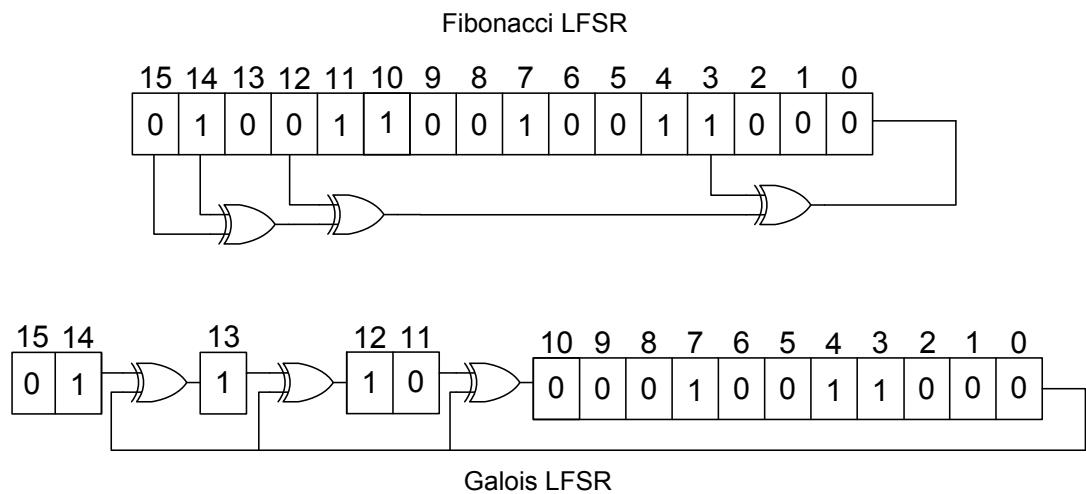

| Figure 3.16. 16-bit Fibonacci and Galois type LFSRs .....                                               | 106 |

| Figure 3.17. Human-readable HAoS Assembly Code .....                                                    | 110 |

| Figure 3.18. HAoS Sample Output .....                                                                   | 111 |

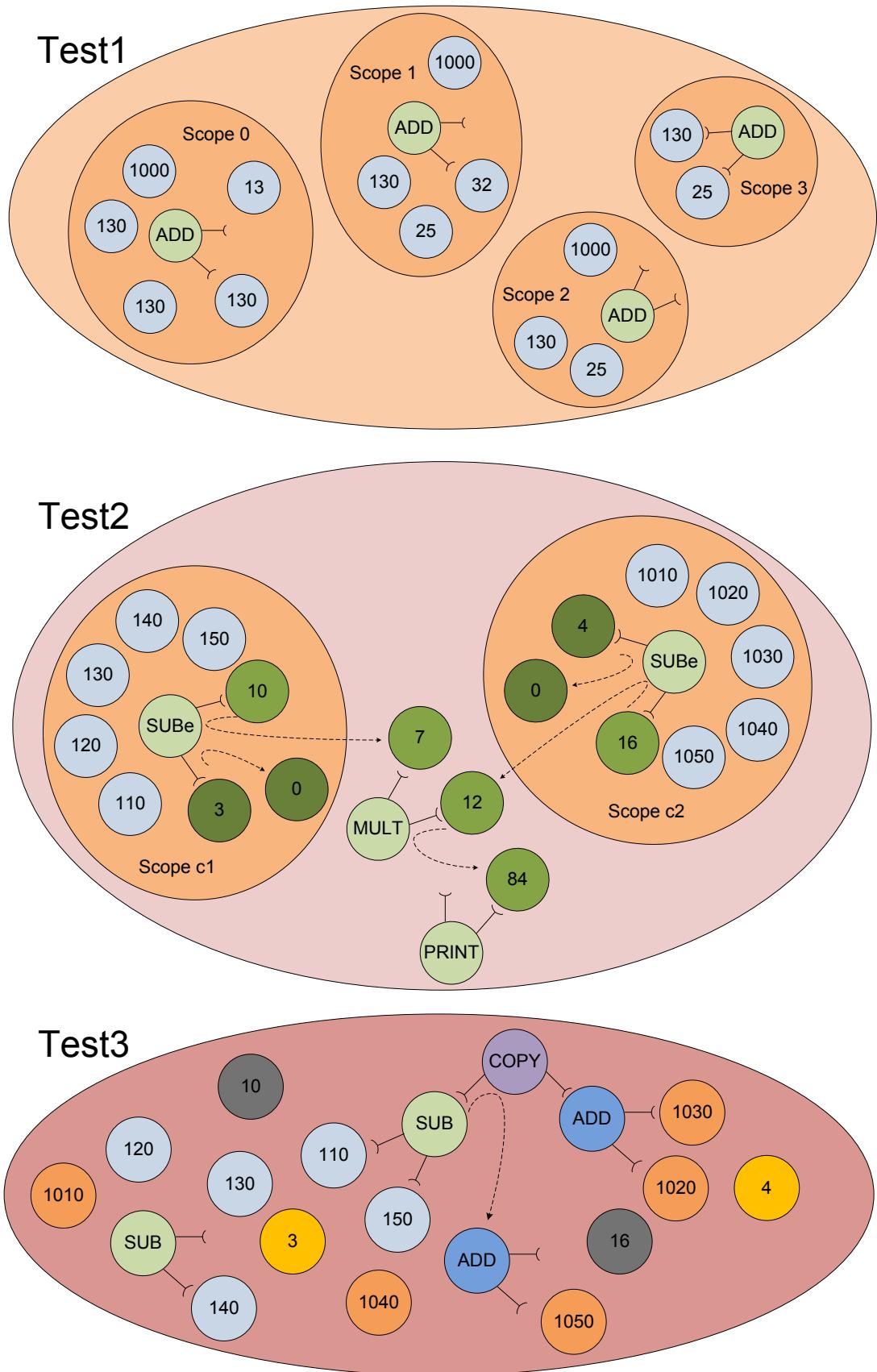

| Figure 3.19. The three verification example SC programs .....                                           | 116 |

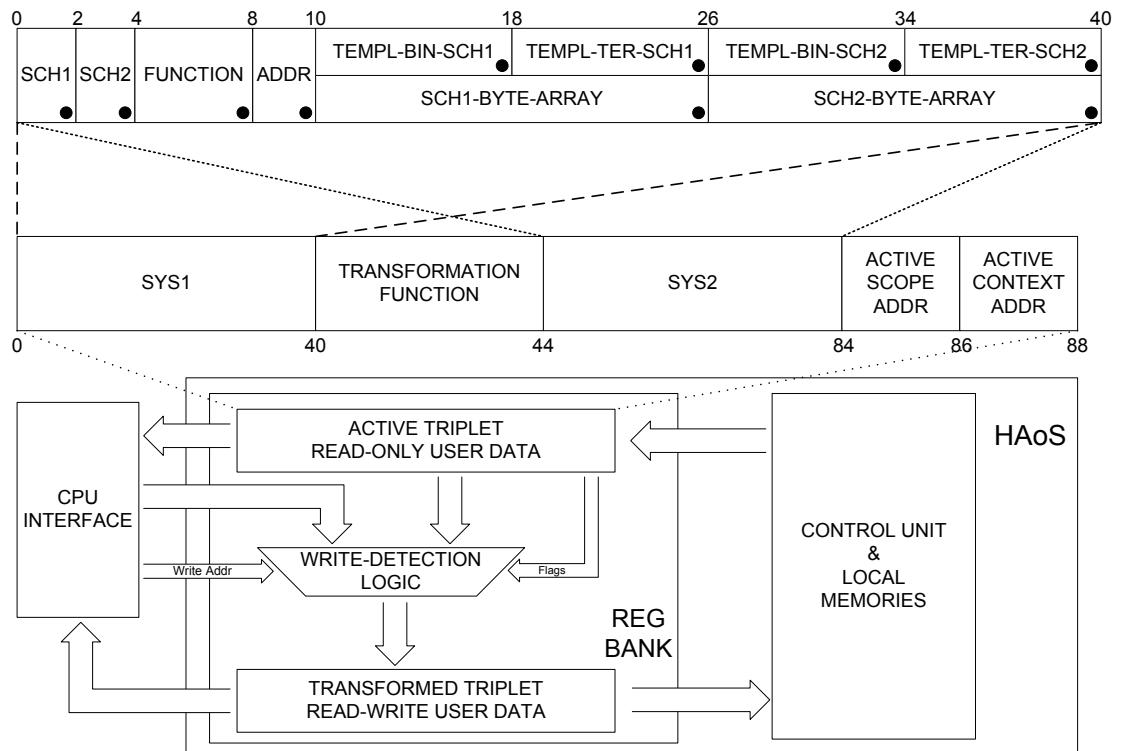

| Figure 4.1. Revised Triplet Memory Map and Write-Detection Mechanism .....                              | 131 |

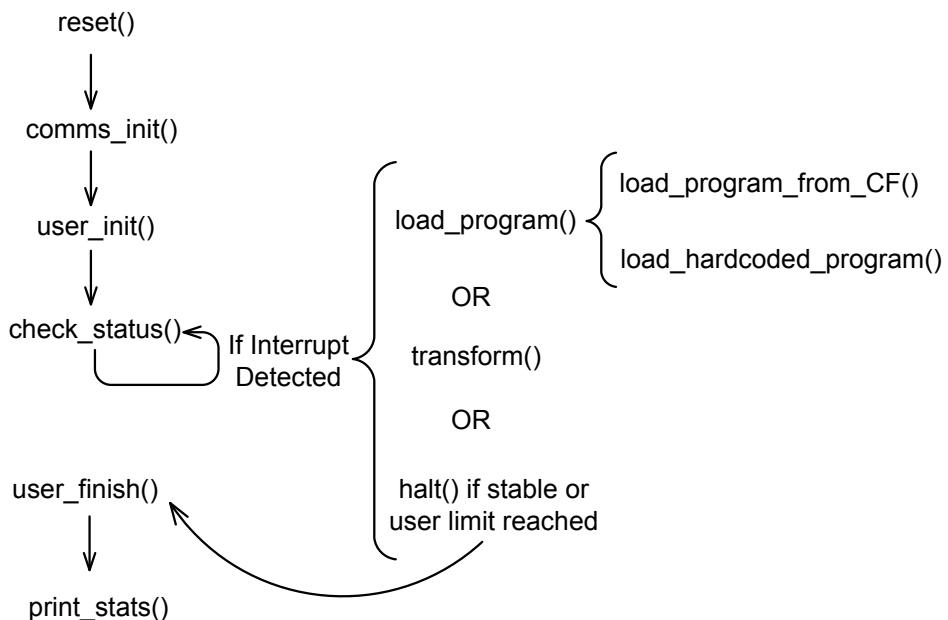

| Figure 4.2. HAoS driver flow diagram .....                                                              | 135 |

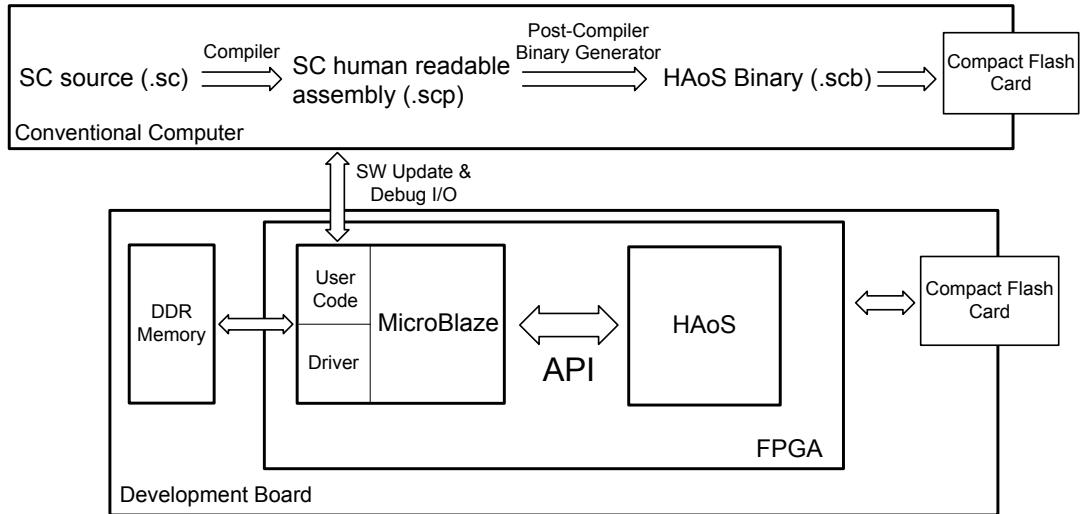

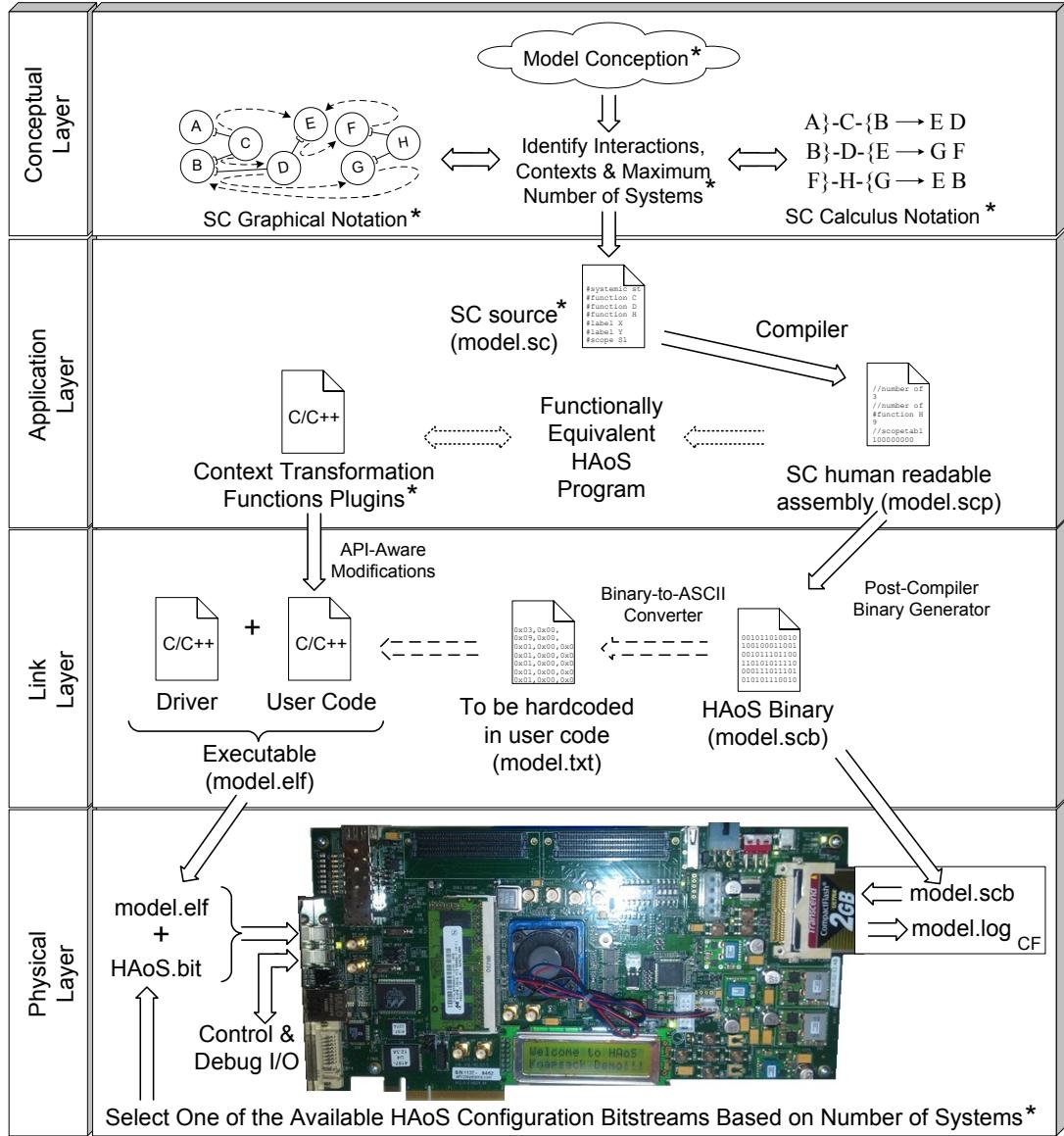

| Figure 4.3. HAoS programming toolchain and software framework .....                                     | 136 |

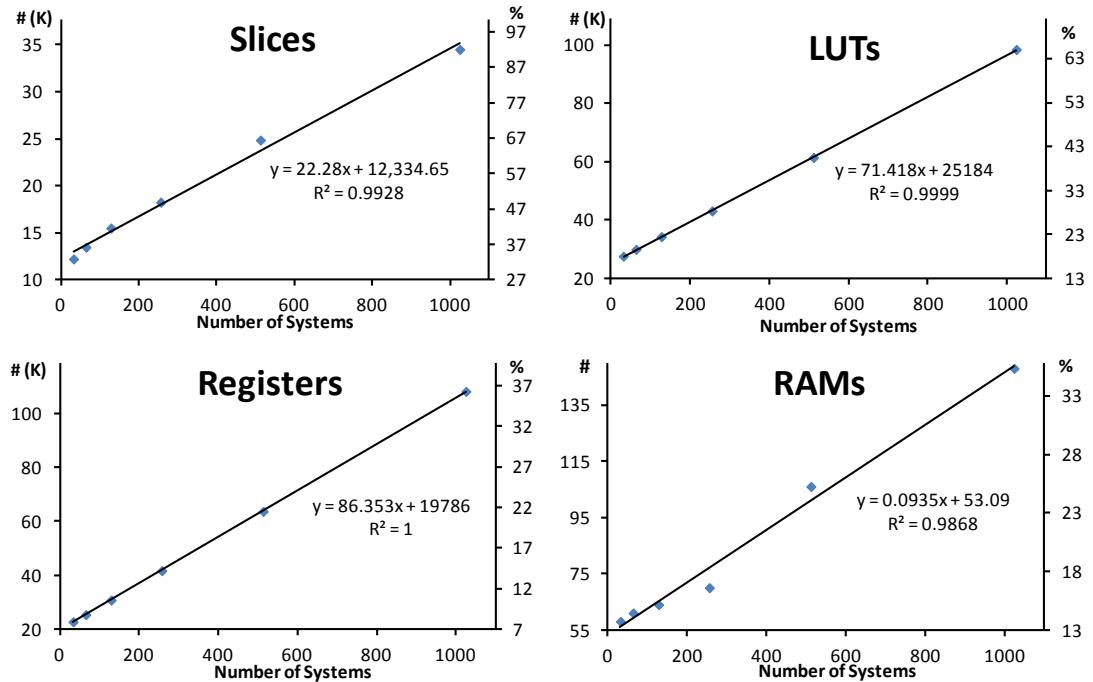

| Figure 4.4. Linearity on area utilization as the number of maximum supported systems is increased ..... | 140 |

| Figure 4.5. HAoS model development methodology .....                                                    | 141 |

| Figure 5.1. 16-Element Binary Knapsack Problem .....                                                    | 146 |

| Figure 5.2. Representation of the optimal solution for the Binary Knapsack Problem ..                   | 147 |

|                                                                                                                              |     |

|------------------------------------------------------------------------------------------------------------------------------|-----|

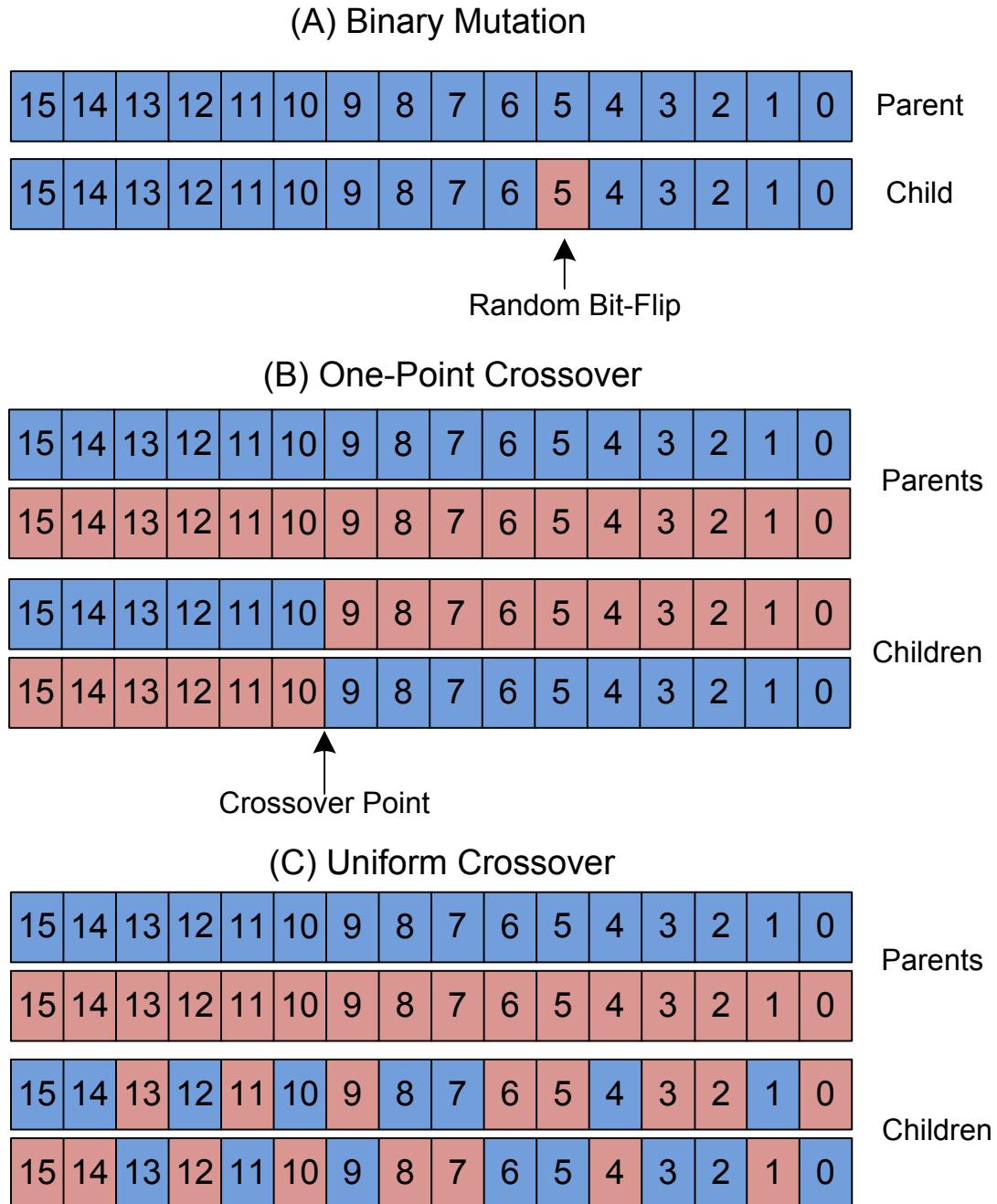

| Figure 5.3. Standard genetic operators: Binary Mutation, One-Point and Uniform Crossover .....                               | 148 |

| Figure 5.4. The binary knapsack SC model. ....                                                                               | 150 |

| Figure 5.5. Binary knapsack problem experimental results across a range of number of systems.....                            | 154 |

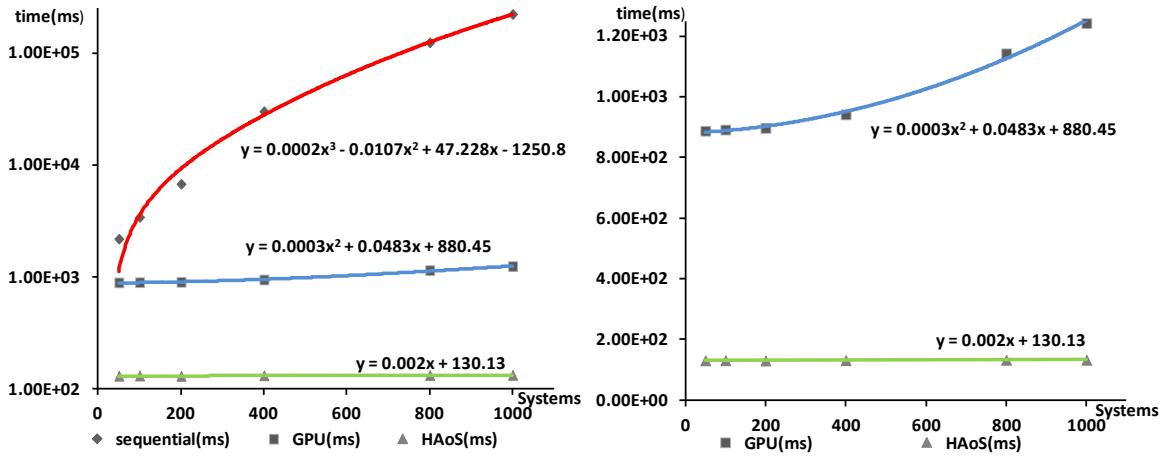

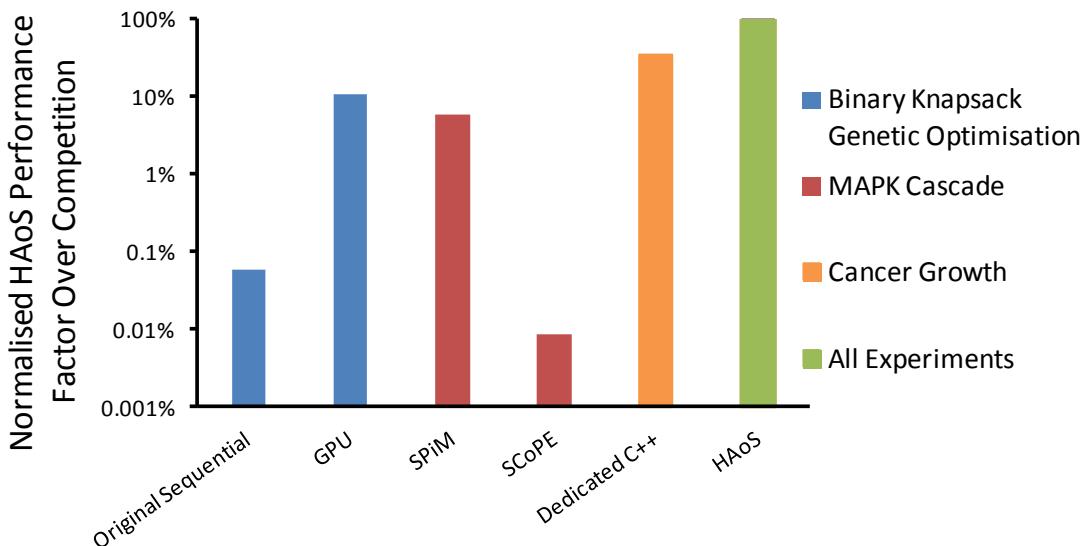

| Figure 5.6. Binary knapsack experiments HAoS normalised performance compared to the sequential and GPU implementations ..... | 155 |

| Figure 5.7. Simplified biochemical description of the MAPK signalling cascade ignoring phosphate groups .....                | 158 |

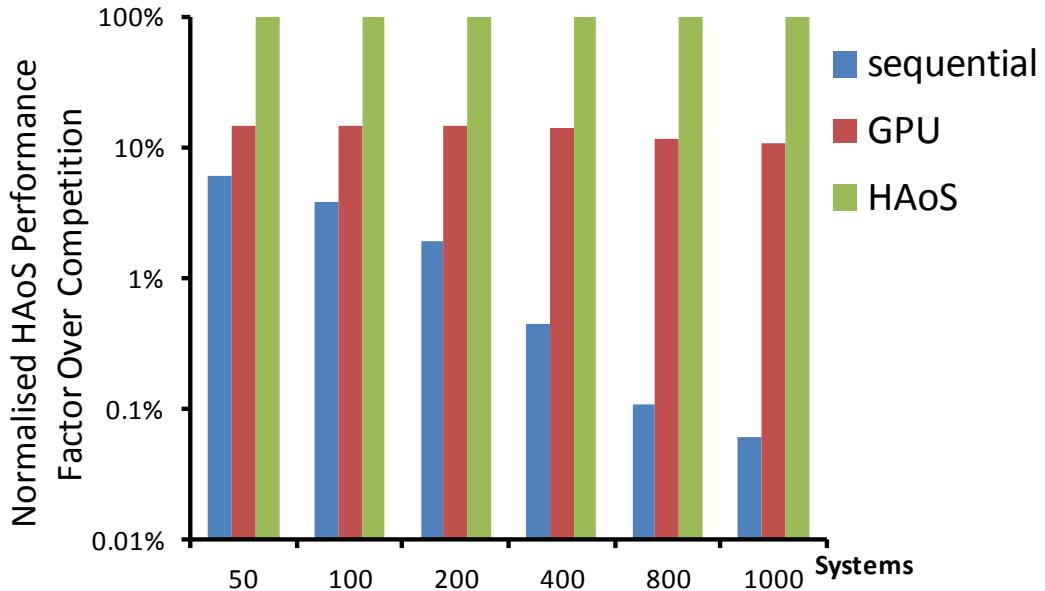

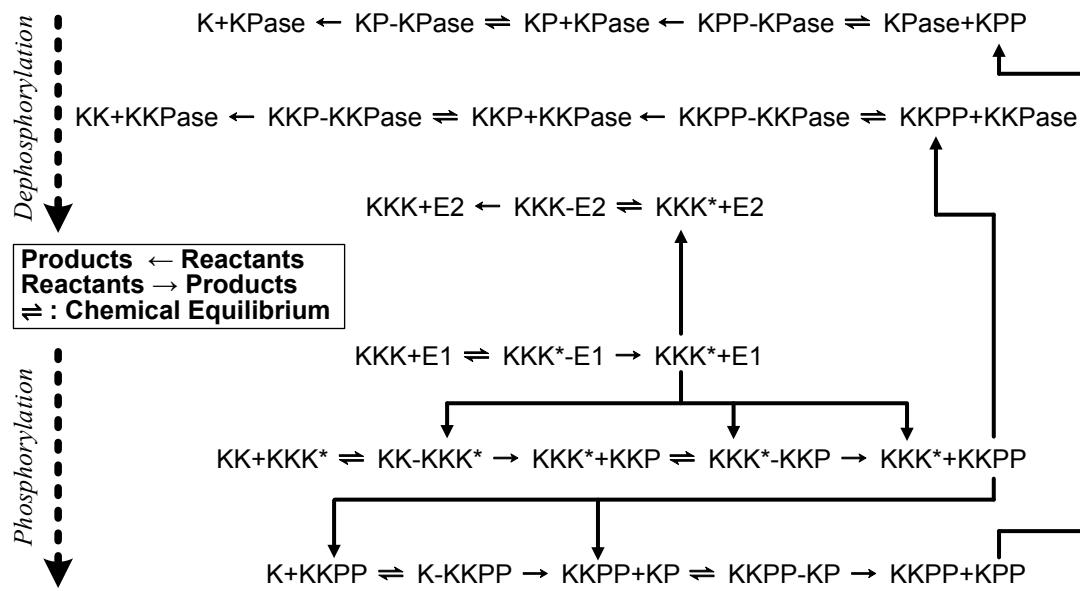

| Figure 5.8. The HAoS MAPK model in SC graphical notation. ....                                                               | 161 |

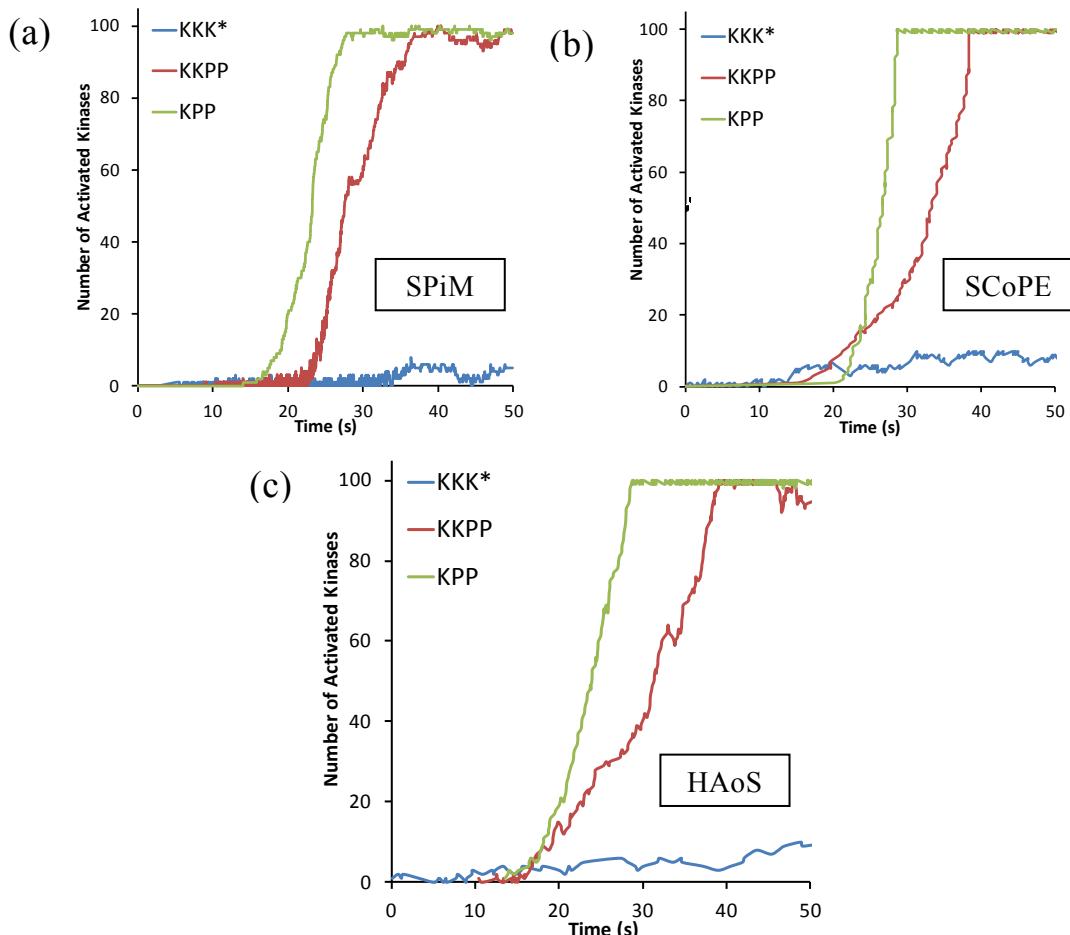

| Figure 5.9. Traversing the MAPK signalling cascade .....                                                                     | 166 |

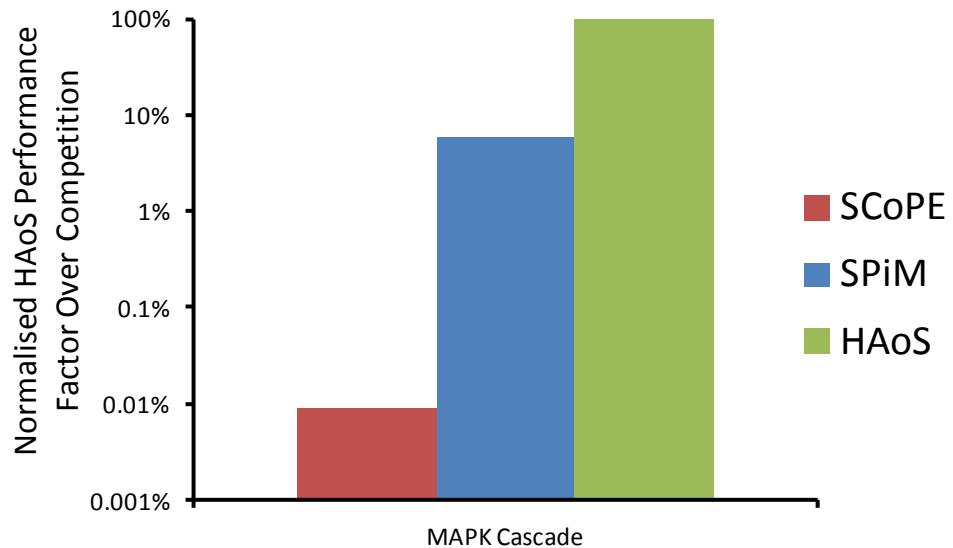

| Figure 5.10. MAPK cascade experiment HAoS normalised performance compared to the SPiM and SCoPE simulators.....              | 168 |

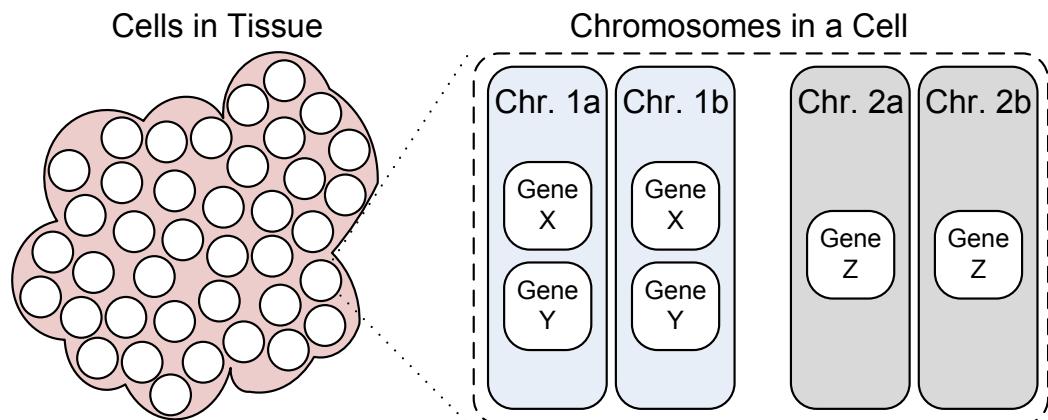

| Figure 5.11. The reference cancer model.....                                                                                 | 171 |

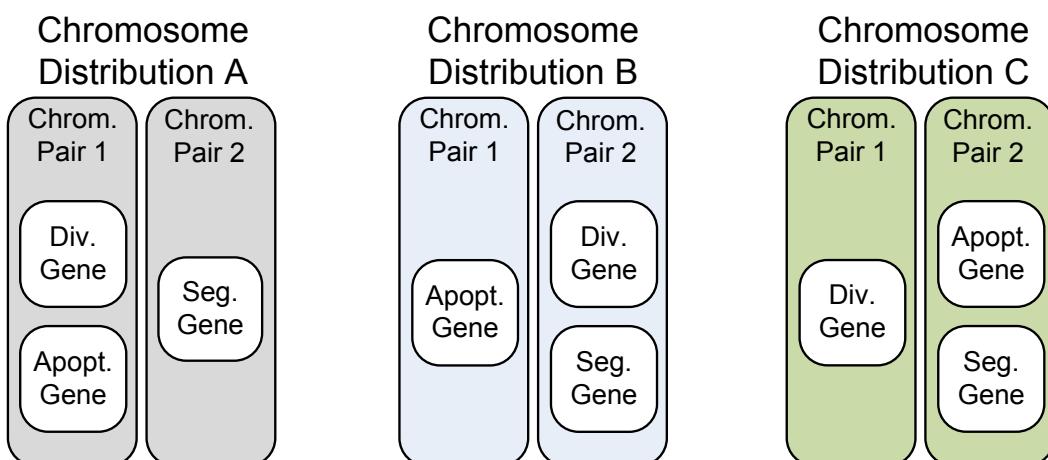

| Figure 5.12. The three genetic configurations, employing different gene chromosomal linkage .....                            | 171 |

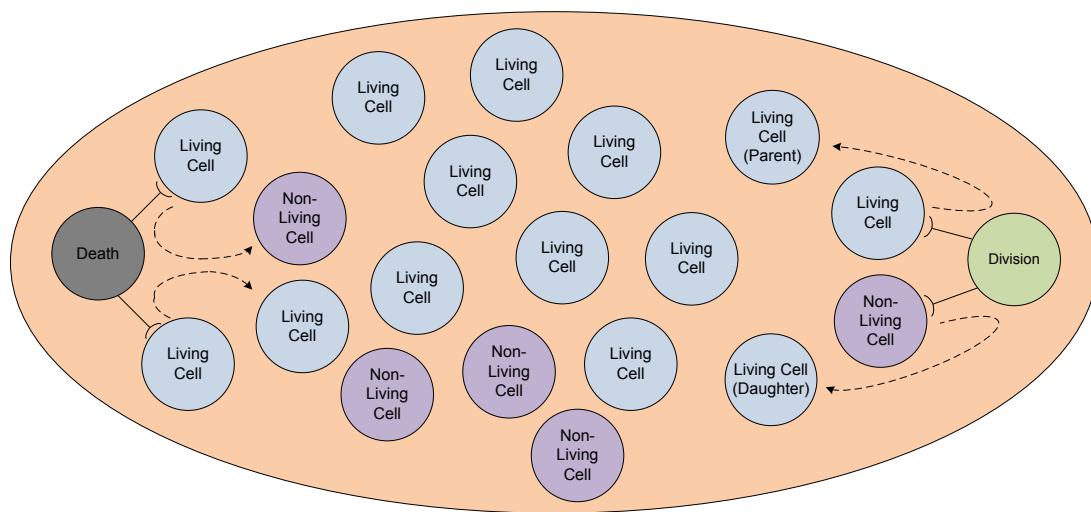

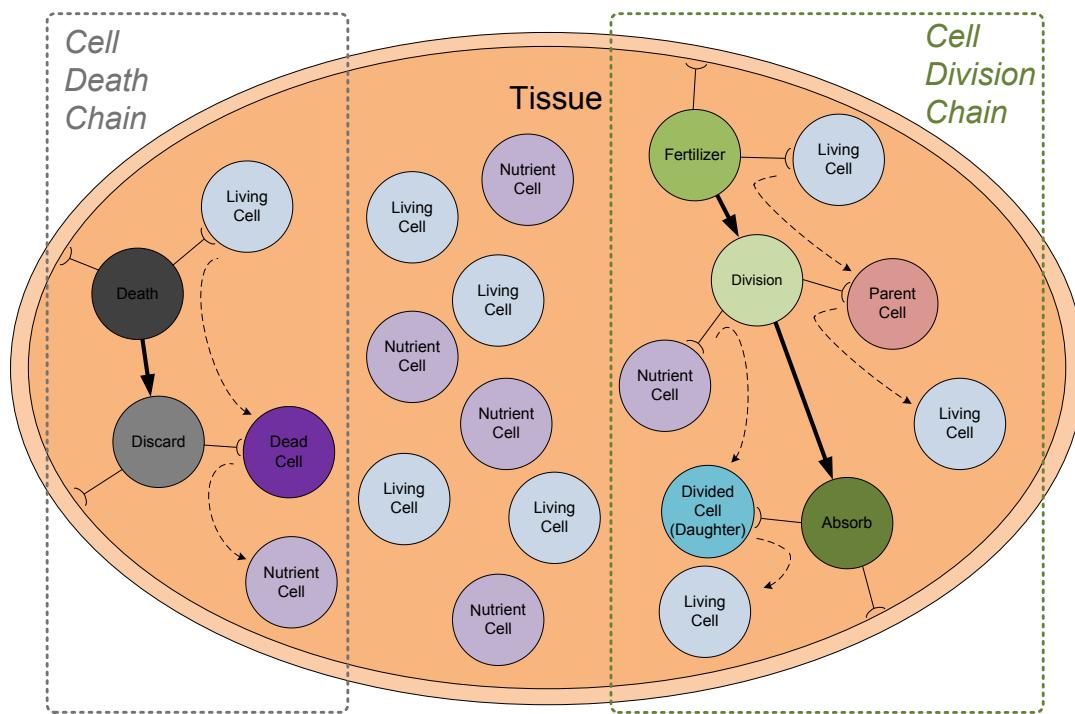

| Figure 5.13. Initial SC cancer model.....                                                                                    | 175 |

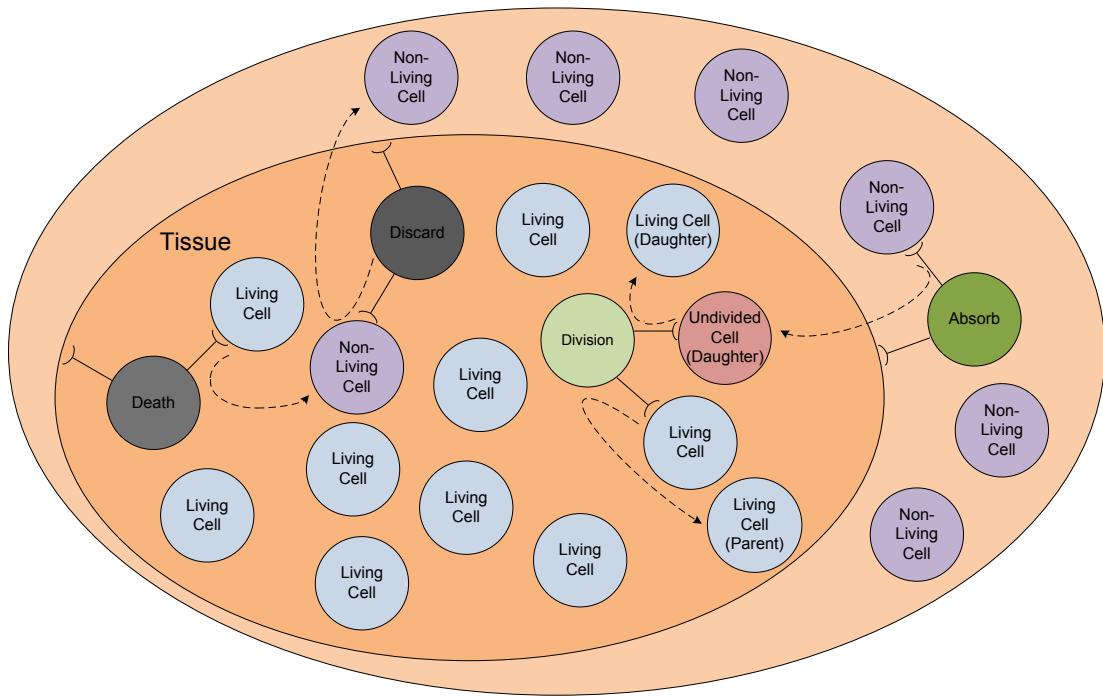

| Figure 5.14. Revised SC cancer model with tissue and two-step cell death and division processes .....                        | 176 |

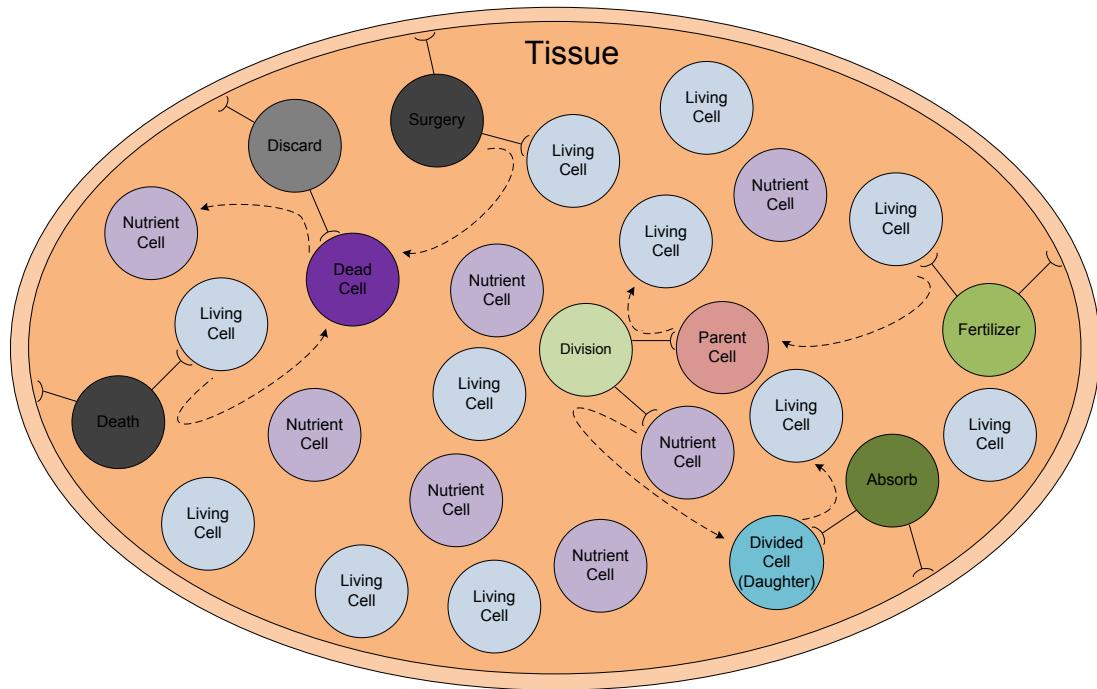

| Figure 5.15. Therapy-Enabled SC cancer model.....                                                                            | 178 |

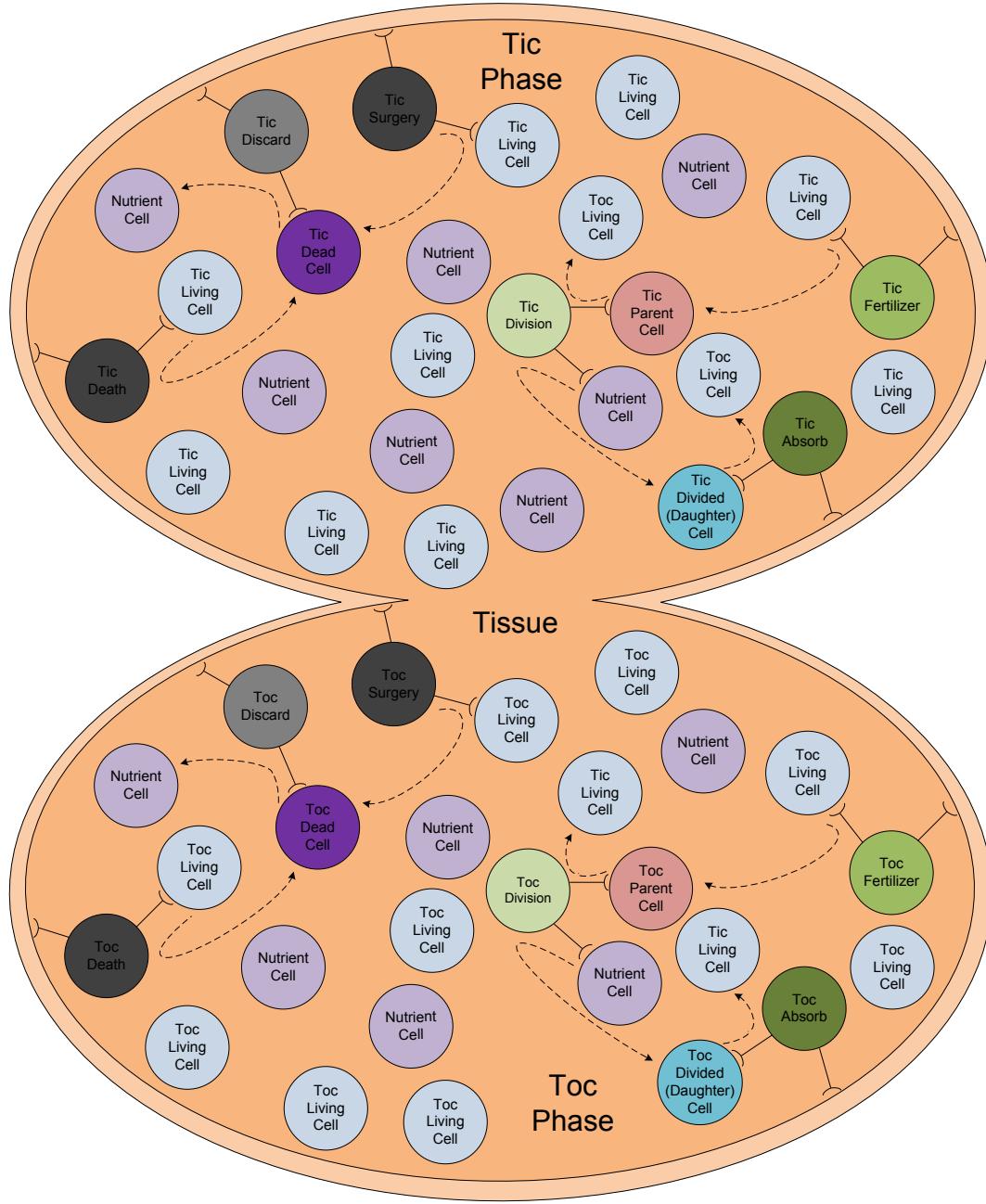

| Figure 5.16. Time-Enabled (Tic-Toc) SC cancer model .....                                                                    | 181 |

| Figure 5.17. Optimized SC cancer model .....                                                                                 | 186 |

| Figure 5.18. SC cancer model data systems and their contents .....                                                           | 189 |

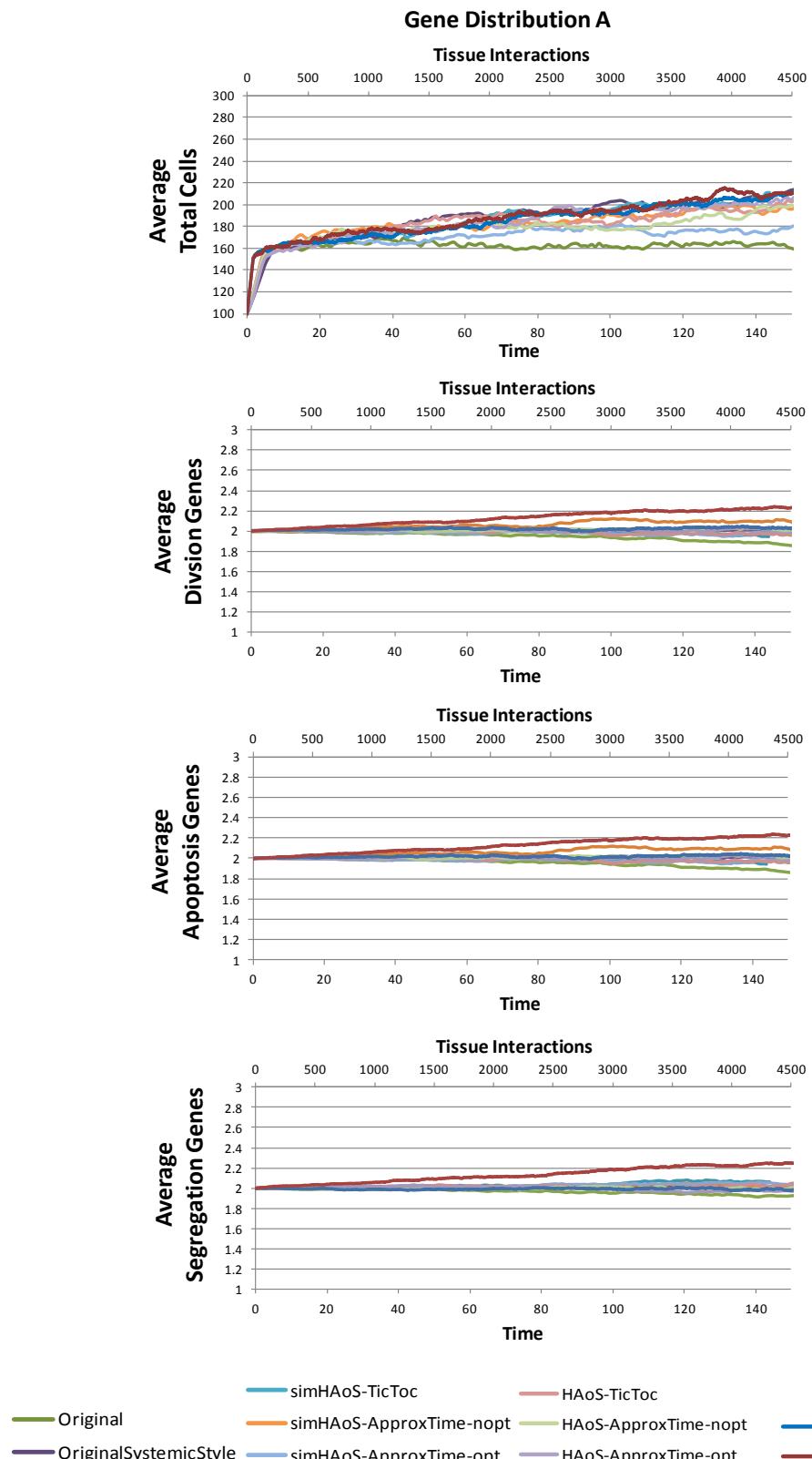

| Figure 5.19. Non-therapy cancer models comparison for gene distribution A .....                                              | 195 |

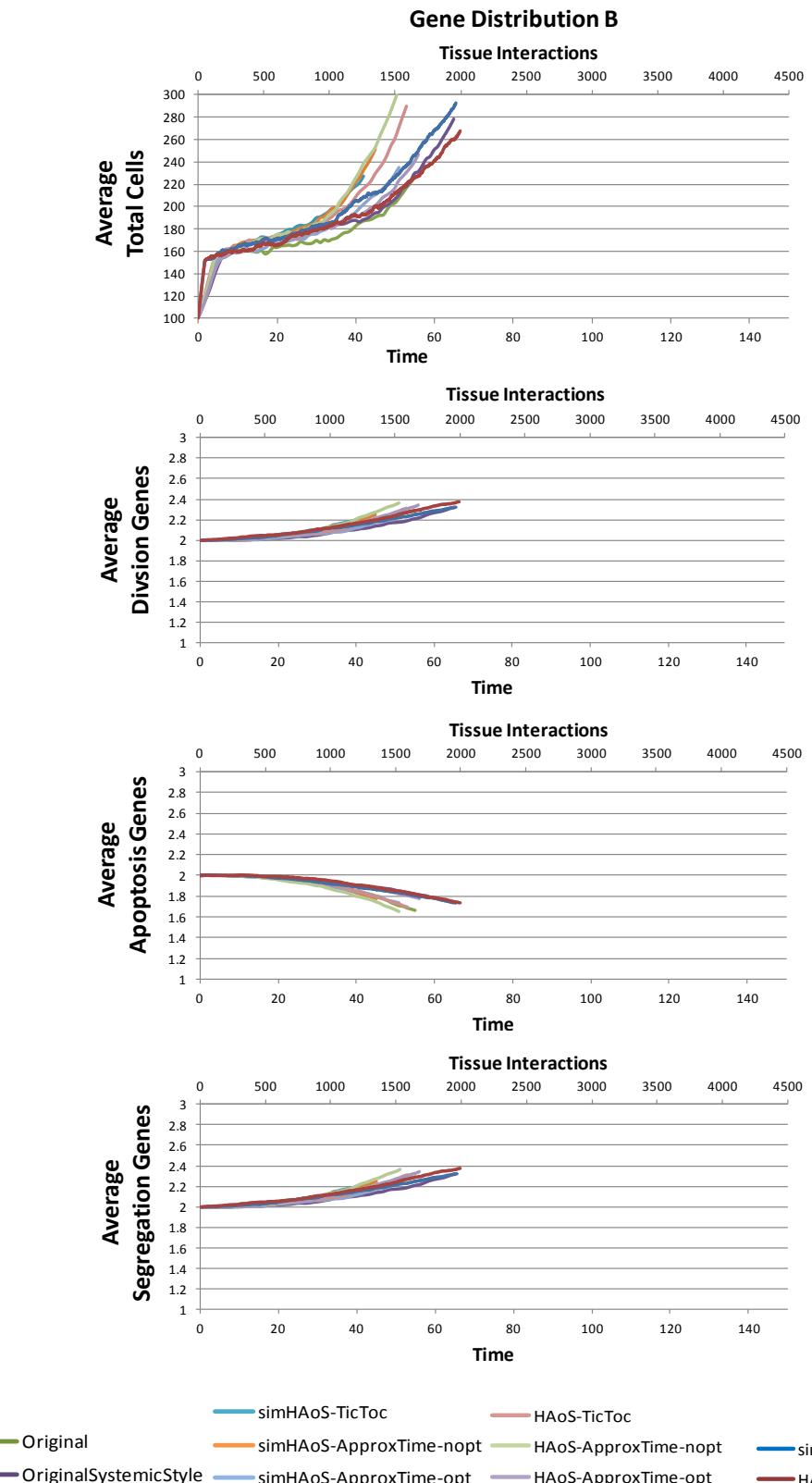

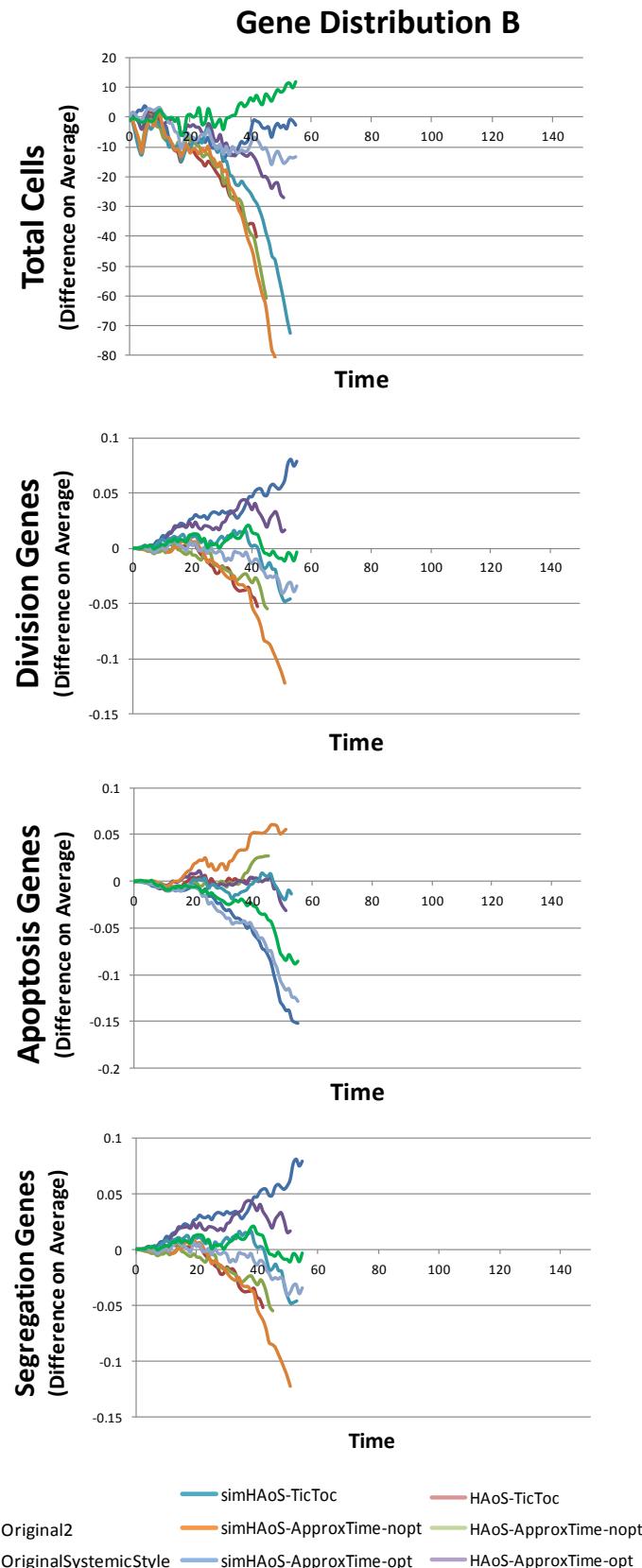

| Figure 5.20. Non-therapy cancer models comparison for gene distribution B .....                                              | 196 |

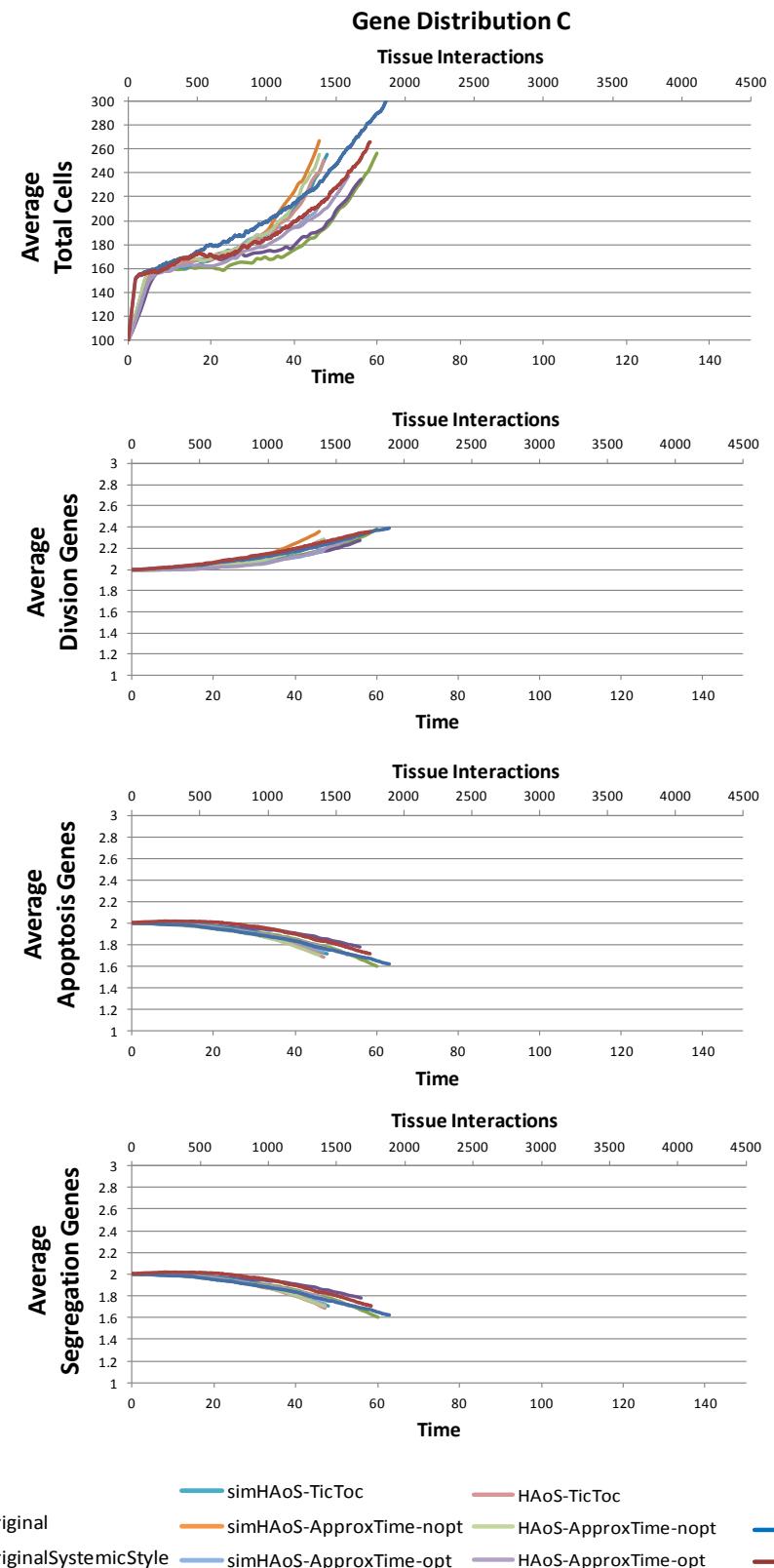

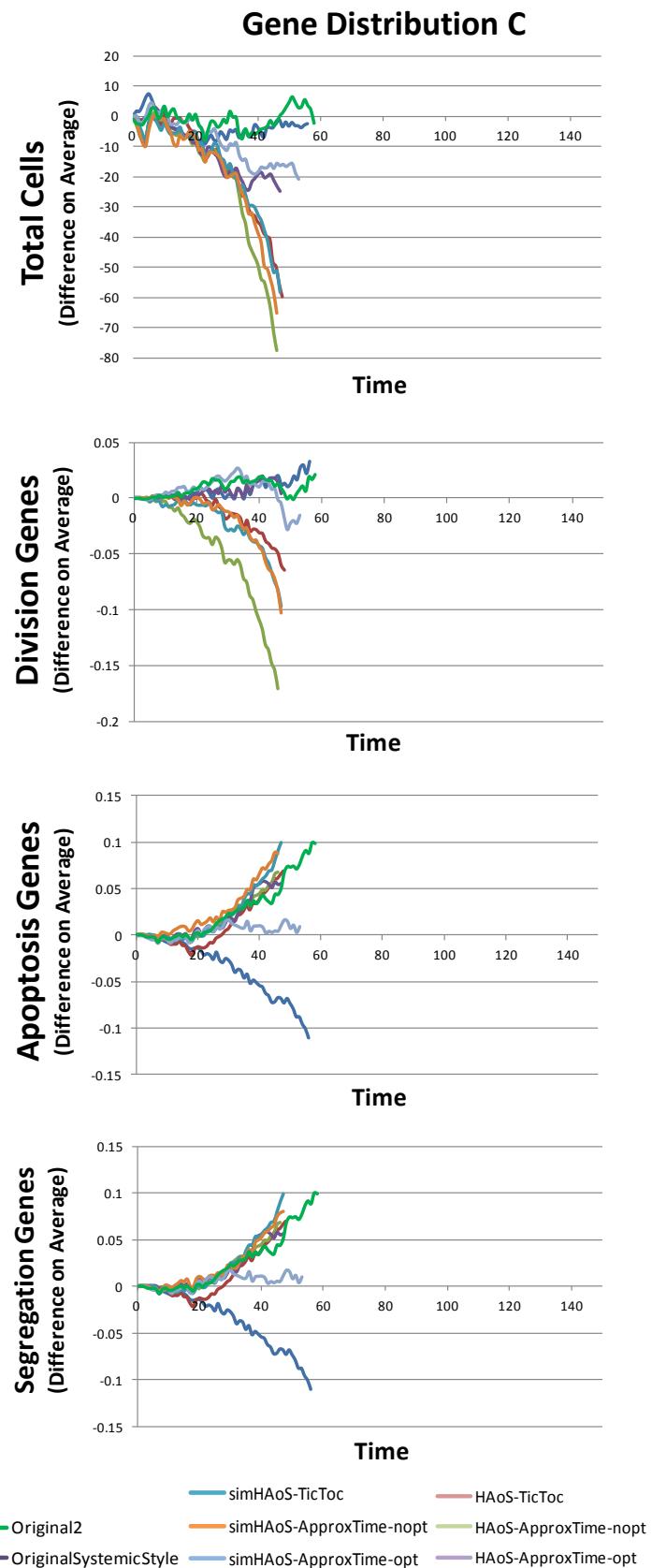

| Figure 5.21. Non-therapy cancer models comparison for gene distribution C .....                                              | 197 |

|                                                                                                                                                 |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

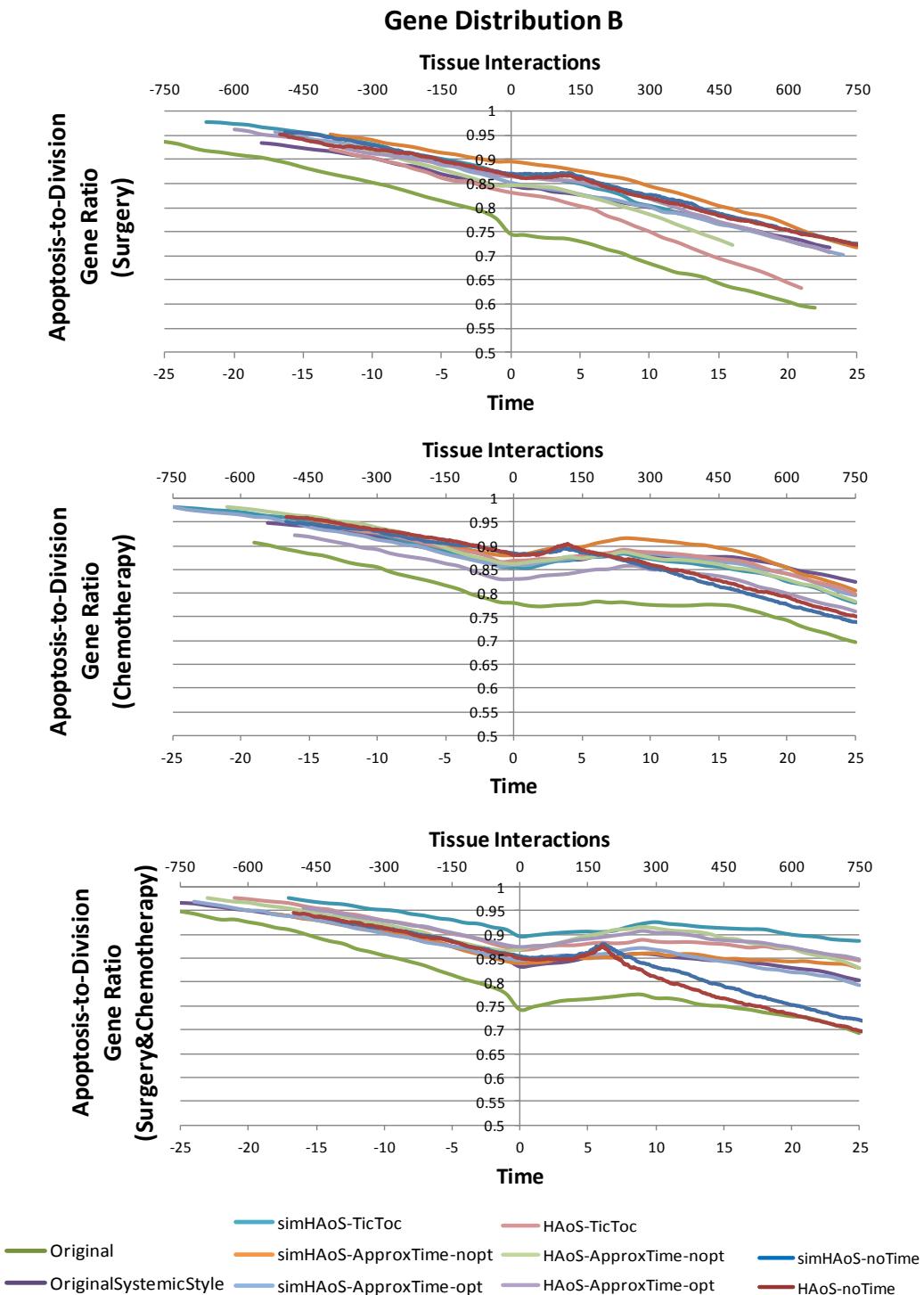

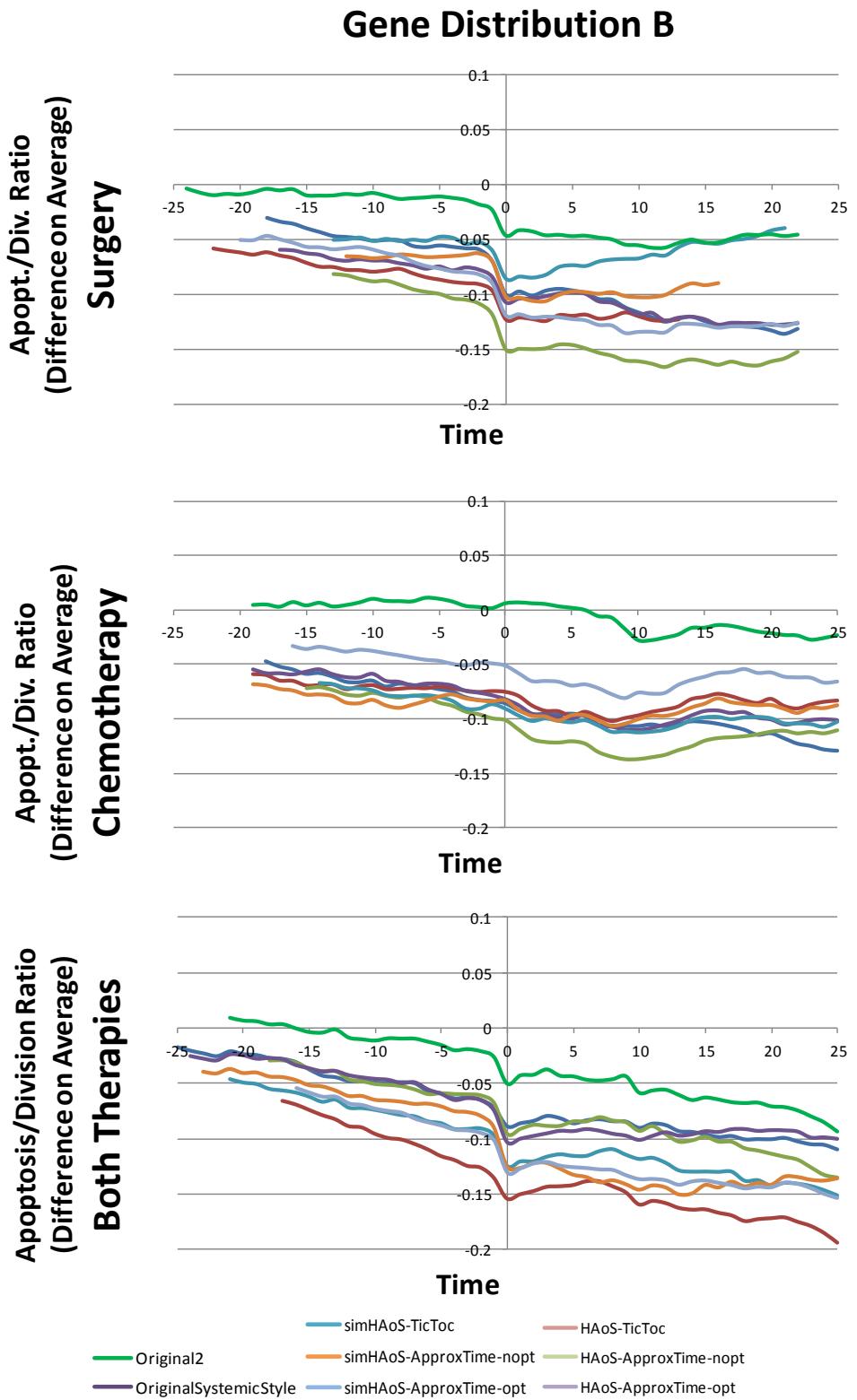

| Figure 5.22. Therapy-enabled cancer models comparison near cancer diagnosis for gene distribution B .....                                       | 198 |

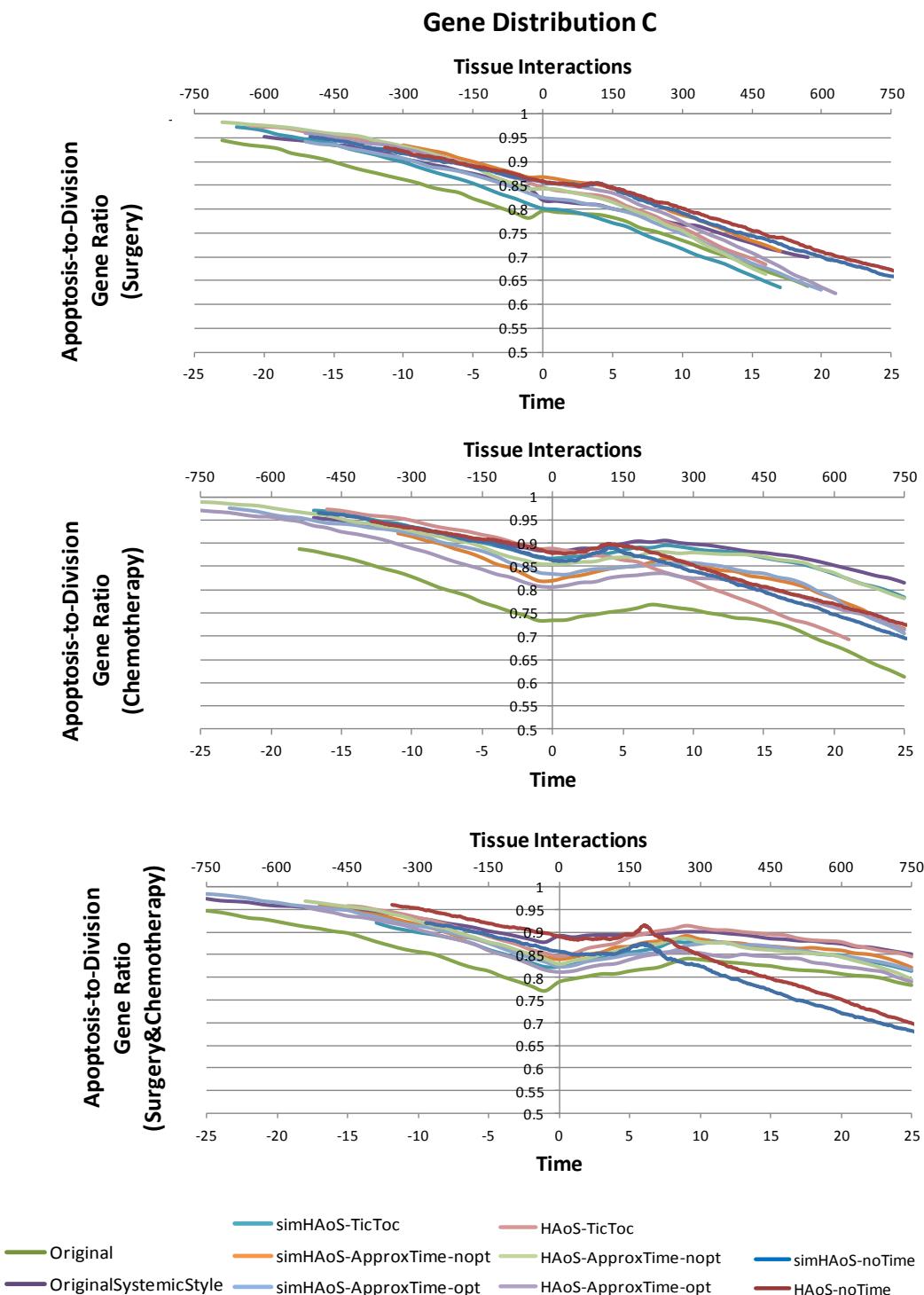

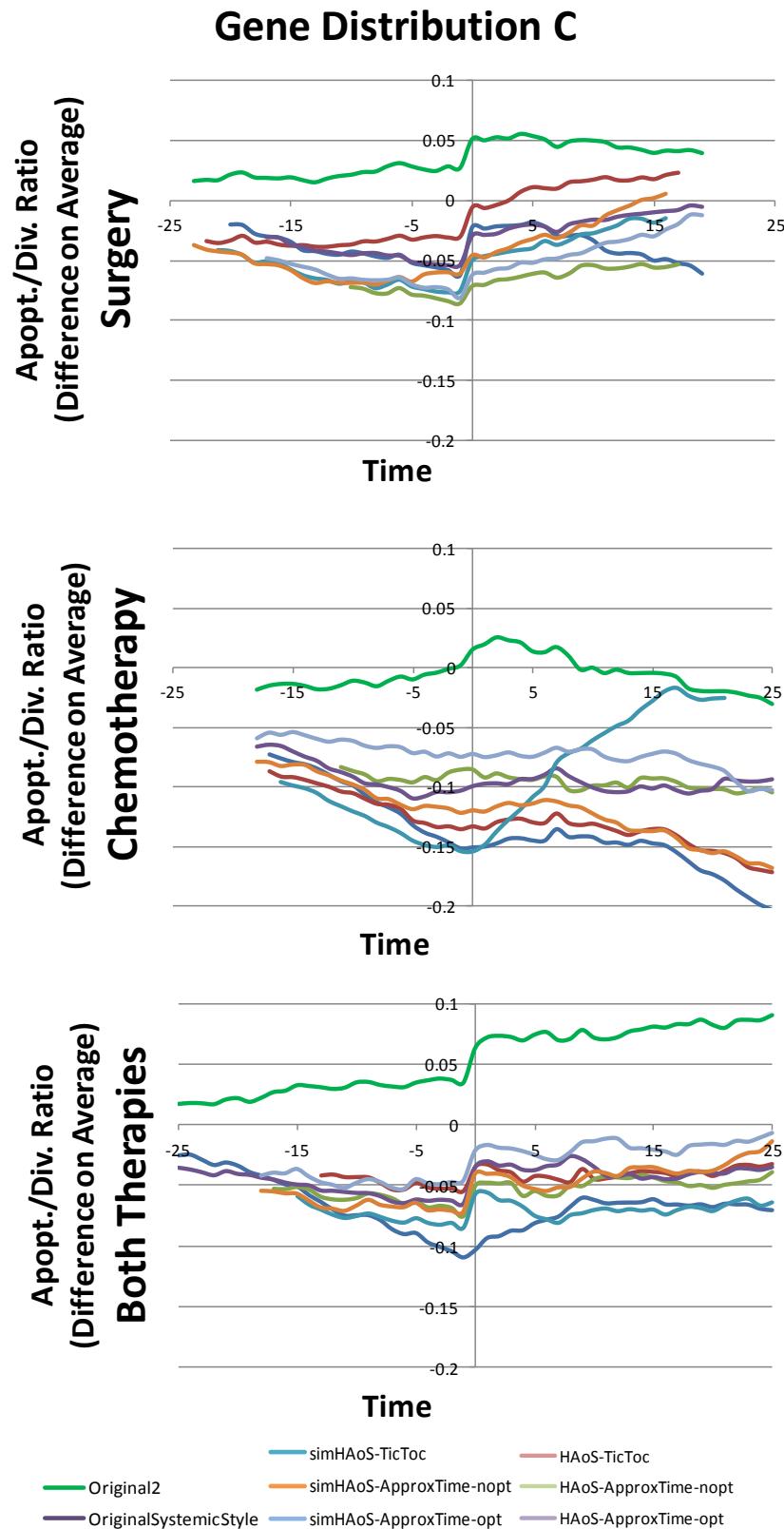

| Figure 5.23. Therapy-enabled cancer models comparison near cancer diagnosis for gene distribution C .....                                       | 199 |

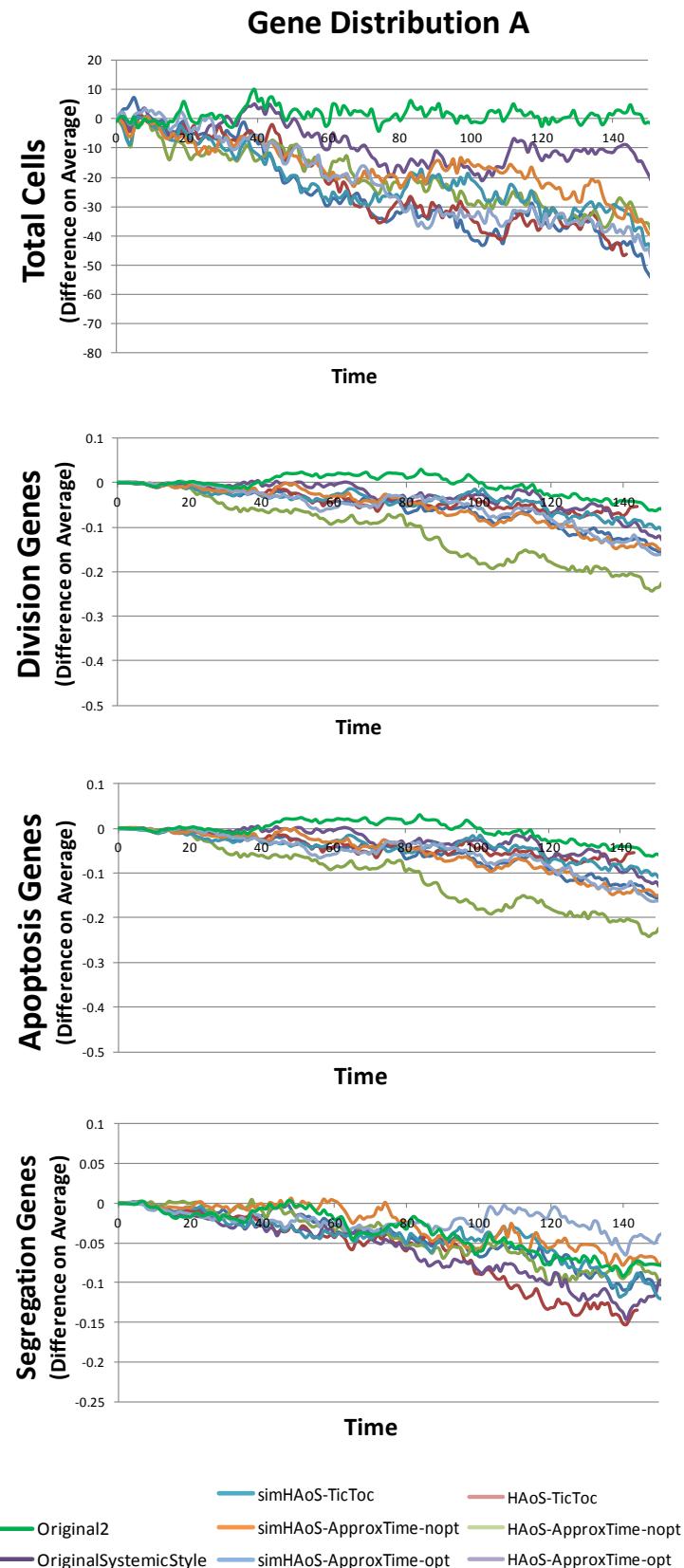

| Figure 5.24. Non-therapy cancer time-supporting models results differences for gene distribution A .....                                        | 203 |

| Figure 5.25. Non-therapy cancer time-supporting models results differences for gene distribution B .....                                        | 204 |

| Figure 5.26. Non-therapy cancer time-supporting models results differences for gene distribution C .....                                        | 205 |

| Figure 5.27. Differences on apoptosis-to-division ratio between the therapy-enabled time-supporting cancer models for gene distribution B ..... | 206 |

| Figure 5.28. Differences on apoptosis-to-division ratio between the therapy-enabled time-supporting cancer models for gene distribution C ..... | 207 |

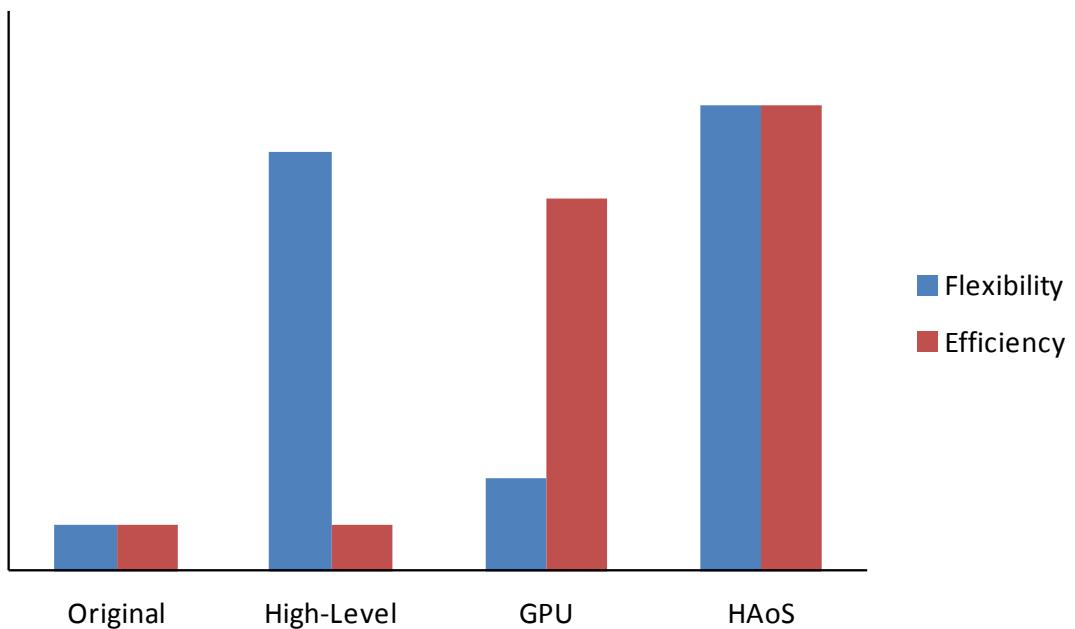

| Figure 5.29. Cancer growth experiment HAoS normalised performance against the dedicated c++ implementation .....                                | 209 |

| Figure 5.30. Performance Evaluation Results Summary .....                                                                                       | 211 |

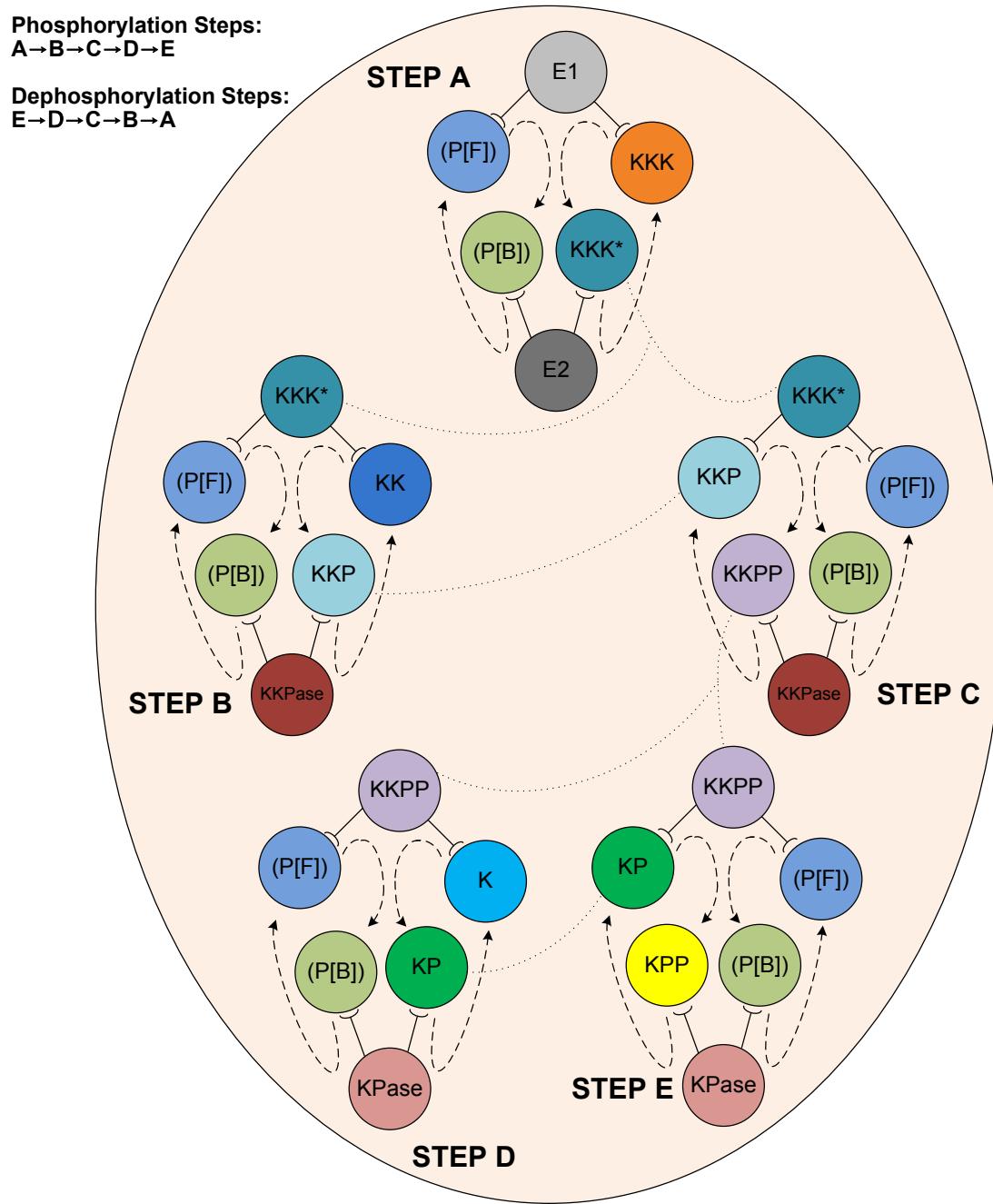

| Figure 6.1. Comparison in flexibility and efficiency provided by the HAoS programming platform .....                                            | 225 |

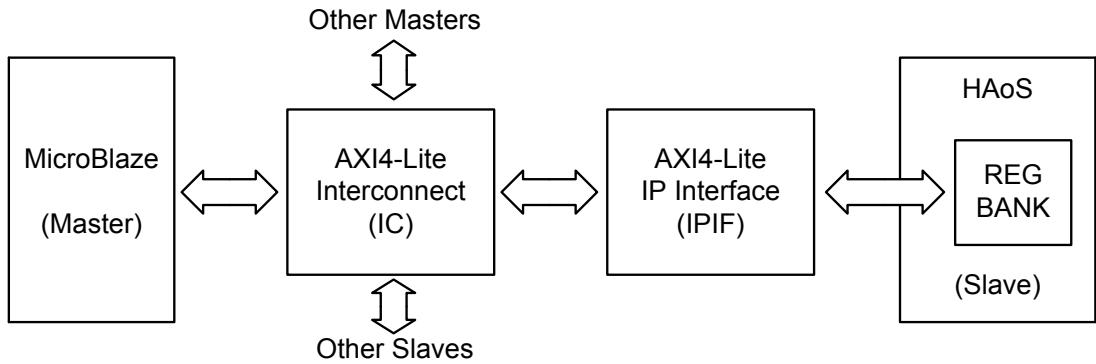

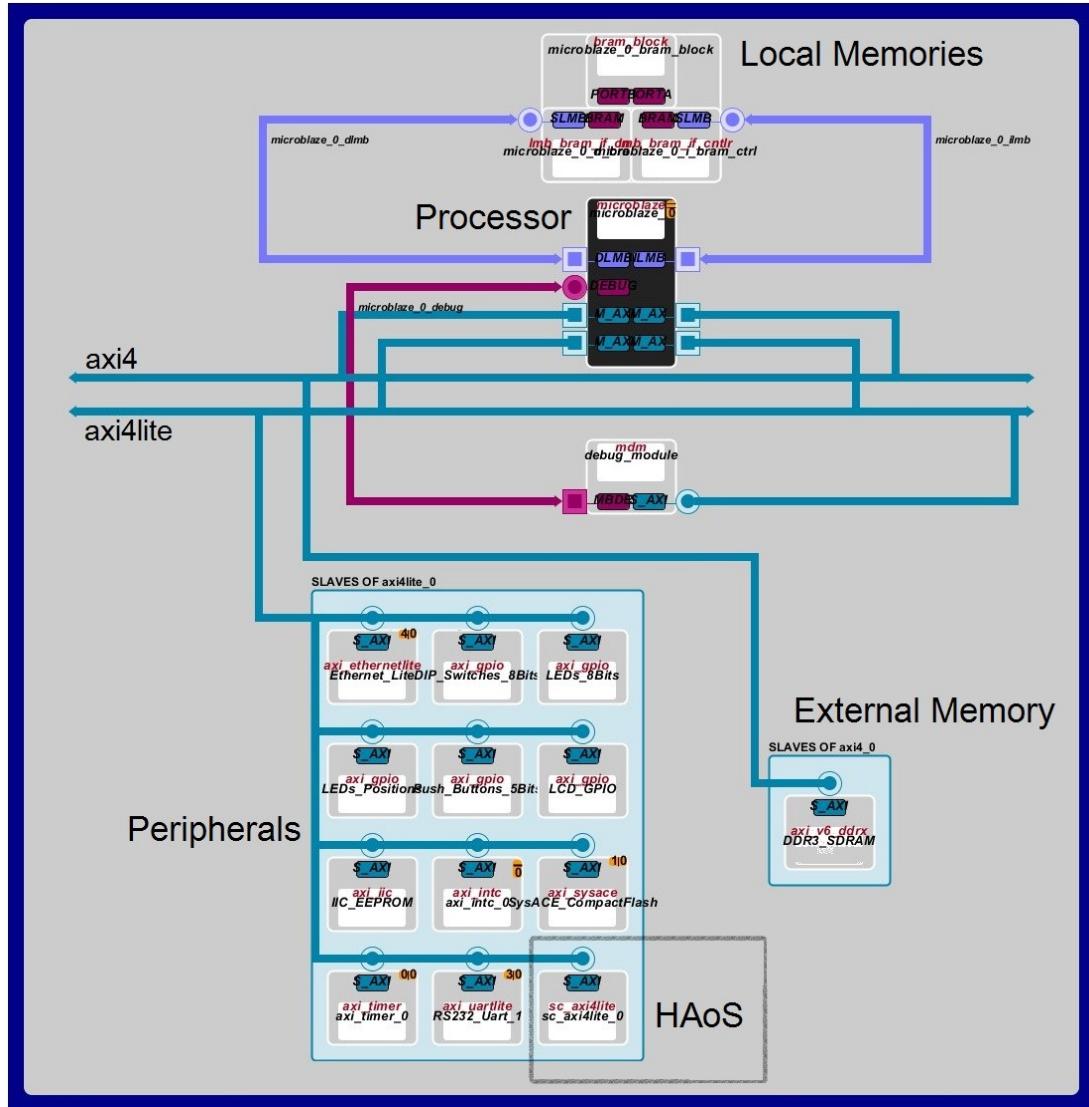

| Figure B.1. The AXI4-Lite based HAoS-MicroBlaze communication link .....                                                                        | 248 |

| Figure B.2. Top-level On-Chip HAoS Platform Block Diagram .....                                                                                 | 249 |

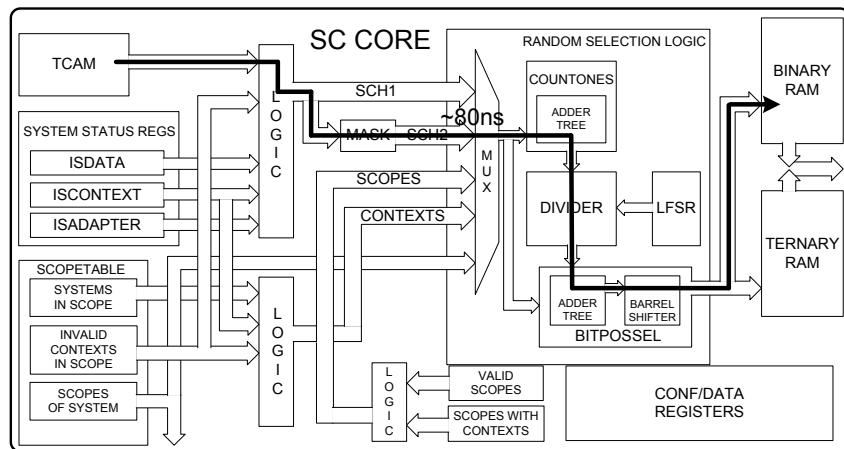

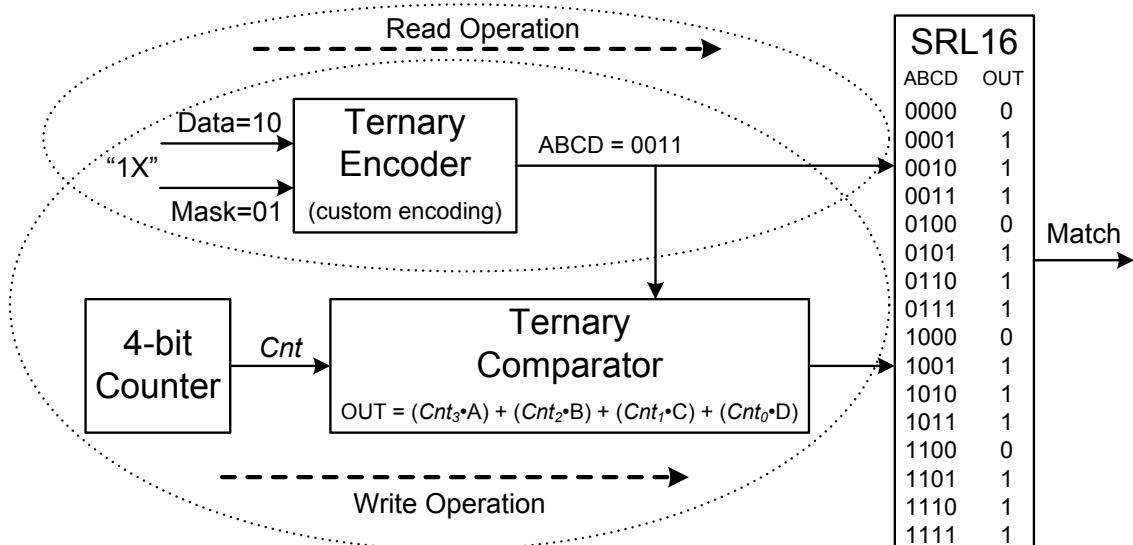

| Figure C.1. Critical path of initial HAoS design based on static timing analysis .....                                                          | 250 |

| Figure C.2. The Revised RSL module .....                                                                                                        | 251 |

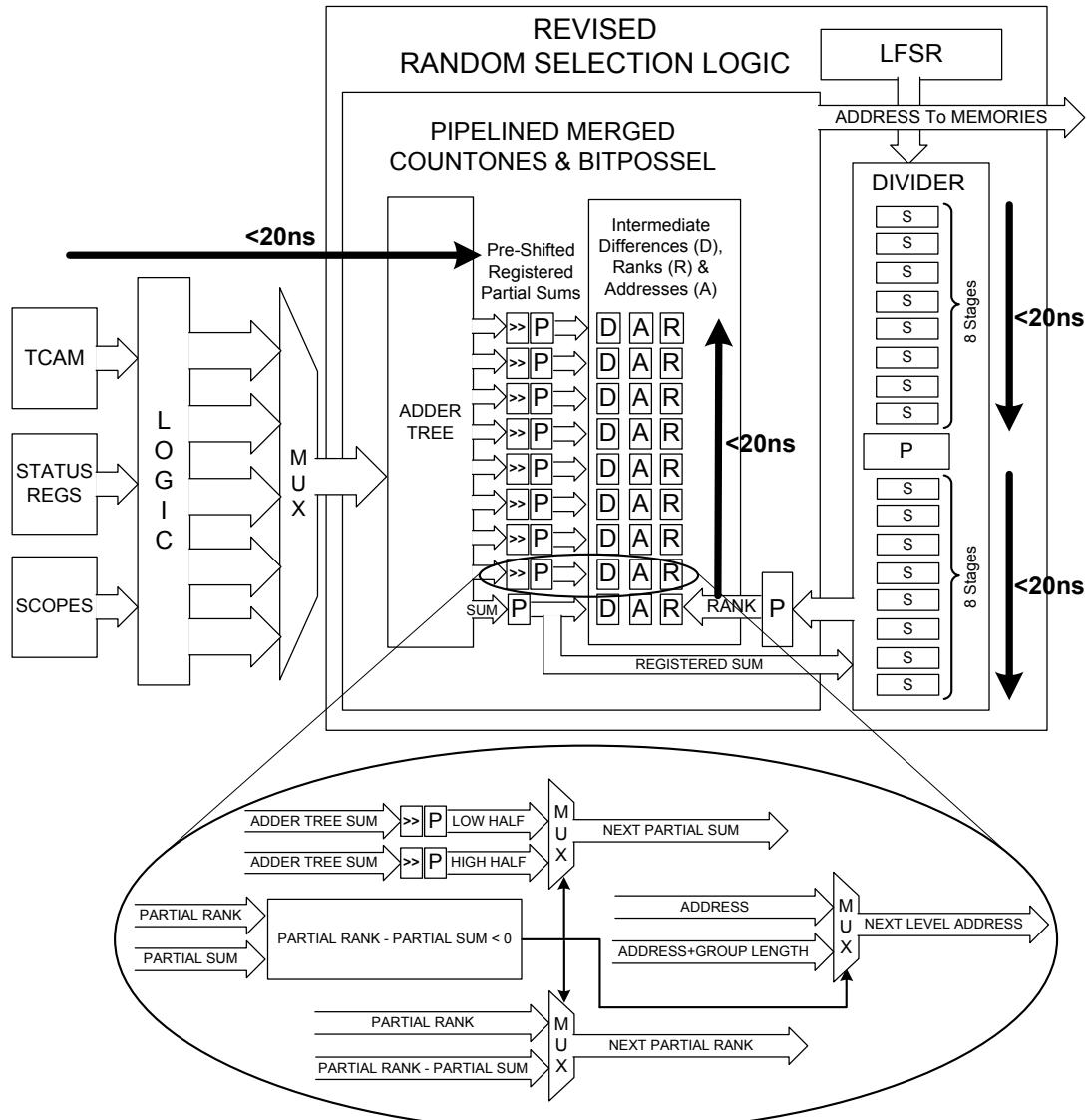

| Figure D.1. The SRL16E-based building block of the base HAoS TCAM .....                                                                         | 253 |

| Figure H.1. Annotated HAoS ASCII program example .....                                                                                          | 262 |

## List of Tables

|                                                                                                                                           |     |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1.1. Properties that differentiate natural from conventional computation .....                                                      | 19  |

| Table 2.1. Approaches to Natural Computation and alternative paradigms .....                                                              | 30  |

| Table 2.2. Features of the original SC implementation .....                                                                               | 69  |

| Table 2.3. Detailed evaluation of the reviewed hardware-based approaches .....                                                            | 75  |

| Table 3.1. HAoS Compression Code.....                                                                                                     | 91  |

| Table 3.2. Implementation-specific features of HAoS and prior implementations .....                                                       | 93  |

| Table 3.3. HAoS Instruction Fields .....                                                                                                  | 95  |

| Table 3.4. HAoS Instruction Set .....                                                                                                     | 95  |

| Table 3.5. Simulated SC test programs.....                                                                                                | 114 |

| Table 3.6. HAoS Prototype (64 systems) Implementation Statistics on Virtex-6 LX240T FPGA .....                                            | 117 |

| Table 4.1. Commonly used interfaces for off-board communication and their nominal raw bandwidths .....                                    | 121 |

| Table 4.2. Sustainable Bandwidth Results for various practical configurations implementing common communication interfaces on FPGAs ..... | 123 |

| Table 4.3. Indicative Collection of Available Soft Processors .....                                                                       | 125 |

| Table 4.4. Benchmark timing improvements reflecting various architectural optimizations .....                                             | 137 |

| Table 4.5. HAoS platform implementations statistics as the number of maximum systems increases.....                                       | 139 |

| Table 5.1. Summary of the Knapsack SC model functions .....                                                                               | 152 |

| Table 5.2. The HAoS MAPK model interactions in SC calculus notation. ....                                                                 | 162 |

| Table 5.3. Summary of the MAPK SC model functions.....                                                                                    | 164 |

| Table 5.4. Performance of the HAoS, SPiM (v1.13) and SCoPE simulators based on simulation duration.....                                   | 167 |

|                                                                                                                                                                           |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 5.5. Time-Enabled (Tic-Toc) cancer SC model interactions .....                                                                                                      | 182 |

| Table 5.6. Timeless and Approximate Time cancer SC models interactions .....                                                                                              | 184 |

| Table 5.7. Optimized Approximate Time cancer SC model interactions .....                                                                                                  | 186 |

| Table 5.8. Biological representation of the systems of the SC cancer models .....                                                                                         | 188 |

| Table 5.9. Absolute and normalized average execution times for all simulated cancer scenarios .....                                                                       | 200 |

| Table 5.10. Statistical comparison of the time-enabled cancer models to the reference one in terms of mean error (ME), standard deviation (STD) and correlation (COR).... | 208 |

| Table E.1. Summary of the provided functions (simplified) in the HAoS API .....                                                                                           | 255 |

| Table F.1. Summary of file types used along HAoS model development .....                                                                                                  | 256 |

## List of Listings

|                                                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| Listing 3.1. HAoS Source Code Example.....                                                                              | 109 |

| Listing 3.2. Selected output from the 3 example SC test programs verifying the functionality of HAoS by simulation..... | 115 |

| Listing 5.1. Binary Knapsack SC model source code.....                                                                  | 151 |

| Listing 5.2. Verification environment output for Binary Knapsack SC model .....                                         | 153 |

| Listing 5.3. MAPK Signalling Cascade SC model source code.....                                                          | 163 |

| Listing A.1. Addition in Multiple Scopes (Test1 Example) Source Code.....                                               | 245 |

| Listing A.2. Subtraction-escape and then multiply and print (Test2 Example) Source Code.....                            | 246 |

| Listing A.3. Context Adapting (Test3 Example) Source Code .....                                                         | 247 |

| Listing G.1. Time-Enabled Cancer Model SC Source Code.....                                                              | 257 |

| Listing G.2. Timeless Cancer Model SC Source Code .....                                                                 | 258 |

| Listing G.3. Approximate-time Cancer Model SC Source Code .....                                                         | 259 |

| Listing G.4. Optimized Approximate-time Cancer Model SC Source Code .....                                               | 260 |

## List of Algorithms

|                                                                                      |     |

|--------------------------------------------------------------------------------------|-----|

| Algorithm 5.1. The reference cancer model algorithm.....                             | 173 |

| Algorithm 5.2. The reference cancer model algorithm written in a “systemic way” .... | 191 |

# Chapter 1

## ***Introduction***

### **1.1 Introduction to Natural Computation**

It has been claimed that everything computes [1], [2]. Biological systems appear to be superb at performing something that resembles computation, although they accomplish that by using methods fundamentally different from those used to perform conventional computation [3], [4]. Supercomputers strive to simulate a microsecond of protein folding [5], yet biology scales from molecules to cells, then to organisms, then to species and so on to more complex structures.

Complex tasks, like DNA synthesis and sequencing, have been shown to outpace Moore's law [6]. Although the semiconductor industry has been making continuous leaps in the past half century, silicon-based approaches seem weak in delivering more raw power, as the physical limitations of this technology appeared quite some time ago [7]. While engineers are left to devise workarounds to these issues (cache memory, branch prediction, out-of-order execution, multi-core chips), modern computers seem to be inefficient and too slow to model biological processes. This incompetence is not surprising, since, although the advances in microprocessor technologies have been numerous, the fundamental design principles have remained unchanged for almost a century. The vast majority of computing devices today follow the design pattern revealed in 1945 by John von Neumann [8]. This is a completely centralized partitioning, comprising of a set of main building blocks: the Central Arithmetic (CA) unit, the Central Control (CC) unit, the Memory (M) and Input/Output (I/O) devices. Von Neumann believed that those "distinctions suggest themselves immediately" [8] and until today the majority of those in the scientific community and the consumer industry agree with this. However nature does not.

While computation in a conventional electronic computer is the outcome of a program, which is a set of defined instructions that are sequentially executed, the rules are quite different in nature. Nature seems to work in a massively parallel fashion instead. Natural systems, viewed in different levels of abstraction, have a common characteristic. A

massive number of subtasks are carried out at any given moment in order to accomplish an operation. This operation can be any biological process. For example, under different contexts, the process of photosynthesis from a leaf in a tree involves chemical reactions among complex biochemical systems in order to convert carbon dioxide in organic compounds [9]. This process is happening through all the leaves of the tree, and it is vital for the tree itself. The tree comprises a system of leaves, branches and roots and each is playing its role in accomplishing the survival of the tree. At the same time, photosynthesis is not only vital for the tree but for all flora in the ecosystem, and in turn for any living organism on the planet relying on oxygen for survival.

The human brain is another example. It is composed of billions of neurons which continuously interact [10] with each other. The brain is just one of the organs that build the nervous system, which in turn along with other systems compose the human body. Groups of people form societies and all the societies, joined, build mankind.

Numerous examples like the ones mentioned above can be given: a herd of deer, an ant colony, our planetary system, the immune system, a school of fish and even the Dow Jones Index. All of them are composed from fundamental building blocks but also, combined with others, constitute more complex structures. The underlying processes seem to work without any centralised control method but with the coexistence and interaction of their structural elements.

The observation of the success of nature in coping with such complex systems had a significant impact in modern science, giving birth to several biologically inspired research fields [11]: Evolutionary Computing (EC) [12], Artificial Neural Networks (ANN) [13], Artificial Immune Systems (AIS) [14], Swarm Intelligence (SI) [15], Particle Swarm Optimization (PSO) [16], Cellular Automata (CA) [17], L-systems [18], Artificial Life (ALife) [19], DNA computing [20] and Quantum Computing (QC) [21] are some of them. According to [11], these fields form three groups: the first five are inspired by nature, the next two (CA and L-systems) simulate and emulate nature by means of computing, while the rest use natural materials for computation. They are all influenced/inspired by nature, serving computation and modelling purposes and hence they constitute a super-group: Natural Computation [11], [22], [23].

Characteristics, embedded in natural systems, have been a rich source of inspiration for the scientific community since it is commonly accepted that nature can outperform any manmade device on factors like complexity, homoeostasis, self-organization, self-replication, self-adaptation and fault-tolerance.

**Table 1.1. Properties that differentiate natural from conventional computation**

| Property Type | Natural Computation | Conventional Computation |

|---------------|---------------------|--------------------------|

| Computational | Stochastic          | Deterministic            |

|               | Asynchronous        | Synchronous              |

|               | Parallel            | Serial                   |

|               | Distributed         | Centralized              |

|               | Continuous          | Batch                    |

|               | Approximate         | Precise                  |

|               | Embodied            | Isolated                 |

|               | Local Knowledge     | Global Knowledge         |

|               | Circular causality  | Linear causality         |

| Behavioural   | Self-organised      | Explicitly Organised     |

|               | Fault tolerant      | Fault intolerant         |

|               | Open-ended          | Limited                  |

|               | Complex             | Simple                   |

|               | Autonomous          | Human-reliant            |

|               | Homoeostatic        | Heterostatic             |

|               | Robust              | Brittle                  |

Various opposing properties that highlight the distinction between natural and conventional computation as they are separated in [22], [24] are given in Table 1.1. Therefore, natural computation in general is/has [22]:

- Stochastic: The behaviour of natural systems is non-deterministic and their interactions are randomised.

- Asynchronous: Mostly<sup>1</sup>, behaviour is not synchronized. There are no clock signals which determine the timing of every behaviour akin to our processors.

- Parallel: Interactions are usually concurrent among all systems.

- Distributed: Computation is spread and allocated across several systems to achieve the result.

- Continuous: Natural systems are designed to keep working for as long as possible; their behaviours are designed to work continuously for the lifetime of each organism.

- Approximate: The notion of an exact number or quantity is meaningless.

---

<sup>1</sup> There can be approximate synchronization to solar or lunar cycles or seasons.

- Embodied: A natural system and its environment constantly affect each other.

- Local Knowledge: Knowledge is not stored in a centralised archive or library. An interaction can occur among two systems at the same hierarchical level which are within range of each other, implying scopes of interaction.

- Circular causality: Two interacting natural systems affect each other during interaction.

- Self-organised: Natural systems define their own organization and architecture without external interventions.

- Fault-tolerant: Natural systems are tolerant to partial failures and usually able to also self-heal.

- Open-ended: Systems in nature are able to adapt and constantly evolve.

- Complex: Natural systems are organized over numerous hierarchical levels in a bottom-up manner. Starting with basic elements at the lowest level, they built successively more complex systems at the higher levels.

- Autonomous: Natural systems are self-reliant and independent of any external authority.

- Homoeostatic: A natural system preserves the inner stability of its state(s) by internal feedback mechanisms.

- Robust: Natural systems can handle and adapt to unforeseeable situations.

Influenced by the importance of those properties, a novel computation model was conceived by Bentley [24]. The new model, systemic computation (SC), was proven to be Turing complete [25] and attempts to embody the much sought characteristics of biological systems found in nature as listed in the left column of Table 1.1<sup>2</sup>. Turing completeness was proved by implementing a rule 110 cellular automata algorithm [17], [26], [27], stating the equivalence of SC to any other computation model.

## 1.2 Introduction to Systemic Computation

Systemic computation, further discussed in section 2.3, has its roots on the work of Jean-Louis Le Moigne's [28] on General System Theory [29]. The core notion that was adopted by systemic computation can be found in the second percept [28] of Le

---

<sup>2</sup> In this work the focus will be on the computational properties.

Moigne's systemic method – interaction – as opposed to the corresponding percept on Descartes' analytical method [30] – reduction. Reductionism can be traced back to ancient Greece [31]. It states that a complex system is a sum of its parts but it is known to have limitations [32]. Holism on the contrary argues that a complex system is more than the sum of its constituents.

Systemic computation adopts a holistic analysis approach of systems embracing the significant importance of the interactions of their fundamental elements and their environment. Its intention is to resemble natural computation in order to simulate biological processes effectively. To accomplish this, it follows the conventions listed below [24] :

- Everything is a system.

- Systems may comprise or share other nested systems.

- Systems can be transformed but never destroyed.

- Interaction between systems may cause transformation of those systems, where the nature of that transformation is determined by a contextual system.

- All systems can potentially act as context and affect the interactions of other systems, and also all systems can potentially interact in some context.

- The transformation of systems is constrained by the scope of systems.

- Computation is transformation.

According to these conventions, it is implied that in order to perform any computation in SC, two main tasks are always involved:

- Identify the interacting systems and

- Transform the interacting systems according to the interaction determined by the contextual system in the scope that this interaction is defined.

### 1.3 Systemic Computation in Practice

While the Systemic Computation paradigm has been designed to feature all the properties of Natural Computation, as they are given in Table 1.1, a practical platform to support SC has yet to be devised. Its highly unconventional nature makes the implementation of such a platform very challenging, since it radically differs from the notion of computation, as we have grown to perceive it. The validity of the concept has

been proven in previous work [22], but in order to take advantage of its potential, applying SC in a practical and efficient way is essential.

Three SC implementations have been developed so far (Original Sequential SC Implementation [24], High-level SC Implementation [22] and the GPU SC Implementation [34]). However, since their conventional design does not denote a natural way of implementing the SC paradigm, they are just low and high level simulations of a systemic computer, with only the latest implementation succeeding in obtaining satisfactory results in terms of speed. As shown later, in section 2.4, these software approaches are largely inappropriate to implement a SC platform, mainly due to the conventional sequential nature of their underlying architecture which is incompatible with the SC paradigm. As illustrated in Figure 1.1, there is no current implementation that combines flexibility with efficiency. Consequently there is a clear need for a new SC programming platform that is both efficient and flexible.

**Figure 1.1. Comparison in flexibility and efficiency of prior software SC implementations. A practical hardware-based implementation is expected to provide a balanced SC programming solution**

As previous work has demonstrated the incompatibility of conventional hardware for SC, it seems likely that the most practical, viable and usable platform which addresses this need would be a novel hardware-based implementation.

It is thus vital to investigate the trade-offs of available implementation platforms in order to identify the substrate that a practical SC platform can be based on and then explore how the practical features of conventional computation can be combined with the

unconventional properties of natural computation and architectural features of SC. In order to properly evaluate such a controversial design, it is required to identify the requirements that define a practical platform for SC and the degree that each of them can be satisfied.

## 1.4 Hypothesis

The hypothesis of this thesis is:

**It is possible to implement a practical Systemic Computation hardware architecture that is viable and useful.**

The thesis will provide evidence to support this hypothesis through an investigation of the viability and utility of a SC practical implementation. Yet, the unconventional nature of SC may itself be proven to be partially incompatible with the practicality aspect of the implementation, as practicality partially implies a conventional way of thinking and undertaking well-studied and proven techniques to accomplish a feasible and usable means to perform Systemic Computation.

In essence, this collision of the definitions of unconventionality and practicality, in a computational context, formulates the main investigation that this work attempts to tackle. It is suggested that investigating the features, advantageous and disadvantageous, that modern hardware implementation platforms offer while exploring potential suitable architectures for Systemic Computation, will result in a satisfactory compromise combining the benefits of the inherent natural properties of SC with the usability and utility provided by a practical platform.

This work will investigate the *viability* of a practical SC implementation and the trade-offs between encompassing natural properties against the feasibility and constraints of the hardware taking into consideration flexibility, performance and scalability. The supported programming model should provide a user-friendly interface to the underlying architecture, which should be optimized in terms of speed and area while being able to easily scale in size.

A practical SC *hardware implementation* is required because software approaches do not seem to be able to efficiently handle the complexity or properly address the implied non-conventional architecture of the SC paradigm (see sections 2.1, 2.4.1 and 2.4.2), since they solely rely on conventional processors. The *utility* of such a custom hardware design will be demonstrated by showing that natural processes can be modelled in a

more native way by addressing these limitations and mapping more efficiently and accurately the SC architectural features.

The outcome of this work should be a *practical* hardware implementation in order to be easily reproduced and also be, at least partially, compatible with conventional architectures, in terms of communications. This will enable reusability and enhance flexibility in order to achieve a broader user community which in return can improve the architecture and expand its functionality. This implies that the suggested implementation should also address availability (meaning that a user should be able to relatively easily access the selected enabling technology). Thus it should be based on a mature technology, possibly using Commercial Off-The-Shelf (COTS) [33] components, with a rich knowledge base which is broadly used both in academia and industry.

This work provides evidence to support its hypothesis by proving a proof of concept via a realisation of a novel SC hardware implementation. Building on the discussion of the three previous sections, it accomplishes this by focusing on three main research challenges:

*Chg1: How can a hardware platform support the natural properties that are central to SC?*

Specifically this challenge focuses on the inherent to SC natural properties of Table 1.1. An ideal platform would be able to support a hardware implementation that would be stochastic, asynchronous, parallel, continuous, distributed, approximate (in a high level) and embodied while it would show circular causality and have only local knowledge. Incorporating these properties, the SC implementation would be self-organized, fault-tolerant, (at least virtually) open-ended, complex, autonomous, homoeostatic and robust.

*Chg2: How can a hardware platform support the underlying architecture of SC?*

Specifically this challenge focuses on the compatibility of the platform with the inherent features of the implied SC architecture: systems, scopes, contexts and interactions among systems should be able to be represented in a manner that allows efficient modelling of systems interactions.

The first two research challenges refer to the *viability of a SC implementation*. It is suggested that investigating the trade-offs of implementing and attempting to combine the desired natural properties with the architectural features of SC will sufficiently

explore how viable such an implementation is. The third challenge addresses the *utility* and *practicality* of the suggested design and the way of realizing it:

*Chg3: How can a hardware platform meet the first two challenges while also being practical and efficient?*

Specifically this challenge focuses on the support of features to result in a practical platform: the resulting solution should be user-friendly, taking into consideration flexibility and adaptability, and efficient in terms of performance and required resources which in extent will prove its utility.

Thus, this thesis proves its hypothesis by addressing its three research challenges. We break down the investigation of the hypothesis and the three sub-challenges into a set of objectives, listed in the next section. This is illustrated in Figure 1.2.

**Figure 1.2. Breakdown and organisation of thesis investigation. A set of objectives address three main research challenges which provide evidence to support the hypothesis**

## 1.5 Objectives

The main objectives for this research work can be identified as:

1. Review the work done on Natural Computation to date with a focus on hardware-based approaches.

2. Review and assess the work done on Systemic Computation (theory and implementations) to date.

3. Investigate the suitability of available hardware implementation platforms for SC by evaluating them in terms of their ability to support the natural properties of SC (*Chg1*), the implied SC architecture (*Chg2*), and practicality/efficiency (*Chg3*) and select the most appropriate.

4. Analyse the SC architectural features and create a prototype hardware implementation designed to support the SC architecture.

5. Create a complete and standalone practical SC programming platform with the ability to meet the three challenges.

6. Analyse and address the limitations of the hardware prototype by means of optimizations and enhancements taking into consideration the research challenges.

7. Evaluate the ability of the prototype SC platform to meet the research challenges by simulating natural models against alternative solutions.

## 1.6 Publications

The work presented in chapter 3 has been awarded the Best Paper Award in the international Annual Doctoral Workshop on Mathematical and Engineering Methods in Computer Science (MEMICS 2011) and was published in the Lecture Notes for Computer Science (LNCS) proceedings of the workshop. Overall this thesis resulted in the refereed publication of two international conference papers, two international journal papers, a book chapter and a research poster, listed below:

- C. Sakellariou and P. Bentley, “Introducing the FPGA-Based Hardware Architecture of Systemic Computation (HAoS)”, in *Mathematical and Engineering Methods in Computer Science*, Lecture Notes in Computer Science (LNCS) vol. 7119, Z. Kotásek, J. Bouda, I. Cerná, L. Sekanina, T. Vojnar, and D. Antoš, Eds. Springer Berlin / Heidelberg, 2012, pp. 179–190.

- C. Sakellariou and P. Bentley, “Describing the FPGA-Based Hardware Architecture of Systemic Computation (HAoS)”, *Journal of Computing And Informatics*, vol. 31, no. 3, pp. 485–505, 2012.

- C. Sakellariou and P. Bentley, “Extending the Hardware Architecture of Systemic Computation to a Complete Programming Platform”, in *IEEE International Conference on Evolvable Systems (ICES 2013) - IEEE Symposium Series on Computational Intelligence (SSCI 2013)*, Singapore, April 2013.

- C. Sakellariou and P. Bentley, “Demonstrating the performance, flexibility and programmability of the Hardware Architecture of Systemic Computation modelling cancer growth”, submitted to *International Journal of Bio-Inspired Computation, Special Issue on Bio-inspired Hardware*, 2013.

- C. Sakellariou and P. Bentley, “Computing Nature at the Intersection with Chemistry: Innovative Architectures”, Book Chapter to appear in *Genesis Engines: Computation and Chemistry in the Quest for Life's Origins*, Springer, 2013.

- C. Sakellariou and P. Bentley, “Building a Bio-Inspired Computer: The Hardware Architecture of Systemic Computation (HAoS)”, in *Frontiers of Natural Computing Workshop*, York, 2012.

## 1.7 Thesis Organization

The thesis comprises six chapters, four lists (including list of figures, tables, listings and algorithms), an extensive reference list and eight appendices. Chapter 2 reviews the literature on the field of Natural Computation, critically focusing on hardware-based approaches, and describes the SC theory, as it was introduced by Bentley [24]. It illustrates how SC can perform computation and presents the three prior SC implementations: Original SC Implementation, High-level SC Implementation and the GPU SC Implementation. Furthermore, it identifies the most appropriate SC hardware implementation platform among the various hardware-based approaches to Natural Computation. Chapter 3 introduces the first FPGA-based Hardware Architecture of Systemic computation (HAoS), discusses the functionality of its structural elements, justifies the design decisions which result in this prototype design, outlines the applied optimizations and details a programming example. It also gives implementation statistics of the suggested design on the intended FPGA development board and explains the verification methodology used to confirm its functionality. Chapter 4 investigates suitable approaches for the implementation of the communication interface between HAoS and the CPU, revisits parts of the design providing enhancements taking into consideration performance, I/O efficiency, user-friendliness and programmability. The HAoS base design is combined with an embedded soft processor to provide a standalone platform while a methodology for HAoS models development is suggested. Chapter 5 verifies and evaluates the functionality of the platform by illustrating how HAoS can be used to simulate three natural models of increasing complexity: a genetic algorithm optimization implementation solving the binary knapsack problem, a well-studied

biochemical process involving enzyme-based protein activation and a more challenging biological model simulating the effect of genetic anomalies and typical treatment approaches to cancer growth. The provided models are given as SC model development examples and the acquired results are compared against previous SC implementations and other conventional programming approaches. The time complexity of the HAoS schemata matching mechanism is also evaluated. Finally, chapter 6 summarizes the thesis, states its contributions, provides a critical evaluation and discusses future work.

# Chapter 2

## ***Background***

The notion of natural computation [35] resulted in significant advances on research in the field of natural computing [11], [23]. Adleman after successfully solving a seven-point Hamiltonian Path problem [36] using DNA sequences in 1994 [20], concludes his article:

*“Biology and computer science —life and computation— are related. I am confident that at their interface great discoveries await those who seek them.”*

*Leonard Adleman [20]*

This chapter discusses various methods attempting to approach natural computation, starting with a broad perspective and increasingly focussing on work more closely related to the topic of this thesis. Section 2.1 provides an overview of some of the major works in this area, and specifically in terms of software-based approaches and alternative paradigms. Section 2.2 gives a critical review of literature related to hardware approaches to natural computation. Conventional and unconventional ways and some related hardware designs are presented in this section and initially assessed regarding their compatibility with the Systemic Computation concept (a thorough analysis is given in the next chapter). Their potential to become the basis of, or inspire the features and requirements of a SC hardware implementation is discussed, as implied by the three research challenges (section 1.4 - supporting natural properties and the SC architecture and being able to facilitate an efficient and practical implementation). Section 2.3 elaborates on the SC paradigm as it was introduced by Bentley [24]. Finally, the three prior SC implementations are overviewed in section 2.4.

Part of the work presented in this chapter has been accepted for publication in [37]. Also, part of this work has been previously submitted for the degree of Master of Research as part of the Doctor of Engineering degree in UCL.

## 2.1 Approaches to Natural Computation

The Natural Computation research field is quite broad. Kari and Rozenberg, attempting to provide a complete review on the field in [23], separate its individual fields and computing paradigms in three groups using the role of nature as the differentiating factor: nature as inspiration, nature as implementation substrate and nature as computation. Especially for the last group, computation can both refer to quantitative algorithms and qualitative approaches that investigate natural processes taking into consideration communications and interactions [23].

**Table 2.1. Approaches to Natural Computation and alternative paradigms**

|                 | Software Approaches                             | Computational Paradigms              | Hardware Approaches          |                              |

|-----------------|-------------------------------------------------|--------------------------------------|------------------------------|------------------------------|

| Conventional    | Exception handling                              | Maths, physics & technology inspired | CGPs <sup>4</sup>            | Conventional                 |

|                 | Recovery blocks                                 |                                      | $\pi$ -calculus              | Multi-core / Multi-CPU       |

|                 | N-version programming                           |                                      | Asynchronous $\pi$ -calculus | Ubiquitous computing         |

|                 | Expert systems                                  |                                      | Stochastic $\pi$ -calculus   | High-availability cluster    |

|                 | Multi-agent systems                             |                                      | Ambient calculus             | Reaction-diffusion computing |

| Nature-inspired | Evolutionary algorithms                         | Nature-Inspired                      | Petri nets                   | Beowulf cluster              |

|                 | Artificial neural networks                      |                                      | Statecharts <sup>5</sup>     | GPU                          |

|                 | Swarm intelligence <sup>3</sup>                 |                                      | Bigraphs                     | Grid / Cloud computing       |

|                 | Artificial immune systems                       |                                      | Ons algebra                  | Pure Peer-to-peer            |

|                 | Artificial Life                                 |                                      | BioAmbient calculus          | Load-balancing cluster       |

|                 | Fractal Geometry (Cellular automata- L-systems) | Systemic computation                 | Membrane computing           |                              |

|                 |                                                 |                                      | Brane calculi                | Wireless Sensor Network      |

|                 |                                                 |                                      | CLS <sup>6</sup>             |                              |

|                 |                                                 |                                      | Bio-graphs                   | Collision-based computing    |

|                 |                                                 |                                      | Systemic computation         |                              |

|                 |                                                 |                                      |                              | Molecular (DNA) computing    |

|                 |                                                 |                                      |                              | Organic Computing            |

|                 |                                                 |                                      |                              | Bacterial Computing          |

|                 |                                                 |                                      |                              | Quantum computing            |

3 Ant colonies (ACO), Particle Swarm Optimization (PSO)

4 Constrained Generating Procedures

5 Just a flow graphical tool, not a computational paradigm

6 Calculus of Looping Sequences

The various approaches to date on natural computation, which for this work are separated into software-based methods, alternative paradigms to computation and hardware-based methods are illustrated in Table 2.1. An extensive literature review can be found in [11], [22], [23]. While the focus of this thesis lies on the hardware-based approaches (discussed in the next sections), a summary (informed by [22]) regarding the related software-based approaches and alternative concepts of Table 2.1 is provided below.

### 2.1.1 Software Approaches

Computation based on software approaches is quite common since they provide great flexibility and ease of use. Conventional software approaches, usually, do not take into consideration natural properties while conventional hardware approaches consider them by simulating them.

Conventional approaches address issues like reliability, robustness and autonomy. Exception handling [38] provides a mechanism of controlling the execution flow in case of foreseeable special cases. Recovery blocks [39] (the same programmer writes multiple versions of some parts of a program – blocks of code) and N-version programming [40] (multiple versions of a whole program are written by different programming teams) exploit code redundancy in order to overcome failures and minimize errors. Expert [41] and multi-agent [42] systems are used to perform autonomous tasks, the former by performing an analysis on a given problem and providing answers, the latter by diverging information and/or interests.

Computer scientists, inspired from nature, expanded on unconventional methods, adapting their programs to create or simulate natural properties like self-organization, self-adaptation and fault-tolerance. A Genetic Algorithm [12] (described in section 2.2.2 in the context of Evolvable systems) is a global heuristic search method and provides distributed, parallel, local and autonomous computation. Artificial Neural Networks [13] is a field inspired by biological neural mechanisms and shows distributed knowledge and self-organization. Swarm Intelligence [15] mimics concepts, inspired by insect civilizations, and based on their collective behaviour obtains self-organization and self-adaptation. Those properties are also observed in Artificial Immune Systems [14], which derive inspiration by (mostly) the adaptive and (less) the innate responses of biological immune systems, and Artificial Life [19] which is a field of study (and an associated form of art [43]) that employs a synthetic approach to the study and creation of life [11] (typical subjects of this study are termites, flocks, herds, evolution and artificial

chemistries). Fractal Geometry [11] deals with non-Euclidean objects of non-integer dimensions which are characterized by self-similarity and infinite detail. In a computational context, Fractal Geometry includes the fields of Cellular Automata [44], [45], systems that are discrete in both time and space, showing properties like self-replication and autonomy, and L-systems [18], a formalism to simulate the development of multi-cellular organisms [11] employing parallel rewriting systems (able to modify an existing word and generate new ones by applying various rewriting rules to its characters in parallel) [23].

### 2.1.2 Alternative Paradigms

In order to further understand and exploit natural processes, new paradigms of computation were developed, since conventional languages were not well suited for effectively simulating nature [22]. Inspiration was derived by conventional sciences (maths, physics and technology) and from nature.

CGPs [46] are finite state machines that can analyse complex systems by reducing them (breaking them down) in mechanisms and constraints of interactions.  $\pi$ -calculus [47] and its extensions (asynchronous  $\pi$ -calculus [48] and stochastic  $\pi$ -calculus [49]) are process calculi used or adapted for biological systems simulation. Ambient calculus [50] is also a process calculus which was developed to describe concurrent systems that include mobility. Petri nets [51] are a graphical tool, with a corresponding mathematical theory, that describes concurrent processes. Originally they were targeting chemical processes. Statecharts [52] are commonly used to describe the data and control flow of state machines in communication and, in general, hardware systems. Bigraphs [53] provide a well defined form of concurrent computations and a graphical notation, that exploits topographical and communication ideas, which is well suited for a number of the aforementioned calculi. Systemic computation can be seen as equivalent to bigraphs while the two paradigms share a similar graphical formalism. Ons algebra [54] is an algebraic formalism attempting to reach the foundations of physical rules development by using, in a metaphorical way, only two elementary particles, the particle of time and the particle of space.

BioAmbients Calculus [55] was designed to allow modelling of biological systems, having biological compartments as a central idea. Membrane computing [56] deals with distributed and parallel computing models of systems (P systems), that use the analogy of the organization of a cell being compartmented by membranes, creating this way hierarchies. Brane calculus [57] identifies the importance of the membrane itself and

gives it an active role on computation. The Calculus of Looping Sequences [58] and its variants is another formalism that allows the description of biological membranes, biomolecular systems and proteins interaction. Bio-graphs [59] were designed to model biological systems in a molecular level and include a corresponding graphical notation.

Since the hypothesis of this work focuses on a hardware-based implementation of SC, the reader is redirected to the work of Le Martelot [22] for a detailed description and a critical review which compares SC with the software approaches and the computational paradigms listed in Table 2.1. The various hardware approaches are described in the next sections.

## 2.2 Hardware-based Approaches to Natural Computation

While computer applications become ever more computationally demanding, the traditional Von Neumann [8] architecture, after serving humanity for more than half a century, appears inadequate [2], [60], [61] when extremely complex tasks are involved (brain function modelling, protein folding). Although refurbished designs keep consumers happy, hardware designers and researchers realised that alternative approaches should be followed for ground-breaking efficiency and performance improvement.

As explained in the previous sections, researchers found inspiration in nature. This is reflected in various hardware-based approaches. In this section, both conventional (subsection 2.2.1) and unconventional (subsection 2.2.2) hardware-based approaches are described<sup>7</sup>. In the context of this thesis, unconventional approaches do not conform to the conventional von Neumann architecture or use standard technologies (and are usually inspired by nature). Relevant silicon-based designs are discussed in subsection 2.2.3. Each paragraph is concluded with a short discussion on the compatibility of each approach to a practical SC implementation.

### 2.2.1 Conventional Hardware Approaches

Conventional hardware-based approaches to natural computation include multi-core chips, supercomputers, computer clusters, peer-to-peer networks and GPUs. They are usually based on some variation of the von Neumann architecture, except GPUs which fall in this category since they are widely used in consumer desktops and laptops, and are

---

<sup>7</sup> It is noted that because of different definitions for various technologies or for clarity reasons there is some overlap between the technologies and methods described in next sections.

attempts to provide more processing power using various design approaches explained below.

### **Chip Multi-Processors**

Chip Multi-Processor (CMP) [62] systems were the response of the semiconductor industry, to the consumer market, when around 2003 the clock frequency of uniprocessor systems reached the limits imposed by the physics of their underlying technology. CMPs take advantage of the limited parallelism that multiple processors provide, often being able to execute more than one instruction thread simultaneously each. The limitation of CMPs to provide natural computation is evident, as their sequential architecture is incompatible with any natural property (except maybe parallelism, but that is true only when they are compared with their predecessor uniprocessor architectures).

CMPs are based on the conventional von Neumann architecture [62]. They are based on the most widely used hardware implementation approach to computation, since their deterministic sequential processors are highly flexible and easily programmable. Their technology is more mature than any other. As such, there is a plethora of tools, specifically designed for them. However, their flexibility comes at the expense of performance, as their generic architecture cannot compete with custom designs, optimized for specific applications. The nature of their architecture makes them incompatible with almost any natural property (maybe except parallelism, since they provide limited support), therefore they are unsuitable for a SC implementation. As shown later in sections 2.4.1 and 2.4.2, CMPs were used for the first two SC implementations, revealing the inefficiency of such an approach, as these implementations could only simulate a systemic computer. Although the high-level SC implementation provided programming flexibility, performance limitations make it inadequate for modelling complex systems.

### **Supercomputers and Computer Clusters**

While CMPs are targeted to the consumers, supercomputers [63] are used for computationally super-demanding tasks, such as modelling climate change, nuclear reactions and molecular interactions [63]. They were introduced by Seymour Cray in the 1960s. Modern supercomputer designs often consist of a cluster of Multiple Instruction stream - Multiple Data stream (MIMD) multiprocessors, which have Single Instruction - Multiple Data (SIMD) processors as building elements. The SIMD processors execute the same instruction on different sets of data while the MIMD processors function asynchronously, enabling the underlying SIMD units to perform different operations on