# An Implantable Stimulator for Selective Stimulation of Nerves

$\mathbf{B}\mathbf{y}$

Martin Bryan Bugbee

A thesis submitted for the Degree Doctor of Philosophy in the University of London

University College London

(University of London)

Department of Medical Physics and Bioengineering

July 2000

ProQuest Number: U642158

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest U642158

Published by ProQuest LLC(2015). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code.

Microform Edition © ProQuest LLC.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### **ABSTRACT**

Acute experimentation performed at many centres over the last twenty years has shown techniques which allow small neurones to be stimulated without large, the reverse of the normal recruitment order usually encountered during electrical stimulation; one-way excitation of neurones; and excitation of only a region of a nerve. These techniques should improve neural prosthesis by, for example: avoiding pain during stimulation and requiring electrode sites and therefore fewer incisions.

To enable chronic clinical experiments of these advanced methods, there is a need for a specialised chronically-implantable stimulator, which can control either dipolar, tripolar or pentapolar nerve cuff electrodes. This thesis is concerned with the design and development of such a stimulator and, in particular, a fully customised analogue integrated circuit that converts incoming digital words into corresponding stimulation currents.

A binary word is transmitted to the implant, which defines the current waveform parameters for the electrodes. This word is loaded into a shift register at the input. Part of the word is presented to a digital to analogue converter, to specify stimulation amplitude, and a pulse generator, which generates either a quasi-trapezoidal, or a square shaped stimulation waveforms. Four novel low offset linear transconductors provide the stimulation currents that are switched to the desired outputs. The charge balancing of the stimulation waveform is realised by a very long time-constant switched capacitor integrator.

The major difficulties in the design of the analogue full custom IC proved to be the linear transconductor stages and the integrator. Results for the test ICs are presented and the design of a complete stimulator system is described.

# TABLE OF CONTENTS

| CHAPTI | ER 1. INTRODUCTION                               | 17 |

|--------|--------------------------------------------------|----|

| 1.1 H  | ISTORY OF IMPLANTED STIMULATORS FOR FES          | 17 |

| 1.2 S  | HORTCOMINGS OF EXISTING STIMULATORS              | 19 |

| 1.2.1  | Electrode Siting                                 | 19 |

| 1.2.2  | Inverse Recruitment of Nerve Fibres              | 19 |

| 1.2.3  | Pain and Unwanted Reflex Activity                | 20 |

| 1.3 T  | HE LARSI STIMULATOR                              | 21 |

| 1.3.1  | Handshaking                                      | 22 |

| 1.3.2  | Use of Blocking Capacitors to avoid Electrolysis | 22 |

| 1.3.3  | Coupling Measurement/Compensation                | 23 |

| 1.3.4  | Minimised Power Losses                           | 24 |

| 1.4 N  | TEW STIMULATORS FOR FES                          | 24 |

| 1.5 T  | HIS THESIS                                       | 24 |

| СНАРТН | ER 2. SELECTIVE STIMULATION                      | 26 |

| 2.5 In | NTRODUCTION                                      | 26 |

| 2.5.1  | Neurophysiology                                  |    |

| 2.5.2  | Peripheral Nerves                                |    |

| 2.5.3  | The Cell                                         |    |

| 2.5.4  | Action Potential Generation                      |    |

| 2.5.4  |                                                  |    |

| 2.5.4  | -                                                |    |

| 2.5.5  | Action Potential Propagation                     | 30 |

| 2.5.5  | 5.1 Myelination                                  | 31 |

| 2.5.6  | Stimulation of Nerve                             | 32 |

| 2.5.6  | 5.1 Electrode Cuff Designs                       | 32 |

| 2.5.6  | 5.2 How Electrodes Cause Action Potentials       | 33 |

| 2.5.7  | Electrical Stimulation of Nerve                  | 33 |

| 2.5.7  | r                                                |    |

| 2.5.7  |                                                  |    |

|        | ELECTIVE STIMULATION METHODS                     |    |

| 2.6.1  | Selective Stimulation by Fibre Size              |    |

| 2.6.1  | .1 Summary                                       | 40 |

| 2.6   | 5.2     | Selective Stimulation by Fibre Position                          | 43  |

|-------|---------|------------------------------------------------------------------|-----|

|       | 2.6.2.1 | Summary                                                          |     |

| CHAPT | ΓER     | 3. SELECTIVE STIMULATOR SPECIFICATION                            | 51  |

| 3.1   | GE      | NERAL REQUIREMENTS OF AN IMPLANTED SELECTIVE STIMULATOR          | 51  |

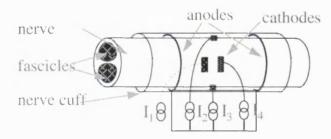

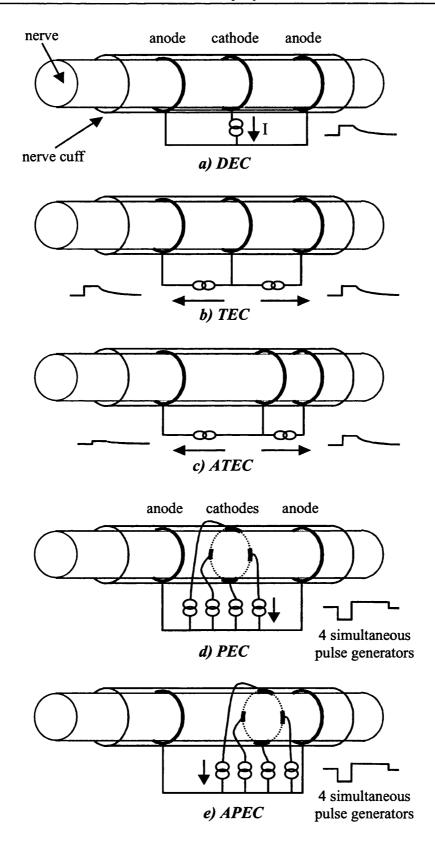

| 3.2   | NE      | RVE CUFF TYPES FOR THE SELECTIVE STIMULATOR                      | 51  |

| 3.2   | 2.1     | Nerve Cuffs for Selective Stimulation by Position                | 51  |

| 3.2   | 2.2     | Nerve cuffs for Selective Stimulation by Fibre Size              | 53  |

| 3.3   | Nu      | MBER OF NERVE CUFFS                                              | 55  |

| 3.4   | STI     | MULATION WAVEFORM SPECIFICATION                                  | 57  |

| 3.4   | 1.1     | Pulse Amplitudes                                                 | 57  |

| 3     | 3.4.1.1 | Asymmetric Dipolar Electrode Cuff (ADEC)                         | 57  |

| _     | 3.4.1.2 |                                                                  |     |

| 3.4   |         | Output Current Ratios                                            |     |

| 3.4   |         | Pulse Durations                                                  |     |

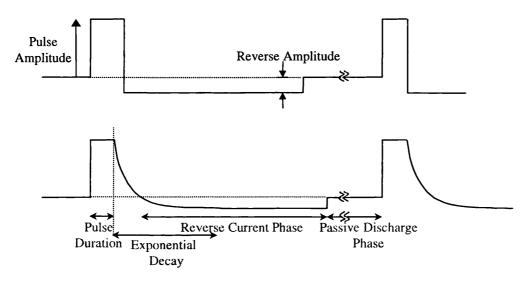

| 3.4   |         | Reverse Current Phase                                            |     |

| 3.4   |         | Passive Discharging                                              |     |

| 3.4   |         | Exponential Decay Time Constant                                  |     |

| 3.4   |         | Output Current Resolution (in Tripolar Operation)                |     |

| 3.4   |         | Stimulation with Multiple Cuffs (The need for a Switching Array) |     |

| 3.5   |         | WER CONSUMPTION                                                  |     |

| 3.6   |         | OICE OF BLOCKING CAPACITOR VALUE                                 |     |

| 3.7   |         |                                                                  | 74  |

| 3.8   |         | STEM DESIGN                                                      |     |

| 3.9   |         | PLANT SPECIFICATION                                              |     |

| 3.10  |         | DESIGN OF THE STIMULATOR CORE                                    |     |

| 3.11  | S       | UMMARY                                                           | 80  |

| СНАР  | TEF     | R 4. DEVELOPMENT OF ANALOGUE BLOCKS FOR                          | THE |

| STIM  | ULA     | TOR CORE                                                         | 81  |

| 4.1   | Int     | RODUCTION                                                        | 81  |

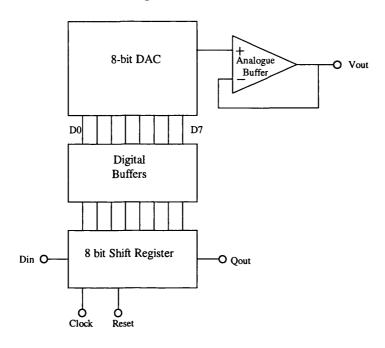

| 4.2   |         | GITAL TO ANALOGUE CONVERTER (DAC)                                |     |

| 4.2   |         | Specification                                                    |     |

| 4.2   |         | Implementation                                                   |     |

|       |         | Results                                                          | 84  |

| 4           | 1.2.4   | Summary                                           | 85  |

|-------------|---------|---------------------------------------------------|-----|

| 4.3         | PUL     | SE GENERATOR                                      | 86  |

| 4           | 4.3.1   | Introduction                                      | 86  |

| 4           | 1.3.2   | Specification                                     | 86  |

| 4           | 4.3.3   | Implementation                                    | 87  |

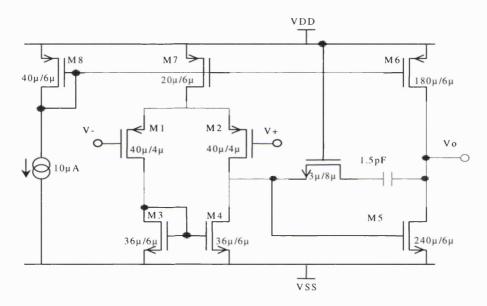

|             | 4.3.3.1 | Amplifier Implementation                          |     |

| 4           | 1.3.4   | Simulation Results                                |     |

| 4           | 4.3.5   | Experimental Results                              | 93  |

|             | 4.3.5.1 | Pulse Amplitude and Duration                      | 93  |

|             | 4.3.5.2 | Exponential Tail                                  | 94  |

|             | 4.3.5.3 | Rise Time                                         | 95  |

|             | 4.3.5.4 | Reverse Phase                                     |     |

|             | 4.3.5.5 | Pulse Generator Amplifier                         |     |

| 4           | 4.3.6   | Discussion                                        | 97  |

| <b>4</b> .4 | AT      | TENUATORS                                         | 99  |

| 4           | 4.4.1   | Introduction                                      | 99  |

| 4           | 1.4.2   | Specification                                     | 99  |

| 4           | 1.4.3   | Implementation                                    | 100 |

| 4           | 1.4.4   | Simulation Results                                | 104 |

| 4           | 4.4.5   | Experimental Results                              | 104 |

| 2           | 1.4.6   | Discussion                                        | 106 |

| 4.5         | 5 LIN   | EAR TRANSCONDUCTOR (VOLTAGE TO CURRENT CONVERTER) | 108 |

| 4           | 4.5.1   | Introduction                                      | 108 |

| 4           | 4.5.2   | Specification                                     | 108 |

| 4           | 4.5.3   | Background                                        |     |

| 4           | 4.5.4   | Implementation: Single Sided Transconductor       |     |

| 4           | 4.5.5   | Analysis of Single Sided Transconductor           |     |

|             | 4.5.5.1 | Offset                                            |     |

|             | 4.5.5.2 | Linearity                                         |     |

| 4           | 4.5.6   | Implementation: Differential Transconductor       | 117 |

|             | 4.5.6.1 | Connection of Outputs to Electrodes               | 117 |

|             | 4.5.6.2 | Common-Mode Feedback                              |     |

| 2           | 4.5.7   | Simulation Results                                | 119 |

| 4           | 4.5.8   | Initial Experimental Results                      | 122 |

|             | 4.5.8.1 | Single Sided Operation                            | 122 |

|             | 4.5.8.2 | Differential Operation                            | 124 |

| 4           | 4.5.9   | Analysis of Transconductor Instability            | 125 |

| 4.5.       | 10    | Experimental Results (using Modified Common-Mode Feedback) | 127 |

|------------|-------|------------------------------------------------------------|-----|

| 4.5.       | 11    | Conclusions                                                | 129 |

| 4.6        | Swi   | TCHING AND DISCHARGE ARRAYS                                | 131 |

| 4.6.       | 1     | Switching Array                                            | 131 |

| 4.6        | 5.1.1 | Specification                                              |     |

|            | 5.1.2 | Implementation.                                            |     |

| 4.6        | 5.1.3 | Results                                                    |     |

| 4.6.       | 2     | Discharge Array                                            | 135 |

| 4.6        | 5.2.1 | Implementation                                             | 135 |

| 4.6        | 5.2.2 | Experimental Results                                       | 136 |

| 4.6        | 3     | Summary                                                    | 136 |

| 4.7        | Lon   | IG TIME CONSTANT INTEGRATOR                                | 137 |

| 4.7.       | 1     | Introduction                                               | 137 |

| 4.7.       | 2     | Specification                                              | 137 |

| 4.7        | 3     | Implementation                                             | 138 |

| 4.7        | 7.3.1 | Background                                                 | 138 |

| 4.7        | 7.3.2 | Switched Capacitor Integrator's                            | 140 |

| 4.7        | 7.3.3 | Integrator Development                                     | 142 |

| 4.7        | 7.3.4 | Improvement in Observed Switching Transients               | 147 |

| 4.7        | 7.3.5 | Integrator Layout                                          |     |

| 4.7        | 7.3.6 | T-Cell Integrator Amplifier                                | 147 |

| 4.7.       | 4     | Simulation Results                                         | 149 |

| 4.7        | 7.4.1 | Simulation of the Integrator Circuit.                      | 149 |

| 4.7        | 7.4.2 | Simulation of DC Output Offset Voltage                     | 151 |

| 4.7        | 5     | Experimental results                                       | 152 |

| 4.7        | 7.5.1 | Integrator Time Constant                                   | 152 |

| 4.7        | 7.5.2 | Integrator Transient Behavior                              | 153 |

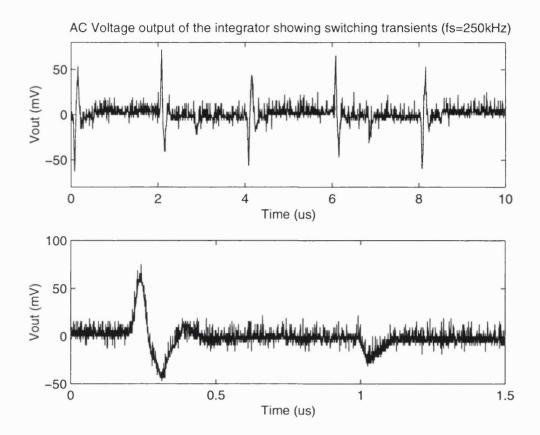

| 4.7        | 7.5.3 | Integrator Switching Transients                            | 153 |

| 4.7        | 7.5.4 | Integrator Output Offset Voltage                           | 154 |

| 4.7        | 7.5.5 | Experimental Results from the Integrator Amplifier         | 155 |

| 4.7.       | 6     | Conclusions                                                | 156 |

| 4.8        | Pov   | VER CONSUMPTION OF THE IMPLANT CIRCUITS                    | 158 |

| 4.9        | SIM   | ULATION RESULTS FOR A COMPLETE STIMULATOR                  | 158 |

| 4.10       | E     | XPERIMENTAL RESULTS FOR THE STIMULATOR                     | 159 |

| 4.11       | E     | FFECT OF OFFSET                                            | 161 |

| 4.11       | S     | UMMARY                                                     | 161 |

| ינו א דווי | ren   | 5 ADDITIONS AND FITTIDE WODE                               | 163 |

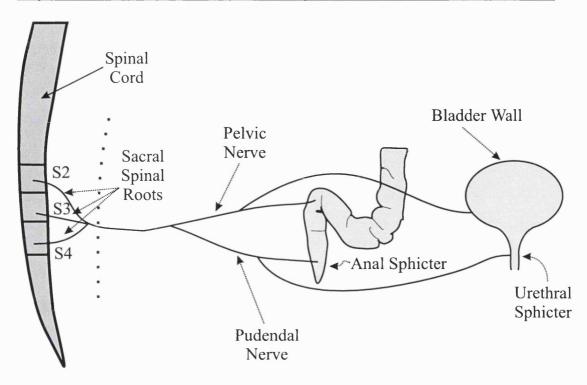

| 5.1.1 Improved Implantable Bladder and Bowel Stimulator       163         5.1.1.2 Und-directional stimulation       165         5.1.1.3 Neuromodulation       165         5.1.1.2 Implantable Foot Drop Stimulator       165         5.2. A Complete Selective Stimulator       166         5.2.1 Overview of a Complete Stimulator       168         5.2.2 Implant Data       169         5.2.3 Stimulation Unit       171         5.2.4 DCU       171         5.2.4.1 Data Decoding       172         5.2.4.2 Control Signals       173         5.2.4.3 Handshaking       173         5.2.5 Implant Schematic       174         5.3 SUMMARY       174         CHAPTER 6. SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A.1.1. PARITHIONING OF THE INTEGRATED CIRCUITS       181         A.1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A.1.3. PCB DESIGN AND LAYOUT       187         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER CIRCUIT       195         A2.1. GENERAL LAYOUT       195         A2.2. CAPACITOR LAYOUT <td< th=""><th>5.1 Pro</th><th>DPOSED APPLICATIONS</th><th>163</th></td<> | 5.1 Pro   | DPOSED APPLICATIONS                               | 163 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------|-----|

| 5.1.1.2       Uni-directional stimulation       165         5.1.2       Implantable Foot Drop Stimulator       165         5.2.2       A COMPLETE SELECTIVE STIMULATOR SYSTEM       166         5.2.1       Overview of a Complete Stimulator       168         5.2.2       Implant Data       169         5.2.3       Stimulation Unit       171         5.2.4       DCU       171         5.2.4.1       Data Decoding       172         5.2.4.2       Control Signals       173         5.2.4.3       Handshaking       173         5.2.4.4       Power Supply Monitoring       173         5.2.5       Implant Schematic       174         5.3       SUMMARY       174         CHAPTER 6.       SUMMARY       174         CHAPTER 6.       SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARITTIONING OF THE INTEGRATED CIRCUITS       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER         CIRCUIT       <                                                                                                                         | 5.1.1     | Improved Implantable Bladder and Bowel Stimulator | 163 |

| 5.1.1.3       Neuromodulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.1.1.1   |                                                   |     |

| 5.1.2 Implantable Foot Drop Stimulator       165         5.2 A COMPLETE SELECTIVE STIMULATOR SYSTEM       166         5.2.1 Overview of a Complete Stimulator       168         5.2.2 Implant Data       169         5.2.3 Stimulation Unit       171         5.2.4 DCU       171         5.2.4.1 Data Decoding       172         5.2.4.2 Control Signals       173         5.2.4.3 Handshaking       173         5.2.4 Power Supply Monitoring       173         5.2.5 Implant Schematic       174         5.3 SUMMARY       174         CHAPTER 6. SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARITIONING OF THE INTEGRATED CIRCUITS       181         A1.3. PCB DESIGN AND LAYOUT       186         A1.3. I SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. USE OF DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS                                                                                                                                       | 5.1.1.2   | Uni-directional stimulation                       | 165 |

| 5.2. A COMPLETE SELECTIVE STIMULATOR SYSTEM       166         5.2.1 Overview of a Complete Stimulator       168         5.2.2 Implant Data       169         5.2.3 Stimulation Unit       171         5.2.4 DCU       171         5.2.4.1 Data Decoding       172         5.2.4.2 Control Signals       173         5.2.4.3 Handshaking       173         5.2.5 Implant Schematic       174         5.3 SUMMARY       174         CHAPTER 6. SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARITIONING OF THE INTEGRATED CIRCUITS       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A1.3. PCB DESIGN AND LAYOUT       187         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. USE OF DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                 | 5.1.1.3   | Neuromodulation                                   | 165 |

| 5.2.1       Overview of a Complete Stimulator.       168         5.2.2       Implant Data.       169         5.2.3       Stimulation Unit.       171         5.2.4       DCU.       171         5.2.4.1       Data Decoding.       172         5.2.4.2       Control Signals.       173         5.2.4.3       Handshaking.       173         5.2.4.4       Power Supply Monitoring.       173         5.2.5       Implant Schematic.       174         5.3       SUMMARY.       174         CHAPTER 6.       SUMMARY.       174         CHAPTER 6.       SUMMARY.       174         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS.       181         A1.1. PARITTIONING OF THE INTEGRATED CIRCUITS.       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS.       186         A1.3. I SSTIM1.       187         A1.3.1 SSTIM1.       187         A1.3.2 SSTIM2.       190         A1.3.3 SSTIM3.       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER         CIRCUIT.       195         A2.1. GENERAL LAYOUT.       196         A2.3. Use of DUMMY TRANSISTORS.       197         A2.4. OUTPUT BUFFER. <td< td=""><td>5.1.2</td><td>Implantable Foot Drop Stimulator</td><td>165</td></td<>                                                      | 5.1.2     | Implantable Foot Drop Stimulator                  | 165 |

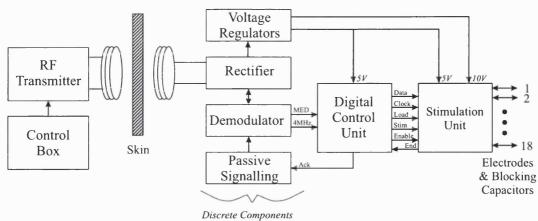

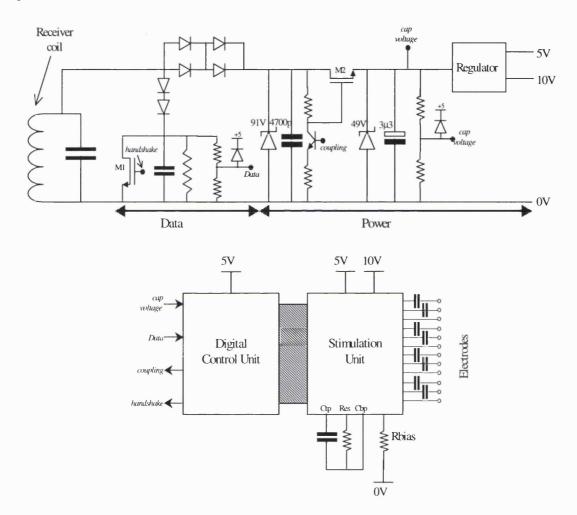

| 5.2.2 Implant Data       169         5.2.3 Stimulation Unit.       171         5.2.4 DCU       171         5.2.4.1 Data Decoding       172         5.2.4.2 Control Signals       173         5.2.4.3 Handshaking       173         5.2.5 Implant Schematic       174         5.3 SUMMARY       174         CHAPTER 6. SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARTITIONING OF THE INTEGRATED CIRCUITS       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A1.3. PCB DESIGN AND LAYOUT       187         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER CIRCUIT       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. USE OF DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                               | 5.2 A C   | COMPLETE SELECTIVE STIMULATOR SYSTEM              | 166 |

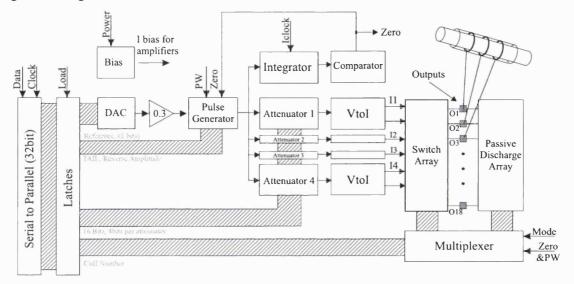

| 5.2.3 Stimulation Unit.       171         5.2.4 DCU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2.1     | Overview of a Complete Stimulator                 | 168 |

| 5.2.4       DCU       171         5.2.4.1       Data Decoding       172         5.2.4.2       Control Signals       173         5.2.4.3       Handshaking       173         5.2.4.4       Power Supply Monitoring       173         5.2.5       Implant Schematic       174         5.3       SUMMARY       174         CHAPTER 6.       SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARTITIONING OF THE INTEGRATED CIRCUITS       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A1.3. PCB DESIGN AND LAYOUT       187         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER CIRCUIT       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. Use of DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                            | 5.2.2     | Implant Data                                      | 169 |

| 5.2.4.1 Data Decoding       172         5.2.4.2 Control Signals       173         5.2.4.3 Handshaking       173         5.2.4.4 Power Supply Monitoring       173         5.2.5 Implant Schematic       174         5.3 SUMMARY       174         CHAPTER 6. SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARTITIONING OF THE INTEGRATED CIRCUITS       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A1.3. PCB DESIGN AND LAYOUT       187         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER CIRCUIT       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. USE OF DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                        | 5.2.3     | Stimulation Unit                                  | 171 |

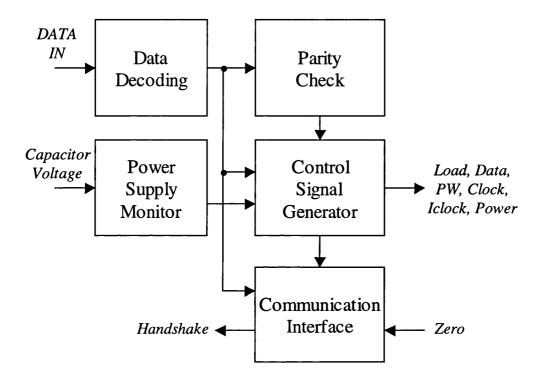

| 5.2.4.2       Control Signals       173         5.2.4.3       Handshaking       173         5.2.4.4       Power Supply Monitoring       173         5.2.5.5       Implant Schematic       174         5.3       SUMMARY       174         CHAPTER 6.       SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARTITIONING OF THE INTEGRATED CIRCUITS       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A1.3. PCB DESIGN AND LAYOUT       187         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. USE OF DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                  | 5.2.4     | DCU                                               | 171 |

| 52.4.3       Handshaking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.2.4.1   | Data Decoding                                     | 172 |

| 5.2.44       Power Supply Monitoring       173         5.2.5       Implant Schematic       174         5.3       SUMMARY       176         CHAPTER 6.       SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARTITIONING OF THE INTEGRATED CIRCUITS       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A1.3. PCB DESIGN AND LAYOUT       187         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER CIRCUIT       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. Use of DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.2.4.2   | Control Signals                                   | 173 |

| 5.2.5       Implant Schematic       174         5.3       SUMMARY       176         CHAPTER 6. SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARTITIONING OF THE INTEGRATED CIRCUITS       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A1.3. PCB DESIGN AND LAYOUT       187         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER CIRCUIT       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. Use of Dummy Transistors       197         A2.4. Output Buffer       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.2.4.3   | Handshaking                                       | 173 |

| 5.3       SUMMARY       174         CHAPTER 6.       SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARTITIONING OF THE INTEGRATED CIRCUITS       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A1.3. PCB DESIGN AND LAYOUT       187         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER CIRCUIT       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. USE OF DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2.4.4   |                                                   |     |

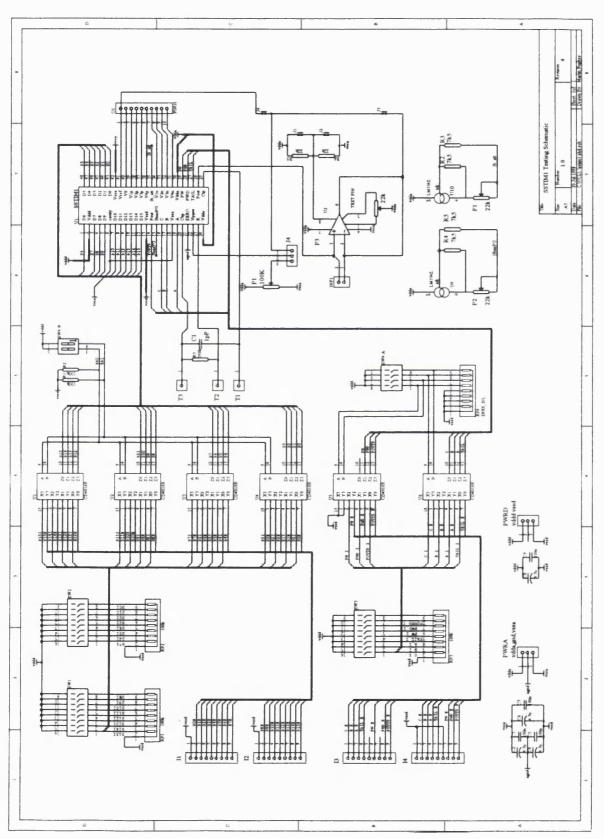

| CHAPTER 6. SUMMARY       176         APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS       181         A1.1. PARTITIONING OF THE INTEGRATED CIRCUITS       181         A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS       186         A1.3. PCB DESIGN AND LAYOUT       187         A1.3.1 SSTIM1       187         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER CIRCUIT       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. Use of Dummy Transistors       197         A2.4. Output Buffer       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2.5     | Implant Schematic                                 | 174 |

| APPENDIX 1. TESTING OF THE INTEGRATED CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.3 Sui   | MMARY                                             | 174 |

| A1.1. PARTITIONING OF THE INTEGRATED CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | СНАРТЕГ   | R 6. SUMMARY                                      | 176 |

| A1.2. OPERATIONAL AMPLIFIER TESTING CONFIGURATIONS 186 A1.3. PCB DESIGN AND LAYOUT 187 A1.3.1 SSTIM1 187 A1.3.2 SSTIM2 190 A1.3.3 SSTIM3 192  APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER CIRCUIT 195 A2.1. GENERAL LAYOUT 195 A2.1. CAPACITOR LAYOUT 196 A2.3. USE OF DUMMY TRANSISTORS 197 A2.4. OUTPUT BUFFER 197 APPENDIX 3. TRANSISTOR EQUATIONS 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | APPENDI   | X 1. TESTING OF THE INTEGRATED CIRCUITS           | 181 |

| A1.3. PCB DESIGN AND LAYOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A1.1. PAI | RTTTIONING OF THE INTEGRATED CIRCUITS             | 181 |

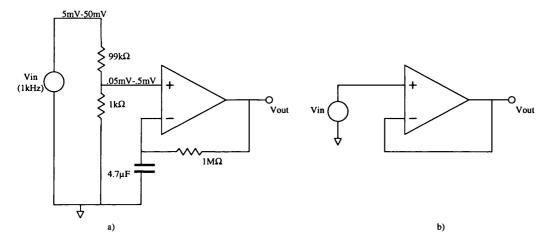

| A1.3.1 SSTIM1       190         A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. Use of Dummy Transistors       197         A2.4. Output Buffer       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A1.2. Op  | ERATIONAL AMPLIFIER TESTING CONFIGURATIONS        | 186 |

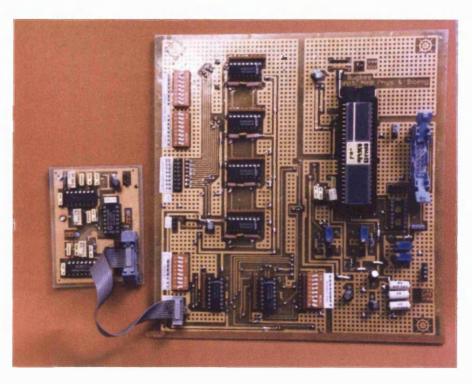

| A1.3.2 SSTIM2       190         A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. USE OF DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A1.3. PC  | B design and layout                               | 187 |

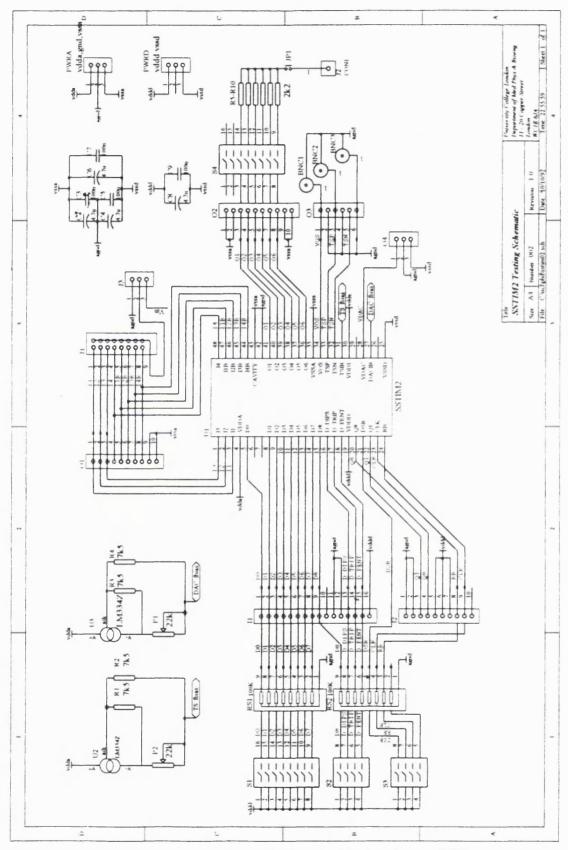

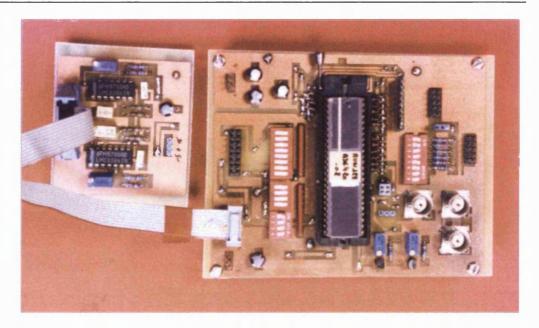

| A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER       195         CIRCUIT       195         A2.1. GENERAL LAYOUT       196         A2.3. USE OF DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A1.3.1    | SSTIM1                                            | 187 |

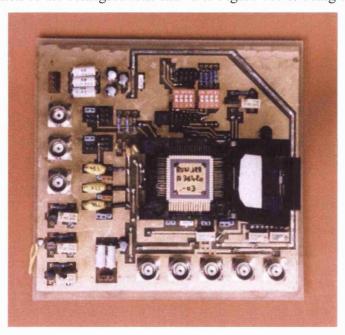

| A1.3.3 SSTIM3       192         APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER       195         CIRCUIT       195         A2.1. GENERAL LAYOUT       196         A2.3. USE OF DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A1.3.2    | SSTIM2                                            | 190 |

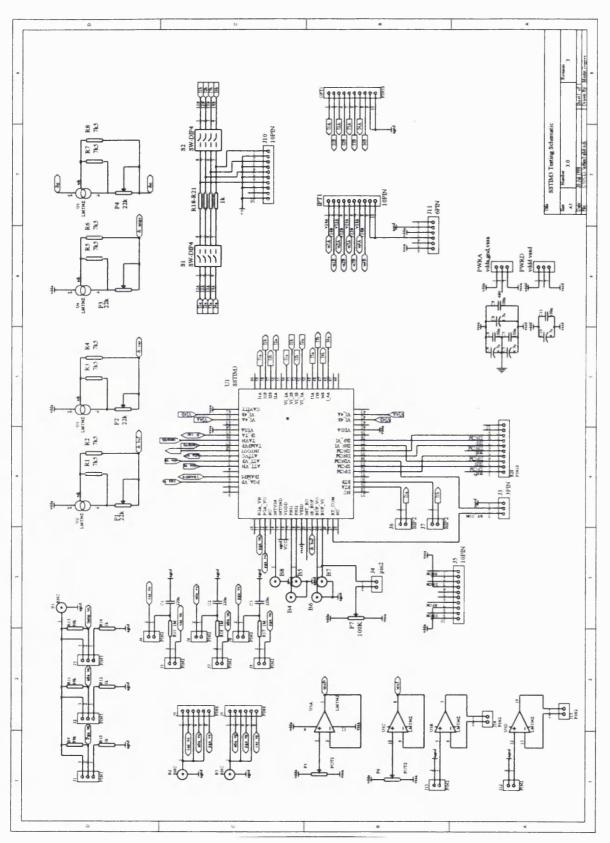

| APPENDIX 2. INTEGRATOR LAYOUT PRECAUTIONS AND BUFFER CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                                                   |     |

| CIRCUIT       195         A2.1. GENERAL LAYOUT       195         A2.1. CAPACITOR LAYOUT       196         A2.3. USE OF DUMMY TRANSISTORS       197         A2.4. OUTPUT BUFFER       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                                   |     |

| A2.1. GENERAL LAYOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                                   |     |

| A2.1. CAPACITOR LAYOUT       196         A2.3. Use of Dummy Transistors       197         A2.4. Output Buffer       197         APPENDIX 3. TRANSISTOR EQUATIONS       200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CIRCUIT.  | •••••••••••••••••••••••••••••••••••••••           | 195 |

| A2.3. USE OF DUMMY TRANSISTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A2.1. GE  | NERAL LAYOUT                                      | 195 |

| A2.4. OUTPUT BUFFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A2.1. CA  | PACITOR LAYOUT                                    | 196 |

| A2.4. OUTPUT BUFFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A2.3. Usi | E OF DUMMY TRANSISTORS                            | 197 |

| APPENDIX 3. TRANSISTOR EQUATIONS200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                                   |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                                                   |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                                                   |     |

|                                  | 8   |

|----------------------------------|-----|

| A3.1.1 n-channel MOSFET          | 200 |

| A3.1.2 p-channel MOSFET          | 200 |

| A3.2. SMALL SIGNAL MOSFET MODELS | 201 |

| REFERENCES                       | 202 |

# TABLE OF FIGURES

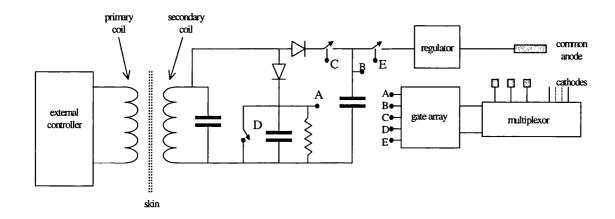

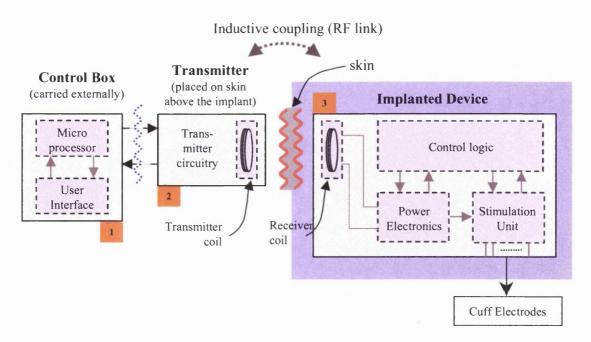

| FIGURE 1. OVERVIEW OF THE LARSI STIMULATOR                                    | 21 |

|-------------------------------------------------------------------------------|----|

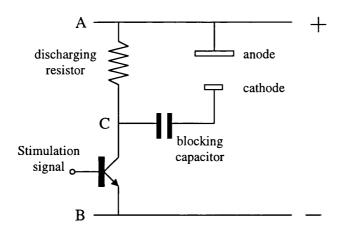

| FIGURE 2. OUTPUT STAGE OF THE LARSI STIMULATOR                                | 23 |

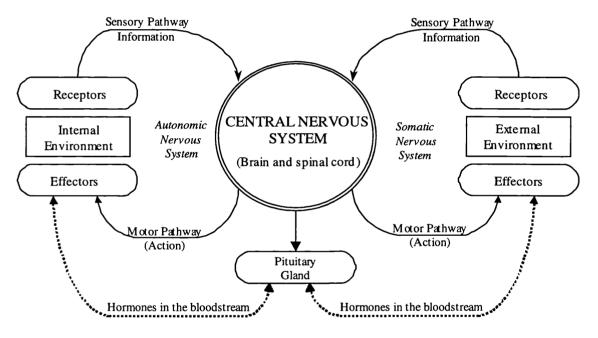

| FIGURE 3. THE NERVOUS SYSTEM                                                  | 26 |

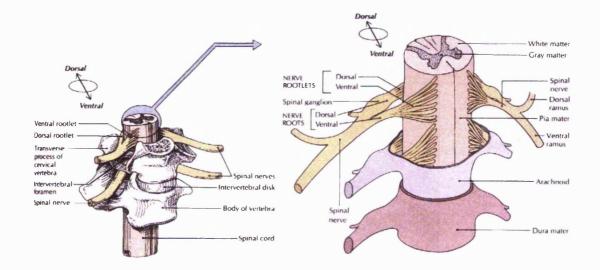

| FIGURE 4. CROSS SECTION SPINAL SHOWING DORSAL AND VENTRAL ROOT LOCATION       | NS |

| (MODIFIED FROM[31]).                                                          | 27 |

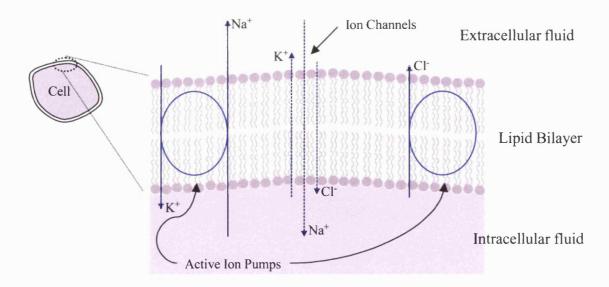

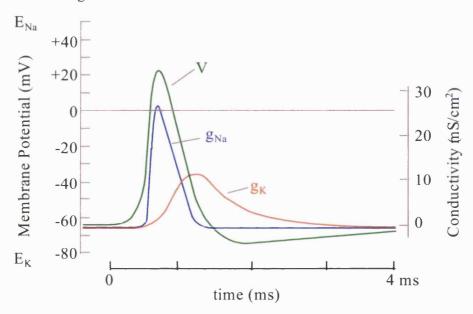

| FIGURE 5. CELL MEMBRANE: STRUCTURE OF THE LIPID BILAYER                       | 28 |

| FIGURE 6. ION TRANSPORT ACROSS A RESTING CELL MEMBRANE.                       | 29 |

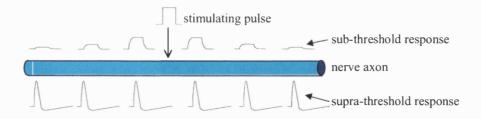

| FIGURE 7. PROPAGATION OF SUB-THRESHOLD AND SUPRA-THRESHOLD STIMULATION        | ΟN |

| ALONG AN AXON.                                                                | 30 |

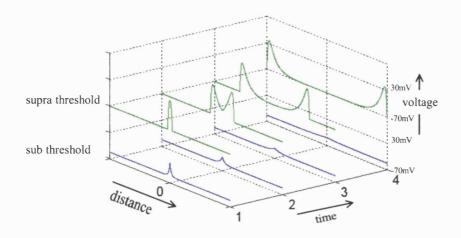

| FIGURE 8. COMPARISON OF THE EFFECT OF A SUB-THRESHOLD STIMULUS (NO.           | N- |

| PROPAGATING) AND A SUPRA-THRESHOLD STIMULUS (PROPAGATING)                     | 30 |

| FIGURE 9. SUPRA AND SUB THRESHOLD STIMULUS PROPAGATION AT VARIOUS TIMES AFT   | ER |

| STIMULATION.                                                                  | 31 |

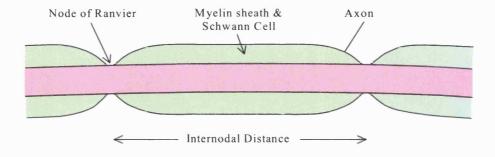

| FIGURE 10. MYELINATED NERVE FIBRE                                             | 31 |

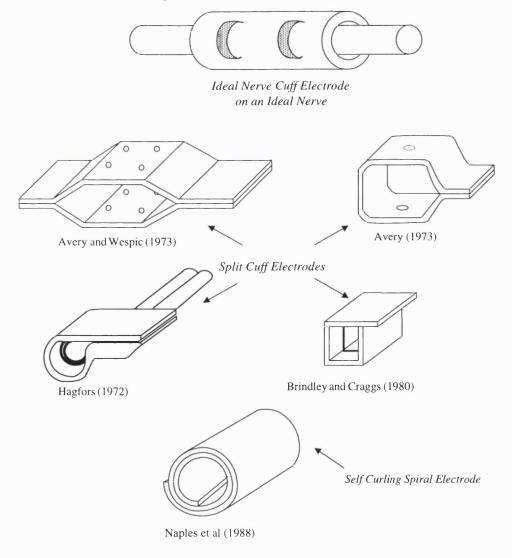

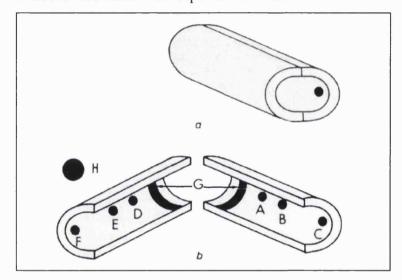

| FIGURE 11. HISTORICAL ELECTRODE CUFF DESIGNS                                  | 32 |

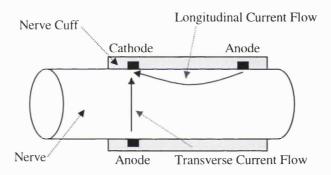

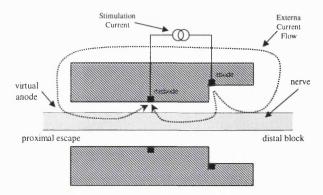

| FIGURE 12. LONGITUDINAL AND TRANSVERSE CURRENT FLOW INSIDE A NERVE CUFF       | 33 |

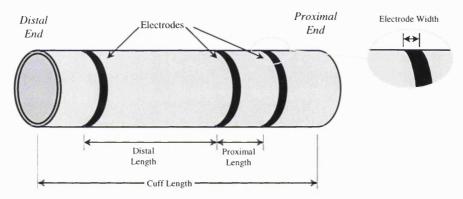

| FIGURE 13. IDEAL TRIPOLAR CUFF ELECTRODE DEFINITIONS                          | 36 |

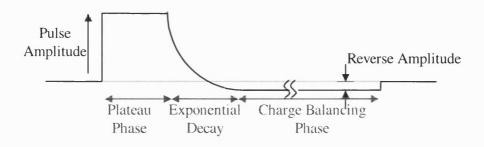

| FIGURE 14. "QUASI-TRAPEZOIDAL" BLOCKING WAVEFORM DEFINITIONS                  | 36 |

| FIGURE 15. SWEENEY AND MORTIMER ATEC                                          | 38 |

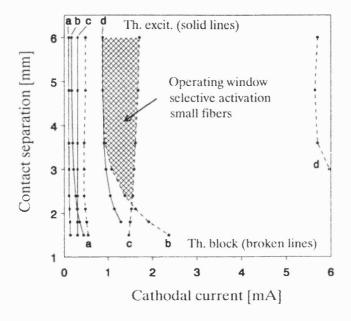

| FIGURE 16. EXCITATION AND BLOCKING THRESHOLDS FOR A) 4UM NERVE FIBRE LOCATION | ED |

| ON BORDER OF NERVE, B) 4UM FIBRE ON AXIS, C) 12UM FIBRE ON BORDER, D) 12U     | JM |

| FIBRE ON AXIS, REPRODUCED FROM [114]                                          | 39 |

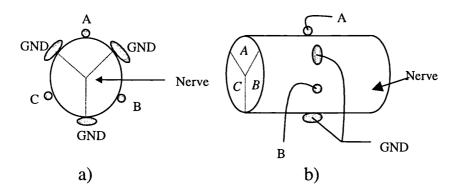

| FIGURE 17. MULTIPOLAR NERVE CUFF USED BY PETROFSKY. A) CROSS SECTION B) SII   | DE |

| VIEW SHOWING ELECTRODE CONNECTIONS                                            | 43 |

| FIGURE 18. McNeal and Bowman split cuff electrode, (a).closed cuff, (b).vie   | EW |

| INSIDE OF THE SPLIT CUFF                                                      | 44 |

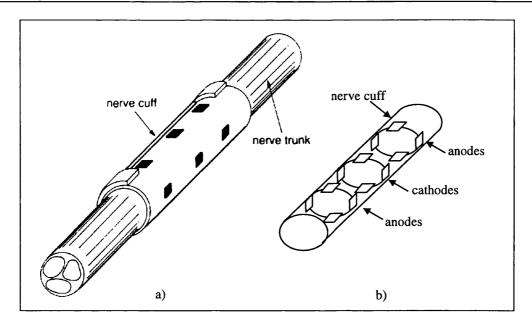

| FIGURE 19. VERAART 12 ELECTRODE NERVE CUFF                                    | 46 |

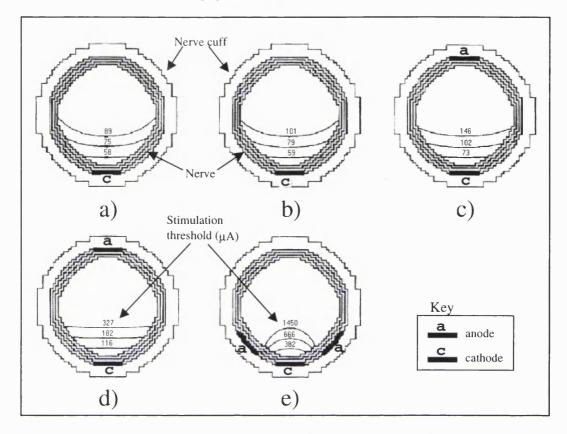

| Figure 20. Recruitment regions inside a nerve cuff for $15\mu m$ fibres [41]. | A) |

| MONOPOLAR, B) LONGITUDINAL TRIPOLAR, C) LONGITUDINAL TRIPOLAR WITH 40         | 1% |

| STEERING, D) TRANSVERSE BIPOLAR E) TRANSVERSE TRIPOLAR                        | 48 |

| FIGURE 21. PENTAPOLAR ELECTRODE CUFF                                          | 52 |

| FIGURE 22. PHOTOGRAPH OF AN ASYMMETRIC PENTAPOLAR ELECTRODE CUFF              | 52 |

| FIGURE 23. NERVE CUFFS FOR USE WITH THE SELECTIVE STIMULATOR                  | 54 |

| FIGURE 24. ANODAL BLOCKING WAVEFORM DEFINITIONS (ANODAL CURRENT WAVEFORMS         |

|-----------------------------------------------------------------------------------|

| shown)57                                                                          |

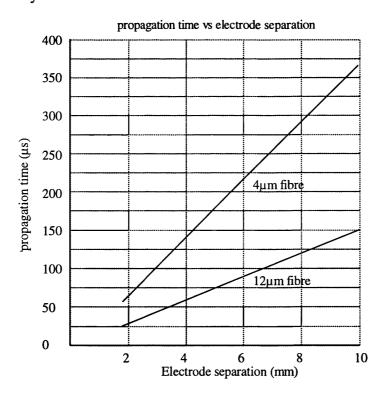

| FIGURE 25. SEPARATION OF THE CATHODE FROM THE BLOCKING ANODE VS PROPAGATION       |

| for 4µm and 12µm fibres60                                                         |

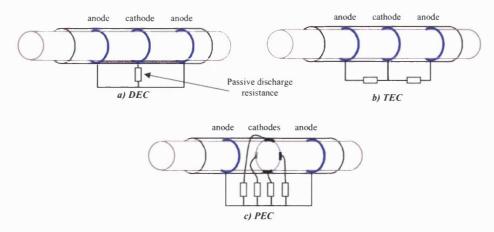

| FIGURE 26. CONFIGURATION OF PASSIVE DISCHARGING RESISTORS FOR THE DEC, TEC        |

| AND PEC62                                                                         |

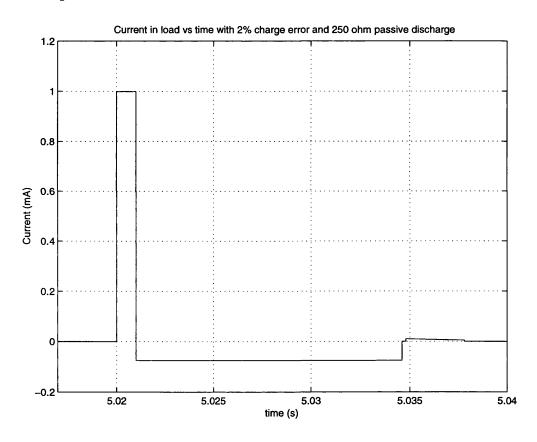

| FIGURE 27. CURRENT IN 1KOHM RESISTIVE LOAD VS. TIME AFTER 5 SECONDS               |

| STIMULATION63                                                                     |

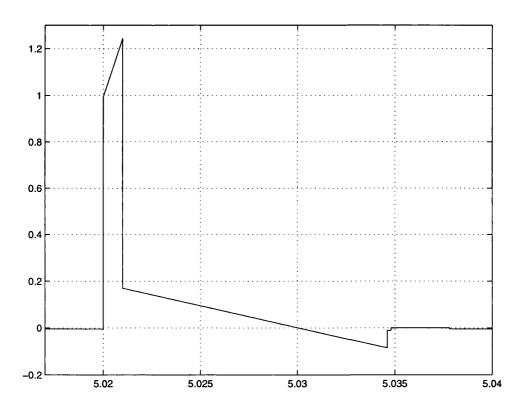

| FIGURE 28. VOLTAGE ACROSS BLOCKING CAPACITOR AND 1KOHM LOAD VS. TIME AFTER 5      |

| SECONDS STIMULATION64                                                             |

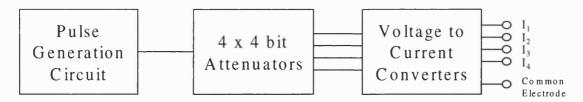

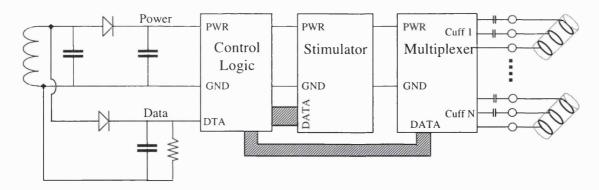

| FIGURE 29. SYSTEM TO GENERATE MULTIPLE OUTPUT WAVEFORMS                           |

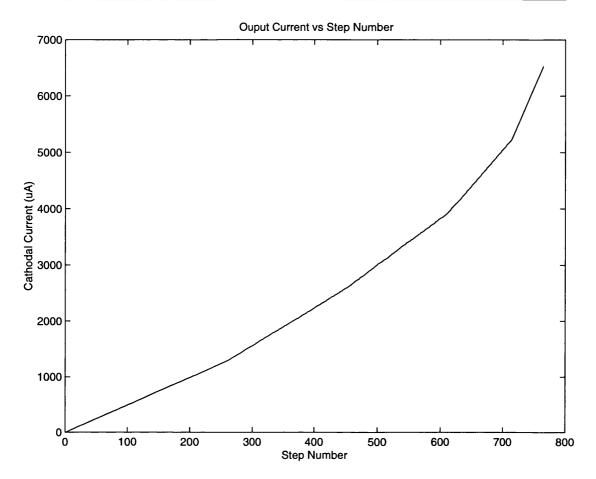

| Figure 30. Output current curve in tripolar operation at $3:1$ current ratio $67$ |

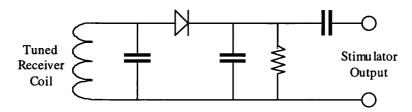

| FIGURE 31. SIMPLE ISOLATED STIMULATOR                                             |

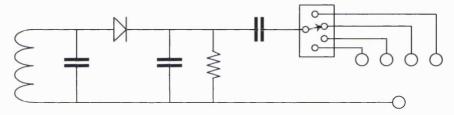

| FIGURE 32. FOUR CHANNEL ISOLATED STIMULATOR                                       |

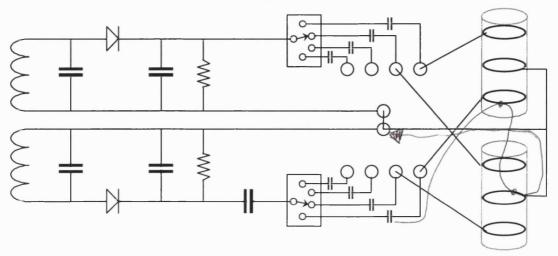

| FIGURE 33. FOUR CHANNEL ISOLATED TRIPOLAR STIMULATOR                              |

| FIGURE 34. FIGURE 34. MULTIPLE CHANNEL MULTIPLEXED TRIPOLAR STIMULATOR70          |

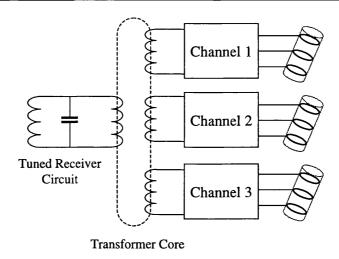

| Figure 35. Multiple channel tripolar stimulator using transformers71              |

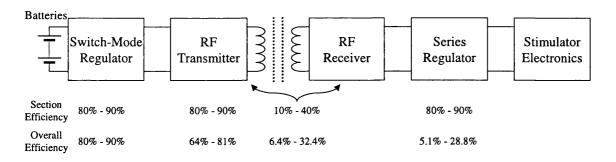

| FIGURE 36. ESTIMATED INDUCTIVELY COUPLE STIMULATOR EFFICIENCY72                   |

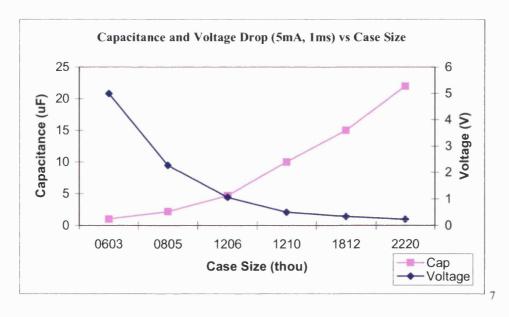

| FIGURE 37. CAPACITANCE AND VOLTAGE VS CASE SIZE FOR BLOCKING CAPACITORS73         |

| FIGURE 38. SELECTIVE STIMULATOR SYSTEM OVERVIEW                                   |

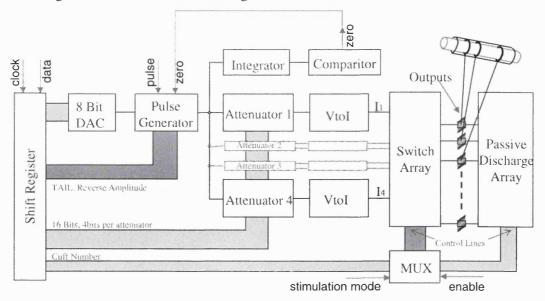

| FIGURE 39. PROPOSED ORGANISATION OF THE STIMULATION UNIT                          |

| FIGURE 40. OVERVIEW OF THE DAC                                                    |

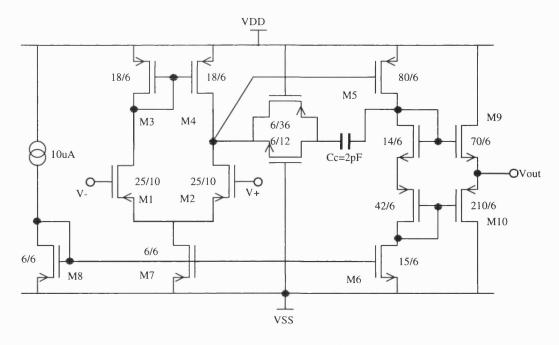

| FIGURE 41. TWO-STAGE DAC OP-AMP (TRANSISTOR SIZES SHOWN)                          |

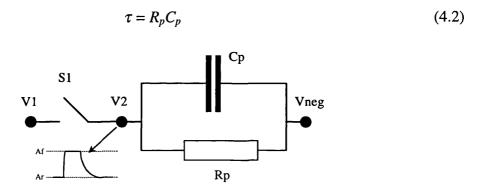

| FIGURE 42. SIMPLE RC CIRCUIT TO PRODUCE A QUASI-TRAPEZOIDAL WAVEFORM 87           |

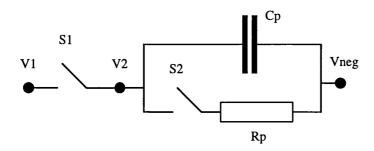

| FIGURE 43. RC CIRCUIT TO REMOVE INACCURACIES IN PLATEAU VOLTAGE                   |

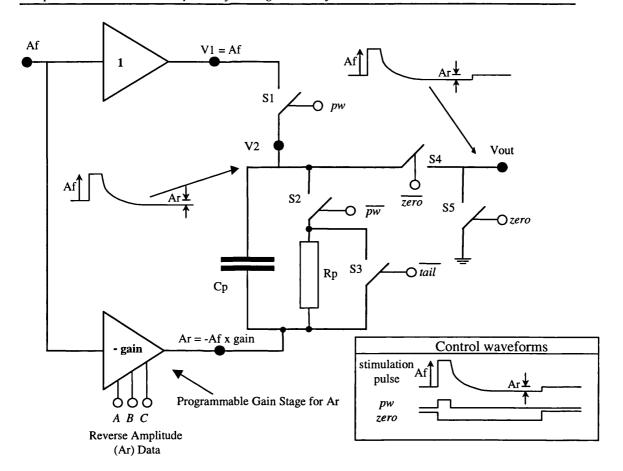

| FIGURE 44. PULSE GENERATOR IMPLEMENTION                                           |

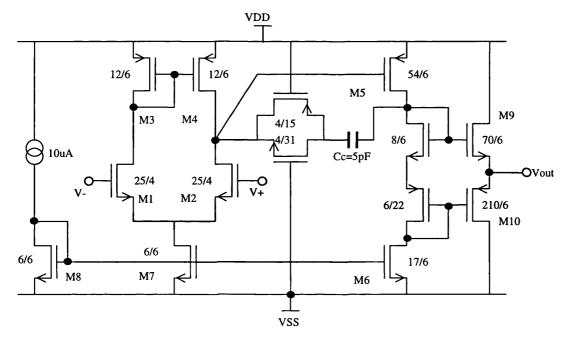

| FIGURE 45. AMPLIFIER FOR THE PULSE GENERATOR                                      |

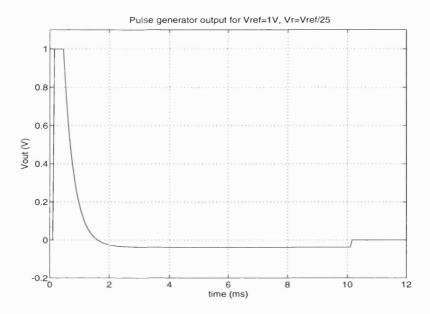

| FIGURE 46. SIMULATED RESPONSE OF THE PULSE GENERATOR FOR A 1V PULSE PLATEAU       |

| AND A REVERSE PHASE OF 1/2692                                                     |

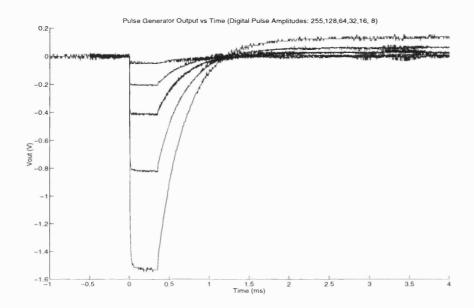

| FIGURE 47. PULSE GENERATOR OUTPUT FOR VARIOUS PULSE AMPLITUDES93                  |

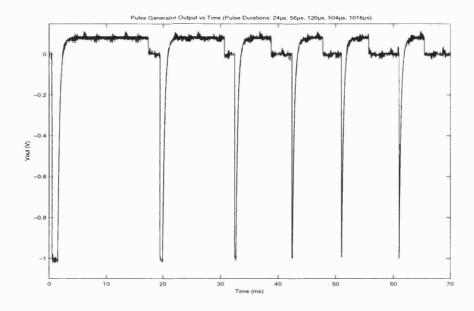

| FIGURE 48. PULSE GENERATOR OUTPUT FOR VARIOUS PULSE DURATIONS                     |

| FIGURE 49. PULSE GENERATOR OUTPUT SHOWING VARIOUS TIME CONSTANTS94                |

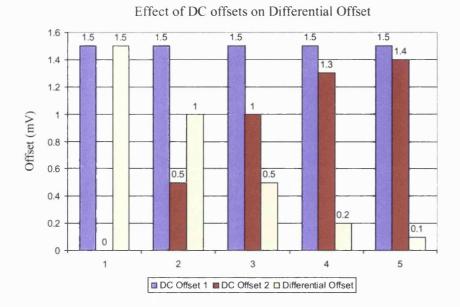

| FIGURE 50. EFFECT OF OFFSET MATCHING ON THE DIFFERENTIAL OFFSET (5 EXAMPLES       |

| SHOWN)                                                                            |

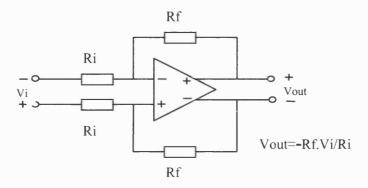

| FIGURE 51. FULLY DIFFERENTIAL ATTENUATOR                                   | 100      |

|----------------------------------------------------------------------------|----------|

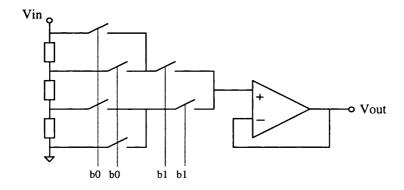

| FIGURE 52. 2-BIT VOLTAGE SCALING DAC ACTING AS AN ATTENUATOR               | 101      |

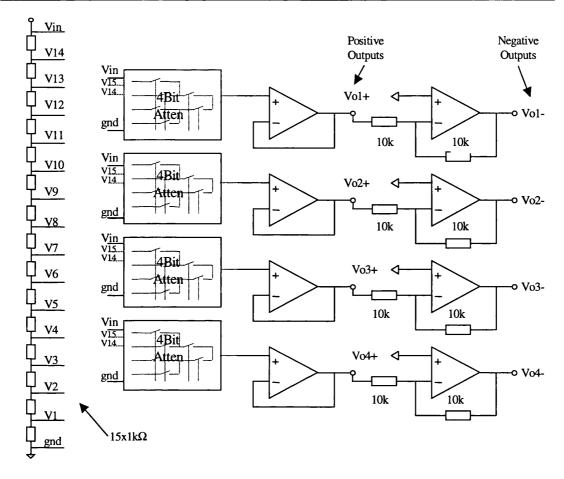

| FIGURE 53. 4-CHANNEL, 4-BIT SINGLE- SIDED TO FULLY-DIFFERENTIAL ATTENUATOR | R 102    |

| FIGURE 54. ATTENUATOR AMPLIFIER                                            | 103      |

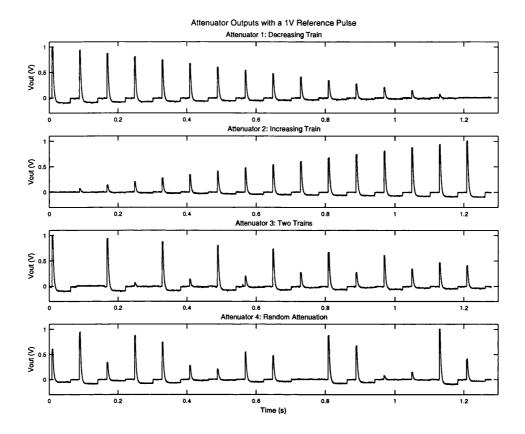

| FIGURE 55. ATTENUATOR NEGATIVE OUTPUTS FOR A FIXED REFERENCE SIGNAL FROM   | ом тне   |

| PULSE GENERATOR (VARIOUS GAINS)                                            | 105      |

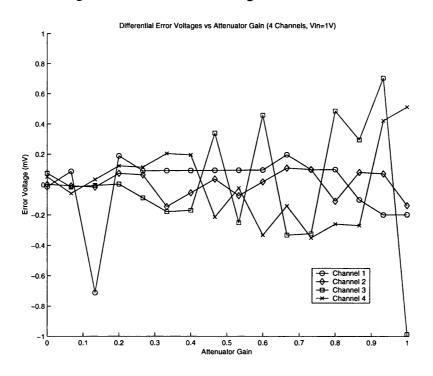

| Figure 56. Differential offset error voltage vs attenuator gain (4 cha     | NNELS,   |

| $V_{IN} = 1V, IC 4)$                                                       | 105      |

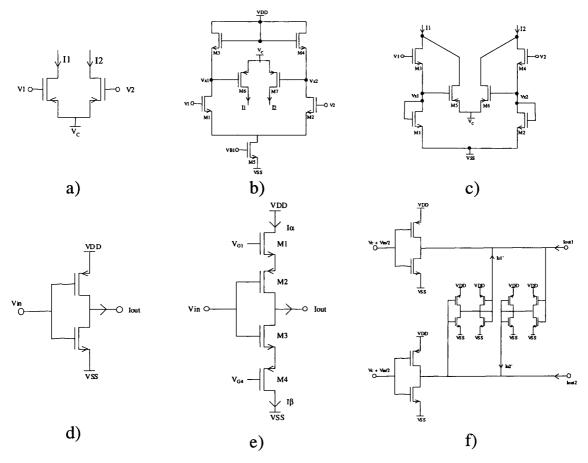

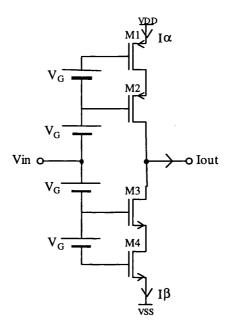

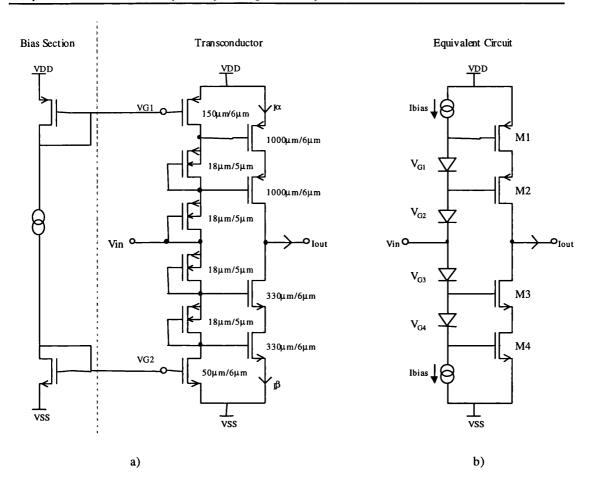

| FIGURE 57. TRANSCONDUCTOR CIRCUITS                                         | 111      |

| FIGURE 58. PROPOSED LINEAR TRANSCONDUCTOR                                  | 112      |

| FIGURE 59. A) PROPOSED LINEAR TRANSCONDUCTOR B) EQUIVALENT CIRCUIT         | 113      |

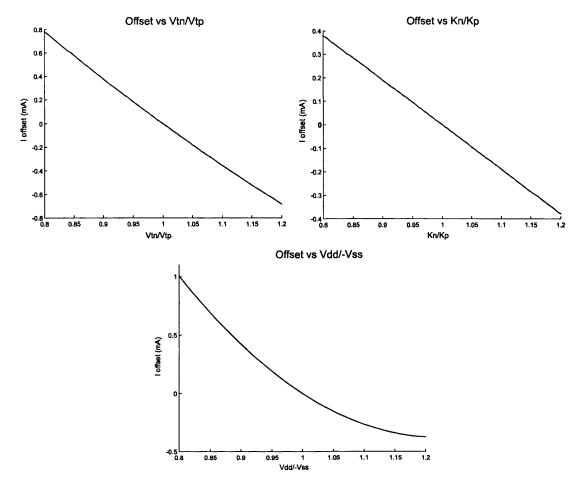

| FIGURE 60. EFFECT OF MISMATCHES ON TRANSCONDUCTOR DC OFFSET                | 116      |

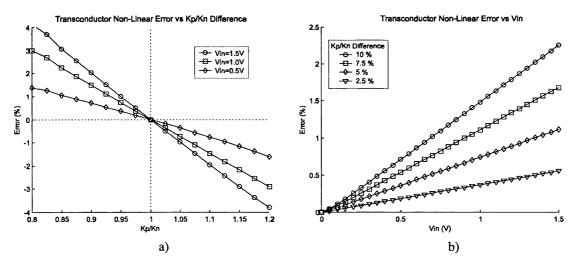

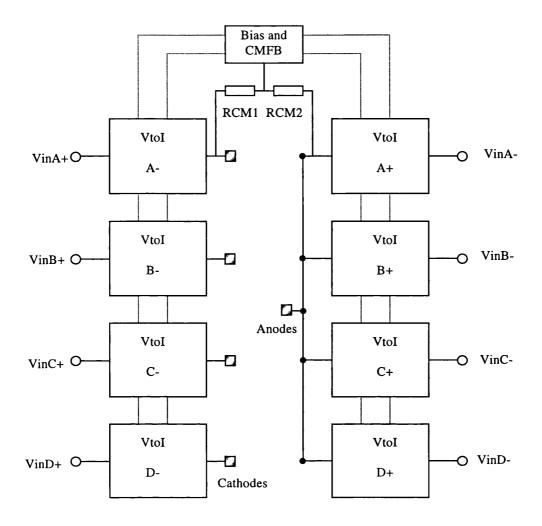

| FIGURE 61. TRANSCONDUCTOR NON-LINEARITY VS A) KP/KN, B) VIN                | 117      |

| FIGURE 62. CONNECTION OF THE TRANSCONDUCTORS AND COMMON MODE FEEDB.        | ACK TO   |

| THE PENTAPOLAR ELECTRODE                                                   | 118      |

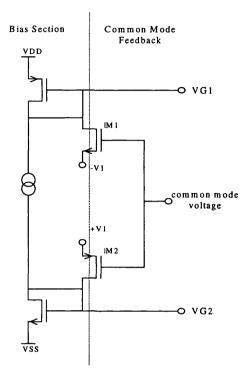

| FIGURE 63. COMMON MODE FEEDBACK FOR THE DIFFERENTIAL TRANSCONDUCTOR        | 119      |

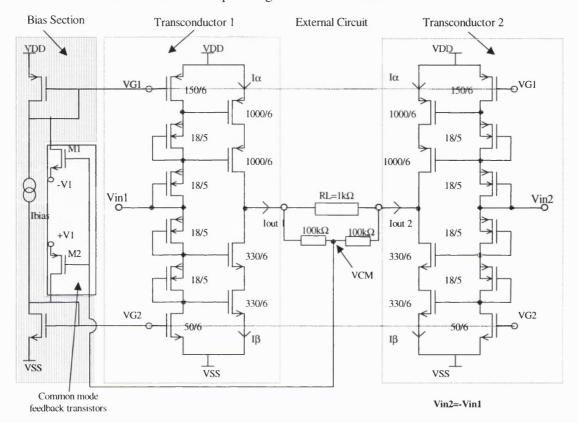

| FIGURE 64. DIFFERENTIALLY CONNECTED TRANSCONDUCTOR                         | 120      |

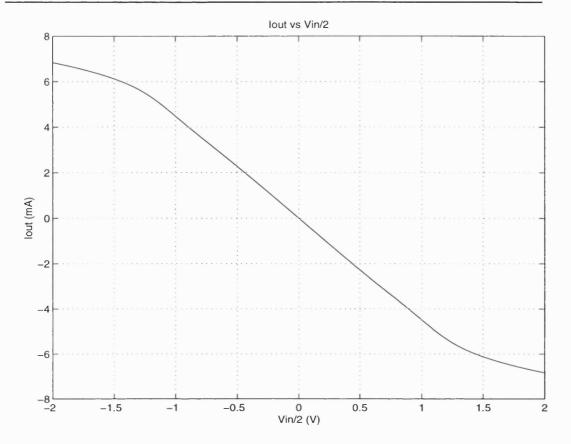

| FIGURE 65. SIMULATED TRANSCONDUCTOR OUTPUT CURRENT IN DIPOLAR OPE          | RATION   |

| $(RLOAD=1K\Omega)$                                                         | 121      |

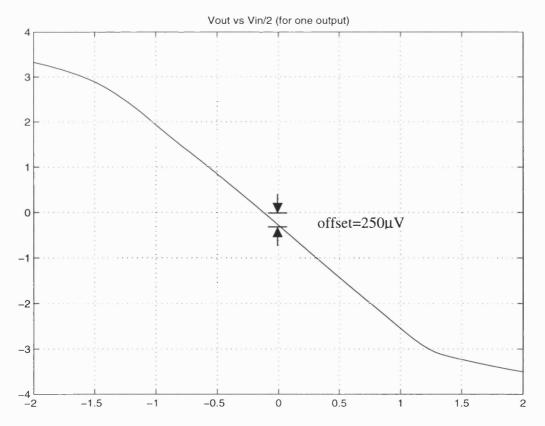

| FIGURE 66. SIMULATED TRANSCONDUCTOR OUTPUT VOLTAGE IN DIPOLAR OPERATION    | on . 121 |

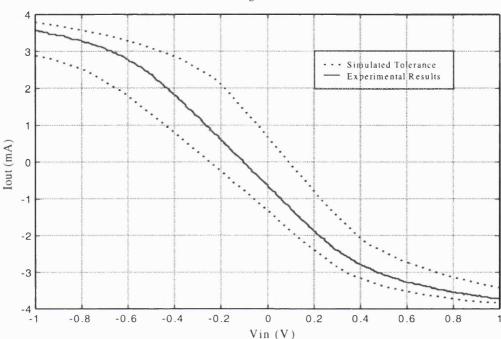

| FIGURE 67. IOUT VS VIN TRANSCONDUCTOR IN SINGLE SIDED MODE                 | 123      |

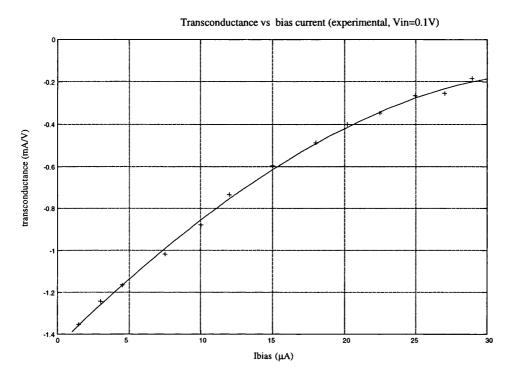

| FIGURE 68 . CHANGE IN TRANSCONDUCTANCE VS BIAS CURRENT                     | 124      |

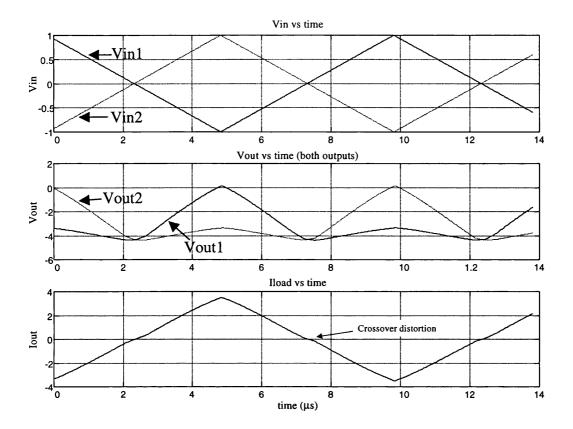

| FIGURE 69 . DIFFERENTIALLY CONNECTED TRANSCONDUCTOR WITH NO CMFB           | 125      |

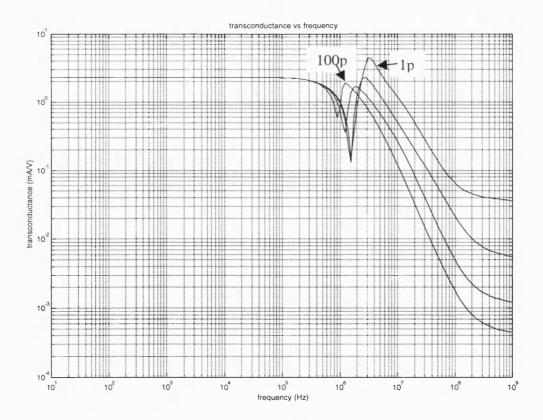

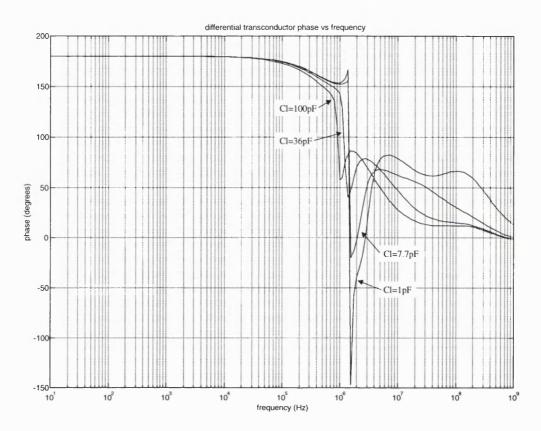

| FIGURE 70. TRANSCONDUCTANCE VS FREQUENCY WITH A DC INPUT VOLTAGE OF        |          |

| FIGURE 71. PHASE VS FREQUENCY WITH A DC INPUT VOLTAGE OF 300MV (IN         |          |

| OUTPUT PHASE SHIFT)                                                        | 127      |

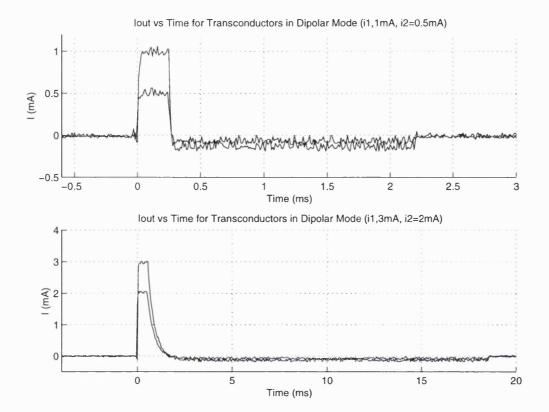

| FIGURE 72. TRANSIENT RESPONSE OF THE TRANSCONDUCTOR OPERATING IN D         | IPOLAR   |

| MODE (TWO ACTIVE CURRENTS), FOR 0.5MA, 1MA, 2MA, 3MA STIMULATION           | PULSES   |

| WITH TWO DIFFERING WAVEFORM SHAPES GENERATED USING THE PULSE GENE          | ERATOR   |

| CIRCUIT (R <sub>LOAD</sub> =1KOHM)                                         | 128      |

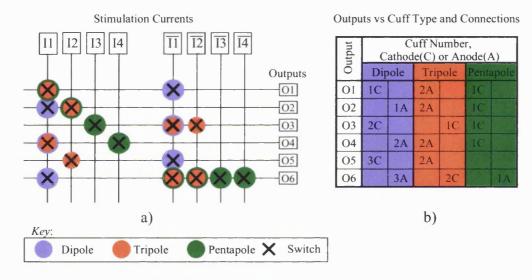

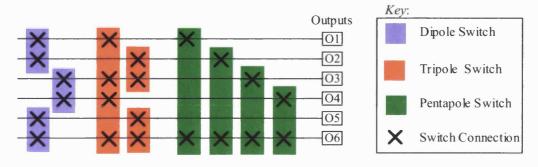

| FIGURE 73. SWITCH-ARRAY ORGANISATION SHOWING OUTPUT SWITCH CONNECTIONS FOR    |

|-------------------------------------------------------------------------------|

| A) CURRENT SOURCES AND CUFF TYPES AND B) ELECTRODE CONNECTIONS AND CUFF       |

| TYPES                                                                         |

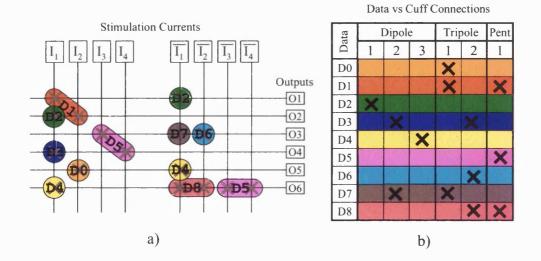

| FIGURE 74. SWITCH-ARRAY DATA ORGANISATION SHOWING OUTPUT SWITCH CONNECTIONS   |

| FOR A) CURRENT SOURCES AND CUFF TYPES AND B) DATA CONNECTIONS AND CUFF        |

| TYPES                                                                         |

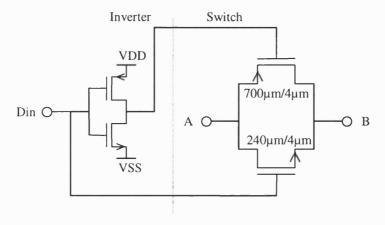

| FIGURE 75. CMOS SWITCH WITH INVERTER                                          |

| FIGURE 76. DISCHARGE-ARRAY ORGANISATION SHOWING SWITCH CONNECTIONS TO         |

| OUTPUTS                                                                       |

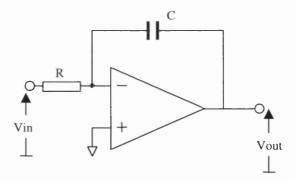

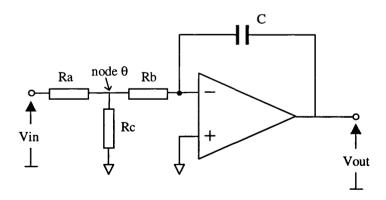

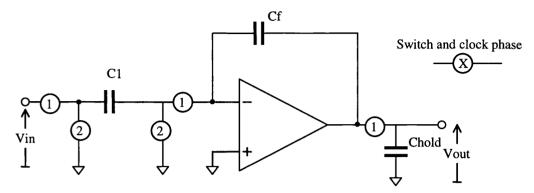

| FIGURE 77. CLASSICAL MILLER INTEGRATOR                                        |

| FIGURE 78. INTEGRATOR WITH A T-CELL RESISTIVE INPUT                           |

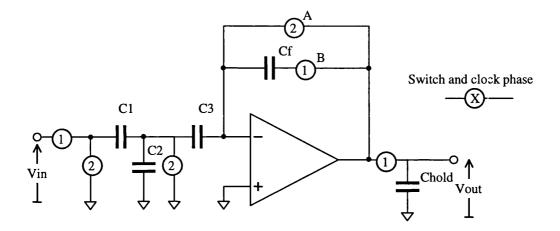

| FIGURE 79. SIMPLE SWITCED-CAPACITOR INTEGRATOR WITH A SAMPLE AND HOLD CIRCUIT |

| 141                                                                           |

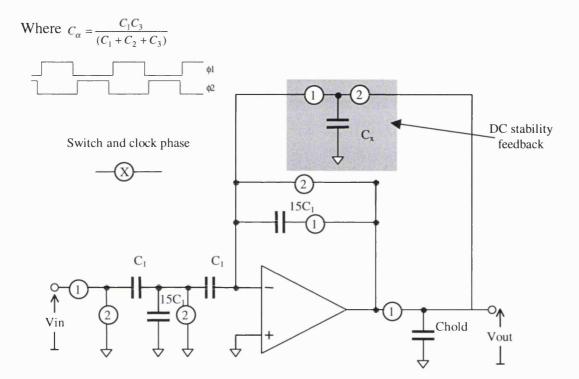

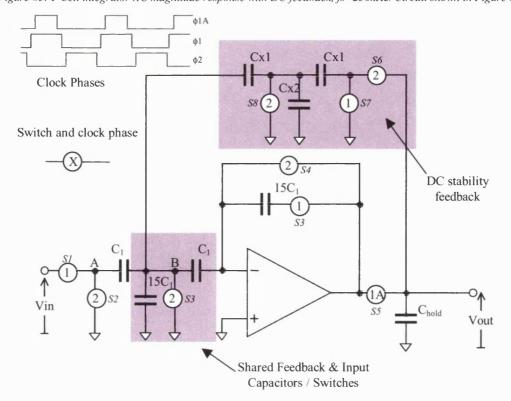

| FIGURE 80. T-CELL SWITCHED CAPACITOR INTEGRATOR                               |

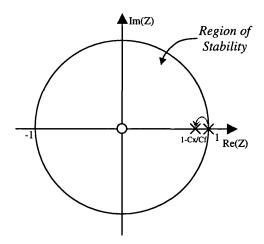

| FIGURE 81. T-CELL INTEGRATOR WITH DC STABILITY FEEDBACK OF FIGURE 81144       |

| FIGURE 82. Z-PLANE POLE-ZERO DIAGRAM FOR THE T-CELL INTEGRATOR                |

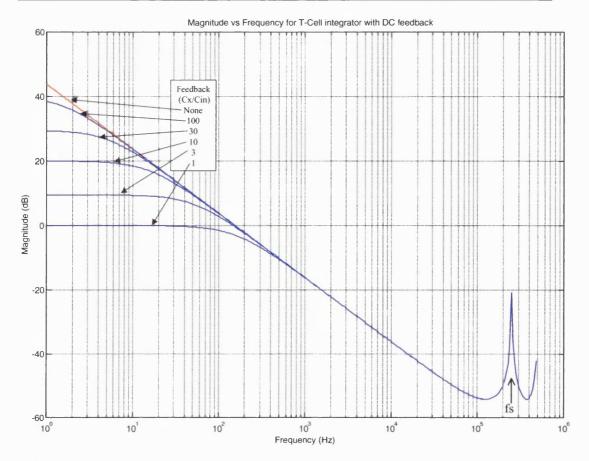

| FIGURE 83. T-CELL INTEGRATOR AC MAGNITUDE RESPONSE WITH DC FEEDBACK,          |

| FS=250KHz. CIRCUIT SHOWN IN FIGURE 81                                         |

| FIGURE 84. FINAL T-CELL INTEGRATOR WITH DC STABILITY FEEDBACK                 |

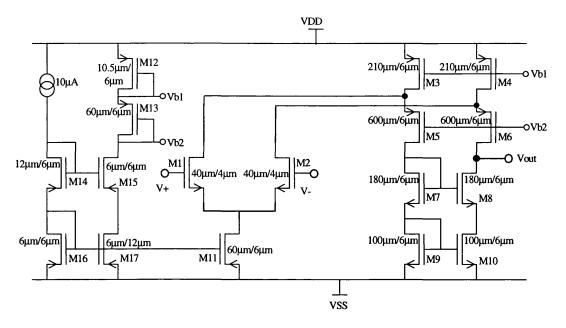

| FIGURE 85. FOLDED CASCODE AMPLIFER FOR THE INTEGRATOR                         |

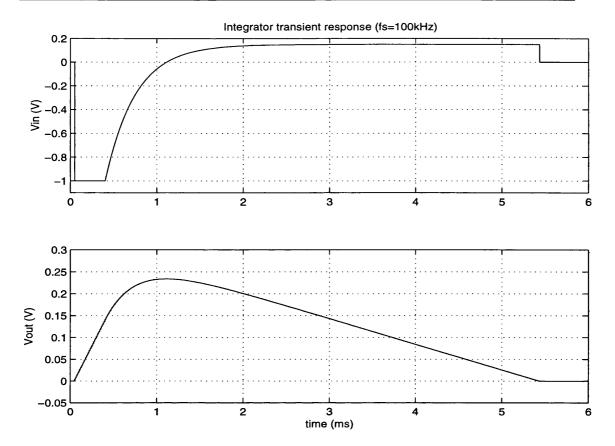

| FIGURE 86. SIMULATION RESULTS FOR THE INVERTING T-CELL SC INTEGRATOR,         |

| FS=100kHz, top signal Vin, bottom signal Vout                                 |

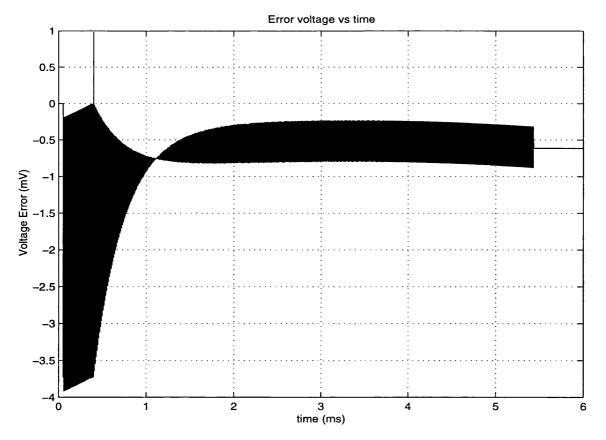

| FIGURE 87. TRANSIENT INTEGRATOR ERROR (FS=100kHz)                             |

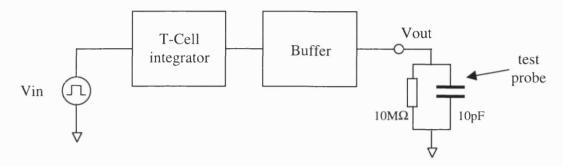

| FIGURE 88. TEST CONFIGURATION FOR THE T-CELL INTEGRATOR                       |

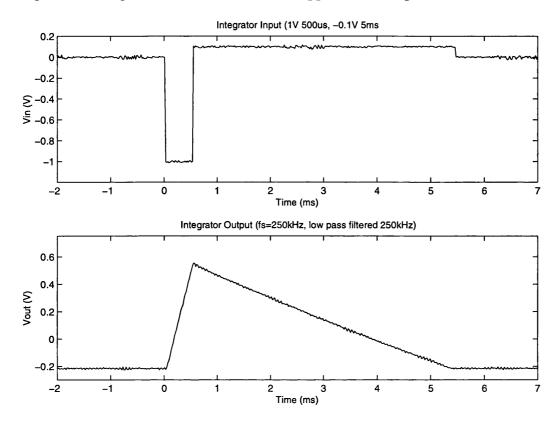

| Figure 89. Integrator output for a 1V quasitrapezoidal input (fs=250kHz,      |

| FILTERED AT 250KHz)                                                           |

| FIGURE 90. INTEGRATOR SWITCHING TRANSIENTS (AC COUPLED, FS=200KHz)154         |

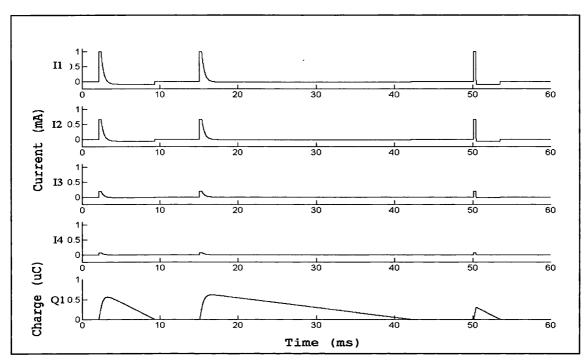

| Figure 91. Output of the stimulator in Pentapolar mode, I1=1ma, I2=2/3ma I1,  |

| I3=1/3MA I1, I4=1/15MA I1, (TWO QUASITRAPEZOIDAL PULSES OF DIFFERING          |

| REVERESE AMPLITUDE AND A SQUARE PULSE SHOWN)                                  |

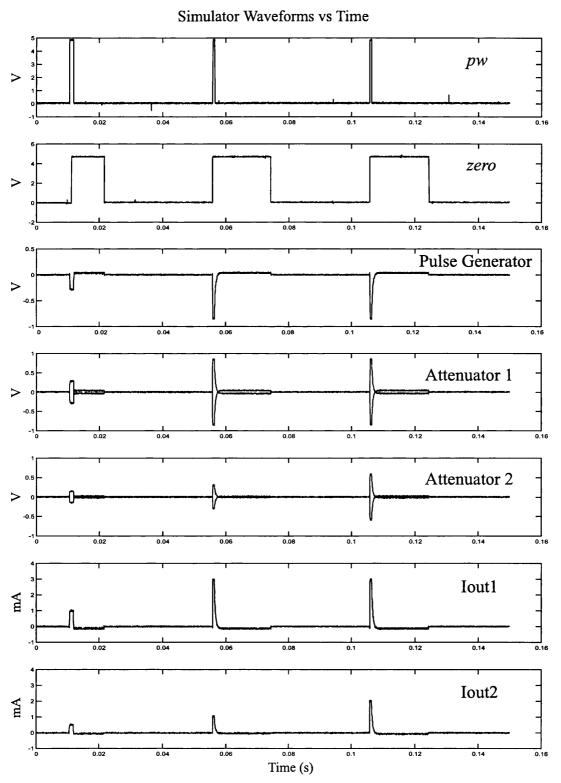

| FIGURE 92.EXPERIMENTAL STIMULATOR WAVEFORMS (TRIPOLAR) FROM TOP TO BOTTOM     |

| SHOWING: PW, ZERO, PULSE GENERATOR OUTPUT, ATTENUATORS 1 AND 2 (POSITIVE      |

| AND NEGATIVE OUTPUTS) AND FINALLY OUTPUT CURRENTS FROM THE                    |

| TRANSCONDUCTOR 160                                                            |

| FIGURE 93. INNERVATION OF THE BLADDER AND BOWEL FROM THE SACRAL ROOTS | 164     |

|-----------------------------------------------------------------------|---------|

| FIGURE 94. OVERVIEW OF A SELECTIVE STIMULATOR SYSTEM                  | 168     |

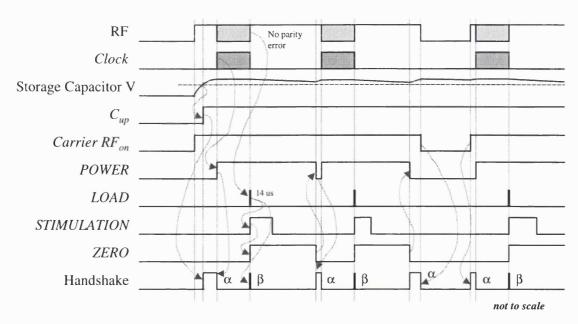

| FIGURE 95. CONTROL SIGNALS AND HANDSHAKING TIMING DIAGRAM             | 170     |

| FIGURE 96. COMPLETE STIMULATION UNIT                                  | 171     |

| FIGURE 97. FLOW DIAGRAM OF THE DIGITAL CONTROL UNIT                   | 172     |

| FIGURE 98. A COMPLETE FOUR-CHANNEL TRIPOLAR SELECTIVE STIMULATOR      | 174     |

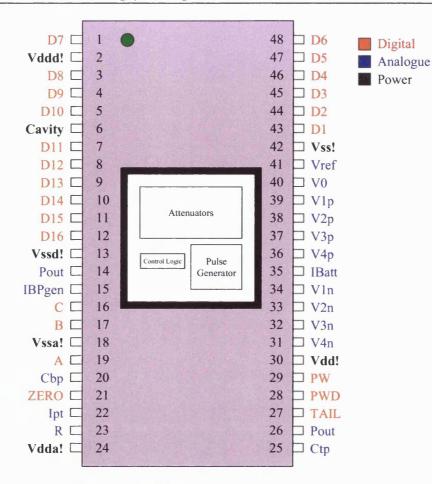

| FIGURE 99. PINOUT AND FLOOR PLAN OF IC SSTIM1                         | 183     |

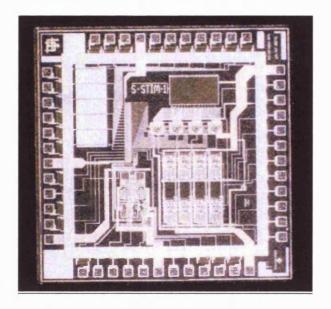

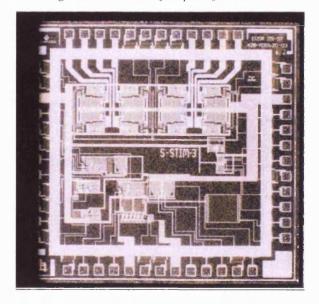

| FIGURE 100. PHOTOGRAPH OF IC SSTIM1                                   | 183     |

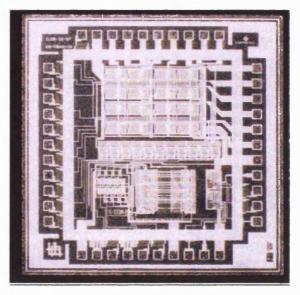

| FIGURE 101. PINOUT AND FLOORPLAN OF IC SSTIM2                         | 184     |

| FIGURE 102. PHOTOGRAPH OF IC SSTIM2                                   | 184     |

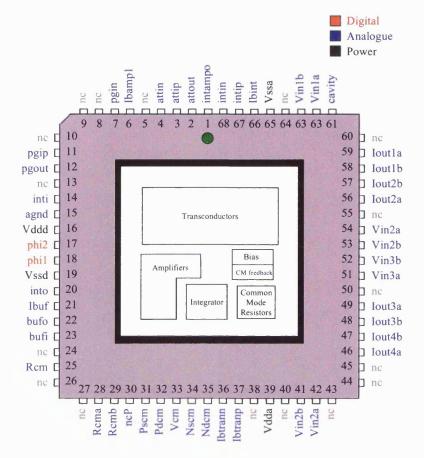

| FIGURE 103. PINOUT AND FLOORPLAN OF IC SSTIM3                         | 185     |

| FIGURE 104. PHOTOGRAPH OF IC SSTIM3                                   | 185     |

| FIGURE 105. AMPLIFIER CONFIGURATIONS FOR A) DC GAIN, AC RESPONSE B) C | )ffset, |

| SLEW RATE                                                             | 186     |

| FIGURE 106. PCBs FOR TESTING SSTIM1                                   | 188     |

| FIGURE 107. SCHEMATIC OF CIRCUIT USED TO TEST SSTIM1                  | 189     |

| FIGURE 108. SCHEMATIC OF CIRCUIT USED TO TEST SSTIM2                  | 191     |

| FIGURE 109. PCB USED FOR TESTING SSTIM2                               | 192     |

| FIGURE 110. PCB USED FOR TESTING SSTIM3                               | 192     |

| FIGURE 111. SCHEMATIC OF CIRCUIT USED TO TEST SSTIM3                  | 194     |

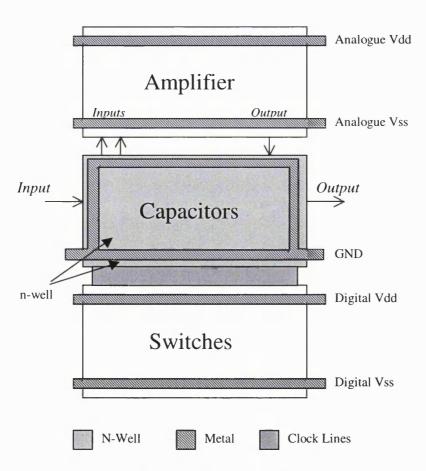

| FIGURE 112. LAYOUT OF THE T-CELL INTEGRATOR                           | 195     |

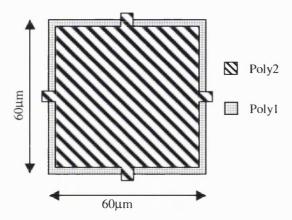

| FIGURE 113. UNIT CAPACITOR LAYOUT FOR THE INTEGRATOR                  | 196     |

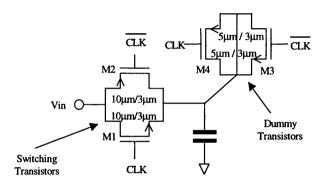

| FIGURE 114. DUMMY TRANSISTOR IMPLEMENTATION FOR A SIMPLE SAMPLE AND   | ) HOLD  |

| STAGE                                                                 | 197     |

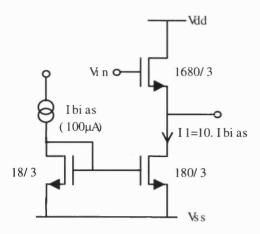

| FIGURE 115. OUTPUT BUFFER FOR THE T-CELL AMPLIFIER                    | 198     |

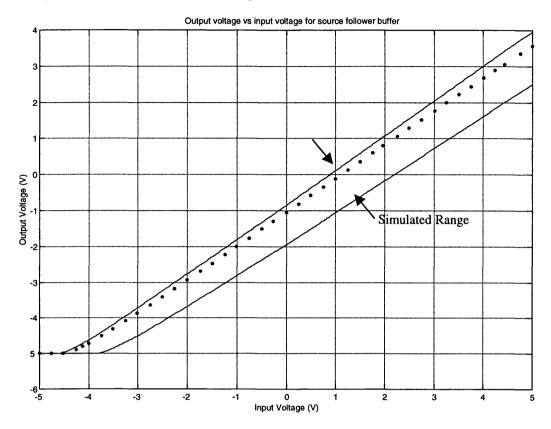

| FIGURE 116. DC CHARACTERISTICS OF THE BUFFER WITH SIMULATED TOLER     |         |

| (IBIAS=100μA)                                                         | 199     |

# LIST OF TABLES

| TABLE 1. SUMMARY OF PREVIOUS WORKS IN SELECTIVE STIMULATION BY FIBRE SIZE         | 42    |

|-----------------------------------------------------------------------------------|-------|

| TABLE 2. SUMMARY OF PREVIOUS WORKS IN SELECTIVE STIMULATION BY FIBRE POSI         | ΠON   |

|                                                                                   | 50    |

| TABLE 3. EXPECTED USES WITH CUFF TYPES FOR THE SELECTIVE STIMULATOR               | 55    |

| TABLE 4. NUMBER OF NERVE CUFFS FOR THE INITIAL TEST DEVICES                       | 56    |

| TABLE 5. EXAMPLES OF THE THRESHOLDS FOUND FOR ANODAL BLOCKING USING TECS          | 59    |

| TABLE 6. OUTPUT WAVEFORMS SPECIFICATION                                           | 65    |

| TABLE 7. CONTROL OF OUTPUT CURRENTS IN TRIPOLAR OPERATION                         | 66    |

| TABLE 8. BLOCKING CAPACITOR PARAMETERS                                            | 73    |

| TABLE 9. NUMBER OF BITS REQUIRED FOR THE STIMULATOR MODULES                       |       |

| TABLE 10. DAC SPECIFICATION                                                       | 82    |

| TABLE 11. MIETEC STANDARD CELL DAC                                                | 82    |

| TABLE 12. DAC AMPLIFIER SPECIFICATION                                             | 84    |

| TABLE 13. CHARACTERISTICS OF THE DAC OP-AMP                                       | 85    |

| TABLE 14. DAC TESTING RESULTS                                                     | 85    |

| TABLE 15. PULSE GENERATOR SPECIFICATION                                           | 86    |

| TABLE 16. SPECIFICATIONS OF THE PULSE GENERATOR OPAMP                             | 91    |

| TABLE 17. PULSE GENERATOR AMPLIFIER SIMULATED CHARACTERISTICS                     | 91    |

| TABLE 18. PULSE GENERATOR SIMULATED CHARACTERISTICS                               | 92    |

| Table 19. Pulse generator experimental rise time with a RPCP set to 350 $\mu s \$ | 95    |

| TABLE 20. REVERSE VOLTAGE (VNEG) MEASUREMENTS FOR AF = 1V                         | 96    |

| TABLE 21. CHARACTERISTICS OF THE PULSE GENERATOR OPAMP                            | 97    |

| TABLE 22. PULSE GENERATOR SPECIFICATION AND EXPERIMENTAL RESULTS                  | 98    |

| Table 23. Attenuator specification                                                | 99    |

| TABLE 24. ATTENUATOR: COMPONENTS AND AREAS OCCUPIED                               | . 103 |

| Table 25. Simulated characteristics compared to specification                     | . 104 |

| Table 26. Attenuator simulated and experimental characteristics compa             | RED   |

| TO SPECIFICATION                                                                  | . 106 |